# Multi-level Parallel Branch-and-Bound Algorithms for Solving Permutation Problems on GPU-accelerated Clusters

Mohand Mezmaz

# ▶ To cite this version:

Mohand Mezmaz. Multi-level Parallel Branch-and-Bound Algorithms for Solving Permutation Problems on GPU-accelerated Clusters. Complexité [cs.CC]. Université Lille 1, 2020. tel-03100303

# HAL Id: tel-03100303 https://hal.science/tel-03100303

Submitted on 6 Jan 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Public Domain

École Doctorale Sciences pour l'Ingénieur Université Lille Nord de France

# HABILITÉ À DIRIGER DES RECHERCHES DISCIPLINE : INFORMATIQUE

présentée et soutenue publiquement, le 18 septembre 2020, par

# Mohand Mezmaz

# Multi-level Parallel Branch-and-Bound Algorithms for Solving Permutation Problems on GPU-accelerated Clusters

Algorithmes Parallèles Multi-niveaux de Séparation et Évaluation pour la Résolution de Problèmes de Permutation sur des Clusters Accélérés par GPUs

Jury

Président : Pierre Boulet Professeur, Université Lille Nord de France

Rapporteurs : Enrique Alba Professeur, Université de Málaga

Frédéric Saubion Professeur, Université d'Angers Pierre Sens Professeur, Sorbonne Université

Examinateurs : Pascal Bouvry Professeur, Université du Luxembourg

Amir Nakib MdC HDR, Université Paris-Est Créteil

Garant : Nouredine Melab Professeur, Université Lille Nord de France

# Acknowledgments

Je tiens tout particulièrement à exprimer ma profonde gratitude à Nouredine Melab, Garant de mon HDR: tannemirt! C'est une grande chance d'avoir continué, après ma thèse, de bénéficier de la rigueur de Nouredine, de sa motivation et de ses conseils.

Mes remerciements sincères vont également à Enrique Alba, Frédéric Saubion et Pierre Sens de m'avoir fait l'honneur de rapporter cette HDR, ainsi qu'a Pierre Boulet, Pascal Bouvry et Amir Nakib d'avoir accepté de faire partie de mon jury. Leur grande implication dans cette soutenance m'a permis de présenter mon HDR, même dans des conditions particulières.

Je voudrais aussi adresser un grand merci à Daniel Tuyttens, Chef du Service MARO de l'Université de Mons. Par sa confiance et ses conseils, Daniel a beaucoup contribué à mes recherches depuis toutes ces années.

Mes remerciements sincères vont également à Rudi Leroy et Jan Gmys, que j'ai coencadré durant leurs thèses. Leurs contributions constituent les ingrédients secrets du succès de cette HDR.

Merci à tous les collègues et anciens collègues du Service MARO d'avoir participé à cet esprit d'équipe formidable.

Mes derniers remerciements et non les moindres vont à ma famille, et en particulier à mes parents. Leurs efforts, leurs patiences et leurs encouragements sont déterminants pour cette réussite.

# **Contents**

| 1 | Mai  | Main research activities since my PhD |                                 |    |  |  |

|---|------|---------------------------------------|---------------------------------|----|--|--|

| 2 | Intr | roduction                             |                                 |    |  |  |

| 3 | Bacl | ckground and related works            |                                 |    |  |  |

|   | 3.1  | Introd                                | uction                          | 15 |  |  |

|   | 3.2  | Permu                                 | tation problems                 | 16 |  |  |

|   |      | 3.2.1                                 | Permutations                    | 16 |  |  |

|   |      | 3.2.2                                 | Flowshop problem                | 17 |  |  |

|   | 3.3  | Linked-list based PB&B                |                                 |    |  |  |

|   |      | 3.3.1                                 | Branching                       | 20 |  |  |

|   |      | 3.3.2                                 | Bounding                        | 21 |  |  |

|   |      | 3.3.3                                 | Pruning                         | 22 |  |  |

|   |      | 3.3.4                                 | Selection                       | 23 |  |  |

|   | 3.4  | Relate                                | d works                         | 24 |  |  |

|   |      | 3.4.1                                 | Parallel CPU B&B                | 24 |  |  |

|   |      | 3.4.2                                 | Parallel GPU B&B                | 26 |  |  |

|   |      | 3.4.3                                 | Cluster B&B                     | 28 |  |  |

|   | 3.5  | Conclu                                | isions                          | 29 |  |  |

| 4 | Sing | le-core                               | e IVM-based permutation B&B     | 31 |  |  |

|   | 4.1  | Introd                                | uction                          | 31 |  |  |

|   | 4.2  | IVM da                                | ata structure                   | 32 |  |  |

|   | 4.3  | 3 PB&B Operations                     |                                 | 34 |  |  |

|   |      | 4.3.1                                 | Selection                       | 35 |  |  |

|   |      | 4.3.2                                 | Branching                       | 37 |  |  |

|   |      | 4.3.3                                 | Bounding                        | 37 |  |  |

|   |      | 4.3.4                                 | Pruning                         | 39 |  |  |

|   |      | 4.3.5                                 | Initialization and finalization | 39 |  |  |

|   | 4.4  | Experi                                | ments                           | 40 |  |  |

|   |      | 4.4.1                                 | Experimental protocol           | 40 |  |  |

|   |      | 4.4.2                                 | Obtained results                | 42 |  |  |

|   | 45   | Conclu                                | isions                          | 44 |  |  |

6 Contents

| 5 | Multi-core Interval-based permutation B&B |                                       |                                         |    |  |  |

|---|-------------------------------------------|---------------------------------------|-----------------------------------------|----|--|--|

|   | 5.1                                       | Introdu                               | uction                                  | 47 |  |  |

|   | 5.2                                       | Factora                               | adic intervals                          | 49 |  |  |

|   |                                           | 5.2.1                                 | Number systems                          | 49 |  |  |

|   |                                           | 5.2.2                                 | Factorial number system                 | 51 |  |  |

|   | 5.3                                       | Interva                               | al-based work stealing                  | 57 |  |  |

|   |                                           | 5.3.1                                 | Work unit: interval of factoradics      | 57 |  |  |

|   |                                           | 5.3.2                                 | Work unit communication                 | 58 |  |  |

|   |                                           | 5.3.3                                 | Victim selection policies               | 60 |  |  |

|   |                                           | 5.3.4                                 | Granularity policies                    | 63 |  |  |

|   | 5.4                                       | Experi                                | ments                                   | 64 |  |  |

|   |                                           | 5.4.1                                 | Experimental protocol                   | 64 |  |  |

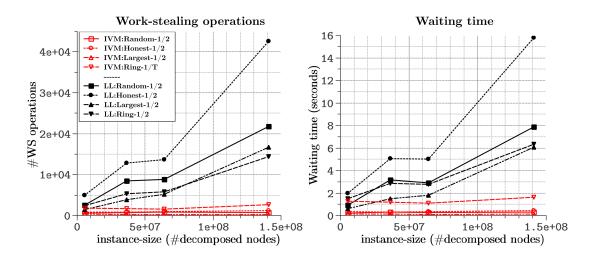

|   |                                           | 5.4.2                                 | Pool management evaluation              | 66 |  |  |

|   |                                           | 5.4.3                                 | Interval-based work stealing evaluation | 67 |  |  |

|   | 5.5                                       | Conclu                                | isions                                  | 69 |  |  |

| 6 | GPU-centric permutation Branch-and-Bound  |                                       |                                         |    |  |  |

|   | 6.1 Introduction                          |                                       |                                         |    |  |  |

|   | 6.2                                       | IVM-ba                                | ased Data structures                    | 73 |  |  |

|   |                                           | 6.2.1                                 | Memory requirements                     | 73 |  |  |

|   |                                           | 6.2.2                                 | Memory constraint: Number of IVMs       | 74 |  |  |

|   | 6.3                                       | Operat                                | ions                                    | 75 |  |  |

|   |                                           | 6.3.1                                 | Bound mapping operation                 | 75 |  |  |

|   |                                           | 6.3.2                                 | IVM mapping operation                   | 79 |  |  |

|   |                                           | 6.3.3                                 | Work stealing operation on GPU          | 80 |  |  |

|   | 6.4                                       | Experi                                | ments                                   | 83 |  |  |

|   |                                           | 6.4.1                                 | Experimental protocol                   | 83 |  |  |

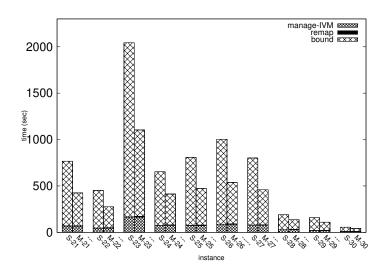

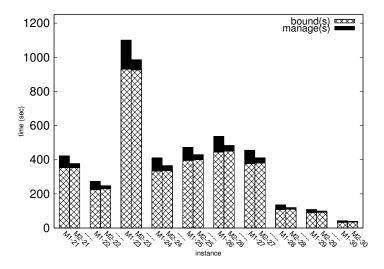

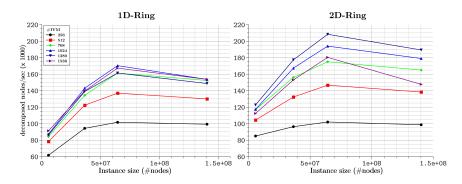

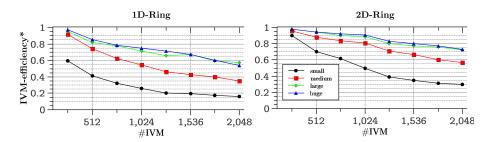

|   |                                           | 6.4.2                                 | Evaluation of bound mapping schemes     | 84 |  |  |

|   |                                           | 6.4.3                                 | Evaluation of IVM mapping schemes       | 86 |  |  |

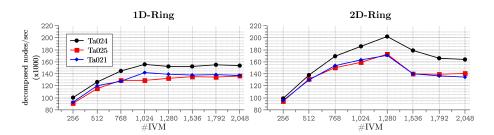

|   |                                           | 6.4.4                                 | Evaluation of work stealing schemes     | 88 |  |  |

|   |                                           | 6.4.5                                 | Comparison of PB&B@GPU and GPU LL PB&B  | 91 |  |  |

|   | 6.5                                       | Conclu                                | sions                                   | 92 |  |  |

| 7 | Permutation B&B for GPU-powered clusters  |                                       |                                         |    |  |  |

|   | 7.1                                       | · · · · · · · · · · · · · · · · · · · |                                         |    |  |  |

|   | 7.2                                       |                                       | al-list operators                       | 96 |  |  |

|   |                                           |                                       | Interval operators                      | 96 |  |  |

| Contents | 7 |

|----------|---|

| Coments  | / |

|          |   |

|              | 7.2.2 Interval-list operators                   | 97  |

|--------------|-------------------------------------------------|-----|

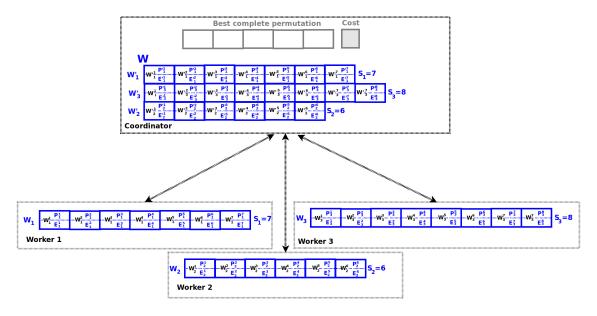

| 7.3          | Data structures and operations                  | 99  |

|              | 7.3.1 Data structures                           | 99  |

|              | 7.3.2 Work processing operations                | 101 |

| 7.4          | Experiments                                     | 103 |

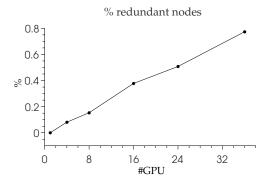

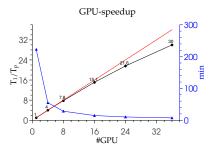

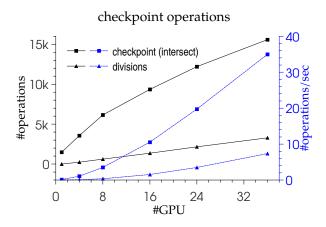

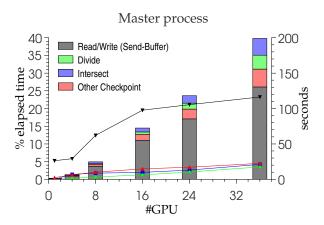

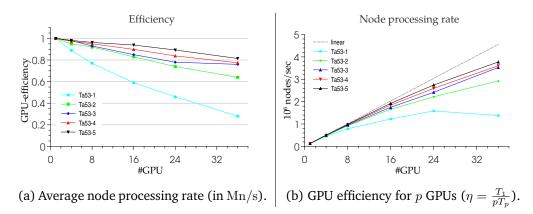

|              | 7.4.1 Experiments on a cluster of GPUs          | 103 |

|              | 7.4.2 Experiments on a cluster of GPUs and CPUs | 108 |

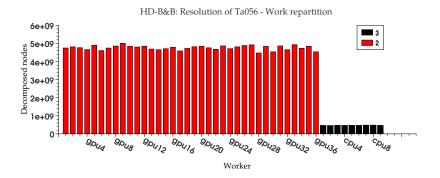

|              | 7.4.3 Resolution of a big instance              | 109 |

| 7.5          | 7.5 Conclusions                                 |     |

| 8 Co         | nclusions and perspectives                      | 115 |

| Bibliography |                                                 |     |

8 Contents

# Main research activities since my PhD

The research works done in my PhD thesis, defended at the end of 2007, focused on the parallelization of combinatorial optimization algorithms. During this thesis, we mainly presented a new approach, called B&B@Grid [MMT07b], for the parallelization of Branchand-Bound (B&B) algorithms.

The results of our experiments show that the coding of B&B@Grid divides the size of the communicated information by an average of 766. These experiments have also shown that the coding of the communicated information, performed using B&B@Grid, is on average 92 smaller than the coding of the token approach of PICO [EPH00], and 465 smaller than the coding of the variable approach published in [IF00]. These experiments demonstrate the advantage of using B&B@Grid in clusters to reduce the size of the communicated information, and therefore the communication delays.

On the other hand, despite the high number of CPU cores in our clusters, about 1111 on average, the experiments, carried out with the *master-worker* paradigm, showed that the master exploits its processor at 1.29% on average, and that workers spend an average of 99.94% of their time in computing. These two percentages are good indicators of the quality of B&B@Grid's load balancing strategy and its ability to scale up.

The B&B@Grid approach is used to solve an instance of the flowshop problem, known as *Ta056* (50 jobs and 20 machines), and published in [Tai93] which has never been optimally solved before. In terms of the used computing power, the *Ta056* resolution ranks second among the large-scale challenges tackled in combinatorial optimization field before 2007. On average, 328 processors were used for more than 25 days, and a peak of about 1200 CPU cores was recorded during this resolution.

In the recent years, GPU-powered clusters appeared to be as more and more interesting alternatives for the parallelization of some algorithms. GPU accelerators are often used in today's largest high performance computing systems for regular and data parallel applications. However, B&B algorithms are highly irregular in terms of workload, control flow and memory access patterns. The research works, presented in this document, are

a continuation of B&B@Grid to adapt B&B algorithms, having an irregular structure, to GPU-powered clusters, having accelerators with a highly regular architecture.

Before presenting our contributions, in the parallelization of B&B algorithms, this chapter describes our main industrial and academic research activities, done after my PhD and which are not presented in this manuscript. This industrial and academic research is presented in Subsection 1 and Subsection 1, respectively.

## 2.1 Industrial research

Our industrial research is mainly carried out in the railway field. These research works allowed us to have several contributions, such as the development of a train simulator, the development of a train autopilot, reducing the energy consumption of a rail network, or automatic learning of the technical parameters of a train. In general, our work for the railway industry is not intended for scientific publications. One of our main industrial partners, Alstom, prefers to keep confidentiality for promising results.

# G-Drive: an automatic train operation

- **Problem description:** The cost of energy, for the traction of passenger trains, is estimated at  $\sim \! 100$  million euros during 2006 in Belgium, and at  $\sim \! 850$  million euros during 2008 in France. Some studies show that, in the same journey and the same driving conditions, a train can consume up to 50 % more energy than another train. Therefore, the cost of the wasted energy for train traction is relatively high.

- Conventional approach: To reduce this cost, railway operators use two types of approaches. The first approach is to give the driver a list of expected times at some track positions during journey. And the second is to equip trains with a driver assistance system.

- Our approach: In collaboration with Alstom, we developed an automatic train control system. This system automatically controls and drive train by optimizing energy consumption and respecting the constraints.

- **Obtained results:** Simulator tests show that our system saves from 15% to 25% energy compared to drivers of the National Railway Company of Belgium.

- **Publications:** We decided to do not publish the used optimization method because Alstom plans to market this system in the coming months. An international patent is under submission. In this patent, I am one of the authors of the developed system.

# **Energy-efficient railway traffic control**

- **Problem description:** In modern railway system, most of the energy required by trains is supplied by the electric network. In recent years, the reduction of energy consuming has become one of the main concerns of the railway managers.

- Conventional approach: Although railway traffic control is an important topic in

the modern railway management system, few results about the studies on railway

traffic control, especially real-time energy-efficient traffic control for general railway system, have been published in the literature. Most of the studies simplify the

problem by using average velocities or constant speeds to estimate the energy consumption of the trains along their journeys.

- Our approach: Our method proposes suitable driving profiles for the trains that run in the same railway network in order to reduce the total energy consumption of the whole railway network. To minimize the total energy consumption of a targeted railway network, it is important to not only propose ecodriving driving profile for each train but also to synchronize the operations of different trains. This synchronization introduces a high reutilization rate of the energy regenerated by dynamic braking operations of the trains.

- **Obtained results:** Experimental data used in to evaluate our approach are supplied by the Belgian railway infrastructure manager.

- **Publications:** This work is published in Mathematical Problems in Engineering journal [TFMJ13]. According to the experimental results, our proposed method can generate energy-efficient traffic control solution, where the driving profile of a train is defined by a suitable mono-train driving strategy that can be different from the driving strategy used by another train part in the same railway network.

# Learning the parameters of a train

- **Problem description:** In some algorithms, it is important to modelize the train. The obtained train model is defined by a set of parameters. These parameters are related to: (1) the train traction system; (2) its braking system; (3) its aerodynamic; (4) the different masses of the train; and (5) its length; In total, any realistic train model is defined by more than 100 parameters.

- **Conventional approach:** For each train, it is important to know the values of these parameters. To find these values, the conventional approach is (1) to contact the

manufacturer of the train to get the values of some parameters, and (2) to measure the values of the other parameters. However, this approach has two disadvantages: (1) measuring the value of a parameter can be an expensive operation; and (2) some parameters, such as the total mass of a train, are constantly changing;

- Our approach: Our learning algorithm deduces the values of the parameters by only observing the behavior of the train. The train is seen as a system which receives input commands. These commands can be traction, braking, or no control. A command changes the state of the train. This state is defined by the position of train, its velocity, and its acceleration. The state of the train can be measured by an odometer, and this state is measured with a certain noise. The role of the learning algorithm is to deduce the parameters of the train using a great number of pair of values. Each pair is defined by (1) an input command and (2) the obtained state.

- Obtained results: With our method, we are able to learn the exact values of all parameters when the states of train is known without noise. If the states contain noise, the algorithm is able to learn these values with an average error of less than 2%.

- **Publications:** These results are obtained in January 2017. Next weeks, we will discuss with our partners the possibility of publishing this work.

## Developing a train simulator

- **Problem description:** In the optimization algorithm of the railway sector, the cost function is sometimes based on the simulation of a train.

- **Conventional approach:** At the beginning of a project, we received a professional simulator, where the simulation is based on a time discretization. However, we observed that the obtained simulations are not sufficiently accurate, and some values do not match those of the train's mathematical model.

- Our approach: So we developed a train simulator, based on a time discretization, and with a better accuracy. This simulator takes into account, not only, the control system, the traction and braking systems, and the aerodynamic of the train, but also, the track topology, namely gradients and curves.

- Obtained results: With negligible maximum errors in the positions, velocities and accelerations, the obtained simulations correspond to those of the train's mathematical model.

• **Publications:** This simulator is more a development work than a research one. As the scientific contribution is not important, we do not plan to publish this work.

# Multi-objective optimized railway timetable

- **Problem description:** A timetable can be improved according to different criteria, such as robustness, which measures the sensitivity of a timetable to disturbances, and total energy consumption. As the Belgian network is relatively dense, it is important to improve the timetable by taking into account these two criteria.

- **Conventional approach:** To the best of our knowledge, there is no work in the literature which optimize the timetable according to the robustness and the energy consumption, using a realistic energy model. In addition, some works try to optimize the timetable by building a new timetable from scratch. However, the users do not like having lot of changes in the timetable.

- Our approach: The objective of our algorithm is not to generate a new timetable but to improve the current one, transparently to the user. Between two successive stations, a timetable defines the moments at which the train must pass at certain intermediate positions of the track (i.e. between two stations). Our algorithm does not modify the arrivals and departures times at the stations, but updates only the times of these intermediate positions.

- Obtained results: The evaluation of the energy consumed by a network requires the

use of a special simulator. In this project, our role was not to develop this simulator,

but only the optimization algorithm. Our optimization software was provided to

our partners approximately six months before the end of the implementation of the

simulator.

- **Publications:** This work is not published.

## Energy-aware railway timetable re-scheduling during disturbances

- **Problem description:** Disturbance management can be seen as a three-step process. The first step is the detection of a disturbance. Then, a decision is made to manage this event. And finally, this decision is implemented.

- Conventional approach: In our work, we assume that another system is responsible

for detecting disturbances. Decision-making, such as the removal of a train, its deviation, or its slowdown, is a complicated process, which is hard to automate. When a

decision is taken to change the path of a train, the Belgian railway operator, Infrabel, manually generates a local timetable for this path.

- Our approach: The software, which we have developed, allows to generate this local timetable automatically by optimizing at the same time the tardiness and the energy consumption.

- Obtained results: The evaluation of the energy consumed by a network requires the

use of a special simulator. In this project, our role was not to develop this simulator,

but only the optimization algorithm. Our optimization software was provided to

our partners approximately six months before the end of the implementation of the

simulator.

- Publications: This work is not published.

# 2.2 Academic research

Simultaneously with industrial research, we also had contributions in the academic research. This section presents only our main academic works which are not related to B&B algorithms. These contributions belong to three different domains, namely combinatorial optimization, cloud computing and machine learning.

# **Hyper-heuristic GRASP**

- **Problem description:** GRASP is a well-known two-phase metaheuristic. First, a construction phase builds a complete solution iteratively component by component by a greedy randomized algorithm. After that, a local search phase improves this solution. The basic GRASP configuration is defined by (1) a cost function, (2) a probabilistic parameter of greediness, and (3) a neighborhood structure.

- Conventional approach: Traditionally, the choice of a GRASP configuration (greediness, cost function, and neighborhood) is guided by the theoretical studies or by manually testing the different parameter values. However, hyper-heuristic framework exists to design and adapt automatically heuristics to solve hard computational search problems. The feature of this framework is a protocol (also called a high-level heuristic or mechanism) that manages with the low-level heuristics (tabu search, genetic algorithms, etc.) looking for the best configuration of their parameters.

- Our approach: Therefore, in our work we propose a hyper-heuristic that runs GRASP configurations in accordance with several predefined configurations. Each

configuration manages a set of one-iteration GRASPs with different parameter. The goal is to automatically test multiple GRASPs and collect performance measures in order to detect the leading configurations for given test instances. We consider 7 well-known neighborhood structures, 9 greediness values, and 5 cost functions (including a cost function based on a bounding which is integrated for the first time in GRASP).

- **Obtained results:** Our computational experiments have not revealed one leading configuration, however the winning one is a stochastic mix of several configurations.

- **Publications:** This work is published in CCPE journal [AMTM17] (Concurrency and Computation: Practice and Experience).

# Optimization of precedence-constrained parallel application problem

- Problem description: Parallel programs can be represented by a directed acyclic graph where each node represents a task and each edge from a node A toward a node B means that the task B starts after the end of the task A. In this graph, The weight of a node A represents the computation cost of the task A, and the weight of an edge (A,B) represents the communication cost from the task A to the task B. These parallel tasks must be deployed on several computing units. Each computing unit can work with different voltage levels. For each voltage level, a computing unit has a processing speed and an energy consumption. Precedence-constrained parallel applications are one of the most typical application models used in scientific and engineering fields.

- **Conventional approach:** In the literature, usually the goal is to deploy this application in order to minimize the total processing time only.

- Our approach: Our objective was to minimize not only the total processing time but also the total energy consumption.

- Obtained results: Experiments show that our method improves on average the results of the literature for about 10,000 standard instances. The energy consumption is reduced by about 50% and the processing time by 10%.

- **Publications:** This work is published in JPDC [MMK<sup>+</sup>11] (Journal of Parallel and Distributed Computing) which is an A\*-journal. According to Google Scholar, this paper is the third most cited paper in JPDC during the last 5 years (more than 120 citations).

# Solving Tuberculosis Transmission Control (TTC) problem using parallel simulationand surrogate-assisted optimization

- **Problem description:** Tuberculosis is the most lethal infectious disease with 10 million cases of active tuberculosis recognized in 2017. The World Health Organization (WHO) proposed the End Tuberculosis Targets, with the objective to cut new cases by 90% between 2015 and 2035.

- Conventional approach: The AuTuMN simulator [TRDM17] implements a tuberculosis transmission dynamic model and facilitates predictions of future tuberculosis epidemic trajectories across diverse scenarios. Besides, the coupling with an economic model allows to compare and analyze different control policies, which then helps decision makers in their effort to decrease local tuberculosis burden. However, solving TTC problem using AuTuMN simulator, like many simulation-based optimization resolutions, are computationally expensive.

- Our approach: In the PhD thesis of Guillaume Briffoteaux, which I co-supervise, we investigate Evolution Controls (ECs) strategies that define the alternation between the simulator and the surrogate within the optimization process. The challenge is to find the best trade-off between the quality (in terms of precision) and the efficiency (in terms of execution time) of the resolution. We consider several ECs from the literature including the mechanism built on the distance-based concept of Hyper-sphere Confident Regions (HCR) and a mechanism derived from Monte Carlo dropout (MCDropout), a technique originally dedicated to quantify uncertainty in deep learning. The investigation of this latter uncertainty-aware EC is uncommon in surrogate-assisted optimization.

- **Obtained results:** We identify some characteristics common to several ECs and then derive from them different variants that are compared considering a pioneering application to the TTC problem. The reported results show that HCR- and MCDropout-based EC coupled with massively parallel computing outperforms the literature strategies.

- **Publications:** A first part of this work is published in the HPCS'2018 conference [BMMT18], the second part is under minor revision for the Future Generation Computer Systems (FGCS) journal (Impact Factor of 5.768), and the third part is submitted to the Swarm and Evolutionary Computation (SWEVO) journal (Impact Factor of 6.330).

# Introduction

This manuscript gives an overview of my research activities focused mainly on two PhD theses that I co-supervised, namely those of Rudi Leroy [Ler15a] and Jan Gmys [Gmy17] defended respectively in 2015 and 2017. Other activities conducted within the context of academic and industrial collaborations are summarized in the CV part of this manuscript (Chapter 1).

Many industrial and economic problems, like flowshop scheduling, are permutation combinatorial optimization problems. Solving these problems consists in finding an optimal permutation of elements among a large finite set of possible permutations. A wide range of these problems is known to be large in size and NP-hard to be solved. The Permutation Branch-and-Bound (Permutation B&B or PB&B) algorithms are one of the most used exact methods to solve these permutation optimization problems. These algorithms are based on an implicit enumeration of all the feasible permutations of the problem to be tackled. Building and exploring the PB&B tree are performed using four main operations: branching, bounding, selection and pruning. In PB&B algorithms, if the lower bound for some tree node A is greater than the best permutation found so far, then A may be discarded from the search. This key idea of the PB&B algorithms significantly reduces the number of explored nodes. However, the execution time of a PB&B notably increases with the size of the tackled problem instance, and often only small or moderately sized instances can be practically solved.

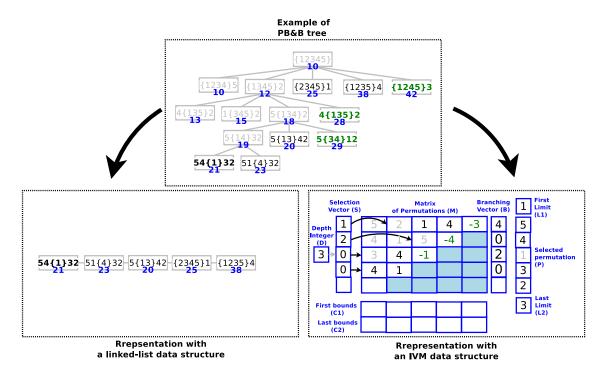

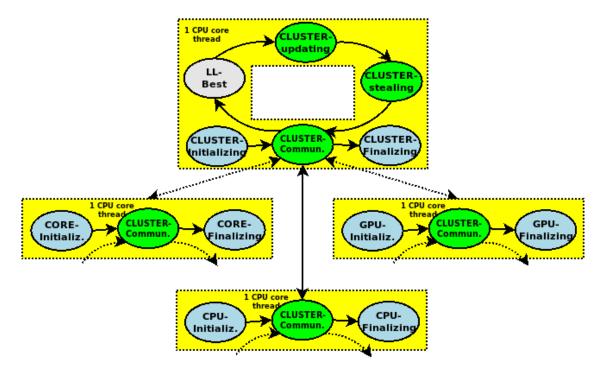

For this reason, over the last decades, parallel computing has been revealed as an attractive way to deal with larger instances of combinatorial optimization problems. Recently, multi-core processors (CPUs), Graphics processing units (GPUs) and computing clusters have been used for the parallelization of several algorithms. To the best of our knowledge, all parallel PB&B algorithms developed in the literature are based on using one centralized or distributed pool which stores nodes [GC94]. In these conventional approaches, PB&B threads cooperate by adding nodes to or removing them from this or these pool(s), usually implemented as a linked list (LL) [Cra06]. A parallel PB&B algorithm stops when this or these pool(s) is/are empty. In the two theses, our work has led to the development of four approaches, renamed in this manuscript PB&B@CORE, PB&B@CPU, PB&B@GPU and PB&B@CLUSTER.

# 2.1 PB&B on single-core processors

A single-core processor is a microprocessor able to run one single thread at any time. Processors remained single-core until it was difficult to improve their computing power by increasing clock speed or the number of transistors. Therefore even processors of smartphones are nowadays no longer single-core processors.

However before developing a parallel approach of an algorithm, it is often important to optimize the serial approach of this algorithm. A serial algorithm can be optimized in order to run it more rapidly or use less memory. If code optimization can be done using new procedures or functions, memory optimization often requires the development of a new data structure.

In our work, we propose an original and pioneering single-core PB&B@CORE algorithm, based on a new data structure, called Integer-Vector-Matrix (IVM), and the factorial number system. This special numbering system [Lai88a], also called factoradic number system, is a mixed radix numeral system adapted to numbering permutations. The objective of our new IVM-based PB&B approach is to accelerate the management of the PB&B pools and to reduce the size of the memory used to store these pools.

Our new PB&B@CORE is compared with a typical LL-based approach [MMT13] in terms of memory usage and CPU time used to manage the PB&B pool. This comparison shows that our PB&B@CORE approach outperforms this typical LL-based PB&B approach.

# 2.2 PB&B on multi-core processors

As indicated before, for decades it was possible to improve performance of a general-purpose CPU by increasing its operating frequency. However in about 2012, manufacturers encounter two main technical barriers to improve the CPU performance, namely the power barrier (i.e. the power consumption exponentially increases with each factorial increase of operating frequency), and the memory barrier (i.e. the gap between memory and processor speeds is increasing). In order to continue delivering regular performance improvements for general-purpose processors, manufacturers such as Intel and AMD have turned to multi-core designs. Multi-core processors embed two or more independent execution CPU cores into a single processor.

By providing multiple execution cores, each sequence of instructions, or thread, has a hardware execution environment entirely to itself. This enables each thread run in a truly parallel manner. Nowadays, most processors can be considered as parallel machines. When designing an algorithm for a multi-core processor, it is therefore important to take into account a certain number of issues, such as the definition of work unit and work

sharing/stealing strategies. A major advantage of multi-core processors is the possibility to parallelize using threads instead of processes. Unlike processes, which have their own virtual memory, the threads of a process share the same virtual memory. Therefore, communications between these threads are faster than between processes. Many programming methods (such as [EPS09a], [PŽ09], and [SECG11]) based on the use of threads have been developed.

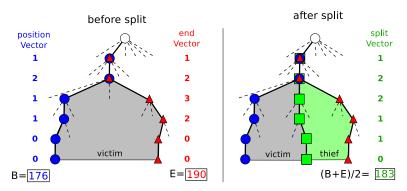

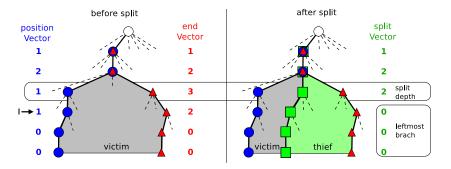

Our new method PB&B@CPU is based on a new approach to manage the pools of nodes of a PB&B parallel algorithm using five different work stealing strategies. This approach aims at reducing the CPU time used to manage the thread private PB&B pools, the memory behavior of the algorithm, the number of performed work stealing operations and finally the total execution time. It is based on the use of the IVM data structure to manage the thread private PB&B pools. In our stealing strategies, work units stolen by threads are intervals of factoradics instead of sets of nodes. The IVM-based PB&B@CPU is compared with the LL-based PB&B approach by solving some hard flowshop scheduling problem instances using the five work stealing strategies.

## 2.3 PB&B on GPU accelerators

Commodity Graphics Processing Units (GPUs) have rapidly evolved to become high performance accelerators for data-parallel computing. Recent GPUs, like Tesla V100, contain more than 5000 of processing units, capable of achieving up to 14 TFLOPS for single-precision arithmetic, and 7 GFLOPS for double-precision calculations. In addition, modern high-performance computing optimized GPUs contain up to 32GB of on-board memory, and are capable of sustaining memory bandwidths up to 900GB/sec. GPU-based accelerators are also becoming popular because of their extraordinary energy efficiency, as illustrated by The Green500 List<sup>1</sup>. The maximum power consumption of Tesla V100 is 300W. However, the parallelization of an application on a GPU can not be done directly. It is important to take into account a certain number of issues, such as the optimization of data transfer between CPU and GPU, the reduction of thread divergence, an efficient mapping of data on the GPU cores, and the best location of data on the different memories of the GPU. Because of all these issues, the usage of GPU is often restricted to regular and data parallel applications.

The irregular nature, in terms of workload, control flow and memory access patterns, of applications such as PB&B may seriously degrade the performance of the GPU. The acceleration of PB&B algorithms using GPUs is therefore a challenging task which is

<sup>&</sup>lt;sup>1</sup>http://www.green500.org

addressed by only a few works in the literature, such as [CM13], using flowshop as a test case, [CMNLdC11], applied to the traveling salesman problem and [LEB12], applied to the knapsack problem where the search tree is binary. All these approaches use linked lists (deques, stacks, etc.) to store and manage the pool of nodes, likewise most parallel PB&B algorithms in the literature. Such data structures are very difficult to handle on the GPU and often induce prohibitive performance penalties. For this reason all GPU accelerated PB&B algorithms at our knowledge perform the management of the pool of nodes at least partially on the CPU, requiring costly data transfers between host and device. In [MCB14] it is shown that the bounding operation for flowshop consumes 97 – 99% of the execution time of a sequential PB&B and that the GPU based parallelization of this operation can provide a substantial acceleration of the algorithm. However, as the management of a list of pending nodes is performed on the CPU, the transfer of data between CPU and GPU constitutes a bottleneck for GPU accelerated B&B algorithms.

This manuscript describes our new PB&B@GPU approach, which is based on the parallelization of PB&B on GPU. This parallel PB&B@GPU algorithm is, to the best of our knowledge, the first one that implements all PB&B operations on the GPU, requiring virtually no interaction with the CPU during the exploration process. It is based on the IVM data structure, which allows the efficient storage and management of the pool of nodes in permutation based combinatorial optimization problems. The IVM structure provides some regularization as it allows to store and manage the pool of nodes with data structures of constant size. However, the IVM-based parallel PB&B is still highly irregular in terms of workload, control flow and memory access patterns. None of these three issues can be ignored when implementing the PB&B algorithm on the GPU and all three are addressed in PB&B@GPU. The focus is put on the reduction of thread divergence which arises in CUDA's SIMD execution model as a consequence of control flow irregularities.

# 2.4 PB&B on GPU-powered clusters

Large-scale GPU clusters are gaining popularity in high performance computing community. In November 2019, nearly 40% of the total compute power on the TOP500 clusters<sup>2</sup> (i.e. 626 petaflops) comes from GPU-accelerated systems. Just over a decade ago, no supercomputers and clusters on the list were accelerated.

By gathering GPU processing power distributed across multiple computing nodes, it is possible to run advanced, large-scale applications efficiently, reliably, and quickly. This acceleration delivers a dramatic boost in throughput and cost savings, paving the way

<sup>&</sup>lt;sup>2</sup>https://www.top500.org

to exascale science applications. The massively parallel hardware architecture and high performance of floating point arithmetic and memory operations on GPUs make them particularly well-suited to many of the same scientific and engineering workloads that occupy HPC clusters, leading to their incorporation as HPC accelerators.

To distribute an algorithm on the computing nodes of a GPU-powered cluster, it is necessary to rethink the conventional parallel mechanisms in order to adapt them to the characteristics of this environment. Taking into account of such characteristics can be done by the resolution of the issues related to communication delays (i.e. optimizing the communication cost) and processor's heterogeneity (i.e. optimizing the load-balancing strategy).

In our work, we have developed a new method, called PB&B@GPU, based on the coordinator-worker B&B@Grid approach [MMT07c]. In order to enable the use of a hybrid CPU-GPU cluster in PB&B@GPU, a redefinition of work units is proposed using interval lists. A detailed description of the coordinator and worker new operations is provided, focusing on the revisited communication scheme. Finally, PB&B@GPU is experimented on three different GPU-enhanced clusters with up to 36 GPUs. The experimental evaluation includes scalability and stability analysis on solving very large flowshop instances.

# 2.5 Document contents

In addition to Chapter 3, which gives a state of the art of B&B algorithms, this manuscript is organized in four main chapters. Chapter 4 proposes an original and pioneer serial PB&B@CORE algorithm, based on a new data structure. Chapter 5 explains our PB&B@CPU, designed to work on multi-core CPUs. Chapter 6 describes the new PB&B@GPU approach, which is based on the parallelization of PB&B on GPUs. And finally, Chapter 7 presents our new PB&B@GPU approach for GPU-powered clusters.

# CHAPTER 3

# Background and related works

| Contents |                  |                   |  |  |  |

|----------|------------------|-------------------|--|--|--|

| 3.1      | 3.1 Introduction |                   |  |  |  |

| 3.2      | Permu            | utation problems  |  |  |  |

|          | 3.2.1            | Permutations      |  |  |  |

|          | 3.2.2            | Flowshop problem  |  |  |  |

| 3.3      | Linke            | d-list based PB&B |  |  |  |

|          | 3.3.1            | Branching         |  |  |  |

|          | 3.3.2            | Bounding          |  |  |  |

|          | 3.3.3            | Pruning           |  |  |  |

|          | 3.3.4            | Selection         |  |  |  |

| 3.4      | Relate           | ed works          |  |  |  |

|          | 3.4.1            | Parallel CPU B&B  |  |  |  |

|          | 3.4.2            | Parallel GPU B&B  |  |  |  |

|          | 3.4.3            | Cluster B&B       |  |  |  |

| 3.5      | Concl            | usions            |  |  |  |

# 3.1 Introduction

The exact resolution methods used in combinatorial optimization are often B&X algorithms. These methods are mainly available in three variants: Branch-and-Bound (B&B), Branch-and-Cut (B&C) and Branch-and-Price (B&P). There are other less known B&B variants like Branch-and-Peg [GGS04], Branch-and-Win [PC04] and Branch-and-Cut-and-Solve [CZ06]. This list is certainly not exhaustive. It is also possible to consider a simple tree-based algorithm like Divide-and-Conquer as a base for the B&B algorithm. It is enough to remove the pruning operation of the B&B, explained later, to obtain the Divide-and-Conquer algorithm. Some authors consider the B&C, B&P algorithms and other variants as separate B&B algorithms. In the remainder of the manuscript, the B&B algorithm designates the simple B&B itself or any other variant of this algorithm. In addition, permutation

B&B (PB&B) designates any B&B algorithm or its variants when it solves a permutation problem.

Many problems, solved by B&B algorithms, are permutation problems, where the goal is to find the optimal scheduling in a set of elements. To the best of our knowledge, these permutation problems are solved using B&B without taking into account the permutation aspect of these problems. With taking into account this aspect, it is possible to significantly improve B&B algorithms. Therefore, the remainder of this manuscript focuses primarily on PB&B. In other words, our manuscript focuses on solving permutation problems using B&B algorithms.

In addition to this introduction and a conclusion, this chapter is divided into three sections. In Section 3.2 and Section 3.3, a background is given on respectively permutation problems and the conventional PB&B algorithm based on linked-list. Finally, Section 3.4 gives a state of the art of B&B algorithms.

# 3.2 Permutation problems

This section presents a brief background on permutations focusing on the flowshop problem considered as a test case to validate our approaches.

#### 3.2.1 Permutations

Let's assume a permutation problem where the objective is to find the best permutation in a set of N elements. These elements can be jobs, cities, locations, and so on. It is always possible to assign a number to each of these N elements. The first element can be designated by 1, the second element by 2, ..., and the last by N. Therefore, any permutation problem of N elements can be represented as a permutation problem of the first N positive natural numbers.

A permutation is obtained after the assignment of numbers to positions. Before making this assignment, all numbers are free and the positions are empty. At the end of the assignment, all numbers are assigned and positions are occupied. During the assignment, some numbers are free, others assigned, some positions are occupied and others empty. In the rest of the manuscript, a number can be said free or assigned, and a position can be said occupied or free.

After the assignment of all numbers to all positions, the permutation is called complete. For example, (2,3,1,4) is a complete permutation where the numbers 2, 3, 1 and 4 are respectively assigned to positions 1,2, 3 and 4. Before starting the assignment, the permutation is said to be empty. For example,  $\{1,2,3,4\}$  is an empty permutation where

all numbers are free and all positions are empty. During an assignment, the permutation is said to be partial. For example,  $(2,3,\{1,4\})$  is a partial permutation, where numbers 2 and 3 are assigned, numbers 1 and 4 are free, positions 1 and 2 are occupied, and positions 3 and 4 are free. A partial permutation can also have the form  $(2,\{1,4\},3)$ . In this example, positions 1 and 4 are occupied and the other positions are empty.

Among the empty positions, it is possible to specify the first, the second, ... and the last empty position. For example, in  $(2, \{1, 4\}, 3)$ , the first empty position is 2 and the last empty position is 3. Among the assigned numbers, it is possible to specify also the first, the second, ... and the last number assigned. For example, in  $(2, \{3, 1, 4\})$ , the last number assigned is 2. On the other hand, looking at the  $(2, \{1, 4\}, 3)$ , it is not possible to find the first and the last number assigned. This manuscript defines the size of a permutation as the number of free numbers or empty positions. For example, the permutations  $(2, \{1, 4\}, 3), \{1, 2, 3, 4\}$  and (2, 3, 1, 4) respectively have as sizes 2, 4 and 0.

Any permutation, whether empty, partial or complete, contains a certain set of complete permutations. For example, the partial permutation  $(2, \{1, 4\}, 3)$  contains the two permutations (2, 1, 4, 3) and (2, 4, 1, 3). The empty permutation  $\{1, 2, 3, 4\}$  contains all 4! possible permutations. In the same way, the complete permutation (2, 3, 1, 4) contains only one complete permutation. **The space of a permutation** P, denoted Space(P), is defined as the set of the complete permutations contained in P.

## 3.2.2 Flowshop problem

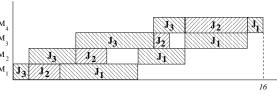

The four approaches presented in this document are validated using the flowshop problem. In manufacturing environments, it is common to find permutation flowshop scheduling problems [BG76, KS80, AGA99] where n jobs have to be processed on m machines where the goal is to optimize an objective function. The objective of the flowshop is to schedule a set of n jobs on a set of m machines where each job  $J_1$ ,  $J_2$ , ...,  $J_n$  is processed on the machines  $M_1$ ,  $M_2$ , ...,  $M_m$  organized in the line. Each job  $J_i$  with  $i=1,2,\ldots,n$  is made of a sequence of m operations  $O_{i1}$ ,  $O_{i2}$ , ...,  $O_{im}$  where operation  $O_{ik}$  is the processing of job  $J_i$  on machine  $M_k$  for a processing time  $p_{ik}$  that can not be interrupted. The objective of the flowshop is to find a processing order on each machine  $M_k$  which minimizes the time necessary to complete all jobs, also known as the makespan. In this manuscript, each reference to the flowshop is actually a reference to the permutation flowshop [AGA99, HS05]. Using Johnson's algorithm [Joh54], it is possible to find an optimal schedule for the flowshop in  $O(n \log n)$  steps when m=2. The problem is NP-hard when  $m\geq 3$  [GJS76]. This is why it is often tackled using metaheuristics [Bas05] to deal with large problem instances. Figure 3.1 shows an example of a flowshop instance where n=3 and

m=4, it also shows the optimal complete permutation.

Optimal Solution

Figure 3.1: Illustration of a permutation flowshop where n=3 and m=4. The table shows the processing times of the jobs on each machine. The Gantt diagram shows the optimal complete permutation for this particular instance.

These are the constraints that a valid flowshop complete permutation should satisfy:

- A machine can not start processing a job before the preceding machines have finished the processing of that job. In other words, machine M<sub>j</sub> can not process operation O<sub>ij</sub> before it is completed on machine M<sub>j-1</sub>.

- An operation can not be interrupted, and since a machine processes one job at a time, the machines are critical resources.

- The sequence of jobs must be the same on all machines, e.g. if job  $J_3$  is processed in second position on the first machine, job  $J_3$  must also be processed in second position on all the other machines.

The lower bound proposed by Lageweg *et al.* [LLK78] is used in our bounding operation. This bound is known for its good results and has complexity of  $O(m^2nlog(n))$ , where n is the number of jobs and m the number of machines. This lower bound is mainly based on Johnson's theorem [Joh54] which provides a procedure for finding an optimal complete permutation for a flowshop scheduling problem with 2 machines.

## 3.3 Linked-list based PB&B

This section describes the conventional PB&B algorithm based on a linked-list. As indicated by its name, the PB&B is based on two main operations, namely *branching* and *bounding*.

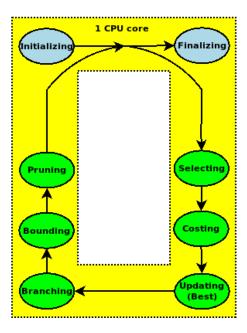

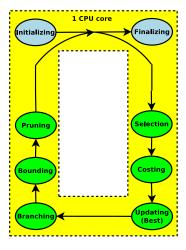

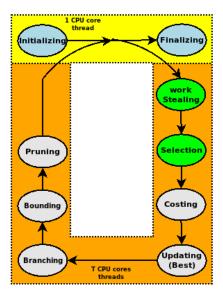

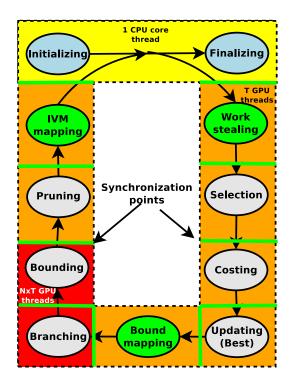

In addition to these two operations, the PB&B algorithm is defined by other operations, as shown in Figure 3.2.

Figure 3.2: The conventional PB&B algorithm and its operations.

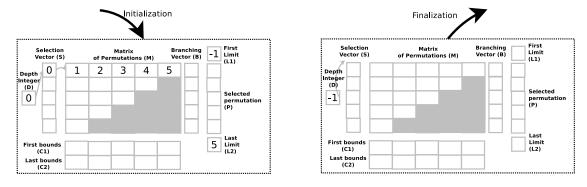

Two of the PB&B operations are called *initializing* and *finalizing* operations. The main role of the initializing operation is to allocate memory for the data structures of the algorithm, to initialize them, and to add the empty permutation to the PB&B pool. The finalizing operation is invoked when this PB&B pool is empty. Its role is to provide the decision maker by the best found permutation, and to release the allocated data structures.

Between these two operations, the PB&B algorithm runs a large number of iterations. At each iteration, the operations of selection, costing, updating, branching, bounding, and pruning always intervene in this order. The selection operation takes a permutation from the pool. Two cases may arise: in the first case, the selected permutation is complete, and in the second case, the permutation is empty or partial.

If the first case occurs, then the costing operation calculates the cost of the permutation. If the calculated cost improves the cost of the best known complete permutation, then the updating operation saves this complete permutation as the new best known complete permutation. In the second case, costing and updating operations are not used. On the other hand, the operations of branching, bounding and pruning intervene. The role of the branching operation is to divide the selected permutation into several permutations. The bounding operation calculates the bound of each of the obtained permutations, and the pruning operation removes a certain number of permutations and puts into the pool the

un-deleted permutations. Each of the following subsections presents in more details one of the main operations of the conventional PB&B.

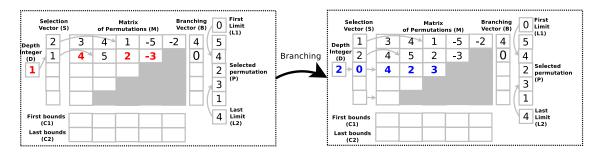

# 3.3.1 Branching

The branching operation works according to the political and sociological strategy *Divide* and rule (from Latin dīvide et imperā). The idea here is to divide a partial permutation P into a set of E sub-permutations. Of course, there are different ways to divide the same permutations P and, for each division, a different set of E of sub-permutations can be obtained. For example, the permutation  $(1, \{2, 3, 4\})$  can be divided into two different ways:

•

$$E_1 = \{(1, 2, \{3, 4\}), (1, 3, \{2, 4\}), (1, 4, \{2, 3\})\}.$$

•

$$E_2 = \{(1, \{3, 4\}, 2), (1, \{2, 4\}, 3), (1, \{2, 3\}, 4)\}.$$

The two divisions are made by filling respectively the first and last empty positions, using one of the three free numbers. In our work, we use only the first free and last positions. However, from a theoretical point of view, it is also possible to use the other empty positions, such as the second empty position, the third position, etc. The branching operation can use any division of a permutation P in a permutation set  $P_1, P_2, ..., P_n$  that meets both of the following conditions:

- $\forall (P_i, P_j), \; Space(P_i) \cap Space(P_j) = \emptyset$ . This first condition indicates that the sub-permutations of P must be disjoint.

- $Space(P) = \bigcup_{i=1}^{i=n} Space(P_i)$ . This second condition is that the permutation space P equals the union of all sub-permutation spaces of P.

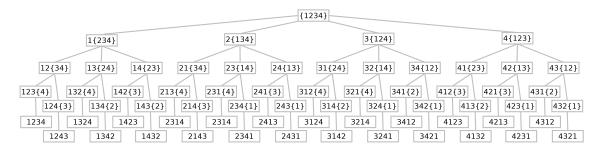

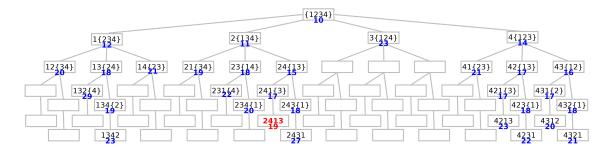

The same permutation P can not be split simultaneously with different techniques. For example, P can not be split using both first and last free positions simultaneously. However, it is possible to use a certain technique of division of the permutation P, and another division technique to divide one of the sub-permutations of P. Therefore, it is possible to use a single division technique, but it is also possible to combine several techniques in the same PB&B algorithm. The example, Figure 3.3 shows the result of a complete division from an empty permutation of size 4. In this example, the division technique used is the one that is based on the first empty position.

Figure 3.3: Example of a complete branching tree using the first empty position division technique.

A PB&B always starts with the division of the empty permutation of size N. The division of this empty permutation produces N partial sub-permutations of size (N-1). The division of each of these partial sub-permutations produces (N-2) sub-sub-permutations of size (N-2). This process continues until the obtained permutations are complete and have size 0. These successive divisions make it possible to define a tree, called branching tree, where the empty permutation is the root of the tree, the complete permutations are the leaves of the tree, and partial permutations constitute the internal nodes of the tree.

The branching tree obtained is constituted of 1 empty permutation, N partial permutations of size N, N(N-1) partial permutations of size (N-1), N(N-1)(N-2) partial permutations of size (N-2), ..., and finally, N! complete permutations. As the size of this tree is exponential, it is impossible to explore, in a reasonable time, all permutations when N exceeds a certain threshold value.

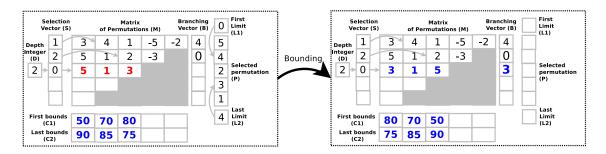

#### 3.3.2 Bounding

To avoid exploring the entire branching tree, the PB&B algorithm uses another operation called the bounding. This operation receives a permutation, as input, and returns a cost, as output. If it is a minimization problem (i.e searching a permutation of minimal cost), then the bounding operation returns a lower bound. On the other hand, if it is a maximization problem, then this operation returns an upper bound. In the remainder of the manuscript, a problem of minimization is considered, but the proposed approaches are also valid for maximization problems.

As explained previously, the space of a partial permutation P, denoted Space(P), is equal to the set of complete permutations contained in P. For example, the permutation space of  $(1,\{2,3\},4)$  includes the permutations (1,2,3,4) and (1,3,2,4). If a bounding operation receives as input the partial permutation  $(1,\{2,3\},4)$ , then this operation should return a value Bounding(P) such that the costs of (1,2,3,4) and (1,3,2,4) must be greater than Bounding(P). In the general case, the following condition must always be satisfied.

•  $\forall P' \in Space(P), Bounding(P) \leq Costing(P')$

For a permutation P, the higher the value of Bounding(P) is, the better the bounding operation which is used. Let P' be the complete permutation with the minimal possible cost in Space(P). The best bounding operation is the one that returns a value of Bounding(P) equals Costing(P'). In addition to the values of Bounding(P), bounding operations can also be compared according to their computation times. The faster a bounding operation is, the better is this operation. If a permutation P is complete, this manuscript assumes that Bounding(P) is always equal to Costing(P).

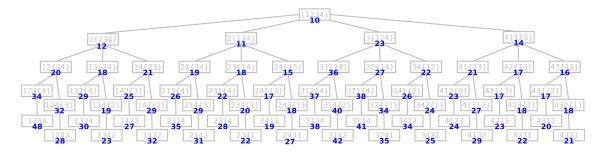

Figure 3.4: Example of a bounding tree with bound values of each node.

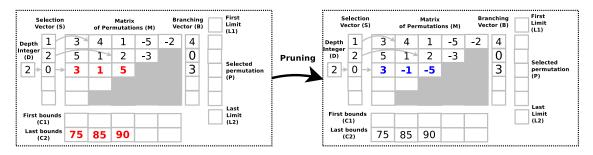

#### 3.3.3 Pruning

Subsection 3.3.1 shows that the branching tree is very large. To find the permutation with minimum cost, it is impossible to explore the entire tree for large problem instances. By knowing the lower bound of each partial permutation, it is possible to avoid exploring a large part of this tree. Let's assume that the algorithm knows a complete permutation P, which has a cost equal to Costing(P), and that this algorithm encounters a partial permutation P', which has a lower bound equal to Bounding(P'). In other words, all complete permutations in Space(P') have a cost greater than Bounding(P'). If Costing(P) is less than Bounding(P'), then there is no complete permutation of Space(P') that can have a better cost than P. Therefore, it is unnecessary to further divide the partial permutation P'. This permutation P' can be ignored and pruned from the branching tree. The pruning operation receives a cost Costing(P) of complete permutation P and the lower bound Bounding(P') of a partial permutation P' and returns a boolean value indicating whether P' should be branched or pruned. Figure 3.5 gives an example of the bounded part of a branching tree. The bounded part of a tree is composed by all the nodes of the tree where the bounds are computed.

Figure 3.5: An example of the bounded part of a branching tree

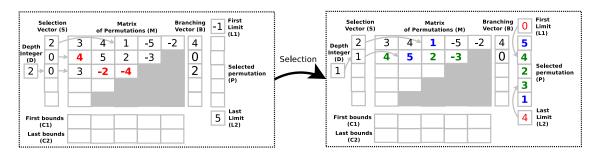

#### 3.3.4 Selection

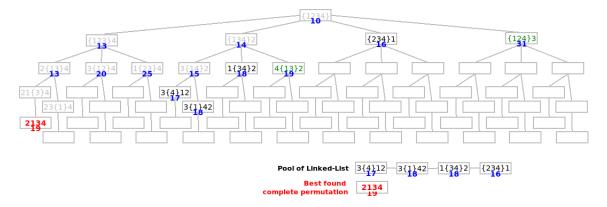

The role of the selection operation is to determine the order in which the permutations of the tree are explored. In other words, its role is always to choose the next permutation, of the pool, coded using a linked-list, to branch. In a PB&B, there are three main strategies for selecting the next permutation of the pool to be branched.

- **Best first:** The permutation of the pool having the smallest bound is chosen first. The advantage of this strategy is to increase the probability of finding more quickly a complete permutation of minimum cost. But its disadvantage is that the number of permutations of the pool increases rapidly.

- Largest first: This strategy selects the permutation of the pool with the largest size. In other words, it first selects the permutation close to the root of the branching tree. This strategy makes it possible to considerably increase the number of permutations of the pool. In parallel computing, the advantage of this strategy is to generate a pool large enough to occupy lot of computing units.

- **Depth first:** This strategy selects the permutation with the smallest size. In other words, it first selects the furthest permutation from the root of the branching tree.

In our four PB&B approaches, the strategy used is a combination of depth and best first strategies. As already explained, a permutation is defined by its size, its bound and its last assigned number. These concepts of the last assigned number and the size of a permutation are explained in Subsection 3.2.1. Using these three values, the selection operation in our PB&B approaches combines depth and best first strategies. More exactly, the Selection operation (1) receives a permutation pool as input, (2) makes sure this pool is not empty, (3) determines the largest size S of all the permutations of the pool, (4) selects the set E of the permutations of the pool having this size S, (5) determines the best bound E of all the permutations of E, (6) selects the subset E' of all the permutations

of E having the bound B, (7) selects the permutation P having the lowest last number assigned, (8) removes this permutation P from the pool, and (9) returns the permutation P as the output of this Selection operation.

Figure 3.6: Example of the best found complete permutation and the content of the pool, coded using a linked-list, when using the depth best first strategy.

For example, Figure 3.6 shows the PB&B tree during its construction and exploration. All the empty nodes of the tree are not explored, the gray permutations are already branched, the green permutations are pruned because of their bounds, the red complete permutation is the one having the minimal cost so far, and black permutations are neither pruned nor branched. In this tree, it is useless to keep in the memory the gray and green permutations. The only permutations that must be kept are those in black and red. Non-branched and non-pruned permutations are generally kept in a data structure called a linked-list, and the best complete permutation found so far can be kept in an array.

## 3.4 Related works

The related works of this section is already published in the thesis of Jan Gmys [Gmy17]. The design of parallel B&B algorithms is strongly influenced by the target architecture and the characteristics of the problem being solved [BHP05]. Therefore, and in spite of the simple and generic formulation of B&B, a large number of parallel algorithms have been proposed for different problems and architectures. [GC94] provides a complete, but over twenty year old survey of parallel B&B.

#### 3.4.1 Parallel CPU B&B

Because of the simple basic formulation of B&B it is interesting to have a framework that allows users to easily customize B&B to solve their problems. Many software frameworks

3.4. Related works

have been proposed, including Bobpp [Men17, Bob], PEBBL [EHP15] and PICO [EPH01], parts of the ACRO project [ACR], ALPS/BiCePS [RLS04], BCP and SYMPHONY, which are parts of the COIN-OR project [CO].

This list includes only those frameworks which appear to be maintained at the time of writing. B&B frameworks establish an interface between the user and the parallel machine by defining abstract types for search tree nodes and solutions. As a user, one provides concrete implementations of these types as well as branching and bounding procedures, while the framework handles more generic parts of parallel B&B. The mentioned frameworks differ by the variant(s) of B&B they provide, the type of parallel model they propose and the parallel programming environment. They are implemented with these frameworks are usually designed as multi-layered class libraries, integrating additional features by building on top of existing layers. For example, BiCePS is built on top of ALPS to provide data handling capabilities required for implementing relaxation-based B&B, and PEBBL began its existence as the "core" layer of the parallel mixed integer programming (MIP) solver PICO.

The older versions of these frameworks are often based on master-worker approaches. In order to avoid that the master processor becomes a bottleneck, hierarchical organizations revealed more efficient than pure master-worker implementations [EHP15, Men17, BMT12b]. In these approaches groups of workers form clusters, cooperating locally and interacting with the master through a form of middle management. The idea is to improve locality and relieve the master process by introducing hubs, each handling several workers (master-hub-worker approach). In general, the role of hubs consists in providing work units to a set of workers and coordinating the search process locally, while limiting interaction with the master and worker processes. For the PEBBL framework near-linear speedups on over 6 000 CPU cores are obtained for large B&B trees and node evaluation costs of about 10 seconds [EHP15].

Recently, [HSH $^+$ 17] compared three implementations of a global optimization (GO) B&B algorithm using different levels of abstraction: the Bobpp framework, Intel Thread Building Blocks and a custom P-thread implementation. While they find the Bobpp implementation easiest to code, the authors show that the two other solutions offer better scalability for the used test case. For the optimized test functions, the authors report node processing rates of about 1 million nodes per second (Mn/s) for the sequential version of their custom implementation on a 2 GHz Sandy Bridge CPU.

[EPS09b] presents a software platform called BNB-Solver, allowing the use of serial, shared memory and distributed memory B&B. The proposed approach uses a global work pool and local work pools for each thread. Each thread stores generated nodes in its local pool during N B&B iterations. After N iterations a part of the local nodes are transferred

to the global pool. When the local pool of a thread is empty, the thread attempts to take nodes from the global pool and blocks if the global pool is empty. The algorithm terminates when the global pool is empty and all threads are blocked. The authors compare the performance of BNB-Solver with the ALPS and PEBBL frameworks and obtain results similar to [HSH $^+$ 17], in the sense that, for a knapsack problem (with a reported sequential node processing rate in the order of  $1 \,\mathrm{Mn/s}$ ) BNB-Solver outperforms both frameworks.

[CMGH08] proposes two schemes for parallelizing B&B algorithms for global optimization on shared memory multi-core systems, Global and Local PAMIGO (Parallel advanced multidimensional interval analysis global optimization). Both algorithms are parallelized using POSIX threads. In Global PAMIGO, threads share a global work pool and therefore a synchronization mechanism is used for mutually exclusive accesses to the pool. For Local PAMIGO, where thread has its own pool of nodes, a dynamic load balancing mechanism is implemented. A thread stops when its local pool of nodes is empty. When the number of running threads is less than the number of available cores, and a thread has more than one node in its local pool it creates a new thread and transfers a portion of its pool to the new thread. Local PAMIGO ends when there exists no more running threads, and Global PAMIGO ends when the global pool is empty. The authors report profiling results for PAMIGO which show that memory management represents a large percentage of the computational burden. As a very large number of nodes are created in a relatively short amount of time, the kernel needs to satisfy memory allocation and deallocation requests from all threads, creating memory contention. The vast majority of parallel B&B algorithms in the literature store nodes in one or several pool(s) implemented as linked-lists (e.g. priority queues, stacks, deques).

#### 3.4.2 Parallel GPU B&B

The study of [JAO<sup>+</sup>11] provides a good overview of the challenges faced when implementing parallel backtracking on GPUs. Most of their conclusions from the investigation of GPU-based backtracking paradigm remain valid for B&B algorithm using a depth first search strategy. A fine-grained parallelization of the search space exploration and/or the node evaluation is necessary in order to make use of the GPU's massive parallel processing capabilities. This strongly depends on the nature of the problem being solved and on the choice of the parallelization model. Other critical factors include latency hiding through coalescence, saturation, and shared memory utilization [JAO<sup>+</sup>11]. Generally speaking, the algorithmic properties of B&B, irregularity of the search space, irregular control flow and memory access patterns are at odds with the GPU programming model. Also, memory requirements for backtracking and B&B algorithms are often difficult to estimate and may

3.4. Related works

exceed the amount of memory available on GPUs. Several approaches for GPU-accelerated B&B algorithms have been proposed. These approaches correspond to different parallelization models and their design is often motivated by the nature of the problem being solved. According to the characteristics of the bounding function one may distinguish among approaches for fine-, medium- and coarse-grained problems.

The GPU B&B and backtracking algorithms for fine-grained problems proposed in [CMNLdC11, CNNdC12, FRvLP10, LLW+15, RS10, ZSW11] perform massively parallel searches on the GPU, based on the parallel tree exploration model. The evaluation of a node for the n-Queens problem in [FRvLP10, LLW+15, ZSW11] requires only a few registers of memory and only a couple of bit operations. The lower bound for the Asymmetric Traveling Salesman Problem (ATSP) used in [CMNLdC11, CNNdC12] is incrementally obtained by adding the cost of the last visited edge to the current cost and therefore has a complexity of  $\mathcal{O}(1)$ . It requires an access to the distance matrix which can be stored in constant or texture memory. The size of the problems being solved is < 20 for both the ATSP and the n-Queens problems. These algorithms for fine-grained problems share a common approach: the search is split in two parts, an initial CPU search and a final GPU search. The upper tree of depth  $d_{cutoff}$  is processed in sequential or weakly parallel manner on CPU, generating a set of active nodes at depth  $d_{cutoff}$ . This active set is sent to the GPU, where the lower part of the tree is processed in parallel. Each node of the active set is used as root node for an independent search, which is mapped either to a thread or a warp. This approach requires very careful tuning of the cutoff depth, which strongly influences granularity and load balancing.

Because of varying thread granularities, one of the major issues faced by such approaches is load imbalance. In all of these works the GPU search is performed without dynamic load balancing. However, as noted by [RS10], if "a job is divided into sufficiently many parts, an idle processor will be instantly fed with waiting jobs" and the "GPU's Thread Execution Manager performs that task automatically". This approach assumes two things: first, the initial CPU search is able to generate a large amount of nodes in a reasonable amount of time, and second, the work distribution among independent B&B searches is not *too* irregular.

For many combinatorial optimization problems the cost of the bounding operation is very high, compared to the rest of the algorithm. For instance, the most used lower bounding function for the flowshop consumes 97-99% of the sequential execution time [MCB14]. However, the cost of evaluating one node is sufficiently small to be efficiently performed by a single GPU thread. We therefore refer to this type of problem as medium-grained. For these problems, existing GPU-accelerated B&B algorithms in the literature use the GPU to evaluate large pools of nodes in parallel [CMMB13, VDM13, LEB12]. They use

conventional stacks or queues to store and manage the B&B tree on the host, offloading the parallel evaluation of bounds to the device. Indeed, for these problems substantial speedups can be achieved despite sequentially performing pool management on the host. Substantial efforts have been made to port larger portions of the algorithm to the GPU and to reduce overheads incurred by data transfers between CPU and GPU. For instance, branching nodes on the device allows to copy only parent nodes to the GPU. Similarly, pruning evaluated nodes on the device reduces the sequential portion and requires only the transfer of non-pruned children nodes back to the host. Further performance improvements can be obtained by overlapping data transfers with GPU computations, as for example in [VDM13]. For fine-grained problems this approach is likely to perform poorly.

For coarse-grained problems the best way to use the GPU may be as an accelerator for the bounding function itself. In [ABEB+16] a GPU-accelerated B&B algorithm for the jobshop scheduling problem is proposed. The approach also offloads nodes to the GPU but uses a block-based parallelization for each node evaluation. The number of nodes that need to be offloaded in order to saturate the GPU is therefore smaller than for medium-grained problems. A GPU-accelerated algorithm for problems with linear programming bounds is proposed in [MCA13]. Using a GPU-based LP-solver to accelerate this type of problems is very challenging. However, the authors report that for large problems above a certain density threshold their hybrid GPU-accelerated solver outperforms the sequential CLP solver of the open-source COIN-OR library.

#### 3.4.3 Cluster B&B

There are very few works on the parallelization of B&B using multiple GPUs and CPUs in distributed heterogeneous systems. In [VDM13] a linked-list based fully distributed hybrid B&B algorithm combining multiple GPUs and CPUs is proposed. As a test case 20 jobs-on-20 machines flowshop instances are considered in their experiments using a platform composed of 20 GPUs and 128 CPUs. For load balancing a random work stealing mechanism is used. The authors propose an adaptive granularity policy to adapt the amount of stolen nodes at runtime to the normalized computing power of thief and victim. The algorithm is based on a 2-level parallel model, using GPUs for parallel evaluation of lower bounds. In order to reduce CPU-GPU communication overhead, an asynchronous implementation with overlapping host and device computations is proposed. Experimentally, near-linear mixed scalability is shown up to 20 GPUs and 128 CPUs. In [CMMT13] the combined usage of multi-core and GPU processing is investigated. An experimental comparison of concurrent and cooperative approaches shows that the cooperative approach improves the performance with respect to a GPU-only approach while the concurrent approach is not

3.5. Conclusions 29

beneficial. Among other issues, the authors identify the reduction of CPU-GPU communication overhead as a major challenge and propose overlapping communication schemes and auto tuning of the offloaded pool sizes to answer this challenge.

Some of the largest known exact resolutions of combinatorial optimization problems have been performed using the master-worker paradigm in combination with grid computing technologies (e. g. *nug30* [ABGL02]). The B&B@Grid platform [MMT07c] uses an interval encoding for work units which significantly reduces the size of messages communicated in distributed B&B. Designed for volatile computing environments, B&B@Grid is fault tolerant thanks to its checkpointing mechanism.

In [BMT12a] an adaptive multi layer hierarchical master-worker approach is applied to the B&B algorithm, using flowshop as a test case. The proposed approach evolves as new resources join the computation, and integrates three types of processes, a super master, masters and workers. Results obtained at the scale of up to 2000 CPUs show that the multi-layered hierarchical approach clearly outperforms single-layered and classical master-worker approach in terms of efficiency for instances smaller than *Ta056*, as it minimizes bottlenecks at the level of the master and reduces idle time of the workers. In [BMT14] the authors extend their approach, proposing a fault tolerance mechanism.

#### 3.5 Conclusions