# Modélisation de transistors en couches minces (TFT) fabriqués en technologies silicium microcristallin très basse température

Mamadou Lamine Samb

### ▶ To cite this version:

Mamadou Lamine Samb. Modélisation de transistors en couches minces (TFT) fabriqués en technologies silicium microcristallin très basse température. Micro et nanotechnologies/Microélectronique. Université de Rennes 1, 2014. Français. NNT: . tel-02441294

# HAL Id: tel-02441294 https://hal.science/tel-02441294

Submitted on 20 Jan 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE / UNIVERSITÉ DE RENNES 1**

sous le sceau de l'Université Européenne de Bretagne

En Cotutelle Internationale avec UNIVERSITÉ CHEIKH ANTA DIOP DE DAKAR (UCAD), SÉNÉGAL

pour le grade de

# **DOCTEUR DE L'UNIVERSITÉ DE RENNES 1**

Mention: (Electronique)

**Ecole doctorale (MATISSE)**

présentée par

# **Mamadou Lamine SAMB**

préparée à l'unité de recherche UMR CNRS 6164 Institut d'Electronique et de Télécommunication de Rennes UFR Informatique - Electronique

Intitulé de la thèse :

Modélisation de

transistors en couches

minces (TFT) fabriqués

en technologies

silicium microcristallin

très basse température

### Thèse soutenue à l'UCAD de Dakar le 08 Décembre 2014

devant le jury composé de :

### Amadou Seidou MAÏGA

Professeur, Université Gaston Berger de Saint Louis / rapporteur

### François TEMPLIER

Ingénieur HDR, CEA LETI / rapporteur

### **Emmanuel JACQUES**

Maître de Conférences, Université de Rennes 1 / examinateur

#### Cheikh SENE

Professeur, Université Cheikh Anta Diop de Dakar / examinateur

### **Tayeb MOHAMMED-BRAHIM**

Professeur, Université de Rennes 1 / co-directeur de thèse

### **Grégoire SISSOKO**

Professeur, Université Cheikh Anta Diop de Dakar / co-directeur de thèse

# Dédicaces

Je dédie ce travail à mon père Papa Ibra SAMB et ma mère Oumoukhayri FALL qui n'ont ménagé aucun effort pour la réussite de toutes mes entreprises

Je dédie aussi cet ouvrage à :

Ma Femme Fatoumata Diagne DIAMANKA

Mon Fils Papa Ibrahima SAMB

Mes Frères et Sœurs

Mes Tantes

Mes Oncles

Mes Cousins et Cousines

Mes Neveux et Nièces

Mes Ami(e)s

Monsieur Mbor TOURE

Monsieur Pathé SY

Madame DIOP née Ndeye Fatou NDAO

Monsieur Mbor TOURE et madame TOURE née Awa BA

Tous (tes) ceux (celles) qui, de près ou de loin, m'ont soutenu tout au long de mon cursus élémentaire jusqu'au cursus universitaire.

### Remerciements

# Remerciements

Ce travail a été effectué entre:

le Département de Microélectronique et Microcapteur (DMM) de l'Institut d'Electronique et de Télécommunication (IETR) de l'Université de Rennes 1

et

Le Laboratoire des Semi-conducteurs et d'Energie Solaire (LASES) de la Faculté des Sciences et Techniques (FST), de L'Université Cheikh Anta DIOP de Dakar (Sénégal)

Sous la codirection respective de :

Monsieur **Tayeb MOHAMMED-BRAHIM** Professeur à l'université de Rennes 1

et de

Monsieur **Grégoire SISSOKO** Professeur à l'Université Cheikh

Anta DIOP de Dakar.

Je tiens à les remercier très vivement pour avoir codirigé cette thèse avec beaucoup de sollicitude. Tout au long de ce travail, leur confiance et soutien ne m'ont jamais fait défaut. Ils sont pour moi plus que des encadreurs, leurs conseils et remarques durant ces années de thèse ont fortement contribué à la réalisation de ce travail

### Remerciements

et sa finalisation. Qu'il me soit permis de leur témoigner ma profonde gratitude.

J'adresse également mes remerciements à Monsieur Amadou Seidou MAÏGA, Professeur à l'UFR-SAT de l'UGB de Saint Louis et à Monsieur François TEMPLIER, Ingénieur HDR, CEA LETI de Grenoble pour avoir spontanément accepté d'être les rapporteurs de cette thèse ainsi que des membres du jury.

C'est le lieu d'associer à ces remerciements:

- Monsieur **Emmanuel Jacques**, Maître de conférences à l'université de Rennes 1 pour avoir suivi de près ce travail et pour m'avoir fait l'honneur de participer à ce jury de thèse.

- Monsieur Cheikh SENE, Professeur à l'université Cheikh Anta Diop de Dakar pour m'avoir fait l'honneur de participer à ce jury de thèse.

C'est l'occasion aussi de nous souvenir que durant ces années nous avons eu le soutien constant et précieux de nos collègues avec à leur tête notre Directeur, le professeur Mamadou SARR, véritable père de famille qui nous ont facilité la conduite de ce travail avec

### Remerciements

tous les aménagements d'emploi du temps et de travail pour effectuer mes différents séjours à l'étranger. Je ne saurais les remercier en y associant tous les membres du personnel administratif, technique et de service

Bien entendu, je ne saurais oublier de dire merci à tous les membres (permanents, thésards vacataires ou stagiaires et docteurs):

- du département Microélectronique et Microcapteurs de l'IETR et

- du Laboratoire de Semi-conducteurs et d'Energie Solaire. Ce fût un immense honneur pour moi de les avoir côtoyé durant ces années de thèse.

Cette thèse n'a pu être réalisée que grâce au financement accordé par le Service de Coopération et d'Action Culturelle (SCAC) de l'Ambassade de France ainsi que les soutiens multiformes des université de Dakar (UCAD), de Thiès (UT) et de Rennes 1. Que leurs autorités, des Recteurs aux Directeurs, ainsi que leurs collaborateurs (trices) trouvent ici l'expression de nos remerciements déférents.

# Sommaire

## Sommaire

| Liste des illustrations                                                               | IV   |

|---------------------------------------------------------------------------------------|------|

| Liste des figures                                                                     | IV   |

| Liste des tableaux                                                                    | VIJ  |

| Glossaire                                                                             | VIII |

| Introduction générale                                                                 | 1    |

| Chapitre I : Etat de l'art et problématique                                           | 5    |

| I.1 Introduction                                                                      | 6    |

| I.2 Electronique fabriquée sur un substrat                                            | 7    |

| I.2.1 Electronique pour pixels d'écrans plats                                         | 7    |

| I.2.1.1 Ecran plat LCD à matrice active (AMLCD)                                       | 8    |

| I.2.1.2 Ecran plat OLED à matrice active (AMOLED)                                     | 11   |

| I.2.2 Electronique sur un substrat pour d'autres applications                         | 13   |

| I.3 Transistors en couches minces                                                     | 15   |

| I.3.1 Structure des TFTs                                                              | 16   |

| I.3.1.1 TFT à grille en dessous (Bottom-Gate)                                         | 17   |

| I.3.1.2 TFT à grille au dessus (Top-Gate)                                             | 17   |

| I.4 Principe de fonctionnement des TFTs                                               | 18   |

| I.4.1 Etat bloquant                                                                   | 18   |

| I.4.2 Etat passant                                                                    | 19   |

| I.4.2.1 Régime saturé                                                                 | 19   |

| I.4.3 Caractérisation des TFTs                                                        | 20   |

| I.4.3.1 Caractéristiques de transfert                                                 | 20   |

| I.4.3.2 Caractéristiques de sortie                                                    | 21   |

| I.4.3.3 Tension de seuil                                                              | 22   |

| I.4.3.4 Mobilité d'effet de champ                                                     | 23   |

| I.4.3.5 Pente sous le seuil                                                           | 23   |

| I.4.3.6 Rapport I <sub>ON</sub> /I <sub>OFF</sub>                                     | 24   |

| I.5 Matériau utilisé dans la fabrication des dispositifs électroniques d'adressage de |      |

| d'écrans plats                                                                        |      |

| I.5.1 Le silicium amorphe                                                             |      |

| I.5.2 Le silicium polycristallin                                                      |      |

| I.5.2.1 Les grains                                                                    |      |

| I.5.2.2 Les joints de grains                                                          |      |

| I.5.3 Le silicium microcristallin                                                     |      |

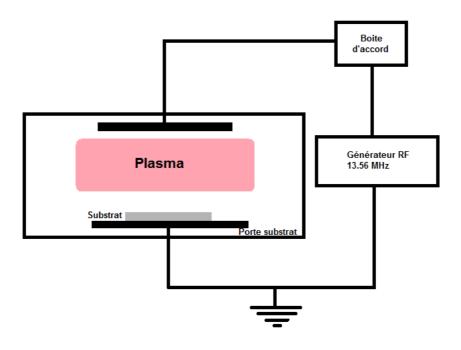

| I.5.3.1 Dépôt du silicium microcristallin par PECVD                                   |      |

| I.5.3.2 Plasma de dépôt du silicium microcristallin par PECVD                         |      |

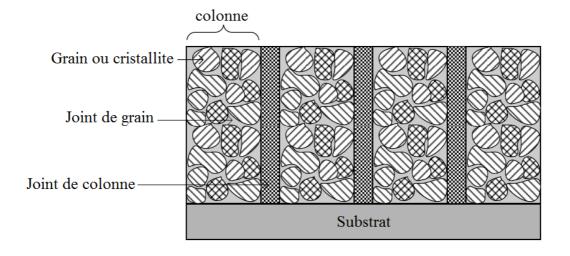

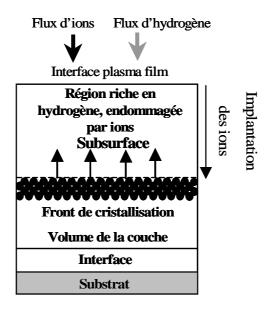

| I.5.3.3 Structure et processus de croissance du silicium microcristallin              |      |

| I.6 Effet de l'épaisseur de la couche active sur les paramètres électrique des trans  |      |

| I.7 Conclusion                                                                        |      |

| Références I                                                                          | 39   |

# Sommaire

| Chapitre II : Effet de la diminution de l'épaisseur de la couche active des TFTs à base de silicium microcristallin : étude expérimentale | 45   |

|-------------------------------------------------------------------------------------------------------------------------------------------|------|

| II.1 Introduction                                                                                                                         |      |

| II.2 Structure et procédé de fabrication des transistors                                                                                  |      |

| II.2.1 Dépôt des couches                                                                                                                  |      |

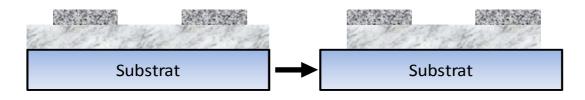

| II.2.2 Masque 1 : Définition de la couche active                                                                                          |      |

| II.2.3 Masque 2 : Isolation des transistors                                                                                               |      |

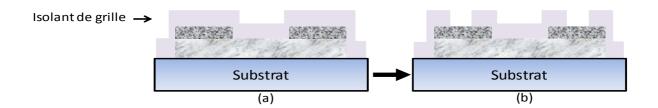

| II.2.4 Masque 3 : Ouverture des contacts drain et source dans l'isolant de grille                                                         |      |

| II.2.5 Masque 4 : Métallisation des contacts source, drain et grille                                                                      |      |

| II.3 Caractéristiques des TFTs utilisant une épaisseur habituelle de 100 nm comme couclactive.                                            | he   |

| II.3.1 Paramètres électriques                                                                                                             |      |

| II.3.1.1 Paramètres électriques à température ambiante                                                                                    |      |

| II.3.1.2 Dépendance en température des paramètres électriques                                                                             |      |

| II.3.2 Stabilité des TFTs                                                                                                                 |      |

| II.3.3 Conclusion sur les TFTs utilisant une épaisseur habituelle de 100 nm comme couche active.                                          | . 58 |

| II.4 Effet de la variation de l'épaisseur de la couche active                                                                             |      |

| II.4.1Caractéristiques de transfert de TFTs utilisant des épaisseurs différentes de couche active.                                        |      |

| II.4.2 Stabilité électrique des TFTs utilisant des épaisseurs différentes de couche active.                                               |      |

| II.4.3 Conclusion sur la comparaison expérimentale des TFTs utilisant des épaisseur                                                       |      |

| différentes de couche active.                                                                                                             | . 67 |

| II.5 Conclusion                                                                                                                           |      |

| Références II                                                                                                                             |      |

| Chapitre III : Simulation électrique des transistors en couches minces sous SILVACO                                                       |      |

| III-1 Introduction                                                                                                                        |      |

| III-2 Matériel et méthodes                                                                                                                |      |

| III-2.1 Outils de Simulation utilisés                                                                                                     |      |

| III-2.1.1 Le logiciel de simulation technologique ATHENA                                                                                  |      |

| III-2.1.2 Le Logiciel de modélisation électrique ATLAS                                                                                    |      |

| III-2.2 Méthodes                                                                                                                          |      |

| III-2.2.1 Elaboration de la structure des TFTs à simuler                                                                                  | . 77 |

| III-2.2.2 Modèle physique utilisé sous ATLAS pour la simulation des propriétés                                                            | 70   |

| électriques des TFTS                                                                                                                      |      |

| <ol> <li>L'équation de Poisson</li> <li>Les équations de continuité des porteurs</li> </ol>                                               |      |

| 1                                                                                                                                         |      |

| Les équations de transport  Modèle de transport de dérive-Diffusion                                                                       |      |

| III-2.2.3 Modèle physique du matériau silicium microcristallin utilisé pour la simulati                                                   |      |

| des propriétés électriques des TFTs                                                                                                       |      |

| III-3 Simulation électrique des transistors en couches minces en utilisant l'outil ATLAS                                                  |      |

| partir de SILVACO                                                                                                                         |      |

# Sommaire

| III-3.1 Caractéristiques des TFTs                                                                                             | 88  |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| III-3.2 Effet de la variation de l'épaisseur de la couche active                                                              | 92  |

| III-3.2.1 Effet de la variation de l'épaisseur de la couche active des TFTs en défauts électriques (silicium monocristallin)  |     |

| III-3.2.2 Effet de la variation de l'épaisseur de la couche active des TFTs co<br>défauts dans leur couche active en silicium |     |

| III-3.2.2.1 Effet sur le courant inverse                                                                                      | 96  |

| III-3.2.2.2 Effet sur la pente sous le seuil                                                                                  | 99  |

| III-3.3 Effet des interfaces isolant de grille-couche active (interface avant) et c<br>active-substrat (interface arrière)    |     |

| III-3.3.1 Effet de la variation de la densité des états profonds à l'interface aractive - substrat)                           |     |

| III-3.3.2 Effet de la variation de la densité des états profonds à l'interface avactive - isolant de grille)                  |     |

| III-4. Conclusion                                                                                                             | 111 |

| Références III                                                                                                                | 112 |

| Conclusion générale                                                                                                           | 114 |

# Liste des illustrations Liste des figures

| Figure I-1: Tétraèdre d'atomes de silicium et leur arrangement ordonné dans le silicium                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| monocristallin 6                                                                                                                                   |

| Figure I- 2 : Vue en coupe d'un écran plat [6]9                                                                                                    |

| Figure I- 3 : Principe de fonctionnement des écrans à cristaux liquides [9]                                                                        |

| Figure I- 4 : Schéma de la matrice de transistors [10]                                                                                             |

| Figure I- 5: Structure d'une OLED [13]                                                                                                             |

| Figure I- 6 : Ecran flexible utilisant une technologie OLED [15]                                                                                   |

| Figure I-7: Circuit pixel OLED à deux TFTs et une capacité (2T1C) [16]                                                                             |

| Figure I- 8 : Architecture générale d'un transistor en couches minces                                                                              |

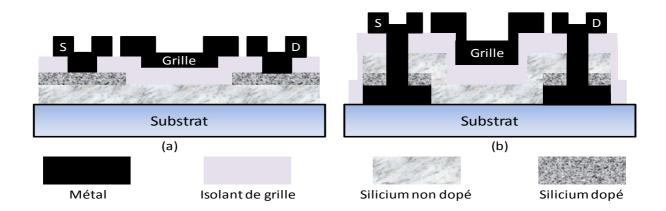

| Figure I- 9 : Structure Bottom-Gate inversée (a) et coplanaire (b)                                                                                 |

| Figure I- 10 : Structure Top-Gate coplanaire (a) et inversée (b)                                                                                   |

| Figure I- 11 : Caractéristique de transfert d'un TFT                                                                                               |

| <b>Figure I- 12 :</b> Caractéristiques de sortie d'un transistor E4 (100μm/20μm) pour plusieurs VDS                                                |

| Figure I- 13 : Caractéristique de transfert en échelle linéaire d'un TFT. La tension de seuil est                                                  |

| déduite dans ce cas d'une extrapolation de la zone linéaire                                                                                        |

| Figure I- 14: Structure cristalline et amorphe [23]                                                                                                |

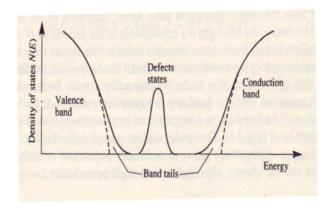

| Figure I- 15 : La distribution de la densité d'états électroniques d'un matériau amorphe [24]                                                      |

| Figure I- 16: Structure du silicium polycristallin obtenu à partir de silane à 90 Pa, 550 °C                                                       |

| recuit à 600 °C pendant 12 heures <b>[25]</b> (a) et structure du silicium polycristallin élaboré par filtrage pour application photovoltaïque (b) |

|                                                                                                                                                    |

| filtrage pour application photovoltaïque (b)                                                                                                       |

| Figure I- 17: Représentation schématique (b)                                                                                                       |

| Figure I- 17: Représentation schématique de la distribution des états introduits par les défauts dans la bande interdite du polysilicium [32]      |

| Figure I- 17: Représentation schématique de la distribution des états introduits par les défauts dans la bande interdite du polysilicium [32]      |

| Figure I- 17: Représentation schématique de la distribution des états introduits par les défauts dans la bande interdite du polysilicium [32]      |

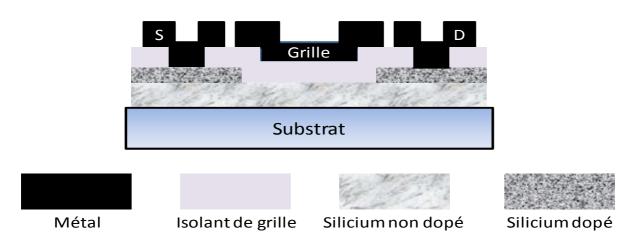

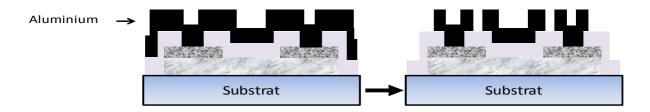

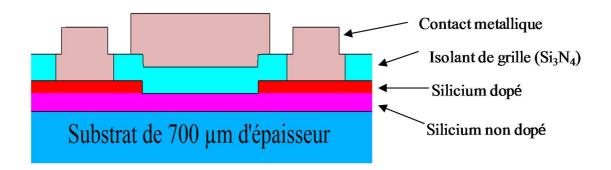

| <b>Figure II- 5 :</b> Vue en coupe de la structure finale après la définition des contacts grille, source et drain                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

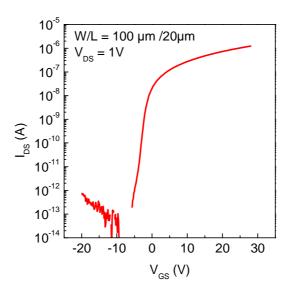

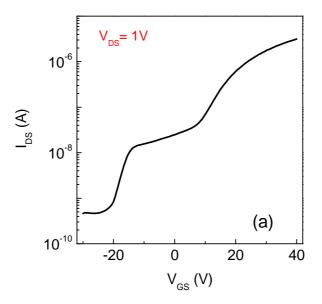

| <b>Figure II- 6</b> : Caractéristique de transfert d'un transistor (W=100 $\mu$ m/L=20 $\mu$ m) de couche active de silicium microcristallin de 100 nm d'épaisseur et une couche isolante à base de nitrure de silicium de 300 nm d'épaisseur (VDS = 1 V)                                                                                                                               |

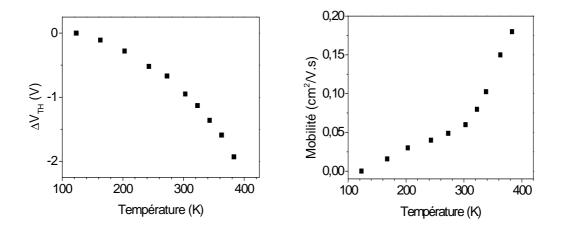

| <b>Figure II- 7 :</b> Variation de la tension de seuil et de la mobilité des transistors utilisant une couche active de 100 nm d'épaisseur                                                                                                                                                                                                                                              |

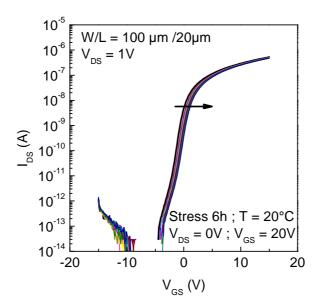

| <b>Figure II- 8 :</b> Caractéristiques de transfert pour un TFT de 100 nm de couche active $(W=100\mu m/L=20\mu m)$ mesurées à différents instants pendant l'application d'un stress de + 20V sur la grille alors que le drain et la source étaient court-circuités. La durée totale du stress est de 6 heures et la température de $20^{\circ}C$                                       |

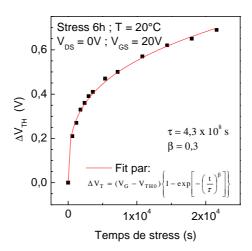

| <b>Figure II- 9 :</b> Lissage par la fonction exponentielle étendue (donnée dans la figure) de la variation de la tension de seuil des transistors en fonction du temps de stress à 20°C par une tension grille de +20V, les drain et source étant court-circuités                                                                                                                      |

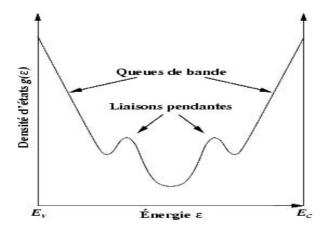

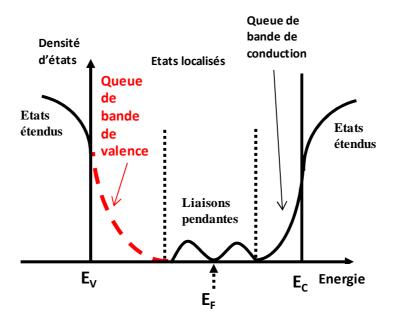

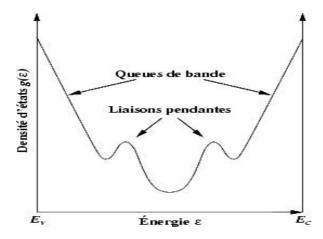

| <b>Figure II- 10 :</b> Schéma de densité d'états d'énergie dans un semi-conducteur désordonné. Des états de défauts existent dans la bande interdite entre Ev et Ec                                                                                                                                                                                                                     |

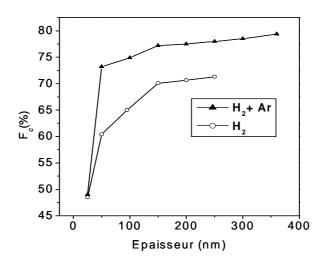

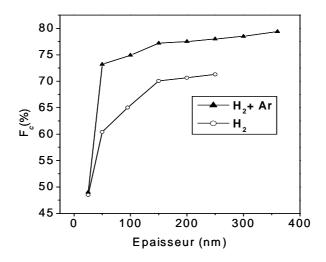

| <b>Figure II- 11 :</b> Evolution de la fraction cristalline en fonction de l'épaisseur pour des couches de $\mu$ c-Si:H déposées avec 1% de silane dans H2 pur (Cercle) et dans un mélange Ar (50%) +H2 (50%) (Triangle) [1]                                                                                                                                                            |

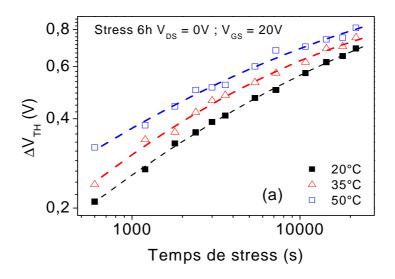

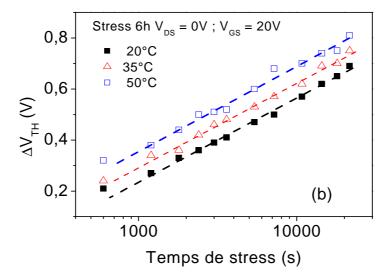

| <b>Figure II- 12 :</b> Evolution de la tension de seuil en fonction du temps de stress sous une tension de grille de +20V appliqué pendant 6 heures à 20°c, 35°C et 50°C tracée dans un graphe logarithmique (a) et semi-logarithmique (b).                                                                                                                                             |

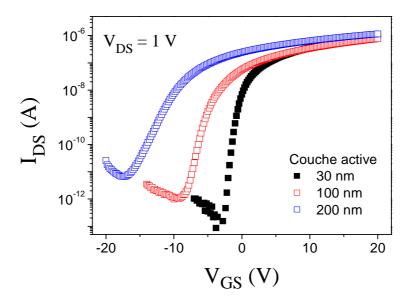

| <b>Figure II- 13 :</b> Caractéristique de transfert de transistors (W=100µm/L=20µm) et de couche active de silicium microcristallin respective de 30 nm 100 nm et 200 nm d'épaisseur et une couche de nitrure de silicium de 300 nm                                                                                                                                                     |

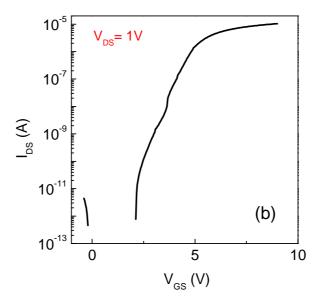

| <b>Figure II- 14 :</b> Effet de canal arrière pour un TFT bottom-gate (a) (courbe fournie aimablement par François Templier, LETI-MINATEC Grenoble) et pour un TFT top-gate fabriqué par l'IETR (b)                                                                                                                                                                                     |

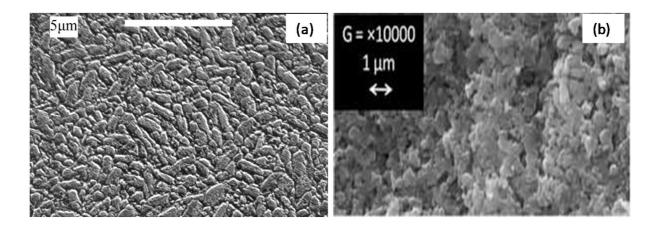

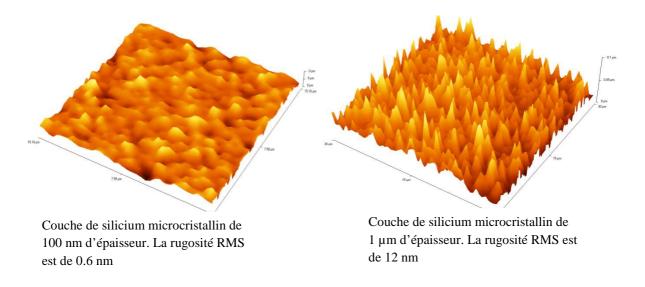

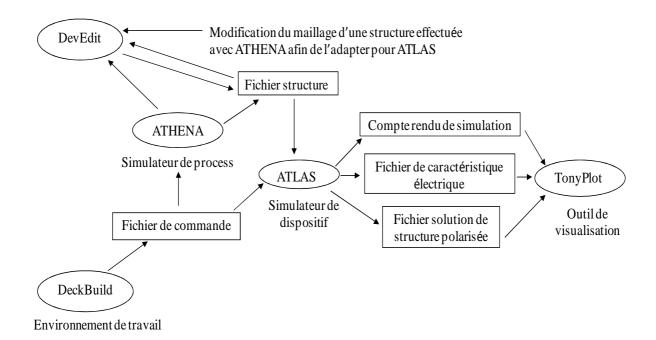

| <b>Figure II- 15 :</b> Topographie de l'état de surface du silicium microcristallin fin et épais analysé par microscopie AFM (Atomic Force Microscopy)                                                                                                                                                                                                                                  |

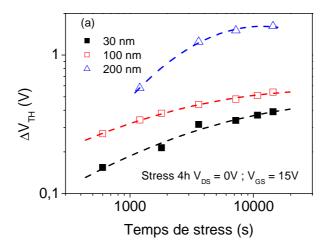

| <b>Figure II- 16 :</b> Variations des tensions de seuil des 3 types de TFTs tracées en logarithmique (a) et en semi-logarithmique (b) sous l'effet d'un stress de +15V sur la grille                                                                                                                                                                                                    |

| <b>Figure II- 17 :</b> Structure d'une couche de silicium microcristallin d'après J. Kocka [16] 66                                                                                                                                                                                                                                                                                      |

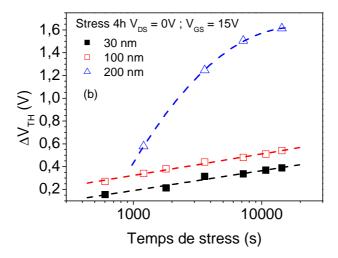

| Figure III- 1 : Schéma explicatif des différentes interactions entre les outils du pack VWF                                                                                                                                                                                                                                                                                             |

| Figure III- 2 : Structure des TFTs simulés [4]                                                                                                                                                                                                                                                                                                                                          |

| <b>Figure III- 3 :</b> Représentation schématique de la distribution des états introduits par les défauts dans la bande interdite du silicium                                                                                                                                                                                                                                           |

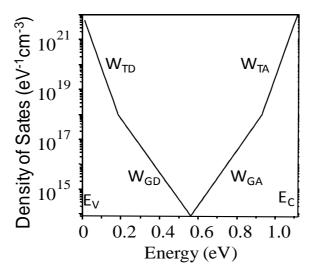

| <b>Figure III- 4 :</b> Distribution de la densité des états dans la bande interdite du silicium [4, 10]                                                                                                                                                                                                                                                                                 |

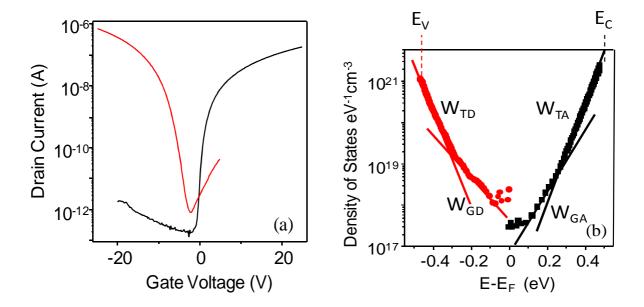

| <b>Figure III- 5 :</b> Densité d'états à l'intérieur de la bande interdite d'un film de silicium microcristallin (b), calculée à partir des caractéristiques de transfert (a) [13] des TFTS de type N et de type P fabriqué simultanément sur une couche de silicium microcristallin non dopé de 100 nm d'épaisseur. Le TFT de type N a une longueur de canal L=20 μm et une largeur de |

| canal W=20 µm. La longueur L et la largeur W du TFT de type P sont respectivement de 20 µm et 80 µm                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

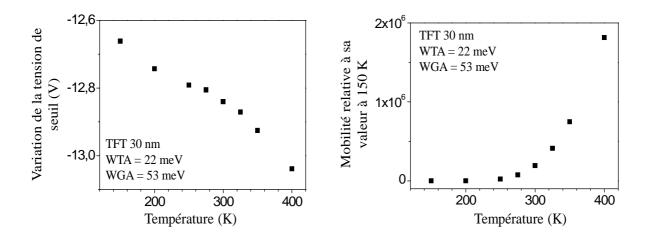

| <b>Figure III- 6 :</b> Variation de la tension de seuil et de la mobilité des transistors avec la température                                                                                                                                                                                                                                                                                |

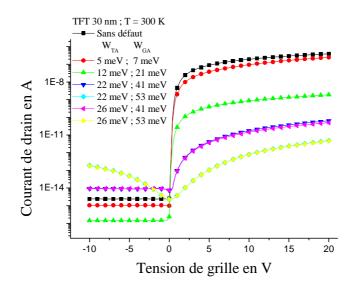

| <b>Figure III-7 :</b> Caractéristiques de transfert en échelle semi-logarithmique du TFT de 30 nm d'épaisseur de couche active à T = 300 K et pour différentes concentrations de défauts dans le canal.                                                                                                                                                                                      |

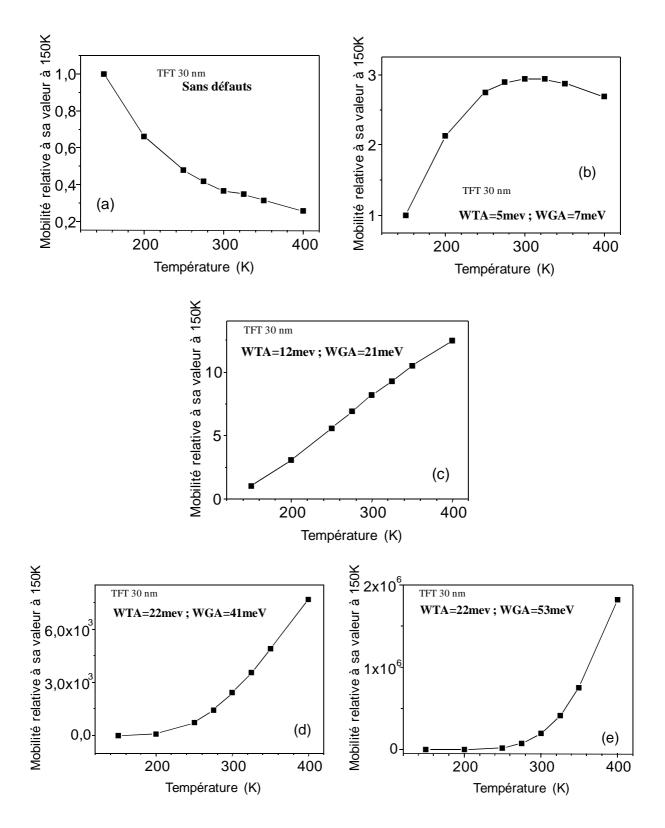

| <b>Figure III- 8 :</b> Evolution de la mobilité d'effet de champ électronique en fonction de la température pour différentes concentrations de défauts dans la moitié supérieure de la bande interdite                                                                                                                                                                                       |

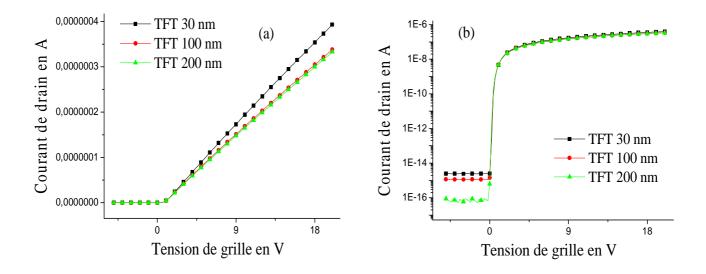

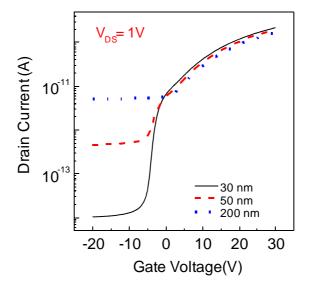

| <b>Figure III- 9 :</b> Caractéristique de transfert en linéaire (a) et semi-logarithmique (b) de transistors de 30, 100 et 200 nm d'épaisseur de couche active et dont la couche de silicium est sans défaut.                                                                                                                                                                                |

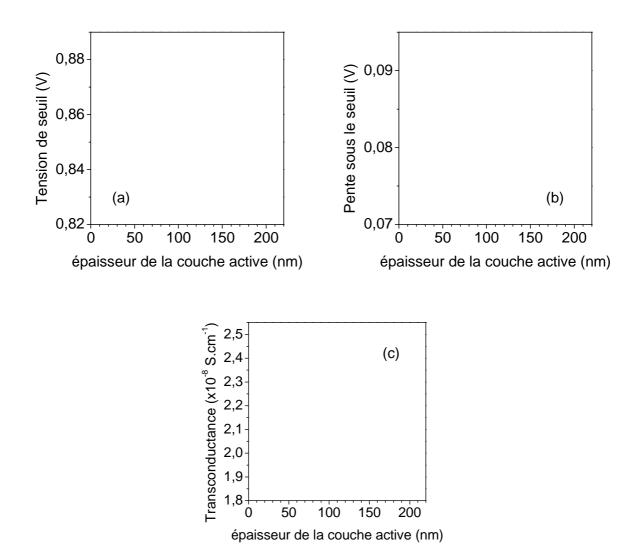

| <b>Figure III- 10 :</b> Tension de seuil (a), pente sous le seuil (b) et transconductance (c) des TFTs en fonction de l'épaisseur de la couche active. Le matériau de la couche active est considéré sans défauts                                                                                                                                                                            |

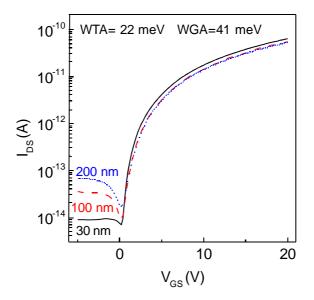

| <b>Figure III- 11 :</b> Caractéristique de transfert des transistors de 30, 100 et 200 nm d'épaisseur de couche active et dont la couche de silicium une densité de défauts caractérisée par WTA = 22 meV et WGA = 41 meV                                                                                                                                                                    |

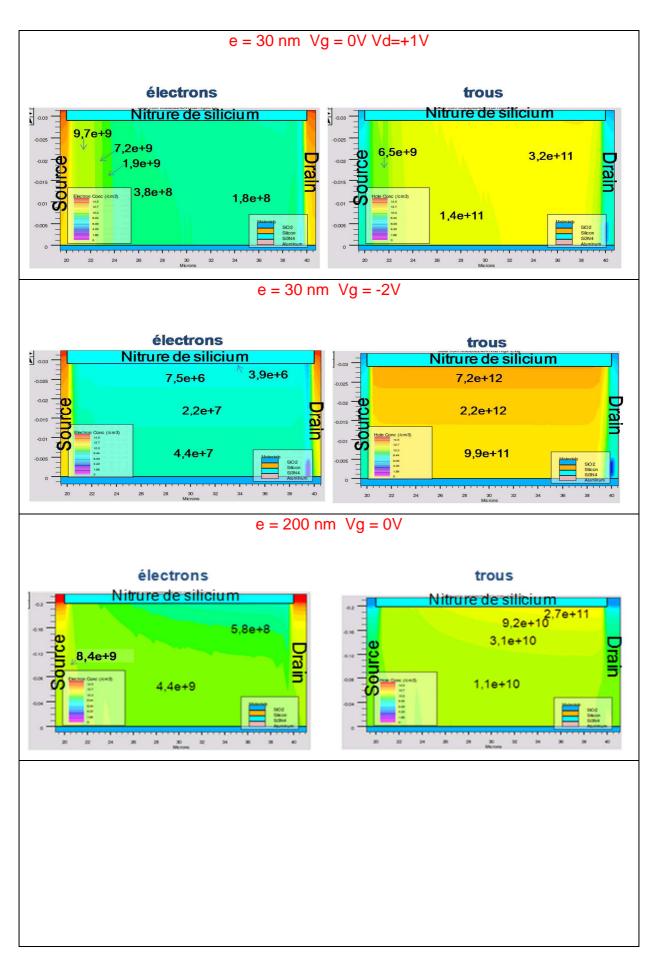

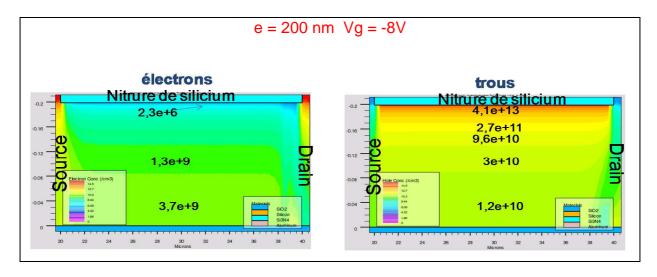

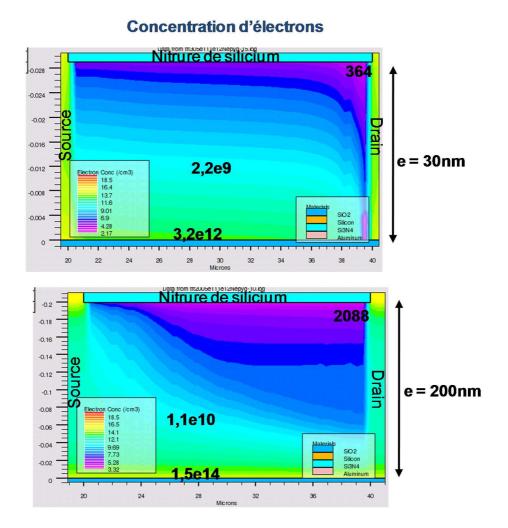

| <b>Figure III- 12 :</b> Concentrations d'électrons et de trous dans les couches actives d'épaisseurs 30nm et 200nm pour des tensions de grille de 0V (correspondant au minimum du courant de drain) et de -2V pour la couche de 30 nm et de -8V pour la couche de 100 nm (correspondant au régime en inverse des transistors)                                                                |

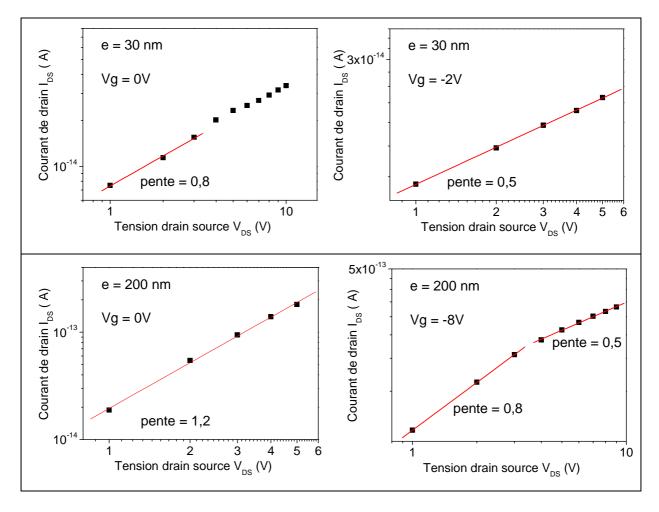

| <b>Figure III- 13 :</b> Courbes courant de drain – tension de drain pour les couches actives d'épaisseurs 30nm et 200nm aux tensions de grille de 0V (correspondant au minimum du courant de drain dans les caractéristiques de transfert de la figure 9) et de -2V pour la couche de 30 nm et -8V pour la couche de 100 nm (correspondant au régime en inverse des transistors)             |

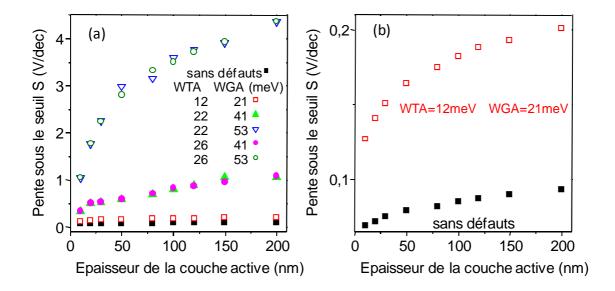

| <b>Figure III- 14 :</b> Variation de la pente sous le seuil (S) avec l'épaisseur de la couche active de TFT pour différentes valeurs de la densité de défauts dans la partie supérieure de la bande interdite. La figure (b) met en évidence le comportement de S pour la plus faible densité de défauts et de silicium monocristallin (sans défauts) [4]                                    |

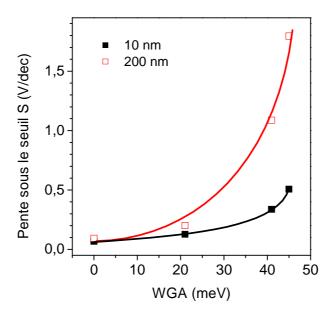

| <b>Figure III- 15 :</b> Effet de la densité de défauts profonds sur la pente sous le seuil simulée pour une couche active épaisse (200 nm) et fine (10 nm). L'effet de l'épaisseur dans la réduction de la pente est plus important pour les matériaux plus défectueux (valeur élevée du $W_{GA}$ ) 101                                                                                      |

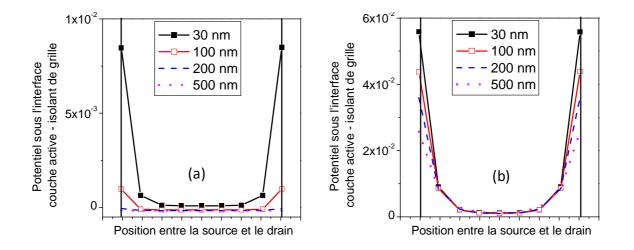

| <b>Figure III- 16 :</b> Profil du potentiel électrique simulé entre la source et le drain, sans tension de grille appliquée à des TFTs ayant différentes épaisseurs (30, 100, 200 et 500 nm) de la couche active pour le silicium avec des défauts dans la bande interdite (microcristalline ) (a) et pour le silicium sans défauts (monocristallin) (b) <b>[10]</b>                         |

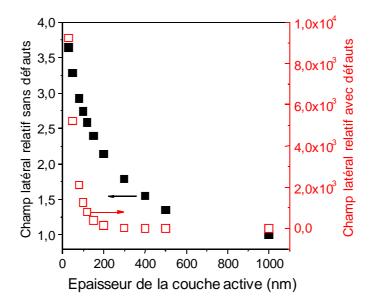

| <b>Figure III- 17 :</b> Variation du champ électrique latéral au niveau de la source (ou du drain), relativement à sa valeur pour une épaisseur de 1 µm, avec l'épaisseur de la couche active sans défauts électriques et en présence de défauts électriques                                                                                                                                 |

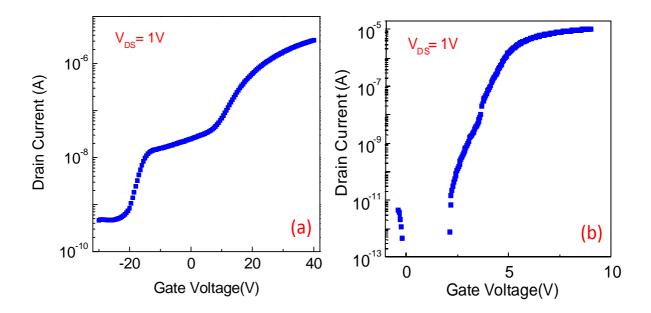

| <b>Figure III- 18 :</b> (a) Caractéristique de transfert d'un μc-Si TFT bottom-gate très mal passivé (présentée avec l'accord de F. Templier du LETI-France) (b) Transférer caractéristique de transfert d'un μC-Si TFT top-gate avec des charges fixes à l'interface couche active substrat. Ces deux caractéristiques montrent deux pentes lors de la croissance du courant de drain [16]. |

| Figure III- 19 : Caractéristiques de transfert de TFTs ayant différentes épaisseurs (30nm, 50                   |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| nm et 200 nm) de couches actives. La densité de défauts à l'interface entre l'isolant de grille et              |  |  |  |  |  |

| la couche active est fixée à 5x1011 cm <sup>-2</sup> et celle entre la couche active et le substrat est fixée à |  |  |  |  |  |

| 1x10 <sup>12</sup> cm <sup>-2</sup> [16]                                                                        |  |  |  |  |  |

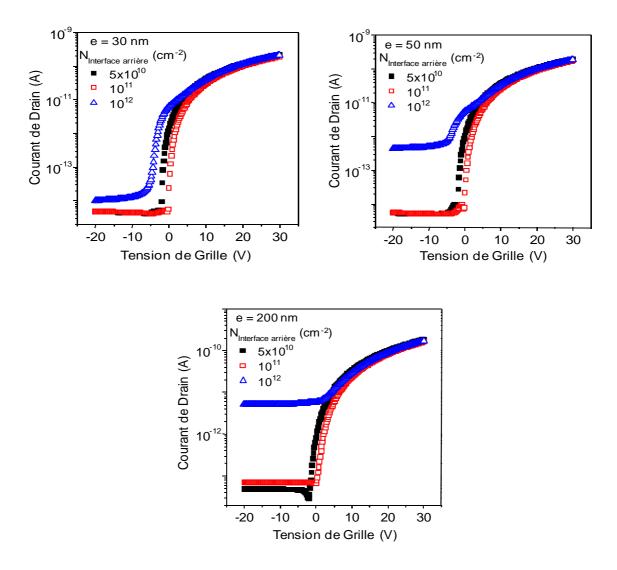

| Figure III- 20 : Caractéristiques de transfert de transistors à couches minces avec 30 nm                       |  |  |  |  |  |

| (e = 30 nm), 50 nm (e = 50 nm) et 200 nm (e = 200 nm) d'épaisseur de couche active. Les                         |  |  |  |  |  |

| caractéristiques sont tracées pour 3 concentrations de défauts différentes à l'interface a arrière              |  |  |  |  |  |

| (couche active - substrat) en maintenant constante la concentration en défauts à l'interface                    |  |  |  |  |  |

| couche active – isolant de grille à $5 \times 10^{11}$ cm <sup>-2</sup>                                         |  |  |  |  |  |

| Figure III- 21 : répartition de la concentration des électrons dans la couche active pour 2                     |  |  |  |  |  |

| TFTs, l'un de 30nm d'épaisseur de couche active et l'autre de 200 nm de coucha active à                         |  |  |  |  |  |

| Vgs = -15V, Ninterface avant = $5x1011$ cm <sup>-2</sup> et Ninterface arrière = $1x1012$ cm <sup>-2</sup>      |  |  |  |  |  |

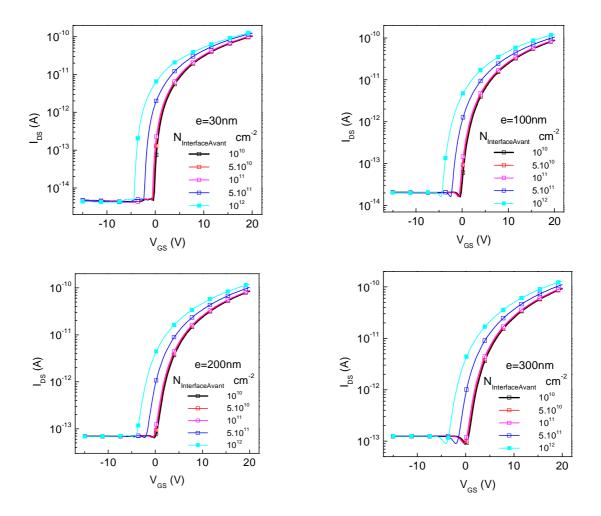

| Figure III- 22 : Caractéristiques de transfert de transistors à couches minces avec 30 nm (e =                  |  |  |  |  |  |

| 30 nm), 100 nm (e = 100 nm), 200 nm (e = 200 nm) et 300 nm (e = 300 nm) d'épaisseur de                          |  |  |  |  |  |

| couches actives. Les caractéristiques sont tracées pour différentes concentrations de défauts à                 |  |  |  |  |  |

| l'interface avant (couche active – isolant de grille) en maintenant constante la concentration en               |  |  |  |  |  |

| défauts à l'interface couche active - substrat à 1x10 <sup>11</sup> cm <sup>-2</sup>                            |  |  |  |  |  |

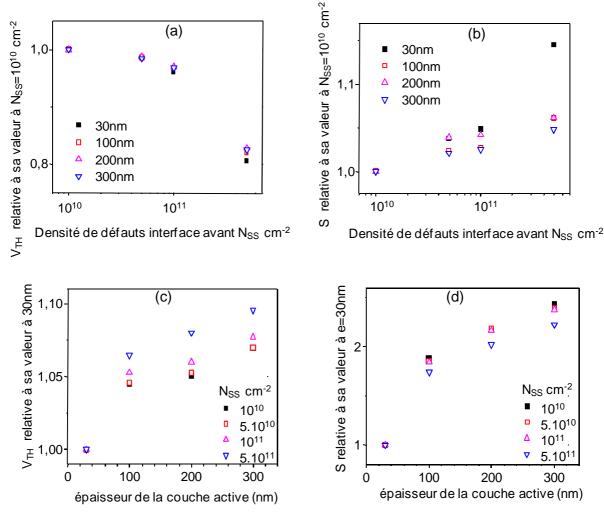

| Figure III- 23 : Variation de la pente sous le seuil S et de la tension de seuil V <sub>TH</sub> en fonction    |  |  |  |  |  |

| de la densité d'états à l'interface avant (isolant de grille - couche active) pour différentes                  |  |  |  |  |  |

| épaisseurs de la couche active et en fonction de l'épaisseur de la couche active pour                           |  |  |  |  |  |

| différentes valeurs de la densité d'états à l'interface avant (isolant de grille – couche active).              |  |  |  |  |  |

|                                                                                                                 |  |  |  |  |  |

|                                                                                                                 |  |  |  |  |  |

|                                                                                                                 |  |  |  |  |  |

| I ista das tableaux                                                                                             |  |  |  |  |  |

| Liste des tableaux                                                                                              |  |  |  |  |  |

|                                                                                                                 |  |  |  |  |  |

|                                                                                                                 |  |  |  |  |  |

| <b>Tableau II-1:</b> Conditions de dépôt des couches de silicium microcristallin (μc-Si) no                              | on dopé   |

|--------------------------------------------------------------------------------------------------------------------------|-----------|

| et dopé                                                                                                                  | 47        |

| Tableau II- 2 : Conditions opératoires de la gravure ionique réactive                                                    | 48        |

| <b>Tableau II- 3 :</b> Paramètres électriques tirés de la caractéristique de transfert du tr représentée sur la figure 1 |           |

| Tableau II- 4: Paramètres électriques des transistors dont leur caractéristique de tra                                   | ansfert a |

| été présentée sur la figure 11                                                                                           | 61        |

# Glossaire

# Glossaire

| Abréviation        | Signification                                                                                                                        |  |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| AFM                | Atomic Force Microscopy (microscope à force atomique)                                                                                |  |  |  |  |  |  |

| AMLCD              | Active Matrix Liquid Crystal Display (écran plat à cristaux liquides à matrice active)                                               |  |  |  |  |  |  |

| AMOLED             | Active Matrix Organic Light-Emitting Diode (diode organique électroluminescente à matrice active)                                    |  |  |  |  |  |  |

| APCVD              | Atmospheric pressure Chemical Vapor Deposition (dépôt chimique en phase vapeur à pressionatmosphérique)                              |  |  |  |  |  |  |

| a-Si               | Amorphous silicon (silicium amorphe)                                                                                                 |  |  |  |  |  |  |

| BAN                | Body Area Network (réseau corporel)                                                                                                  |  |  |  |  |  |  |

| HF                 | High Frequency (haute fréquence)                                                                                                     |  |  |  |  |  |  |

| HF                 | Hydrofluoric Acid (acide fluorhydrique)                                                                                              |  |  |  |  |  |  |

| H <sub>2</sub> O   | Eau                                                                                                                                  |  |  |  |  |  |  |

| $H_2O_2$           | Eau hydrogénée                                                                                                                       |  |  |  |  |  |  |

| HCl                | Acide Chlorhydrique                                                                                                                  |  |  |  |  |  |  |

| LCD                | Liquid Crystal Display ( écran plat à cristaux liquides)                                                                             |  |  |  |  |  |  |

| LPCVD              | Low Pressure Chemical Vapor Deposition (dépôt chimique en phase vapeur à basse pression)                                             |  |  |  |  |  |  |

| MIS                | Metal Insulator Semiconductor (structure capacitive Metal-Isolant-Semiconducteur)                                                    |  |  |  |  |  |  |

| μc-Si:H            | Hydrogenated Microcrystalline Silicon (silicium microcristallin hydrogéné)                                                           |  |  |  |  |  |  |

| MOS                | Metal Oxyde Semiconductor (structure capacitive Métal-SiO2-Silicium)                                                                 |  |  |  |  |  |  |

| MOSFET             | Metal Oxyde Semiconductor Field Effect Transistor (Transistor à effet de champ à structure Métal-Oxyde-Silicium)                     |  |  |  |  |  |  |

| NH <sub>4</sub> OH | Ammonium hydroxide solution (solution d'hydroxyde d'Ammonium)                                                                        |  |  |  |  |  |  |

| OLED               | Organic Light-Emitting Diode (diode organique électroluminescente)                                                                   |  |  |  |  |  |  |

| PECVD              | Plasma Enhanced Chemical Vapor Deposition (dépôt chimique en phase vapeur assistée par plasma)                                       |  |  |  |  |  |  |

| PEN                | Polyethylene Naphthalate (polyéthylène naphtalate)                                                                                   |  |  |  |  |  |  |

| RCA                | Radio Corporation of America (Werner Kern a développé ce procédé de nettoyage en 1965 alors qu'il travaillait pour RCA, d'ou le nom) |  |  |  |  |  |  |

| RF                 | Radio Frequency (fréquence radio)                                                                                                    |  |  |  |  |  |  |

| RFID               | Radio Frequency Identification (radio-étiquettes)                                                                                    |  |  |  |  |  |  |

| RMS                | Roughness Mean Square (rugosité de surface)                                                                                          |  |  |  |  |  |  |

| sccm               | Standard Centimeter Cube per Minute (centimètre cube par minute standard)                                                            |  |  |  |  |  |  |

| SF <sub>6</sub>    | Hexafluorure de Soufre                                                                                                               |  |  |  |  |  |  |

| SOI                | Silicon on Insulator (silicium sur isolant)                                                                                          |  |  |  |  |  |  |

| SPC                | Solid Phase Crystallization (cristallisation à phase solide)                                                                         |  |  |  |  |  |  |

| TFT                | Thin Film Transistor (transistor en couche mince)                                                                                    |  |  |  |  |  |  |

# Introduction générale

Les technologies de l'information et de la communication sont devenues indispensables dans ce monde où l'information doit être disponible en continu. Elles sont utilisées dans tous les secteurs de développement et elles sont rendues accessibles partout dans le monde grâce à la création de dispositifs portables. Ces derniers doivent être légers et préférentiellement souples. De plus, leur taille nécessairement miniature, impose d'intégrer l'électronique de commande et de traitement avec d'autres fonctions mécaniques, optiques ou biologiques sur le même support. Bon nombre de ces microsystèmes doit disposer d'écran de visualisation, le plus souvent tactile à matrice active de petite ou de grande taille. Ainsi, pour intégrer les composants électroniques avec les dispositifs dans les matrices actives d'adressage de pixel ou avec d'autres fonctions utilisables dans les télécommunications et les capteurs, il est utile sinon indispensable que ces composants soient fabriqués directement sur des supports de verre (température < 600°C) ou de plastique (température < 200°C).

Les transistors à effet de champ, plus précisément les transistors en couches minces (ou TFT en Anglais pour Thin Film Transistor) sont les éléments de base de cette électronique. Ils sont constitués par des dépôts successifs de couches élémentaires qui sont principalement des semi-conducteurs, des diélectriques et des couches métalliques. Il y a cependant une préférence quant à l'utilisation du silicium comme semi-conducteur dans la majeure partie des dispositifs électroniques. Son abondance sur la terre, son faible coût ainsi que ses propriétés électriques compatibles avec la technologie basse température l'ont promu au rang de matériau providentiel. Le fait qu'il soit constitué d'un seul élément rend sa chimie simple et lui donne un avantage certain sur les semi-conducteurs composés. Il est à la base de toute l'électronique actuelle.

Les composants de l'électronique conventionnelle sont fabriqués à haute température de l'ordre de 1000°C et utilisent un matériau silicium dit monocristallin. Cette température élevée est incompatible avec une intégration sur des substrats de verre ou de plastique. La technique de fabrication des transistors en couches minces (TFT) qui se distingue de celle des autres types de transistors permet leur intégration directement sur les différents types de substrat. Des performances remarquables de l'électronique intégrée avec d'autres fonctions ont été réalisées sur des substrats de verre qui peuvent supporter des températures de l'ordre de 600°C. Cependant, les avancées technologiques actuelles imposent l'utilisation de substrat flexible transparent comme support qui nécessite une technologie de fabrication à basse température (< 200°C). La structure monocristalline n'étant pas compatible avec cette

technologie sera substituée par la structure amorphe ou poly cristalline ou encore micro cristalline suivant les techniques et les conditions de fabrication.

Les activités de recherche du Département Microélectroniques et Microcapteurs de l'Institut d'Electronique et de Télécommunication de Rennes (IETR) sont principalement axées sur la réalisation de dispositifs en couches minces à base de silicium. Ceux-ci constituent les éléments de base de toute l'électronique. Le Département a ainsi acquis une expérience certaine dans le dépôt de couches minces de silicium, d'isolants et de conducteurs métalliques par différentes techniques, LPCVD, APCVD, PECVD, Pulvérisation réactive, Evaporation par effet joule et dans la fabrication de dispositifs électroniques à partir de ces couches. La particularité de ces dispositifs est la complète compatibilité de leur procédé de fabrication avec l'utilisation de substrats de type verre ou plastique, ne supportant pas des températures élevées. Cette longue expérience permet au Département d'être présent actuellement dans la problématique de microsystèmes complètement intégrés sur un même substrat, portables et éventuellement flexibles.

Cette thèse s'inscrit dans cette problématique de fabrication de dispositifs électroniques à la plus basse température possible, compatible avec l'utilisation de substrats plastiques transparents. La technologie de fabrication développée par le Département a permis de réaliser des TFT de type N et de type P ayant des caractéristiques électriques (mobilité, stabilité, ...) permettant d'envisager leur utilisation pour la conception et la réalisation de circuits plus complexes.

Le travail de thèse a ainsi pour objectif d'accompagner ce développement par une modélisation du fonctionnement des transistors en couches minces afin de comprendre les mécanismes sous-jacents et de pouvoir faire un retour à la technologie. Le document est subdivisé en trois chapitres. Il commence par un chapitre décrivant l'état de l'art au niveau international et au niveau de la technologie développée dans l'IETR. Le chapitre suivant présente les résultats expérimentaux obtenus sur des TFTs fabriqués en faisant varier des paramètres dont le plus important est l'épaisseur de la couche active. Le dernier chapitre est consacré à la modélisation du comportement de ces TFTs par l'utilisation d'un logiciel développé par SILVACO. Il permettra d'expliquer les résultats expérimentaux présentés précédemment dans le second chapitre afin de pouvoir orienter l'optimisation du procédé de fabrication. Il constitue aussi une base de départ pour le développement d'une bibliothèque

technologique, qui servira pour la conception de dispositifs électroniques à base de transistors en couches minces fabriqués à basse température directement sur tout substrat

| <b>~1</b> • • | • |   | <b>.</b> | 1  | 11 .  |    |       |     | . •   |    |

|---------------|---|---|----------|----|-------|----|-------|-----|-------|----|

| Chapitre      | 1 | : | Etat     | de | I'art | et | prob. | lėm | ıatıq | ue |

### I.1 Introduction

L'électronique est devenue maintenant un facteur incontournable de la vie moderne. Presque aucun acte humain actuel ne se fait sans l'aide de l'électronique que l'on soit chez soi, au travail, au volant de sa voiture et partout ailleurs. Les dispositifs de cette électronique utilisent dans leur très grande majorité du silicium comme matériau actif. Le silicium, matériau semi-conducteur, réunit l'ensemble des critères permettant à des dispositifs électroniques aussi nombreux à fonctionner sur notre terre telle qu'elle est. Il est largement disponible partout sur terre (28% de la croûte terrestre). Il n'est constitué que du seul élément silicium permettant une technologie simplifiée ne dépendant que des propriétés chimiques de ce seul élément. La largeur de sa bande interdite permet aux dispositifs électroniques de bien bloquer le passage du courant ou de laisser un courant suffisant passer suivant les conditions de polarisation aux températures habituelles sur terre.

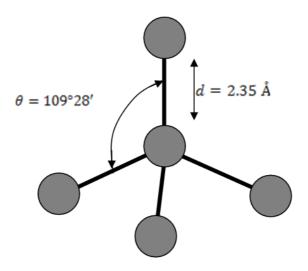

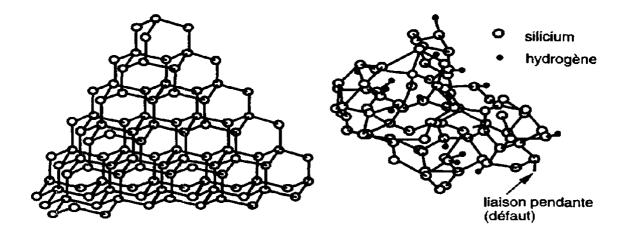

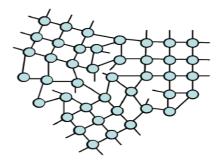

Ce matériau, idéal si l'on peut dire, se présente suivant différents états du point de vue de sa cristallinité et donc du point de vue de l'ordre de positionnement des atomes à l'intérieur. Dans son état monocristallin, il se présente comme la superposition ordonnée à l'échelle du mètre d'un tétraèdre d'atomes de silicium (Figure I.1) [1].

Figure I- 1 : Tétraèdre d'atomes de silicium et leur arrangement ordonné dans le silicium monocristallin

Cet ordre permet d'obtenir du silicium les meilleures propriétés de transport électroniques et ainsi de fabriquer les dispositifs performants actuels. La superposition ordonnée est obtenue grâce à différentes techniques de purification et de croissance cristalline à des températures largement supérieures à 1000°C [2]. Après ces étapes de purification et de croissance et après découpe des lingots cristallins obtenus, les substrats de départ à partir desquels sont fabriqués les dispositifs électroniques sont des plaquettes de quelques centaines de micromètres d'épaisseur et de couleur grisâtre ou bleue après polissage. Elles sont donc rigides et ne sont pas transparentes à la lumière visible.

## I.2 Electronique fabriquée sur un substrat

La non-transparence des plaquettes de silicium monocristallin constitue un problème si la transparence est nécessaire. Le problème a commencé à se poser à la fin des années 1970 lorsque le besoin de développer largement l'affichage de données et d'images et donc des écrans permettant cet affichage. L'affichage n'est possible que s'il est possible de commander différemment des petites zones voisines sur la surface de l'écran leur donnant différents tons de gris allant du noir au blanc ou différentes couleurs. Ces petites zones, appelées pixels, doivent être suffisamment petites pour que l'écran apparaisse comme uniforme à l'œil. De la lumière de différents tons ou de couleurs doit sortir de ces pixels. Ils doivent donc être transparents. Un écran d'affichage est donc un substrat transparent sur lequel on vient déposer des pixels petits commandés électriquement. Le problème de l'électronique a donc consisté à mettre des dispositifs de commande sur des substrats transparents.

### I.2.1 Electronique pour pixels d'écrans plats

Un écran plat pour l'affichage est constitué d'une matrice de pixels reproduisant une image. Chaque pixel est une source de lumière constituant un des points de l'image. Il doit être polarisé pour obtenir la lumière correspondante à ce point de l'image. La méthode de polarisation dépend du type de production de cette lumière.

Les écrans plats LCD à matrice active ou AMLCD (Active Matrix Liquid Crystal Display) dominent le marché actuel des écrans. Cependant, il est apparu les écrans OLED à matrice active ou AMOLED (Active Matrix Organic Light-Emitting Diode)

Les OLEDs, sont actuellement un domaine de recherche en très grande expansion et qui devrait permettre le développement d'une nouvelle génération d'écrans plat. La technologie des OLEDs basée sur le substrat de plastique est développée activement pour concurrencer la technologie AMLCD dans les applications partant des petits écrans aux

grands [3]. Aujourd'hui, les AMOLEDs sont déjà commercialisés par plusieurs compagnies. Ils sont utilisés principalement dans les petits appareils souples (les téléphones portables, les appareils photos, les baladeurs, les portes photos). T. Tsujimura et al. [4] ont démontré la faisabilité en ce qui concerne le succès dans la fabrication de grands écrans OLED (sur substrat verre) comprenant des tailles supérieures à 20". A une échelle bien moins grande, les OLEDs s'appliquent aussi pour l'avionique [5].

Dans la suite, la définition et le principe de fonctionnement de ces deux types d'écrans seront présentés et le rôle essentiel que jouent les transistors en couches minces dans le bon fonctionnement de ces écrans sera précisé.

### **I.2.1.1** Ecran plat LCD à matrice active (AMLCD)

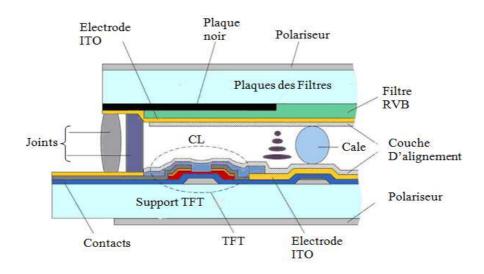

Un écran plat à matrice active est constitué d'un cristal liquide inséré entre deux plaques de verre (cf figure I.2). La plaque supérieure, est recouverte d'une couche uniforme de matériau conducteur transparent servant de contre électrode. L'autre plaque comporte un réseau déposé de lignes et de colonnes. A l'intersection de chaque ligne et de chaque colonne est situé un transistor en couches minces dont le rôle est :

- dans la phase d'adressage (mode de conduction du transistor), de charger un condensateur élémentaire ayant pour diélectrique le cristal liquide.

- dans la phase de stockage (mode bloquant du transistor), de maintenir la charge de ce condensateur.

une borne de ce condensateur est formée d'un carré de conducteur transparent relié au transistor, l'autre borne est la contre électrode. Un élément d'image, ou pixel, est défini par cette capacité de cristal liquide et de son transistor associé.

Chapitre I : Etat de l'art et problématique

Figure I- 2: Vue en coupe d'un écran plat [6]

Pour afficher une image, un écran plat LCD utilise des cristaux liquides qui soumis à un courant électrique laissent passer ou pas la lumière. Celle-ci passe à travers 3 matrices à cristaux liquides, devant chacune d'elles se trouve un filtre de couleur : un rouge, un vert et un bleu [7]. En fonction du signal envoyé, les cristaux liquides vont plus ou moins laisser passer la lumière, celle-ci est alors concentrée sur un prisme central qui diffusera un seul faisceau lumineux et formera ainsi une image.

Un cristal liquide est un état de la matière qui combine des propriétés d'un liquide conventionnel et celles d'un solide cristallisé. Ces propriétés permettent à certains cristaux liquides de modifier la polarisation de la lumière. Leurs molécules mésomorphes, de forme allongée, peuvent se déplacer parallèlement les unes par rapport aux autres. Déposées sur une plaque gravée en sillons, les molécules vont s'aligner dans les sillons.

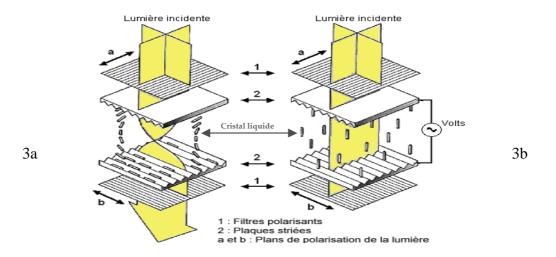

Le principe des écrans LCD consiste alors à placer des cristaux liquides entre deux polariseurs croisés dont la direction de polarisation est orientées à 90° l'une par rapport à l'autre. Les molécules, au repos, vont passer progressivement d'une orientation à l'autre (cf figure I.3) [8]. L'écran est ensuite éclairé par une lumière extérieure qui est polarisée par un filtre suivant la direction parallèle aux sillons de la première plaque. Sa polarisation est guidée par les molécules et après une rotation de 90°, elle passe par un deuxième filtre polarisant (cf figure I.3a). Ce dernier fonctionne comme un grillage dense et mince qui force la lumière à ne suivre qu'un seul chemin, celui parallèle aux fentes du filtre polarisant.

Sous l'effet d'une tension de commande, les molécules vont progressivement s'orienter dans le sens du champ électrique et la lumière sera bloquée par le deuxième polariseur (cf figure I.3b).

Figure I- 3 : Principe de fonctionnement des écrans à cristaux liquides [9]

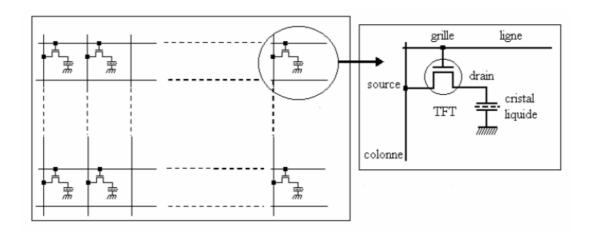

Les transistors en couches minces jouent ainsi un rôle important dans le fonctionnement des écrans plats LCD. Dans la figure I.4, nous présentons le schéma électrique équivalent d'un pixel.

Figure I- 4 : Schéma de la matrice de transistors [10]

L'application d'une tension sur une ligne fait que tous les transistors, dont les grilles sont reliées à cette ligne, deviennent passants, et la tension présente sur une colonne est transférée à l'élément d'image situé à l'intersection de cette ligne et de la colonne.

A l'inverse, les autres lignes n'étant pas excitées, les transistors, qui sont dans leur état bloquant, permettent de conserver aux bornes de l'élément image l'information précédemment inscrite. Ici réside tout l'intérêt de l'incorporation de transistors à la matrice active du fait qu'ils fournissent à la fois l'activation ou la désactivation recherchée et l'effet de mémoire.

L'écran plat à matrice active LCD comprendra autant de transistors que de points d'images.

De nos jours, les transistors en couches minces de commande utilisés dans les écrans plats LCD sont principalement fabriqués à partir du silicium amorphe déposé par PECVD (Plasma Enhanced Chemical Vapor Deposition) à une température d'environ 250°C. Cependant, ils présentent deux inconvénients : une très faible mobilité et une dérive de la tension de seuil lors de son fonctionnement. Ce dernier est corrigé par les constructeurs en intégrant des circuits de compensation.

### **I.2.1.2** Ecran plat OLED à matrice active (AMOLED)

Les écrans plats OLED à matrice active sont des écrans qui associent une technique matrice active et une technologie OLED. Cette technologie s'annonce prometteuse compte tenu de son excellent angle de vue, sa forte résolution, sa faible consommation électrique et son temps de réponse rapide [11, 12]. Elle est devenue aujourd'hui le centre d'intérêt de nombreuses sociétés.

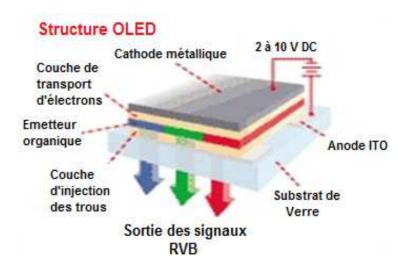

Une cellule OLED (cf figure I.5) est composée d'une pile de couches organiques fines prises entre une anode transparente et une cathode métallique. Les couches organiques comprennent une couche d'injection, une couche de transport de trous, une ou plusieurs couches émettrices et une couche de transport d'électrons. L'application d'un courant précis à la cellule OLED engendre une recombinaison des charges positives et négatives dans les couches émettrices afin de produire une lumière électroluminescente. La structure des couches organiques, le choix de l'anode et de la cathode sont conçus pour maximiser le processus de recombinaison dans les couches émettrices, ce qui optimise l'émission de lumière à partir de l'appareil OLED [13].

Chapitre I : Etat de l'art et problématique

Figure I- 5: Structure d'une OLED [13]

Les matériaux utilisés dans la conception de ces diodes offrent à la technologie OLED des avantages intéressants par rapport à celle des cristaux liquides. En effet, la propriété électroluminescente de l'OLED ne nécessite pas l'introduction d'un rétro éclairage ce qui confère à l'écran des niveaux de gris plus profond et une épaisseur moindre. La flexibilité de ces matériaux offre aussi la possibilité de réaliser un écran souple et ainsi de l'intégrer sur des supports très variés comme les plastiques (cf figure I.6). L'utilisation de ces substrats plastiques est intéressante, car il permet l'affichage léger et incassable [12, 14].

Figure I- 6: Ecran flexible utilisant une technologie OLED [15]

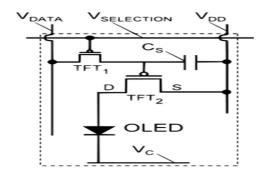

La technologie OLED utilisée dans la fabrication des écrans plats utilise deux transistors en couches minces et une capacité pour la commande des pixels. Dans la

figure I.7, nous présentons un schéma électrique équivalent utilisé pour la commande d'un pixel.

**Figure I-7:** Circuit pixel OLED à deux TFTs et une capacité (2T1C) [16]

Dans cette technologie OLED, le circuit de commande de pixel comporte au moins deux transistors comme le montre la figure ci-dessus. Le premier transistor (TFT1) joue le rôle de commutateur électronique de manière analogue à celle des écrans LCD. La diode électroluminescente est directement contrôlée par le second transistor (TFT2) qui lui fourni le courant nécessaire à son éclairage. Pour le bon fonctionnement des écrans OLED, il est plus que nécessaire que le courant fourni soit précis. IL est donc important que les transistors utilisés soient de bonnes qualités. Ils doivent avoir des caractéristiques très stables. Cependant, comme pour les écrans LCD, les transistors à base de silicium amorphe utilisés dans la fabrication des écrans OLED posent beaucoup de problème sinon même plus du fait de leur instabilité et leur faible mobilité.

### I.2.2 Electronique sur un substrat pour d'autres applications

Des nos jours de nouveaux besoins de systèmes portables, légers, autonomes pouvant épouser toutes les formes sont à la base du développement de l'électronique sur substrat flexible. En effet, depuis quelques années, plusieurs travaux de recherches sont menés pour l'élaboration de produits électroniques souples.

Ces derniers sont utilisés dans la fabrication des écrans flexibles (cf figure I.6), des patchs biologiques, des cartes RFID avec une électronique intégrée directement sur la carte, des cellules solaires intégrées dans les vêtements ou des caméras sphériques

tridimensionnelles de type « fish eye »... Cela a pour conséquence l'expansion du marché de l'électronique.

De plus, cela permet aussi la réduction importante du coût de production des dispositifs précédemment mentionnés par rapport aux circuits intégrés directement sur les substrats de silicium et de verre

L'électronique flexible occupe aujourd'hui une place importante dans les domaines de la médecine, du sport, des télécommunications, de l'informatique. L'utilisation des écrans tactiles dans les téléphones portables, les ordinateurs, les tablettes etc ..., sont des exemples d'applications en informatique et en télécommunication. Le "Body Area Network" (BAN) est une technologie utilisée dans plusieurs domaines tels que le sport, le jeu, mais son utilisation dans le domaine médical est majeure.

Le BAN est une technologie de réseau sans fil basée sur les radiofréquences qui consiste à interconnecter sur, autour ou dans le corps humain de minuscules dispositifs pouvant effectuer des mesures (capteurs) ou agir de façon active (actionneurs). Ces capteurs très miniaturisés, disposant d'une grande autonomie et utilisant des courants de très faible puissance peuvent être capables de dialoguer avec un centre de service distant, pour alerter un service d'urgences hospitalières par exemple. Les principales applications se trouvent dans les domaines de la santé, des premiers secours, du militaire, du divertissement, du sport, de l'intelligence ambiante ou des interactions homme-machine [17, 18].

Des recherches avancées sont menées pour le remplacement dans un futur proche des prothèses mécaniques par des prothèses électroniques ou des neuroprothèses.

Les prothèses électroniques permettent de gérer différentes phases de la marche afin de la rendre plus naturelle et plus confortable. [19].

La Neuroprothèse est un appareillage se rattachant au système nerveux. Ces prothèses neurologiques sont contrôlés indirectement par le cerveau; celui-ci envoie des signaux électriques naturels par le biais des nerfs (mouvements, réaction, sensibilité...) traduit et reproduit par la neuroprothèse [20].

L'électronique traditionnelle MOS sur wafer de silicium peut être résumée comme un assemblage d'un grand nombre de transistors MOS. De la même manière, l'élément de base

de l'électronique sur tout substrat est un transistor MOS appelé ici transistor en couches minces car formé d'une superposition de couches minces. Il est présenté dans le paragraphe suivant.

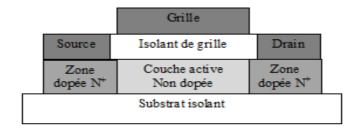

### I.3 Transistors en couches minces

Les transistors en Couches Minces (TCM) autrement appelés Thin Film Transistors (TFT) sont des transistors à effet de champ. Ils sont formés par un dépôt successif de plusieurs couches minces (quelques dizaines à quelques centaines de nanomètres) (voir figure I.8). Celles-ci généralement au nombre de trois sont : une couche métallique, une couche isolante et du semi-conducteur. La figure 1.8 présente un transistor en couches minces dans sa forme générale.

Figure I- 8: Architecture générale d'un transistor en couches minces

Comme le montre la figure I.8, un transistor en couches minces est généralement composé d'une couche active, de deux zones dopées identiques, d'un isolant de grille surmonté par du métal (la grille) déposé suivant un certain ordre sur un substrat. Comme pour la grille, une couche métallique (l'aluminium plus particulièrement ou du polysilicium fortement dopé dans certains cas) termine les deux zones dopées pour constituer les contacts source et drain.

Le fonctionnement des transistors en couches minces TMC est basé sur le contrôle du courant qui s'écoule entre la source et le drain à travers une tension commandée par la grille. C'est la polarisation de la capacité métal/isolant/semi-conducteur (MIS) qui module la conductivité du canal au niveau de la surface du semi-conducteur. Lorsqu'une tension positive est appliquée à la grille ( $V_{GS}$ ), on obtient une accumulation de charges négatives à l'interface entre semi-conducteur et isolant de grille.

Dans le cas d'un transistor de type N, lorsque la tension de la grille est positive et dépasse une certaine tension de polarisation (appelée tension de seuil  $V_{TH}$ ), nécessaire à l'établissement d'une forte inversion, il y a création d'un canal conducteur de type N entre la source et le drain. Lorsque la tension de grille est négative, le transistor doit être bloquant. Pour un bon fonctionnement des transistors en couches minces, il est important que :

- La couche active non dopée soit de bonne qualité sans défauts électriques afin de favoriser le passage des porteurs majoritaires. Ceci permet d'engendrer un courant I<sub>on</sub> très élevé sous l'effet d'une faible polarisation de grille et donc une faible tension sous le seuil.

- Les zones dopées soient fortement dopées afin de réduire les résistances d'accès et ainsi contribuer à l'augmentation du courant I<sub>on</sub>.

- La couche isolante ne laisse pas passer du courant entre la grille et la couche nondopée et ne doit pas contenir de charges mobiles pouvant influencer le courant drainsource. En plus, elle doit présenter une bonne interface avec la couche non dopée sans défauts électriques.

### I.3.1 Structure des TFTs

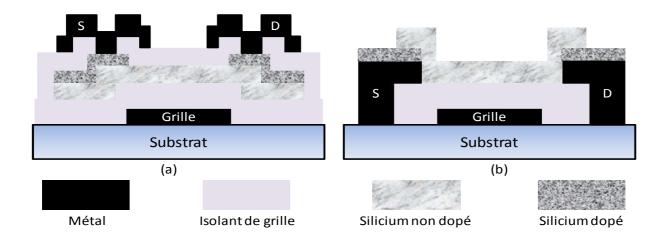

Suivant l'ordre de dépôt du semi-conducteur par rapport à l'isolant de grille, on distingue deux types de structures :

- Si le semi-conducteur est déposé sur l'isolant de grille, la structure du transistor obtenu est de type Bottom-Gate (pour dire grille en dessous) ;

- Si l'isolant de grille est déposé sur le semi-conducteur, la structure du transistor obtenu est de type Top-Gate (pour dire grille au dessus).

Les structures Top-Gate ou Bottom-Gate peuvent être coplanaires ou inversés selon la disposition du canal et des contacts source et drain par rapport au semi-conducteur. On parle de structures coplanaires quand les contacts source et drain et le canal sont du même coté par rapport au semi-conducteur. Dans le cas contraire, où ces derniers sont sur des cotés opposés, on parle de structures inversées.

### I.3.1.1 TFT à grille en dessous (Bottom-Gate)

La performance et les caractéristiques électriques des transistors en couches minces dépendent des matériaux utilisés, des conditions de dépôt et de l'ordre de dépôt des différentes couches. Les transistors en couches minces qui ont la structure à grille en dessous sont les plus utilisés aujourd'hui dans la fabrication des transistors à base de silicium amorphe pour l'adressage des écrans plats à matrice active comme le montre l'exemple de la figure I.2. Ils ont l'avantage d'avoir un courant  $I_{\rm off}$  meilleur ( $I_{\rm off}$  plus faible) que celui des transistors ayant la structure à grille au dessus. Nous présentons sur la figure I.9 deux modèles de TFTs Bottom-Gate.

**Figure I-9 :** Structure Bottom-Gate inversée (a) et coplanaire (b)

### I.3.1.2 TFT à grille au dessus (Top-Gate)

Par sa technique de fabrication, la structure Top-Gate des TFTs présente un canal situé en surface là ou la qualité cristalline du matériau silicium est meilleure ce qui par conséquent favorise la mobilité électronique des porteurs de charge. Cette structure est plus avantageuse pour le silicium polycristallin et le silicium microcristallin qui ont une fraction cristalline qui évolue avec l'épaisseur. Par contre, par rapport à la structure bottom gate, elle a un courant de fuite relativement élevé. Nous présentons sur la figure I.10 les structures de base des TFTs Top-Gate les plus fréquentes dans la littérature.

Chapitre I : Etat de l'art et problématique

Figure I- 10 : Structure Top-Gate coplanaire (a) et inversée (b)

Il est plus évident d'utiliser la structure inversée car la gravure du canal est bien contrôlée. Le deuxième avantage de cette structure est son courant I<sub>off</sub> qui est généralement nettement meilleur que celui de la structure coplanaire.

Un des désavantages de la structure inversée est que les porteurs de charges doivent traverser toute la couche intrinsèque pour parvenir à la zone du canal. Cela engendre une résistance d'accès beaucoup plus grande que dans la structure coplanaire. De plus, le problème de l'interface du silicium dopé et du silicium non dopé réduit les performances.

# I.4 Principe de fonctionnement des TFTs

Le fonctionnement des transistors est basé sur le contrôle du courant qui circule entre la source et le drain par l'application d'une tension variable sur la grille. Lorsque la tension appliquée est positive, il y'a accumulation de charge à l'interface isolant-semi-conducteur et dès qu'elle devient supérieure à une tension dite de seuil (V<sub>TH</sub>), un canal conducteur est créé rendant ainsi possible le passage de courant entre la source et le drain lorsque ces derniers sont polarisés.

### I.4.1 Etat bloquant

Lorsque la tension de grille est insuffisante pour créer un canal, un courant faible peut circuler entre le drain et la source. Ce courant résulte de la polarisation en inverse de la jonction drain-source.

### I.4.2 Etat passant

Lorsque la grille est polarisée par une tension supérieure à la tension de seuil, un canal conducteur est créé entre la source et drain. Un courant peut alors circuler entre la source et le drain, le transistor est passant.

Pour une tension de drain très faible  $(V_{DS} \ll V_{GS} - V_T)$ , la zone de canal a une conductance constante. Le canal se comporte comme une résistance ohmique qui est fonction des caractéristiques géométriques du transistor. La variation de conductance du canal est négligeable. Le courant de drain varie alors proportionnellement à  $V_{DS}$ :

$$I_{DS} = \frac{W}{L} \mu_{FE} C_{OX} (V_{GS} - V_{T}) V_{DS}$$

(I. 1)

W (µm): largeur du canal

L (μm): longueur du canal

$\mu_{FE}$  (cm<sup>2</sup>. V<sup>-1</sup>. s<sup>-1</sup>) : mobilité d'effet de champ

Cox (F. cm<sup>-2</sup>) : capacité par unité de surface de l'oxyde de grille

V<sub>T</sub> (V): tension de seuil du transistor

A partir de l'équation 1, il est possible de définir la transconductance  $g_m$  et la conductance  $g_t$  du drain comme suit :

$$g_{\rm m} = \frac{\partial I_{\rm DS}}{\partial V_{\rm GS}} \Big|_{V_{\rm DS} = {\rm cte}} = \frac{W}{L} \mu_{\rm FE} C_{\rm OX} V_{\rm DS} \tag{I.2}$$

$$g_{t} = \frac{\partial I_{DS}}{\partial V_{DS}} \Big|_{V_{GS} = cte} = \frac{W}{L} \mu_{FE} C_{OX} (V_{GS} - V_{T})$$

(I.3)

### I.4.2.1 Régime saturé

Quand  $V_{DS}$  atteint la valeur de  $(V_{GS} - V_T)$ , il y a saturation. La tension drain-source atteint une valeur nommée  $(V_{DSsat})$  appelée tension de saturation. C'est le pincement du canal du côté du drain.

Quand la tension drain-source augmente au delà de la tension de saturation, la région voisine du drain n'est plus en inversion; le point de pincement se déplace vers la source. L'excédent de tension au delà de  $V_{DSsat}$  se retrouve aux bornes de la zone de désertion dont la résistance est très supérieure à celle du canal. La tension aux bornes du canal reste approximativement égale à  $V_{DSsat}$  et le courant de drain reste dans ces conditions sensiblement constant et égale à  $I_{DSsat}$  et son expression est la suivante :

$$(I_{DS})_{sat} = \frac{W}{2L} \mu_{FE} C_{OX} (V_{GS} - V_T)^2$$

(I.4)

La transconductance en régime de saturation est alors déduite de la relation :

$$(g_{\rm m})_{\rm sat} = \frac{\partial I_{\rm DS}}{\partial V_{\rm GS}} \Big|_{V_{\rm DS_{\rm sat}}} = \frac{W}{L} \mu_{\rm FE} C_{\rm OX} (V_{\rm GS} - V_{\rm T}) \tag{I.5}$$

### I.4.3 Caractérisation des TFTs

L'ensemble des mesures électriques est réalisé sous pointe dans une cage métallique à température ambiante et à l'abri de la lumière. Le dispositif utilisé est un analyseur HP 4155 programmable, servant de source de tension et de multimètre. Ce dispositif de mesures nous permet d'obtenir les caractéristiques de transfert et de sortie des transistors. Il permet également de réaliser des mesures de stress sur les composants.

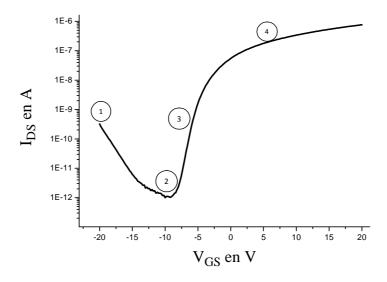

### I.4.3.1 Caractéristiques de transfert

La figure I.11 présente une caractéristique de transfert  $I_{DS}$  = $f(V_{GS})$  typique d'un transistor en couches minces. Cette dernière présente les quatre zones de fonctionnement des transistors en couches minces :

Chapitre I : Etat de l'art et problématique

Figure I-11: Caractéristique de transfert d'un TFT

La zone (1) présente l'état bloquant du transistor avec un courant non nul ( $I_{DS} = I_{OFF}$ ) dû à la génération des porteurs piégés et accélérés par la forte tension au niveau du drain.

La zone (2) met en évidence la conduction ohmique de toute la couche active.

La zone (3) représente la formation du canal et le courant de drain augmente très rapidement avec la tension de grille.

La zone (4) montre l'état passant du transistor ( $I_{DS} = I_{ON}$ ).

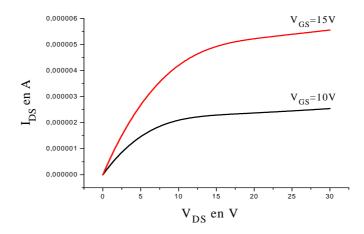

#### I.4.3.2 Caractéristiques de sortie

Les caractéristiques de sortie  $I_{DS} = f(V_{DS})$  d'un TFT pour deux valeurs de  $V_{GS}$  sont présentées en figure I.12. Elles décrivent le fonctionnement en régime linéaire pour de faibles tensions de grille et en régime de saturation lorsque  $V_{DS}$  augmente. Cette caractéristique montre également une bonne modulation du courant de drain par la tension de grille.

Chapitre I : Etat de l'art et problématique

Figure I- 12 : Caractéristiques de sortie d'un transistor E4 (100µm/20µm) pour deux VDS

Par la suite, une description détaillée des paramètres électriques régissant le comportement électrique sous l'effet de champ d'un transistor en couches minces qui sont :

- $\checkmark$  La tension de seuil ( $V_{TH}$ ),

- ✓ La mobilité d'effet de champ des porteurs à l'état passant  $(\mu)$ ,

- ✓ La pente sous le seuil (S),

- ✓ La transconductance  $(g_m)$ .

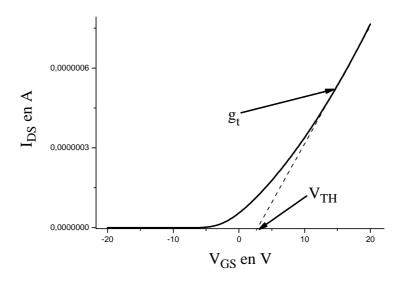

#### I.4.3.3 Tension de seuil