# Approximate computing for high energy-efficiency in IoT applications

Geneviève Ndour

#### ▶ To cite this version:

Geneviève Ndour. Approximate computing for high energy-efficiency in IoT applications. Other [cs.OH]. Université de Rennes, 2019. English. NNT: 2019REN1S033 . tel-02292988v2

# HAL Id: tel-02292988 https://theses.hal.science/tel-02292988v2

Submitted on 22 Nov 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

#### L'UNIVERSITE DE RENNES 1

COMUE UNIVERSITE BRETAGNE LOIRE

ECOLE DOCTORALE N° 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique

Par

# « Geneviève NDOUR »

« Approximate computing for high energy-efficiency in internet-of-things applications »

Thèse présentée et soutenue à Grenoble, le 17 juillet 2019 Unités de recherche : CEA LETI Grenoble, IRISA INRIA Lannion

#### Rapporteurs avant soutenance :

Florent DE DINECHIN Professeur à l'INSA Lyon, CITI

Lionel TORRES Professeur à l'Université de Monpellier, LIRMM

#### **Composition du Jury:**

Président: Olivier SENTIEYS Professeur à l'Université Rennes 1, IRISA INRIA Examinateurs: Alberto BOSIO Professeur à l'Ecole Centrale de Lyon, INL

Olivier SENTIEYS Professeur à l'Université Rennes 1, IRISA INRIA

Florent DE DINECHIN Professeur à l'INSA Lyon, CITI

Lionel TORRES

Professeur à l'Université de Monpellier, LIRMM Dir. de thèse: Arnaud TISSERAND Directeur de Recherche CNRS, Lab-STICC Lorient Co-dir. de thèse: Anca MOLNOS Ingénieur de Recherche, CEA LETI Grenoble

# **ACKNOWLEDGEMENT**

J'adresse mes remerciements à mon directeur de thèse Arnaud TISSERAND et à mon encadrante Anca MOLNOS pour leurs conseils sur toutes les décisions prises pour la réalisation des travaux de recherche et pour mes démarches personnelles. Merci également à Yves DURAND et à Edith BEIGNE pour leur soutien dans l'encadrement de la thèse.

Mes remerciements vont aussi aux rapporteurs Lionel TORRES et Florent DE DINECHIN pour la relecture de la thèse et à tous les membres du jury qui ont accepté d'évaluer mon travail.

Je remercie également Tiago TREVISAN-JOST pour l'implémentation du simulateur RISC-V et les collègues du DACLE/LISAN pour l'estimation du modèle d'énergie. Ces outils m'ont permis de valider les idées développées durant la thèse par une série d'expériences.

J'adresse toute ma reconnaissance à mes collègues du LIALP pour l'ambiance de travail qui constituait une source de motivation tout au long de mon stage de fin d'études et de ma thèse. Merci au chef de labo Vincent OLIVE pour son accueil.

Un grand merci aux personnes que j'apprécie beaucoup et qui ont constitué ma seconde famille : Adja (my bestie), Roxana, Maha, Sanaa, Oumayma et les membres de la chorale Sainte Cécile de Grenoble, pour leur amitié et leur aide (e.g. relecture d'articles, pot de thèse, conseils, moments de détente entre la rédaction de deux chapitres de thèse).

Je ne pourrai finir sans exprimer toute ma gratitude à ma famille. Merci à mes parents Palé TOURÉ et Robert NDOUR pour leur soutien moral et matériel ainsi que leur confiance indéfectible dans mes choix. Merci à mes frères : Djibril, Jean et à ma soeur Coumba pour leur soutien.

Au terme de ce parcours, je remercie enfin mon mari Justino LOPES pour son soutien et son attention qui m'ont accompagnée tout au long de ces années, dans les bons et les mauvais moments. Merci d'avoir fait la thèse avec moi et d'avoir accepté de différer beaucoup de nos projets personnels pour achever cette thèse dans les meilleures conditions.

# **TABLE OF CONTENTS**

| 1 | Intro | oduction                                                      | 9  |

|---|-------|---------------------------------------------------------------|----|

|   | 1.1   | Context                                                       | 9  |

|   | 1.2   | Problem statement                                             | 12 |

|   | 1.3   | Contributions                                                 | 13 |

|   | 1.4   | Thesis organization                                           | 15 |

| 2 | Stat  | te of the art                                                 | 17 |

|   | 2.1   | Numerical data representation                                 | 19 |

|   |       | 2.1.1 Floating-point                                          | 19 |

|   |       | 2.1.2 Fixed-point                                             | 20 |

|   | 2.2   | Algorithmic approximations                                    | 23 |

|   | 2.3   | Hardware blocks for approximate computing                     | 25 |

|   |       | 2.3.1 Fixed width adders and multipliers                      | 26 |

|   |       | 2.3.2 Variable width adders and multipliers                   | 27 |

|   | 2.4   | Software for approximate computing: programming, compiler and |    |

|   |       | runtime support                                               | 28 |

|   | 2.5   | Benchmark applications and quality metrics                    | 31 |

|   | 2.6   | RISC-V processor                                              | 37 |

|   |       | 2.6.1 RV32I instruction formats in our work                   | 37 |

|   |       | 2.6.2 RISC-V base opcodes map                                 | 38 |

|   |       | 2.6.3 RISC-V architecture                                     | 39 |

|   | 2.7   | Energy models                                                 | 40 |

|   | 2.8   | Chapter summary                                               | 42 |

| 3 | RIS   | C-V processor extended with reduced width units               | 45 |

|   | 3.1   | Extended RISC-V ISA with reduced width instructions           | 46 |

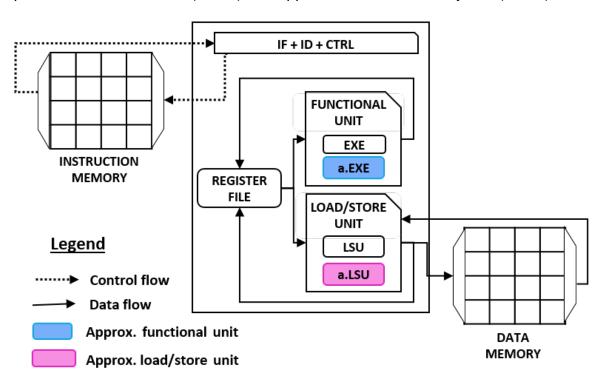

|   | 3.2   | Architecture of the extended RISC-V                           | 50 |

|   | 3.3   | Energy model per instruction class                            | 51 |

|   |       | 3.3.1 Energy model for full width instructions                | 51 |

#### TABLE OF CONTENTS

|   |      | 3.3.2     | Energy model for reduced width instructions                        | 51  |

|---|------|-----------|--------------------------------------------------------------------|-----|

|   | 3.4  | Exper     | imental environment                                                | 55  |

|   |      | 3.4.1     | Programming support for our extended RISC-V                        | 55  |

|   |      | 3.4.2     | Instrumentation tool                                               | 59  |

|   | 3.5  | Chapt     | er summary                                                         | 62  |

| 4 | Eva  | luation   | of reduced width units on applications                             | 63  |

|   | 4.1  | Metho     | dology                                                             | 64  |

|   | 4.2  | Impac     | t of the fixed-point conversion on the applications output quality | 65  |

|   |      | 4.2.1     | Jmeint application                                                 | 65  |

|   |      | 4.2.2     | Sobel filter application                                           | 66  |

|   |      | 4.2.3     | Forwardk2j application                                             | 69  |

|   | 4.3  | Impac     | t of reduced width units for addition and multiplication on ap-    |     |

|   |      | plication | ons energy consumption                                             | 70  |

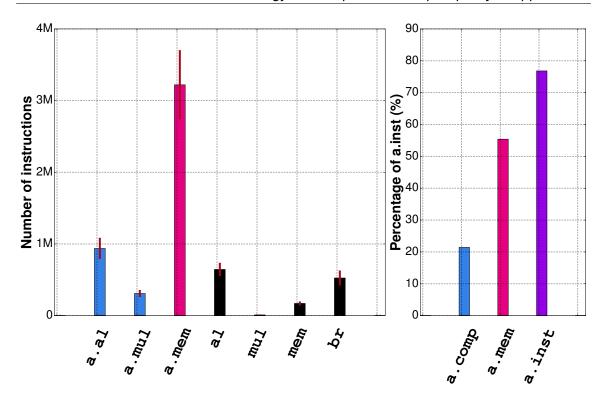

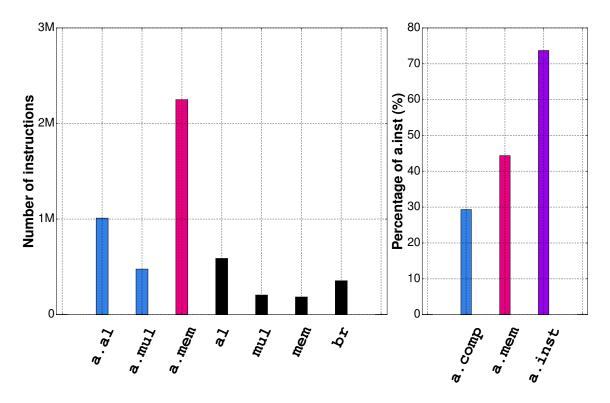

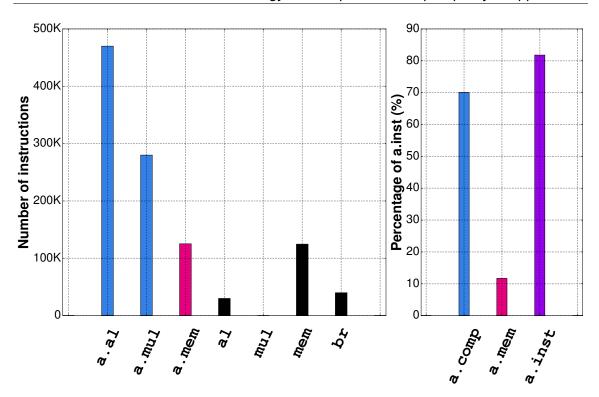

|   |      | 4.3.1     | Instruction breakdown                                              | 71  |

|   |      | 4.3.2     | Energy evaluation                                                  | 75  |

|   | 4.4  | Impac     | t of the reduced width units for both computations and mem-        |     |

|   |      | ory ac    | cesses on energy consumption and output quality of applica-        |     |

|   |      | tions     |                                                                    | 80  |

|   |      | 4.4.1     | Instruction breakdown                                              | 80  |

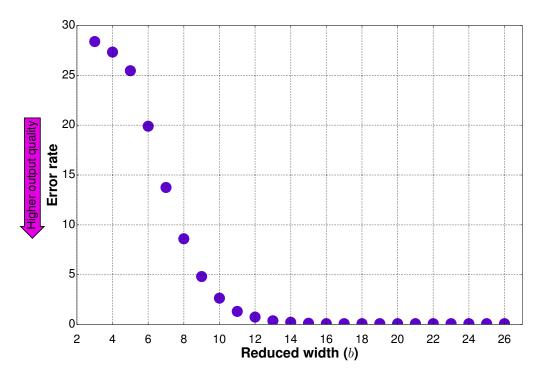

|   |      | 4.4.2     | Output quality evaluation                                          | 82  |

|   |      | 4.4.3     | Output quality vs energy trade-off study                           | 85  |

|   | 4.5  | Chapt     | er summary                                                         | 89  |

| 5 | Glol | bal ene   | rgy model with software and architecture parameters                | 91  |

|   | 5.1  | Globa     | l energy model                                                     | 92  |

|   |      | 5.1.1     | Notations                                                          | 92  |

|   |      | 5.1.2     | Energy reduction                                                   | 94  |

|   | 5.2  | Case      | study 1: impact of software parameters                             | 95  |

|   |      | 5.2.1     | Width estimation for a given energy reduction                      | 95  |

|   |      | 5.2.2     | Energy reduction estimation for a given width                      | 97  |

|   | 5.3  | Case      | study 2: impact of hardware units                                  | 99  |

|   | 5.4  | Chapt     | er summary                                                         | 102 |

| 6 | Con  | clusio    | n and future work                                                  | 103 |

| TARI | $\cap \vdash$ | $\cap$ | VITE. | NITC |

|------|---------------|--------|-------|------|

|      |               |        |       |      |

| Publications | 120 |

|--------------|-----|

| Bibliography | 129 |

# INTRODUCTION

#### 1.1 Context

Reducing *energy consumption* is crucial for embedded computing and to deploy new applications as highlighted, for instance, by the power challenge stated in the International Roadmap for Devices and Systems [37]. This reduction is particularly important for the devices of the *Internet of Things* (IoT) since they are often battery powered and may harvest energy in their immediate environment. Such devices have to be designed for being powered-up during many years. Hence every opportunity for *reducing* their energy consumption should be taken into account.

The loT is a *global network of numerous devices* including *sensors* (*e.g.* smoke detectors, microphones, antennas, light detectors), *actuators* (*e.g.* motors, speakers, lights) and *computers* (*e.g.* microcontrollers, data loggers, small multicore processors). These devices are dispersed into the environment or embedded in everyday objects (*e.g.* smartphones, tablets, connected watches). They exchange various types of informations from a few bits to larger data with possible connections to the cloud. See [43] for more details. IoT devices are used in many applications from various domains such as building and home automation, emergency notification systems, transportation systems, bio-medical systems, gaming and entertainment applications. Computations in IoT devices have to comply with strong resource constraints such as power consumption (due to battery limits), silicon area (for reducing fabrication costs) and also timings (to ensure service quality). Reducing the energy consumption during the global design of IoT services is a major challenge to increase the battery life of the devices.

Recently many applications and systems based on various *approximation* solutions have emerged. Some approximations can be applied due to the natural robustness of the applications or the algorithms to small errors. IoT devices collect data acquired by sensors in their environment, process and aggregate those

data into compact messages sent to a higher-level system. These sensors data are subject to inherent variations and noises (*e.g.* measurement noise(s)). For instance, small differences for a few pixels over an image do not change its informational content. Processing all of those data with the maximal precision (*i.e.* width of the operands in operators) or with the maximal intended accuracy (*e.g.* algorithms with the higher quality) allowed by the circuit can be wasteful. For instance, temperature data for home automation may not require a large dynamic and accuracy.

Approximate computing is a field that explores various methods to reduce some computation costs, such as power consumption, execution time or silicon area, by allowing, ideally small, degradations during intermediate computations without compromising the quality of the final result [92, 12, 53]. Examples of error-tolerant applications amenable to approximate computing are: signal and image recognition, mining, fuzzy search, lossy compression, multimedia, data analytics, *etc.* Approximate computing evolved along three main directions: hardware, applications, and analysis.

First, on the hardware side, the literature advanced from switches and gates [62, 64], towards arithmetic operators [35, 61], and finally to dedicated accelerators [55, 33]. Many types of approximate hardware units are proposed, see [18] for a complete study. Whereas some computation kernels can benefit from hardware accelerators, another direction is to evaluate the interest of *integrating approximate* hardware units into a general purpose embedded processor. Using this type of flexible solution, multiple applications and kernels could potentially benefit from these approximate units, without the need to build a specific accelerator for only one kernel. Therefore one of the main question in this thesis is: would IoT applications benefit from a small general purpose processor containing functional units with a reduced width?

Second, on the application side, several types of work are proposed. For instance, algorithmic modifications are proposed to reduce the number of operations required to solve a problem by skipping loop iterations or instructions [17, 76]. These modifications lead to good initial energy reductions. In this work, we consider a reference implementation of an algorithm and we investigate how to reduce the energy consumption further using an embedded processor equipped with reduced width units. Furthermore, new programming models and data-types

are proposed to express approximations in a high-level language [74, 73]. Compiler support for approximate computing targets either code generation for specific programming models [74, 68], or introduce static approximations in a conventional source code [67, 14]. Methods for runtime control are also implemented to manage the output quality and the energy consumption during the execution of a program [39, 94].

Some programming and compiler methods can be beneficial to an embedded processor with reduced width instructions. For this purpose, we build a set of tools around the RISC-V environment [10] for program annotation, compilation and simulation. We aim to enable fast exploration of applications and kernels, without necessarily claiming novelty at this level. Future work will explore which programming support and compiler level optimizations are more suitable for this task.

Third, to evaluate the impact of approximations in complete applications, a growing number of works deal with methods and tools for analyzing errors in some computation kernels [72, 65]. This type of approaches may also involve algorithmic changes. Some formal error-analysis methods are proposed, however intensive simulations are still required for large workloads and realistic applications [21]. As this is not the main topic of this thesis, we use simulations to evaluate the output quality for various applications executed on our modified processor.

Energy consumption estimations and models are important to evaluate some trade-offs between the output quality and the actual energy reduction, although this topic is not central to approximate computing. Complete and accurate energy models for processor cores and memories are important but they are hard to obtain from the literature. The thesis was carried out in CEA Leti where we have an internal, private, implementation of a RISC (reduced instruction set computer) 32-bit processor in a test chip. We used our internal data from the test chip measurements integrated into some power models from the literature [61] to construct our energy model for our processor at the instruction level.

Numerous low-power embedded processors do not include floating-point units because the hardware implementation of a floating-point support requires a higher silicon area and power consumption than fixed-point or integer ones. A recent work by Barrois *et al.* [18] show that, for some particular workloads such as K-means, floating-point operations on a reduced width (*e.g.* 8-bit) are more efficient than

fixed-point solutions and with larger width (*e.g.* 16-bit) the fixed-point operations are more efficient than the floating-point operations. As we aim to study applications running on a general embedded processor, we stick to conventional cores with integer or fixed-point units.

### 1.2 Problem statement

As introduced above, the main goal of this thesis is to determine whether IoT applications would benefit from a general purpose processor core equipped with reduced width units for approximate computing. This general question implies to answer several more detailed questions stated below.

In the current literature, the evaluation of approximate arithmetic operators in general, and for reduced width ones in particular, is only performed for standalone units (*i.e.* not embedded in a processor running a complete application). In this stand-alone context, approximate operators can lead to important energy reductions, for instance up to 58% in [35]. But, in complete applications running in a general purpose processor not all operations can be approximated. Subsequently, one question in our more complete context is: *how much global energy reduction can be obtained on complete applications with such approximate units embedded in a processor?*

In approximate computing, most of the functional units studied in the state of the art are adders and multipliers. However the energy evaluation of full width (e.g. 32 bits) arithmetic and data-memory operations in [54] and [82] indicates that data-memory operations may consume more than 2 times the energy of arithmetic ones in current circuits technologies. Hence we investigate the extension of the reduced width principle to data-memory units. Here another question is: to which extent both approximate arithmetic and data-memory units impact the energy consumption and the result quality of a given application executed in our processor?

Finally, various optimizations can be performed on the hardware or/and on the software parts of a complete system leading to very different impacts on the global energy reduction. Not all application parts are amenable to approximations. Currently, there is a lack of general models providing an early insight into the global energy reduction offered by approximate computing methods (in software or/and in hardware). It would be interesting to have simple and relevant models such as

the Amdahl's law for speedup evaluation in parallel computers. For a given a set of applications, another question is: when and where implementing reduced width units is worthwhile? More precisely, which processor units impact the most the energy consumption, and can they benefit from reduced width approximations in hardware? Similarly on the software side, another question is: what software characteristics impact the most the global power consumption? For example, the ratio between memory and computation operations may be a key factor to estimate the power gain when using reduced width units.

### 1.3 Contributions

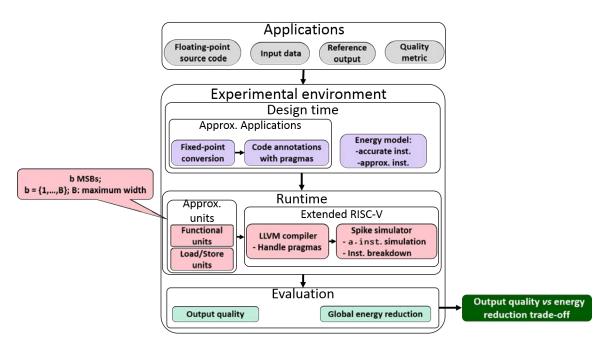

Our first contribution is the evaluation of some trade-offs between the application output quality and the energy consumed by an embedded general purpose processor extended with approximate units. We target a platform composed of a RISC-V processor core [10] coupled with a data and an instruction memory. The RISC-V is an open source processor which allows us to easily extend compilation and simulation tools needed for our exploration. The RISC-V supports instruction set architecture (ISA) extensions. Then, we extend the RISC-V with approximate units where the width is reduced. In these reduced width units, the operations, for both computations and data-memory accesses, are performed on a given number of most significant bits configurable at runtime.

We propose a set of annotations and an instrumentation tool to ease our experimental investigations. During an internship, Tiago Trevisan Jost implemented a compiler support to handle *pragmas* added in the source code and he extends the RISC-V simulator [11] with profiling tools that return statistics including the number of executed instructions of a given type [81]. This work was put in perspective and integrated with an energy model proposed in this thesis. We construct an energy model for each reduced width instruction and we integrated it in the tool-chain to perform application-level energy consumption estimations.

After testing and validating the extended RISC-V platform, we evaluate the impact of the reduced width integer units on some fixed-point applications. Our objective is to study the trade-offs between the estimated energy reduction and the application quality reported during intensive simulations, with various reduced widths for the units. In this evaluation, we first study the impact of common reduced

arithmetic operators (integer addition and multiplication in our processor). Then we extend the investigation to both computations and data memory accesses with various reduced widths. Our evaluation is performed on a selection of applications from the Axbench benchmark suite [93]: jmeint, Sobel filter and forwardk2j.

We also deal with the impact of the conversion from the floating-point representation into the fixed-point one on the output quality for the tested applications. Most of the benchmarks proposed in the state of the art are implemented in floating-point. Then, we have to convert them into fixed-point for our processor. Using several errors metrics, we evaluate the quality degradation due to this conversion for the selected benchmarks. Our experiments suggest that these applications are suitable for fixed-point computations, the error compared to the initial floating-point solution is acceptable (less than 0.1%) for configured widths from 16 bits and above.

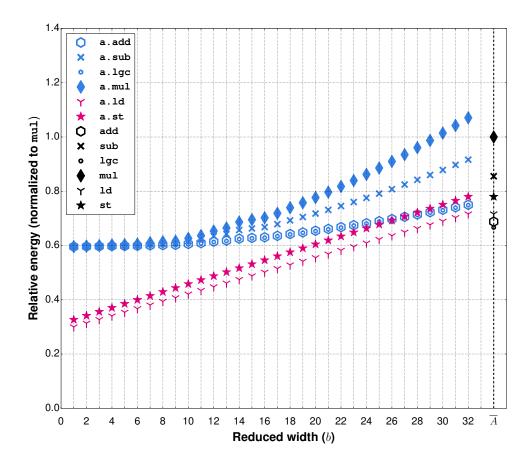

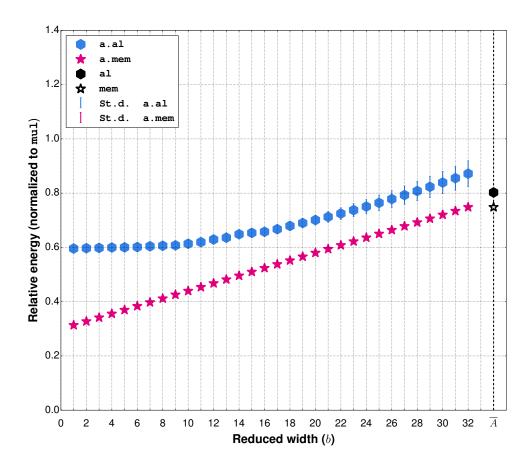

Our results show an energy reduction, for the tested applications executed with reduced width units for both computations and data-memory accesses, improved up to 14%, compared to the reduction obtained using only reduced width units for addition and multiplication. This improvement is due to the fact that all tested applications contain other types of instructions than addition and multiplication, *e.g.* numerous memory accesses, <code>load</code> and <code>store</code>. Extending the reduced width principle to the data-memory unit decreases a lot the global energy consumption. We can conclude that a general purpose processor extended with reduced width units must integrate both computations and data-memory approximate units. Using approximate units only for computations lead a very small power gain.

Our second contribution is a global energy model for both hardware and software designers to have an early insight into the application-level energy consumption. Our model includes both software parameters and hardware architecture ones. The software parameters are the percentages of reduced width operations for both computations and data-memory accesses and the width required for some target output quality. The hardware parameters are the widths of the units and the energy reduction obtained for each type of stand-alone approximate unit. Our global energy model is inspired from Amdahl's law. In parallel computing, the Amdahl's law evaluates the speedup of an application executed in a parallel computer. It clearly shows that both the actual number of processors and the ratio of the parallel and the sequential parts in the program are keys elements. Similarly,

in approximate computing for complete applications (*i.e.* not only small kernels), our model as well as our experimental results show that the energy consumption depends on both the degree of approximation (*i.e.* the configured width in the units in our study) and on the proportion of approximate instructions in a complete program.

# 1.4 Thesis organization

The manuscript is organized in five main chapters as follows.

The **Chapter 2** presents the state of the art. We first discuss the closest related work to the thesis contributions. Second we present several quality metrics and applications in various domains to evaluate the tested approximate computing methods. Then we describe the RISC-V processor targeted in our study. Finally a summary that leads to the thesis contributions is presented.

The **Chapter 3** describes the architecture of the RISC-V processor extended with reduced width units. We first describe the extensions for reduced width computations and data-memory units. Then we present our energy model used to estimate the energy consumption of both full width and reduced width instructions.

The **Chapter 4** investigates the energy *vs* output quality trade-offs of applications executed on our RISC-V extended with reduced width units. At first the tested applications are converted from the floating-point to the fixed-point representation to study the impact of this conversion on the output quality. Then we study the impact of reduced width computations and data-memory accesses on the output quality and on the global energy consumption.

The **Chapter 5** presents a global energy model that includes both software parameters and hardware architecture ones. At first we present a generic energy model. Then we use our global energy model on several applications and we show how a software and a hardware designer can estimate the impact of some optimizations on the global energy reduction.

The **Chapter 6** concludes the thesis. At first the main contributions are summarized, then some future work is proposed.

# STATE OF THE ART

This chapter reviews the literature in the domain of approximate computing. Approximate computing is a field that explores methods to trade computation cost (in terms of execution time, power consumption, or chip area) with degradations in the quality of the computation result. Such degradations should be minimal or acceptable for the application concerned. The means to realize this trade-off are multiple: changing the algorithm, skipping operations, reducing the arithmetic precision, embedding memory blocks that have a non-negligible probability to lose their state, etc. As approximate computing is not yet a well established field, the terminology is not yet widely adopted. The idea of accepting errors in operations is present in many domains, and it may be referred to as:

- Inexact computing: "designing unreliable hardware and computing systems that are useful for unreliable computing elements while garnering resource savings in return" [62]. Palem, Enz and their collaborators explore the energy saving limits of what they call inexact circuits [63], [64], [45]. The studies are performed at a fundamental physical level, e.g. network of switches including AND, OR and NOT gates, and further build inexact arithmetic operators, e.g. additions, and kernels, e.g. FFT.

- Probabilistic computing: "energy spent by the processing units is lowered, resulting in an increase of the probability that some operations might go wrong" [30]. George et al. from Georgia Institute of Technology, USA, explore the potential, in terms of energy reduction, of the probabilistic arithmetic units such as adders and multipliers. In these units, the circuits supply voltage is lowered proportionally to the output errors. The probabilistic arithmetic units are used to implement an FFT reducing the energy by a factor of 5.

- Fault-tolerant computing: "the ability of computing in a presence of faults to reduce the resource costs" [71]. This concept is already investigated for

- a long time [71, 60], and it is applied by different communities in hardware and software. Building fault-tolerant systems requires to analyze the types of errors tolerated and the components reliable for fault-tolerant computing [16], [51], which is rather close to what approximate computing requires.

- Stochastic computing: "The ability to exploit the statistical nature of application-level performance metrics and to match it to the statistical attributes of the underlying device and circuit fabrics" [75]. Solutions for stochastic computing are proposed by various communities. For example Shanbhag and this team, from Illinois University, Urbana, USA, describe the potential in terms of performance and energy reduction in the design of non-ideal circuits, *i.e.* circuits designed for error-tolerant operations [75]. The authors raise also the challenges related to the design of computer aided design (CAD) for stochastic computing, *e.g.* develop techniques for mapping software programs onto programmable processors. Xiu et al. from Purdue University, USA, explore numerical methods for stochastic computations, *e.g.* Monte Carlo [91].

- *Imprecise computing*: "The approach which enables programs to produce results that are not correct using less time or resources" [31]. Imprecise computing [46] is oftenly employed interchangeably with approximate computing [46, 31, 90]. This term seems to be preferred in the real-time domain.

- Significance-driven computing: "the ability to maximize quality while meeting user-specified energy constraints" [83]. The term is coined by with a team from Thessaly university, Greece and Queen's university Belfast, United Kingdom [83, 66, 84]. The authors propose a programming framework for the investigation of the energy reduction and the output quality of software programs. The framework includes a programming model with pragmas directives to annotate the source code, a compiler support that handles the pragmas directives and a runtime controller that makes decisions at runtime. The pragmas directives indicate the relative importance of the tasks and allow the runtime controller to execute the approximated version of a given source code, provided by the programmers.

Our work investigates the impact of reduced width arithmetic operations on applications. As such, it may fall under the name of *significance-driven computing* or *imprecise computing*.

This chapter is organized as follows. Since our study focuses on the reduced width, we first describe the numerical data representation formats used in the approximate computing methods in Section 2.1. Second we present algorithmic approximations applied in both hardware and software solutions in Section 2.2. Third we present the hardware blocks for approximate computing in Section 2.3, and the software-level solutions for approximate computing including programming and compiler support and runtime control in Section 2.4. Then we describe the benchmark applications and the quality metrics for evaluation of our approximation strategy in Section 2.5. Then we present the target processor to execute these applications in Section 2.6. Finally we present the energy model estimated to evaluate the energy consumption of various instructions in Section 2.7. Section 2.8 summarizes the chapter.

## 2.1 Numerical data representation

In a computer, real numbers (*i.e.* reals) are typically encoded on a finite number of bits. The two common number formats are: the floating-point representation and the fixed-point one. Because the width of a given format is finite, not all reals can be represented, thus, for some numbers, rounding is required. Several rounding modes exist. For an in-depth presentation of real numbers and the associated arithmetic we refer the reader to [56]. In what follows we introduce the basic concepts necessary to understand the rest of the thesis.

# 2.1.1 Floating-point

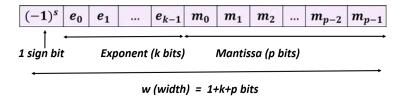

The number x is represented in floating-point by three bit fields, as presented in Figure 2.1:

- sign s; s = 0 if x > 0 and s = 1 if x < 0;

- exponent e; e is an integer such that  $e_{min} < e < e_{max}$ ;  $e_{min}$  is the smallest possible exponent and  $e_{max}$  is the largest possible exponent;

- significant (or mantissa) m; m has one bit before the radix point and at most p-1 bits after; p is the precision: the number of bits of the mantissa.

Figure 2.1: Floating-point representation

$$x = (-1)^s \times m_0 \cdot m_1 m_2 \dots m_{p-1} \times 2^e \tag{2.1}$$

#### **Rounding modes**

The rounding modes to represent a number (x) in a given format are:

- rounding towards  $-\infty$  ( $R_-(x)$ ): returns the largest machine number that is less than or equal to x;

- rounding towards  $+\infty$  ( $R_+(x)$ ): returns the smallest machine number that is greater than or equal to x;

- rounding towards 0 ( $R_0(x)$ ): is equivalent to  $R_-(x)$  if  $x \ge 0$  and to  $R_+(x)$  if  $x \le 0$ ;

- rounding to nearest: returns the closest machine number to x; if x is equidistant to two consecutive machine numbers, the result could be: the number that is away from 0, the even number, or the odd one.

## 2.1.2 Fixed-point

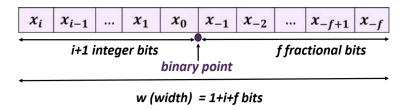

The number x is represented in fixed-point by a fixed number of bits before and after the binary point, as presented in Figure 2.2. The fixed-point format consists of:

- an integer part represented on "i + 1" bits including the signed bit that is the most significant bit  $(x_i)$

- a fractional part represented on "f" bits

• a width, that is the total number of bits: w = 1 + i + f

Figure 2.2: Fixed-point representation

$$x = \sum_{k=-f}^{i+1} (x_k \times 2^k)$$

(2.2)

The same rounding modes as ones presented above in Sub-section 2.1.1 can be used in the fixed-point representation.

The conversion from one format to another is possible. The direction of the conversion in embedded systems is mostly from the floating-point representation to the fixed-point one. For example, [50] proposes a methodology for the floating-to-fixed-point conversion for software implementations for DSP architectures. The aim is to determine the fixed-point specification minimizing a program source code execution time for a given accuracy constraint. Fixed-point libraries, proposed to help programmers implementing their applications, are compared in what follows.

#### **Fixed-point libraries**

Libfixmath, a C/C++ library [1], implements all mathematical functions such as trigonometric functions, logarithm and exponential functions, root square function and arithmetic operators. However the library handles only the format Q32.16 for data representation, *i.e.* w = 32 and f = 16. The smallest and the largest width in Libfixmath is 32 bits and the rounding mode is the rounding towards  $+\infty$ .

The Fixed Point Class C++ [2] implements the cosines and sinus functions, the exponential and the root square functions and the arithmetic operators. The format Qw.f is represented with  $w \in \{8, 16, 32\}$  and each of the three w values includes a number of fractional bits f, with  $f \in \{1, 2, \dots, 8\}$ ,  $\{1, 2, \dots 16\}$  or  $\{1, 2, \dots 32\}$ ,

respectively. In Fixed Point Class, the smallest width is equal to 8 bits and the largest width is 32 bits and the rounding mode is the rounding towards  $+\infty$ .

The MFixedPoint C/C++ library [3] implements only arithmetic operators. The width of the format Qw.f is represented with  $w \in \{32,64\}$  and  $f \in \{1,2,...32\}$  or  $\{1,2,...64\}$ , respectively. In MFixedPoint, the smallest width is equal to 32 bits and the largest width is 64 bits and the rounding mode is the rounding towards  $+\infty$ .

Libfi, a C/C++ library [4] implements only arithmetic operators. The represented formats in Libfi are more flexible than the above ones: the width does not have to be a power of two:  $w \in \{2, 3, ..., 32\}$  and  $f \in \{1, 2, ...32\}$ .

In Libfi, the overflow behavior and the rounding mode are customizable. Libfi proposes a data-type format that allows to handle five parameters:

- *TOTAL\_WIDTH*: total number of bits in binary representation, including the sign for signed numbers; it corresponds to w in the Qw.f format;

- FRACTION\_WIDTH: number of fractional bits; it corresponds to f in the Qw.f format;

- SIGNEDNESS: Fi::SIGNED for signed numbers; SIGNEDNESS:Fi::UNSIGNED for unsigned numbers;

- *OVERFLOW*: behavior when a number overflows the range representable with the selected quantization parameters; the valid parameters are:

- Fi::Saturate: saturate the number to the maximum or to the minimum value allowed with the selected quantization parameters;

- Fi::Wrap: wrap the value around when overflow occurs; if we try to increase the largest possible value, the smallest possible value is returned; as opposite, if we try to decrease the smallest possible value, the largest possible value is returned;

- Fi::Throw: when overflow occurs, throw a Fi::PositiveOverflow or a Fi::NegativeOverflow exception, depending on the direction of the overflow;

- Fi::Undefined: the behavior of overflow is undefined; this overflow option is selected when execution speed is more important than the output results;

• ROUNDING: behavior when a number is not representable with the selected quantization parameters. The rounding modes are the same as ones presented in Subsection 2.1.1;

Table 2.1 summarizes the features of each fixed-point library presented above. For each of them, we indicate the types of implemented functions: arithmetic operations and mathematical functions such as trigonometric functions, exponential, square root. Although Libfi implements less functions than others, it allows to make computation in low precision, *e.g.* less than 8 bits and it allows to handle overflow behavior during simulations. In our investigation, we select Libfi which is more flexible than the others libraries. To handle the functions not implemented in the Libfi library an approximation of such functions is performed with Sollya [25] designed for implementation of numerical functions, including the estimation of the mathematical functions in their polynomial versions.

| Libraries         | Arith.   | Math.<br>functions | Low precision $(w < 8)$ | Scalability (w not necessarily a power of 2) | Overflow<br>handled | All rounding modes |

|-------------------|----------|--------------------|-------------------------|----------------------------------------------|---------------------|--------------------|

| Libfixmath        | <b>✓</b> | <b>✓</b>           | X                       | X                                            | X                   | X                  |

| Fixed Point Class | <b>✓</b> | ✓                  | ✓                       | ×                                            | X                   | X                  |

| MFixedPoint       | ✓        | X                  | X                       | ×                                            | X                   | X                  |

| Libfi             | <b>✓</b> | Х                  | ✓                       | ✓                                            | <b>✓</b>            | ✓                  |

Table 2.1: Fixed-point libraries

# 2.2 Algorithmic approximations

A given problem may be solved by multiple algorithms. Approximations can be done at this level by choosing an algorithm with less steps or without mathematical functions that have a costly implementation.

One of the algorithmic approximation approaches applied on both hardware and software solutions is the approximations of the costly mathematical functions with CORDIC [87] or polynoms [42]. For example, [49] estimates the cos(x) and sin(x) functions with a CORDIC-based approach using shifts and additions operations. Other methods such as polynomial approximation are proposed to reduce the computation time due to iterations in CORDIC-based methods.

[42] proposes a polynomial approximation solution. The authors estimate, with additions and multiplications operations, the mathematical functions includ-

ing  $-(\frac{x}{2})log_2(x)$ ,  $cos^{-1}(x)$ ,  $\sqrt{-ln(x)}$ , ln(1+x),  $\frac{1}{(1+x)}$ . The proposed solutions aim to reduce the size of the interval of input data by proposing a segmentation method other than the traditional uniform segmentation, as presented on Fig.2 of the third page of the paper. The experimental results indicate that for more than 8 bits of precision, the area is reduced by a factor of 2 with their segmentation method compared to the uniform one.

One common limitation that we note in the existing methods for mathematical polynomial approximation is the fact that the energy consumption of the studied functions is not evaluated. The metrics to evaluate the effects of the function approximations are for example, the output accuracy [80], the memory size [22].

One of the most implemented methods applied on software solutions is task skipping [17], [77], [76]. The method consists in reducing the number of executed operations for a given program source code. For example, [17] proposes an automatic framework that allows programmers to reduce the energy consumption of the expensive loops. The programmer provides the source code with loop perforation (i.e. with less iterations of the loops than the actual ones) and the function for evaluation of the output quality. For each execution, the output is compared against the expected output to evaluate the quality loss by running the application with less iterations in the loops. The reduction of the number of instructions is implemented with an early termination of the loops when the required quality of result is reached. The experiments are performed on commercial applications and a web-search engine executed on an Intel core 2 Duo (3GHz) processor and an Intel 64-bit Xeon Quad core (2.33 GHz) processor. The results indicate that the energy consumption can be reduced by up to 21% for an error rate equal to 0.27%. We note that the proposed approach allows users to be less involved in the quality of results evaluation and the method improves energy reduction for an acceptable quality of output. The task skipping allows also to reduce the computation time of a given program as indicated in [77]. [77] evaluates the loop perforation technique on a set of applications, e.g. Monte Carlo simulation, search space enumeration, in order to generate source code that produces results with less computations. The experiments are performed on the PARSEC suite [20] that includes image processing, multimedia and scientific applications executed on an Intel Xeon X5460 Quad core processor. The results indicate that for an error less than 5%, the execution

time is reduced by a factor of 2.

Another approach that can be applied on loops and other operations are proposed in [76]. The approach consists in the implementation of a mechanism called *Hardware Redundant Execution (HaRE)*. The *HaRE* allows to reduce the errors on computations by returning in some previous states that are not costly and that have an impact on the program output quality. The *HaRE* allows to activate a task with the pragma *HaRE on* or to avoid a task to be executed with the pragma *HaRE off*. The experiments are performed on machine learning applications executed on Graphite, a simulator for multi-core systems [52]. The results indicate that with an error rate equal to 0.1%, the computation time can be improved by up to 54%.

The above solutions produce good costs reductions, *e.g.* energy consumption, computation time for an acceptable quality of output of the evaluated applications. In this work, we keep the number of program operations and investigate how the energy consumption can be reduced with an acceptable output quality, by executing them with reduced width units embedded in a processor.

## 2.3 Hardware blocks for approximate computing

Decreasing circuit complexity or clocking up less area are ways to reduce the energy consumption in hardware design. Several solutions have been proposed, for example: the approximate accelerators [55], [33] and the approximate operators [35], [61].

The design of arithmetic operators for approximate computing, *e.g.* adders and multipliers, is one of the most common work in the approximate computing community at hardware level. The energy consumption of these operators is reduced by applying methods such as the voltage scaling and the width reduction.

The voltage scaling aims to reduce the circuit's energy consumption. The principle is to increase or decrease the supply voltage depending on the required energy reduction and the target output quality. Several solutions have been proposed *e.g.* [26], [70]. The width reduction at hardware level consists in reducing the number of bits in the design of hardware blocks to reduce their complexity [95],[35].

The proposed arithmetic operators for approximate computing can be grouped into two categories: the fixed width ones and the variable width ones. The difference between the two categories is the fact that the variable width operators can

be reconfigured at runtime and the fixed width operators cannot be changed at runtime.

## 2.3.1 Fixed width adders and multipliers

The fixed width operators are operators in which the precision is not configurable at runtime, *i.e.* the precision does not change with the new parameters, *e.g.* input data, energy budget. Different solutions have been proposed for adders and multipliers.

[95] proposes an adder that consists of two parts: an accurate part and an inaccurate one. For the accurate part, the adder follows the standard addition principles from the least significant bit (LSB) to the most significant bit (MSB). For the inaccurate part another mechanism is applied from MSB to LSB. The mechanism consists in performing the standard one-bit addition if the two bits of the operands are equal to "0" or if the two bits are different from one to another; but when the two bits are equal to "1", all bits in the right part, from this bit are set to "1". The adder is implemented using a library for  $0.18\mu m$  CMOS technology and simulated with a frequency set to 100 MHz. The results indicate 60% of power reduction when compared to the conventional adders. We note that the mechanism applied on the fixed width adders improves the energy reduction and the delay. The limitation of such operators is the fact that it is optimized for a given width configuration.

The design of multipliers is also one of the topic of interest in approximate computing at circuit level. In [40] an approximate multiplier is proposed. It is composed of two parts: a multiplication part in which the standard accurate multiplication is applied and a non-multiplication part in which a special mechanism is applied. The mechanism consists in checking the bit position of each operand. If the two bits are equal to "0", the corresponding bit result is set to "0" and if one or both of the two bits are equal to "1", the process finishes and all result bits that follow are set to "1". The multiplier is implemented using a library for  $0.18\mu m$  CMOS technology and simulated with a frequency set to 100 MHz. The results indicate that, in comparison with the standard multiplier, for a 12-bit multiplier, the power dissipation decreases from 50% to 96% and a reduction of area by a factor of 2.1 for more than 90% of output quality. The results are interesting but we note the same limitations as in the fixed width adders, *i.e.* the complexity in the configurability of the circuits

to fit with parameters such as accuracy, energy savings requirements.

The above operators (adders and multipliers) are energy-efficient and can be configured for a given application. We target a general purpose embedded processor that can execute multiple applications. The fixed width operators are not convenient to handle different widths demands.

## 2.3.2 Variable width adders and multipliers

Variable-width operators are operators in which the precision can be configured at runtime. Several operators are proposed, *e.g.* [86], [38], [35], [61].

[86] presents an adder with an accurate and an inaccurate part. The inaccurate part performs computations with reduced bits in the carry chain. In this adder the output is evaluated at runtime. A signal indicates if the result is equal to the expected one. If the result is not correct, the errors induced by the approximations are corrected by performing the addition on the accurate part. The adder is implemented using a library for  $0.18\mu m$  CMOS technology. The results indicate that the proposed adder can be  $1.5\times-2.5\times$  faster than an accurate adder.

[38] proposes an accuracy-configurable approximate adder (ACA) that includes an error-correction functionality and aims to reduce the number of bits in the carry chain. ACA supports both accurate and inaccurate computations; the accuracy of computation is reconfigurable. The adder is divided into three sub-adders and the middle one corrects the potential errors, as presented on Figure 2 on the second page of the paper. The error detector is implemented with several AND gates. The ACA design is synthesized to a TSMC 65nm cell library with Synopsys Design Compiler. For simulations at gate-level, Cadence NC-Sim is used. The results indicate that the energy can be reduced by up to 30% when compared with the conventional pipelined adder.

[35] proposes a Dynamic Range Unbiased Multiplier for Approximate Applications (DRUM). The parameterizable multiplier is implemented to dynamically tune the precision of computations depending on the accuracy and the power consumption target. The proposed method limits the number of bits by selecting dynamically a range of bits on the two operands. For each operand, the k-1 bits from the most significant bits (MSBs) are selected; the  $k^{th}$  bit is set to 1. The design is synthesized to a TSMC 65nm cell library with Synopsys Design Compiler. The evaluation

of DRUM is performed on a hardware Gaussian filter. The results indicates that for an acceptable accuracy, *i.e.* SNR of 91 dB, the whole Gaussian filter design with DRUM achieves power savings of 58% for k=6 bits.

[61] implements a 16-bit multiplier in which the width is scaled with the voltage scaling method. A given number of LSBs of the operator inputs are set to zero. The method is evaluated on booth multiplier implemented on a 28nm FDSOI standard-cell library from STMicroelectronics. The results indicate that the energy consumption of a 16-bit fixed-point multiplier, at 10 bits is reduced by up to 32%.

The variable width operators solved the issues raised in the fixed width ones, i.e. the configurability at runtime. Although the proposed operators have large energy savings, up to 58%, when evaluated separately, most of them are not evaluated on a complete application. The evaluation of these operators on real applications, are required to have an insight into the global energy reduction for a given program.

# 2.4 Software for approximate computing: programming, compiler and runtime support

The application of the approximate computing techniques at software level requires programming models to express specific data-types for the *approximable* variables. Note that in this thesis, the *approximable* variables refer to the variables in which the approximation leads to acceptable quality degradation. The authors in [74], [68], [73] propose programming and compiler support for approximate computing.

[74] proposes EnerJ, an extension of the Java programming language. EnerJ includes type qualifiers (@Approx and @Precise) to declare the *approximable* variables. The type qualifiers allow to mark *approximable* variables for low-power memory storage operations and approximate operations for computation. The strategy applied in operations for computation is the floating-point width reduction. For the low-power memory storage operations, the applied strategies are the reduction of the supply voltage and the reduction of the refresh rate of the DRAM. EnerJ is evaluated on a set of applications in various domains: SciMark2 suite [5] including scientific kernels, ZXing [6], a bar code reader for mobile devices, jMon-

keyEngine [7], a 2D and 3D game engine that implements triangle intersection problems, ImageJ [8], a program for image processing, Raytracer [9], a 3D renderer that generates images by tracing the path of light as pixel. The evaluated applications are executed on both desktop and mobile environments. The results indicate that with at most 34% of annotated variables, the energy reduction is from 10% to 50% with an acceptable output quality. We note that the proposed extensions for EnerJ are simple to implement by a programmer.

[68] proposes FLEXJAVA, a framework for Java applications that allows programmers to make annotations on the source code to mark the *approximable* parts, as in [74]. Moreover FLEXJAVA handles object-oriented programming concepts, *e.g.* inheritance, polymorphism. The same approximation strategies as [74] are applied both in the computation and memory storage operations (*i.e* floating-point width reduction, reduction of the supply voltage and reduction of the refresh rate). The evaluation is performed on the same applications and platforms as EnerJ. Compared to the EnerJ, FLEXJAVA claims to reduce the programmer efforts in the annotation process: from  $6\times$  to  $12\times$ , because for the same energy reduction, FLEXJAVA reduces the number of required annotations from  $2\times$  to  $17\times$ . We note that FLEXJAVA proposes a safety analysis to identify the sensitive operations.

[73] proposes ACCEPT, a framework that includes C/C++ type qualifiers derived from EnerJ (@Approx and @Precise). The pointer types are not yet handled in the approximation scheme. The approximation strategies are the loop perforation [77], the neural acceleration [28]. ACCEPT is evaluated with the PARSEC parallel benchmark suite [19] in 3 platforms: a standard x86 server, a mobile SoC with an FPGA for neural acceleration, and a low-power embedded sensing device. The results indicate that the speed up is improved by up to  $2.3\times$  on the x86 server, up to  $4.8\times$  on the mobile SoC, and up to  $1.5\times$  on the embedded device for errors less than 10%, acceptable for the evaluated applications.

The above solutions claim a high energy reduction, *i.e.* up to  $2\times$ . To improve the energy reduction (by up to  $2.8\times$ ), other work proposes runtime control solutions. However most of them implement the task skipping techniques [69] or handle the cores for execution (*i.e.* host processor, accelerators) [48].

[69] develops a runtime framework that automatically skips operations, on a given source code during the program execution. The authors target applications

with high volume of data including a reduced-and-rank (RnR) kernel, used in, e.g. video processing, recognition, search and data mining. A RnR kernel allows to perform a reduction operation (e.g. L1-norm, distance computation, dot product) between a given input data vector and a set reference vectors to return a set of reduction outputs. From these outputs, the user deducts the degree of approximation of a given source code. An other approach deducts the degree of approximation of a given source code by studying the correlation between the current input data and a set of previous input data. The experiments are performed on eye detection and clustering applications executed in a hardware extended with additional registers, counters, and control logic. The additional components, synthesized with Synopsys Design Compiler and mapped to a 45nm Open Cell Library, allow to automatically tune the quality knobs. The results indicate that the energy is improved up to  $2.38\times$  and  $2.5\times$  when the quality constraints are relaxed to 2.5% and 5% respectively, acceptable for the evaluated applications. The energy overhead induced by the search of the degree of approximation and by the additional components is around 10% compared to the energy consumption of the original program. We note that the overhead energy costs are acceptable in comparison with the global energy reduction obtained with the method.

[48] implements a predictor that estimates the quality of output degradation of a given program and indicates which source code version (original or approximated) has to be executed. The selected version of the source code to be executed on a host processor or on an approximate accelerator depends on the required quality of output. The methods for the predictor design are a table-based approach and a neural approach. The table-based approach, with a training phase, maps the input data to the corresponding prediction, *e.g.* errors on the quality of output. The neural approach estimates models for quality of output control, with a set of training data. The experiments are performed on a set of applications in various domains: image processing, clustering, 3D gaming, executed on a processor that includes an accurate core and a neural processing unit. The results indicate that for the table-based predictor the energy consumption is reduced by up to  $2.8\times$  for an error of 5% and the neural predictor achieves 17% larger energy reduction than the table-based predictor. We note large energy reduction, however we have no idea about the values of energy overhead costs induced by the runtime process.

The proposed solutions for runtime control mostly investigate the task skipping

technique. To exploit the configurability of the units that we study in our contributions, the runtime control of the data representation could be studied for more energy reduction. Moreover the solutions are mostly for floating-point architectures. Since numerous low-power embedded processors do not include floating-point units because the hardware implementation of a floating-point support requires a higher silicon area and power consumption than fixed-point or integer ones. Barrois *et al.* [18] highlights the advantages of fixed-point operators compared to the floating-point ones, *e.g.* in terms of energy reduction, silicon area. On a real application such as K-means, the floating-point representation with reduced widths (*e.g.* 8 bits) provides more energy reduction. However with larger widths (*e.g.* 16 bits) the fixed-point representation is still less costly in terms of energy consumption compared to the floating-point one. As we aim to study applications running on a general embedded processor, we stick to conventional cores with integer or fixed-point units.

# 2.5 Benchmark applications and quality metrics

The benchmark applications potentially of interest for approximate computing area, for example Mediabench [41], ALPbench [44] which aim at the evaluation of multimedia and communication systems. These suites include applications such as data compression, human machine interface. The San Diego vision benchmark [85] includes applications for features tracking, image segmentation, robot localization. MEVBench [27] includes applications for mobile computer vision. Minebench [57] is a data mining benchmark suite for clustering, classification applications. Axbench [93], a benchmark suite proposed by the approximate computing community, it includes a series of applications from various domains.

We select benchmark applications with available input data and quality metrics, and that tolerate approximations. Thus in this thesis we perform experiments with Axbench applications that provide a large set of input data and quality metrics, and that are specifically implemented to evaluate the impact of an approximate computing method.

#### **Axbench**

Axbench is a suite of CPU and GPU applications proposed to evaluate the impact of the neural network method [28] on the application output quality, the energy consumption and/or the computation time. The CPU applications are more suitable for our investigation. Axbench includes as CPU applications: blackscholes, FFT, inversek2j, forwardk2j, jmeint, jpeg, K-means, Sobel filter.

All the above applications are implemented in floating-point format. We target integer architectures to reduce the computation costs of the floating-point operations on the embedded systems. For each of the evaluated applications, we convert them in fixed-point representation with Libfi presented in Subsection 2.1.2. The errors introduced by the fixed-point conversion are evaluated with metrics presented below.

Most of these applications include complex mathematical functions such as logarithm, exponential, square root, and trigonometric functions, as presented on Table 2.2. Most of the embedded systems do not include floating-point arithmetic unit (FPU). We estimate these functions with polynomial approximation using Sollya [25].

| Applications | Arith. op | Cos/Sin | Tan | Acos/Asin | Atan     | Log      | Exp      | Sqrt     |

|--------------|-----------|---------|-----|-----------|----------|----------|----------|----------|

| Blackscholes | ✓         | Х       | X   | Х         | X        | ✓        | <b>√</b> | ✓        |

| FFT          | <b>✓</b>  | ✓       | X   | Х         | <b>✓</b> | <b>√</b> | X        | <b>√</b> |

| Inversek2j   | ✓         | ✓       | X   | ✓         | X        | X        | X        | Х        |

| Forwardk2j   | ✓         | ✓       | X   | Х         | X        | Х        | X        | Х        |

| Jmeint       | <b>✓</b>  | X       | X   | Х         | X        | Х        | X        | Х        |

| Jpeg         | ✓         | Х       | X   | Х         | X        | X        | X        | ✓        |

| K-means      | ✓         | X       | X   | Х         | X        | X        | X        | ✓        |

| Sobel filter | <b>✓</b>  | X       | X   | Х         | X        | X        | X        | <b>√</b> |

Table 2.2: CPU-Axbench applications

We note that jmeint includes only arithmetic operations. Sobel filter, K-means, jpeg, the image processing applications, include arithmetic operations and the square root function. Blackscholes includes arithmetic operations, logarithm, exponential and square root functions. Other applications, *i.e.* inversek2j, forwardk2j and FFT include arithmetic operations, trigonometric functions. FFT includes the square root function in addition to trigonometric and arithmetic operations.

We choose to study the jmeint application because it includes only arithmetic functions and 2 other applications: the Sobel filter, that includes the square root

function in addition to arithmetic operations, and the forward2j including arithmetic and trigonometric functions. The square root and the trigonometric functions are estimated in polynomial approximations, using the fpminimax function of Sollya.

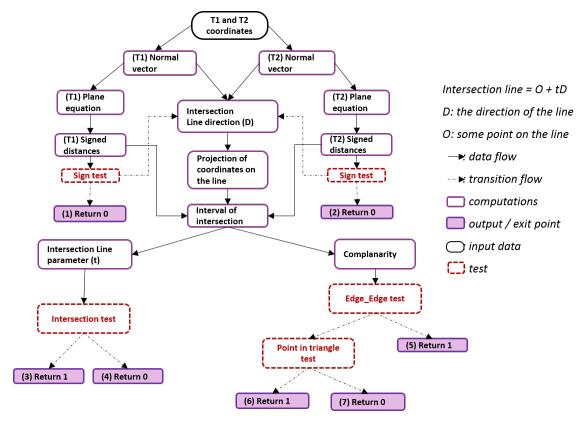

#### **Jmeint application**

Jmeint is an algorithm used in many 3D applications, *e.g.* gaming. Jmeint, with geometric computations, verifies if two 3D-triangles intersect. The input is a pair of triangles' coordinates in 3D-dimensional space and the output is a boolean value which indicates whether the two triangles intersect: 1 if the two triangles intersect and 0 if they do not intersect. The steps of the algorithm are presented on Figure 2.3. To evaluate the quality of output, we compute the error rate that is the ratio between the number of correct outputs and the total number of outputs.

Figure 2.3: Jmeint algorithm steps

#### **Jmeint quality metrics**

To evaluate the output quality of the jmeint application, we compute the error rate. The error rate is an error metric that indicates the frequency of errors in a method evaluation. For jmeint, we compute the error rate between the vector of outputs returned by the approximated program and the vector of outputs returned by the original program. The formula of the error rate is:

$$\epsilon = \frac{N_{inc}}{N_t} \tag{2.3}$$

where  $N_{inc}$  is the number of incorrect outputs and  $N_t$  is the number total of outputs.  $N_{inc}$  is estimated with the *hamming distance*. The *hamming distance* between two words (of the same length) is the number of places where the digits are different, *i.e.* the number of positions where one is equal to 0 and the other equal to 1 and vice versa [79]. The two words in jmeint correspond to the two compared vectors of outputs.

Example: let's consider a = 010110, b = 111101, the hamming distance d = 1+0+1+0+1+1=4.

#### Sobel filter application

The Sobel filter is a kernel for image processing and computer vision applications, particularly for edge detection algorithms. Edge detection is an image processing technique to discover the boundaries between regions in an image.

The input is a RGB image and the output is a gray-scale image (PNG format) in which the edges are emphasized, as presented on Figure 2.4. The image gradient of each pixel is calculated by convolving the image with a pair of filters (horizontal and vertical filters), that are  $3\times 3$  matrix.

#### Sobel filter quality metrics

The image quality evaluation is an issue in image processing applications, for that, several metrics are proposed in this area, *e.g.* the RMSE, the PSNR and the SSIM. The metrics values are computed with the parameters of the two compared images, *i.e.* the image returned by the reference program and the image returned by the approximated one.

(a) Sobel filter input

(b) Sobel filter output

Figure 2.4: Sobel filter input/output

The RMSE [78] and the PSNR [78] estimate the absolute errors between pixels of two compared images but are less correlated to human perception of image quality compared to the SSIM metric [88].

Let x and y be the matrix of the 2 compared images.

RMSE =

$$\sqrt{\frac{1}{N} \sum_{i=1}^{N} (x_i - y_i)}$$

(2.4)

where:

- $N = 3 \times height \times weight$

- 3 is the number of pixel components: r, g, b;

- *height* and *width* are the dimensions of the images;

- *i* is the position of the pixel component on the images;

- $x_i$  is the reference pixel component value,  $y_i$  is the approximated pixel component value;

$$PSNR = 20 \times \log_{10}(\frac{L}{RMSE})$$

(2.5)

where L is the dynamic range of the pixel values (e.g. 255 for 8-bit images).

Let x and y the 2 compared images:

SSIM

$$(x, y) = \frac{(2\mu_x \mu_y + C_1)(2\sigma_{xy} + C_2)}{(\mu_x^2 + \mu_y^2 + C_1)(\sigma_x^2 + \sigma_y^2 + C_2)}$$

(2.6)

where:

- $\mu_x$  and  $\mu_y$  are the mean pixel values of respectively the image x and the image y;

- $\sigma_x$  and  $\sigma_y$  are the standard deviations between pixel values of respectively the image x and the image y;

- $\sigma_{xy}$  is the covariance of the two images x and y;

- $C_1=(K_1L)^2$  and  $C_2=(K_2L)^2$ , included to avoid instability when  $\mu_x^2+\mu_y^2$  and  $\sigma_x^2+\sigma_y^2$  are very close to zero;

- $K_1 = 0.01$ ,  $K_2 = 0.03$  and L is the dynamic range of the pixel values (255 for 8-bit images).

#### Forwardk2j application

Forwardk2j is a kernel for robotic applications. It aims to compute the positions of a robot's end-effector with the angles of the 2-joint robotic arm.

Forwardk2j takes as input the angles of the 2-joint robotic arm ( $\Theta_1$  and  $\Theta_2$ ) and computes the position of the end-effector of the 2-joint robotic arm (x and y).

#### Forwardk2j quality metrics

To evaluate the quality of output in the forwardk2j application, we compute the *mean relative error (MRE)* for each coordinate between the outputs returned by the approximated program and the outputs returned by the original program.

MRE =

$$\frac{1}{N} \sum_{i=1}^{N} \left| \frac{x_i - y_i}{x_i} \right|$$

(2.7)

where N is the total number of data, x the set of original reference values, y the set of approximated values.

Note that computing the *mean relative error (MRE)* with a series of very small or null expected values (that are the denominators) is an issue in mean relative error computations. To overcome these issues, there are some other measures

proposed in the literature, e.g. Mean Absolute Scaled Error (MASE) [29], Symmetric Mean Absolute Percentage Error (SMAPE) [32].

The *standard deviation* is computed on the values obtained with the above metrics (*i.e. RMSE*, *PSNR*, *SSIM*, *MRE*) for the purpose of evaluating the dispersion of a set data around the mean value. The lower the standard deviation, the most the data are closed to the mean, *i.e.* low differences between the elements of the studied data set.

$$\sigma = \sqrt{\frac{\sum_{i=1}^{N} (x_i - \bar{x})^2}{N - 1}}$$

(2.8)

where  $\bar{x}$  is the mean value of the data set.

# 2.6 RISC-V processor

This section presents the processor core baseline that we consider in our experiments. We utilize an open source RISC-V core [10]. The RISC-V community provides an open Instruction Set Architecture (ISA) specification and a large set of tools to simulate and synthesize RISC-V processor cores, as well as a large software tools base to program, debug, and test applications for RISC-V.

One can customize a RISC-V processor core to include, for example, integer multiply/divide, single and double precision floating-point arithmetic. The processor can work on 32, 64, or 128 bits. In the context of this thesis, we are interested in a 32-bit integer processor, with code-name "RV32I base" in the RISC-V terms. From the proposed basic instruction formats [89], we use R-type, I-type and, S-type, described below.

#### 2.6.1 RV32I instruction formats in our work

The R-type format is for instructions with two source registers and one destination register, *e.g.* addition (add), subtraction (sub). The I-type is for instructions with one source and one destination register, *e.g.* load word (lw), addition with an immediate value (addi). The S-type format has two source registers and an immediate destination, *e.g.* conditional branch instructions.

For the R-type format, the bits[31:25] (i.e. the field funct) indicate the type of

| 3 | 1 25      | 24 20 | 19 15 | 14 12  | 11 7     | 6 0    |        |

|---|-----------|-------|-------|--------|----------|--------|--------|

|   | funct     | rs2   | rs1   | funct3 | rd       | opcode | R-type |

|   |           |       |       |        |          |        | ,      |

|   | imm[1     | 1:0]  | rs1   | funct3 | rd       | opcode | I-type |

|   |           |       |       |        |          |        |        |

|   | imm[11:5] | rs2   | rs1   | funct3 | imm[4:0] | opcode | S-type |

Figure 2.5: 32-bit RISC-V base instruction formats in our work [89]

operations to be executed, the bits[24:20] (*i.e.* the field rs2) correspond to one source register and the bits[19:15] (*i.e.* the field rs1) to the other source register, the bits[14:12] (*i.e.* the field funct3) inform to the processor which registers from the registers source and destination communicate with an external accelerator, the bits[11:7] (*i.e.* the field rd) correspond to the destination register, the bits[6:0] (*i.e.* the field opcode) are for the code of the executed operation.

The I-type format has a imm[11:0] field in the bits[31:19] for the immediate values to compute with the value of the register rs1. The format includes only one source register file that corresponds to the bits[19:15]. From 19 bits and below the I-type and the R-type have the same formats.

The S-type has the same formats as the R-type, except the fields funct and rd in R-type, that correspond to imm[11:5] and imm[4:0] for the immediate values in S-type.

# 2.6.2 RISC-V base opcodes map

An opcode is mapped with each of the instructions as presented on Table 2.3.

The opcodes of the operations are different from one operation to another. The opcode targeted *reserved* are only for the standard extensions of the RISC-V. Hence these opcodes cannot be used for external extensions added in the standard RISC-V ISA. Inversely, the opcodes *custom-0* and *custom-1* are recommended for the external extensions and are avoided for the standard extensions of the RISC-V. The opcodes *custom-2/rv128* and *custom-3/rv128* are reserved for the RV128 format and can utilized for the custom instruction-set extensions in RV32 and RV64.

In this thesis, we use the opcodes *custom-0* and *custom-1* to extend the standard RISC-V with reduced width units.

inst[4:2] 000 001 010 100 011 101 110 111 inst[6:5] LOAD-FP | custom-0|MISC-MEM | OP-IMM | AUIPC OP-IMM-32 LOAD 48b 00 01 STORE STORE-FP custom-1 AMO OP LUI OP-32 64b **NMADD** 10 MADD **MSUB NMSUB** OP-FP reserved custom-2/ 48b rv128 11 BRANCH JALR reserved JAL SYSTEM reserved custom-3/ rv128  $\geq$  80b

Table 2.3: RISC-V base opcode map [89]

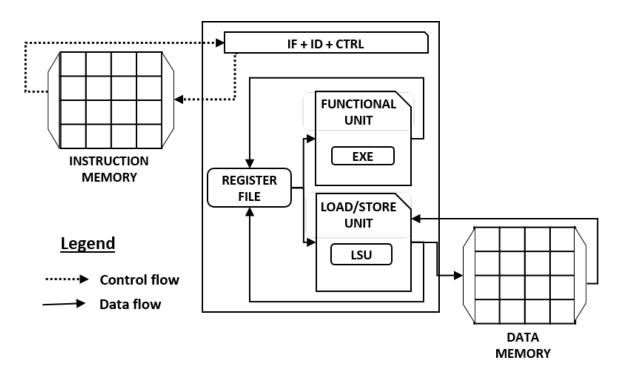

#### 2.6.3 RISC-V architecture

The RV32I base can be implemented in several ways. Figure 2.6 presents the RISC-V architecture. We consider a pipeline with the following classic stages: instruction fetch (IF) to bring the instruction from the instruction memory at the address supplied by the program counter (PC); instruction decode (ID) to decode the instruction, *i.e.* interpret the type of instruction and specify the register operands; execution (EXE) to compute the arithmetic and logic instructions results or to compute addresses for memory instructions, *i.e.* load and store; full width load/store unit (LSU) to load/store the data from/in the data-memory. Note that in our investigation, the memory does not refer to both the *dynamic random access memory (DRAM)* and the *static random access memory (SRAM)*, we only consider the SRAM.

The standard instructions in the original RISC-V processor could be grouped into categories:

- arithmetic and logic instructions: addition (add), subtraction (sub), multiplication (mul), division (div), negate value (neg), shift left logical (sll), shift right logical (srl),...

- branch instructions: branch on equal (beq), branch on less than (blt), branch

Figure 2.6: RISC-V Architecture

on greater than (bgt), jump (j),...

- data transfer instructions: load immediate (li), load word (lw), store word (sw), move (mv),

- comparison instructions: set equal (seq), set not equal (sne), set less than (slt), greater than (sgt),...

# 2.7 Energy models

For estimation of the global energy consumption of a given application, several energy models have been applied on various architectures, *e.g.* [54] and [82] estimate the accurate values of energy consumption of the arithmetic and memory instructions.

[54] measures the contribution of the data transfer and arithmetic instructions on the total power consumption of the AMD and Intel systems. The energy consumption of each instruction is measured: for double and single floating-point instructions and for access cache and RAM. The results indicates that the data

transfer power consumption is higher in the AMD architecture, *i.e.*  $2.8\times$ , compared to the Intel power consumption of the data transfer. For Intel, we note that a byte transfer on the RAM consumes  $2.9\times$  more than a double precision addition and  $2.6\times$  more than a double precision multiplication.

[82] proposes an energy model for ARM instructions, based on the energy measurements on two different ARM processors: Cortex-A7 and Cortex-A15. The measurements are obtained with the voltage/current sensors provided by the ODROID XU+E big.LITTLE Platform [34]. The measurements are performed on several types of instructions: integer, float and, double. We note that for the integer instructions, on the smallest memory (4KB), the load and store instructions consume  $2\times$  more than the additions and multiplications and  $2.5\times$  for a higher memory (*i.e.* 256KB). For the double instructions, on the smallest memory (4KB), the load and store instructions consume  $2\times$  more than the additions and have approximately the same values as the multiplications energy consumption.

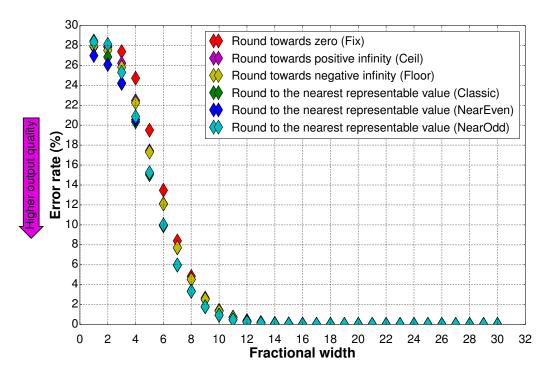

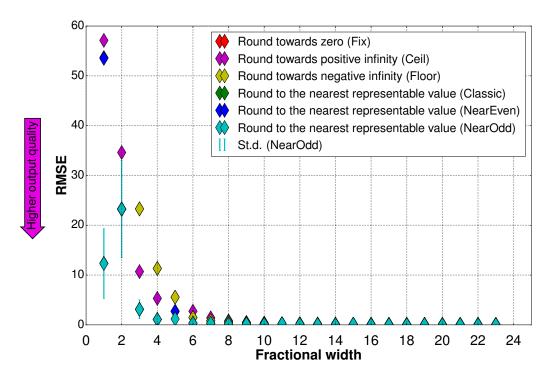

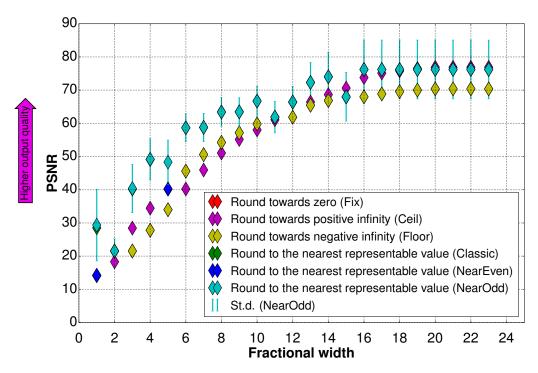

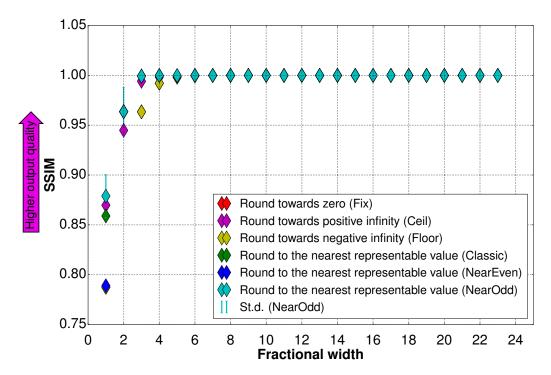

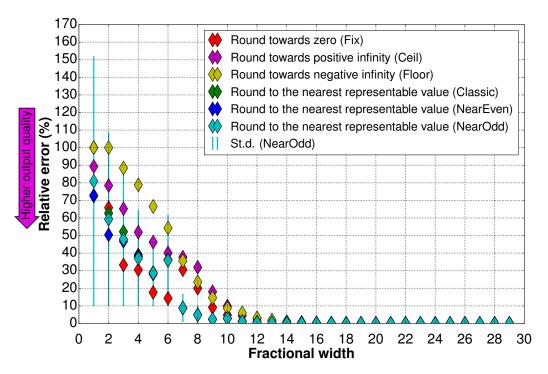

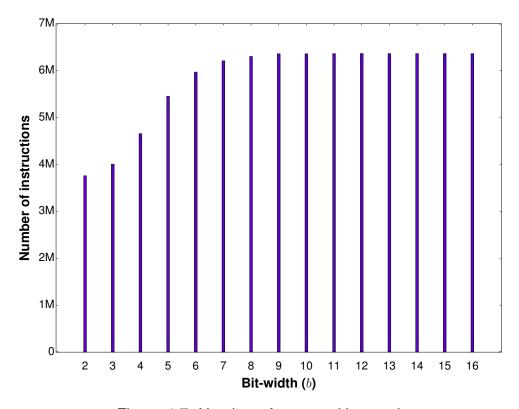

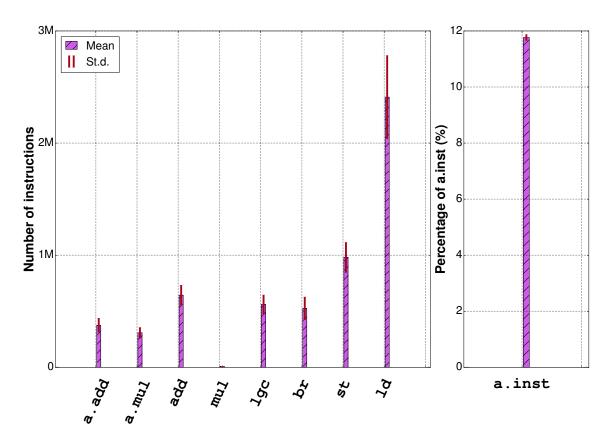

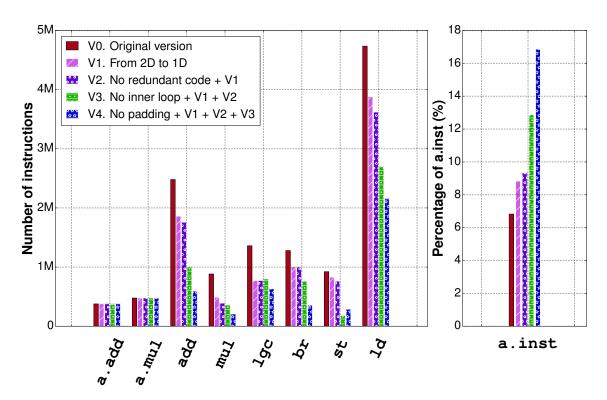

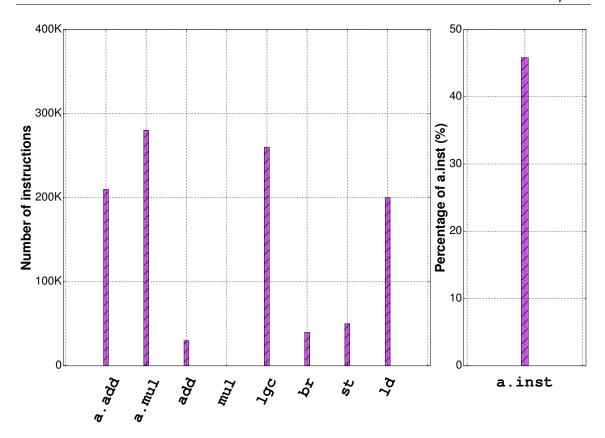

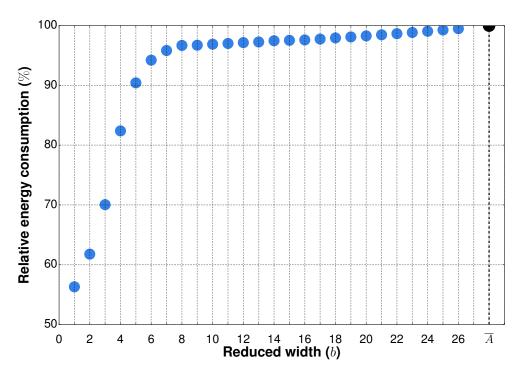

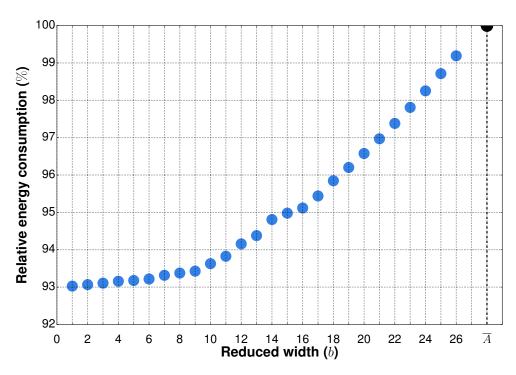

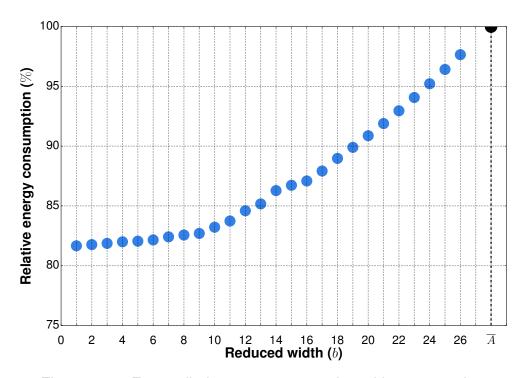

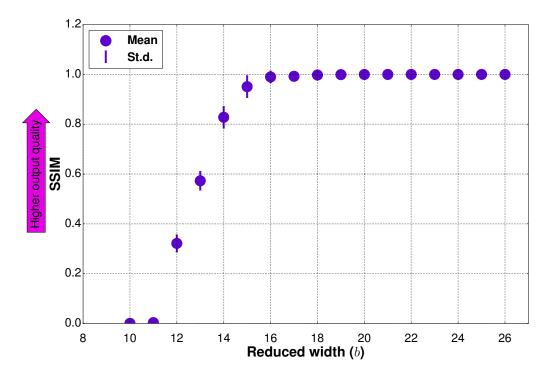

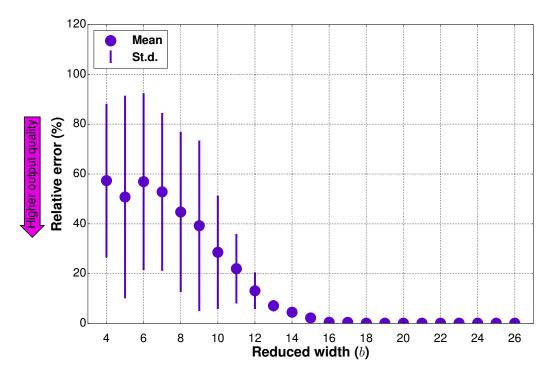

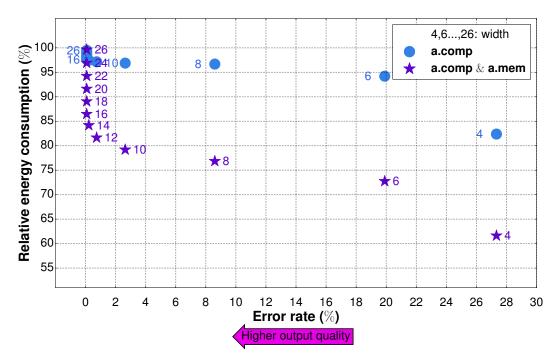

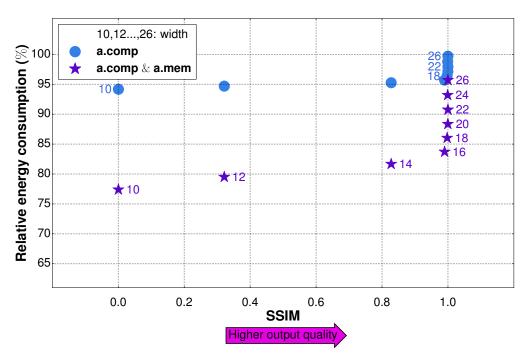

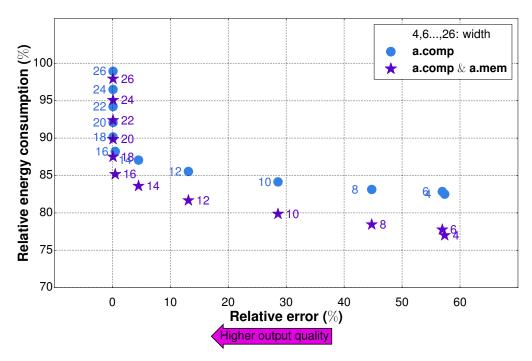

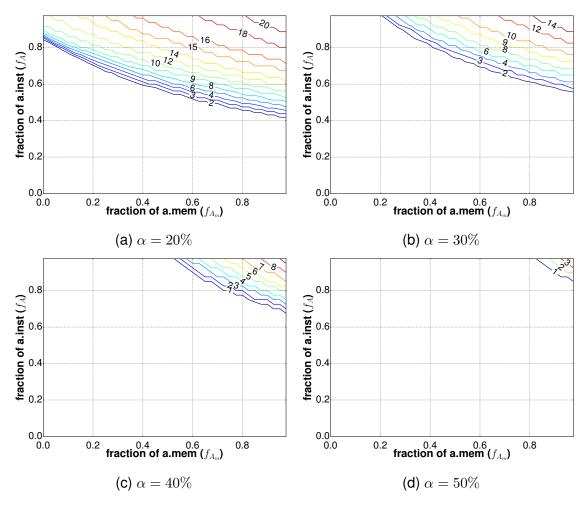

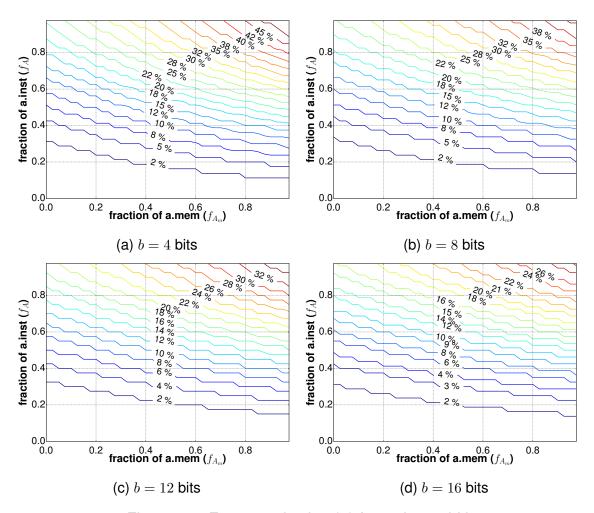

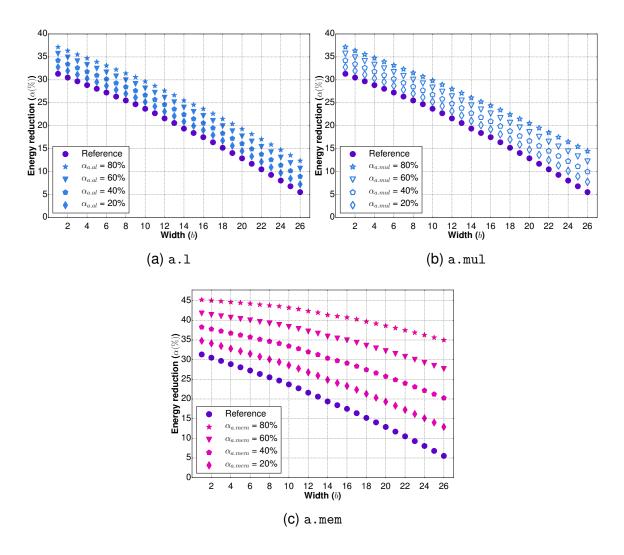

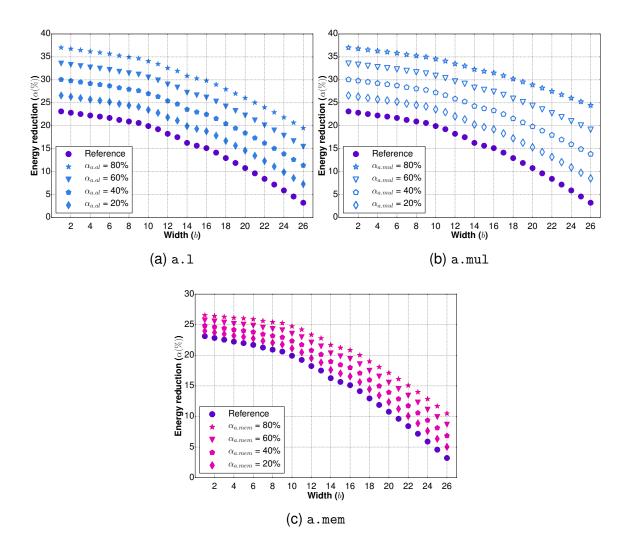

We note that in the above architectures, the costs for memory accesses is larger than the costs of the arithmetic instructions (*i.e.* from  $2 \times$  to  $2.9 \times$ ). We can deduce that in addition to the approximation of the common arithmetic units, the approximation of the memory units could be beneficial for energy efficiency.