# Parallel SystemC/TLM Simulation of Hardware Components described for High-Level Synthesis

Denis Becker

#### ▶ To cite this version:

Denis Becker. Parallel System C/TLM Simulation of Hardware Components described for High-Level Synthesis. Artificial Intelligence [cs.AI]. Université Grenoble Alpes, 2017. English. NNT:  $2017 {\rm GREAM082}$ . tel- $01709 {\rm 813v3}$

# HAL Id: tel-01709813 https://hal.science/tel-01709813v3

Submitted on 18 Sep 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : **Informatique** Arrêté ministériel : 25 mai 2016

Présentée par

### **Denis Becker**

Thèse dirigée par **Matthieu Moy** et co-encadrée par **Jérôme Cornet**

préparée au sein du Laboratoire Verimag, de STMicroelectronics et de l'École Doctorale de Mathématiques, Sciences et Technologies de l'Information, Informatique

# Simulation Parallèle en SystemC/TLM de Composants Matériels décrits pour la Synthèse de Haut-Niveau

Parallel SystemC/TLM Simulation of Hardware Components described for High-Level Synthesis

Thèse soutenue publiquement le **11 décembre 2017**, devant le jury composé de :

#### M. Frédéric Pétrot

Professeur, Université Grenoble Alpes, France, Président

#### M. Rainer Dömer

Professeur, University of California, Irvine, CA, États-Unis, Rapporteur

#### M. François Pêcheux

Professeur, Université Pierre et Marie Curie, France, Rapporteur

#### Mme Diana Göhringer

Prof. Dr.-Ing., Technische Universität Dresden, Allemagne, Examinatrice

#### M. Philipp Hartmann

Senior System Design Methodology Engineer, Intel Corp., Allemagne, Examinateur

#### M. Tanguy Sassolas

Ingénieur-chercheur, CEA, France, Examinateur

#### M. Matthieu Moy

Maître de Conférences, Université Lyon 1, France, Directeur de thèse

#### M. Jérôme Cornet

CAD Dev. Senior Staff Engineer, STMicroelectronics, France, Co-Encadrant de thèse

This work is licensed under a Creative Commons Attribution 4.0 International License.

https://creativecommons.org/licenses/by/4.0

## Remerciements

« Finir une thèse, c'est pas facile. » Et si j'y suis finalement arrivé, ce n'est pas tout seul. Outre les difficultés techniques, pour lesquelles l'aide de mes encadrants fut précieuse, toute une ribambelle de moments de doute ont parsemé mon chemin. Pour ceux-là, le soutien sans faille des amis et de la famille a été incalculablement salutaire. Je vais donc user et abuser de cette carte blanche introductive pour remercier tous ceux qui par leur participation, qu'elle soit administrative, technique, morale ou affective, ont contribué à faire en sorte que ma thèse se termine de la bonne manière.

Je commence par remercier STMicroelectronics et Verimag de m'avoir accueilli pendant ces trois années fraichement révolues. Merci à Florence Maraninchi, Matthieu Moy, Laurent Maillet-Contoz et Jérôme Cornet pour la mise en place de la collaboration entre l'entreprise et le laboratoire, ce qui n'est pas une tâche facile. Dans mon cas, les rouages étaient cependant bien huilés par les anciens thésards qui sont déjà passés au travers.

Merci aux membres du jury de thèse pour le temps qu'ils ont passé à la lecture du manuscrit, pour leurs retours constructifs, et pour leur participation à distance ou en présence à la soutenance ; au président, Frédéric Pétrot ; aux rapporteurs, Rainer Dömer et François Pêcheux ; et aux examinateurs, Diana Göhringer, Philipp Hartmann et Tanguy Sassolas.

« Trois ans, c'est court. » Cette phrase résonne particulièrement bien à l'oreille d'un thésard, et je remercie rétrospectivement mes encadrants pour me l'avoir suffisamment rappelée. Matthieu, malgré son nombre de thésards à encadrer, ses enseignements à donner, ses différents travaux de recherche à mener et son déménagement à Lyon, a toujours trouvé du temps à la fois pour m'aider techniquement et me relancer moralement. Jérôme, malgré un contexte « de transition » un peu difficile autour de l'équipe, une charge de travail importante et de nombreuses responsabilités, a donné de son temps pour me guider et me soutenir. Dans cette catégorie, j'en profite aussi pour remercier Laurent, qui malgré un emploi du temps chargé, a pris une place importante dans ma thèse en participant régulièrement aux réunions et au sprint final. Mes encadrants ont réussi à supporter ma discrétion pendant tout ce temps, et ont été présents quand il le fallait, avec bienveillance, ce qui était particulièrement appréciable pendant les douloureux derniers mois où il fallait passer du temps à relire et corriger le document que vous pouvez lire en tournant la page (ce que, moi-même, je m'apprête à faire).

Reconnaissance du ventre oblige, je continuerai par le côté entreprise. Mais quelques phrases ne suffiraient pas à dessiner un portrait assez fidèle de l'ambiance qui règne dans l'équipe que j'ai rejointe... ce sont des « pauv' tarés » qui ne pensent qu'à « manger manger », ce qui fait qu'au milieu d'eux je me suis rapidement senti à ma place. Merci pour tous ces « p'tits déj » toujours parfaitement justifiés (anniversaire, déménagement, publication d'article, achat/vente de véhicule) ainsi que pour toutes les autres occasions de manger que vous avez trouvées. Cette équipe, c'est une sorte de village gaulois où les tracas du quotidien souvent se diluent. Grâce à vous, mon estomac gargouillera à 11h14 tous les jours. Merci en vrac pour les crêpes, les tiramisus, les barbecues, les raclettes, les

plans machiavéliques fomentés à la cantine, les parties de Go ; outre Jérôme et Laurent, merci à Fred, Jean-Philippe, Aurélien, Perrin, Yussef, Éric, Laurence, Nafissa, Felipe, Florian, Julien, Nicolas, Cyril, Michel, Lionel, Anthony, Antoine, Laurent B, Hervé, Alain, Stéphane F et L, Jérôme Cz, Emmanuel... (ça en fait du monde, j'espère que je n'ai oublié personne... je vais utiliser l'astuce inclusive de l'équipe pour être sûr) bref, à toute l'équipe qui, je crois, s'appellera « ex-SPG » pour longtemps encore.

Je remercie tout aussi chaleureusement mes collègues du côté laboratoire, avec une pensée particulière aux thésards de ma « génération » avec lesquels j'ai commencé et terminé cette aventure. C'était rassurant de savoir que je n'étais pas le seul à avoir l'impression quasi-permanente de pédaler dans la semoule (ou plutôt dans la choucroute en ce qui me concerne). J'en profite ici pour consigner mes excuses aux plus jeunes thésards qui vont maintenant devoir supporter nos conseils avisés et nos suggestions pertinentes, ainsi qu'aux plus anciens thésards qui nous avaient pourtant prévenus. Enfin, je ne peux pas terminer cette partie sans remercier mes collègues du midi, surtout pour les fameuses parties de coinche post-repas en salle de réunion informelle. Merci donc aux collègues de coinche : Maxime, Anaïs, Amaury. Toutes mes excuses pour les imbécilités que vous avez dû entendre (au passage, encore merci à Amaury pour sa participation dans ce domaine). Merci à mes collègues de pause, et je pense en particulier à Alex, qui a aussi été mon jumeau de soutenance. Merci à ceux qui ont partagé mon bureau avec bonne humeur: Hamza (é-Vim-demment), Yuliia, Laurent, Juliana, Thomas, Vincent. Merci à tous ceux qui ont essayé de relancer veri-foot pour le tournoi des labos (avec le succès que l'on connaît). Enfin, merci à tous les membres de Verimag et plus particulièrement de l'équipe Synchrone (cf. l'astuce inclusive) dont j'ai fait partie pendant ces trois années.

« Last but not least. » Pour terminer, je veux remercier tous mes amis qui ont été d'un soutien sans faille côté coulisses tout au long de la thèse. Je serai, par vérécondie, plus évasif dans ce dernier paragraphe, mais sa longueur ne pourrait de toute façon pas atteindre la mesure de ma reconnaissance. Merci aux copains de la musique et du kebab, à ceux du club de Go de Grenoble, à toute la fine équipe du vendredi soir, à ceux qui se sont mariés, à ceux qui ne se sont pas mariés, à ceux que je voyais souvent, à ceux que je voyais moins souvent (pour des raisons géographiques), à ceux qui ont aussi emprunté le chemin de la recherche (pour nos rassurantes discussions sur le thème « pourquoi, déjà, on a choisi de faire ça? ») et aussi à ceux qui ont choisi « un vrai travail » (sic). Sans vous tous, ça aurait été une autre paire de manches à relever, comme on dit chez nous.

Enfin merci à ma famille, mes parents et mon frère, qui ont été des soutiens permanents et précieux.

# Résumé

Cette thèse a été menée dans le cadre du dispositif CIFRE<sup>1</sup> et s'est déroulée entre l'entreprise STMicroelectronics et le laboratoire Verimag.

# Chapitre 1: Introduction Générale

Le chapitre 1 décrit le contexte général dans lequel s'inscrit cette thèse. Les systèmes sur puce sont utilisés quand des contraintes de place, de puissance de calcul ou de consommation d'énergie rendent impossible l'utilisation d'un ordinateur classique. Un système sur puce est constitué d'un programme, le logiciel embarqué, qui s'exécute sur du matériel, incluant un ou plusieurs processeurs. Le système est constitué de ces deux éléments, et concevoir un système sur puce implique de prendre en compte les interactions entre le logiciel embarqué et le matériel. Pour permettre le développement du logiciel embarqué, le matériel de la puce est représenté par un modèle, qui est un programme écrit en SystemC (une bibliothèque C++). Grâce à ce modèle sont réalisées des simulations du système sur puce : le logiciel embarqué est exécuté non pas sur du matériel physique mais sur le modèle SystemC qui le représente.

L'objectif des simulations est de représenter les interactions qui ont lieu entre les instructions du logiciel embarqué et l'état du matériel. La durée d'exécution des simulations impacte directement la durée du développement du logiciel embarqué. Avec le temps, cette durée de simulation est devenue un problème, en partie dû à l'augmentation de la complexité des systèmes, mais aussi à d'autres facteurs. L'objectif de la thèse est d'étudier les causes des lenteurs observées en simulation, et de proposer des solutions afin de résoudre ce problème, notamment en identifiant et exploitant un potentiel de calcul parallèle présent dans ces simulations.

# Chapitre 2: Contexte et Problématique

Le chapitre 2 présente des informations techniques faisant partie du contexte nécessaire pour comprendre la suite du manuscrit. Au début sont présentées les notions de multi-tâche et de calcul parallèle, ainsi que les problèmes classiques qu'on observe dans ce domaine. Ensuite, le chapitre présente la librairie SystemC ainsi que le niveau d'abstraction TLM (*Transaction Level Modeling*). En effet, ce sont des modèles TLM qui sont utilisés pour représenter le matériel d'un système sur puce dans le cadre du développement du logiciel embarqué.

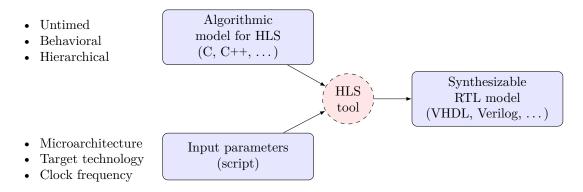

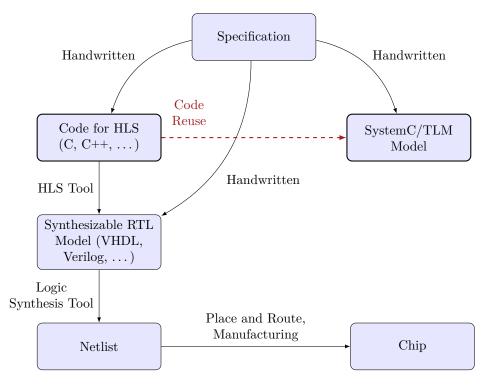

Enfin, le chapitre termine par une présentation de la synthèse de haut-niveau, ou HLS (*High-Level Synthesis*). La HLS permet de concevoir des composants matériels à partir d'une description de haut niveau, correspondant en général à un programme écrit en C ou en C++. Ce programme décrit le comportement fonctionnel du composant, et un outil

<sup>&</sup>lt;sup>1</sup>Convention Industrielle de Formation par la REcherche

de HLS est chargé de générer automatiquement un modèle de matériel réalisant cette fonction. L'objectif de la HLS est de permettre de concevoir des composants matériels plus rapidement et plus efficacement qu'en les décrivant à la main dans un langage dit bas-niveau comme le VHDL ou le Verilog. Le fait que la HLS soit utilisée, notamment à STMicroelectronics, a une influence sur le flot de conception et aussi sur la façon dont sont élaborés les modèles TLM.

# Chapitre 3: Profilage de Simulation

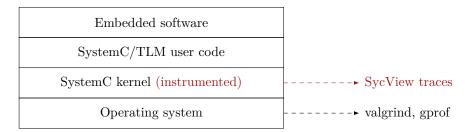

Le chapitre 3 présente une première série de contributions autour du profilage de simulations SystemC. En effet, nous avons précédemment dit que les simulations devenaient complexes et que des problèmes de performances apparaissaient. Une des premières étapes menant à la résolution du problème est donc d'analyser un exemple de simulation. Après l'étude de l'état de l'art en matière d'analyse de modèles SystemC/TLM, nous avons conclu qu'il était nécessaire de développer un outil d'analyse spécifique pour récolter des informations permettant de savoir pourquoi une simulation est lente, et d'identifier par la même des moyens d'accélération.

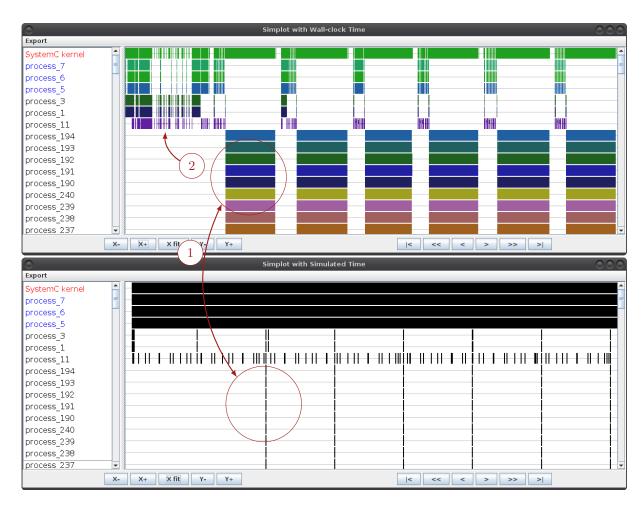

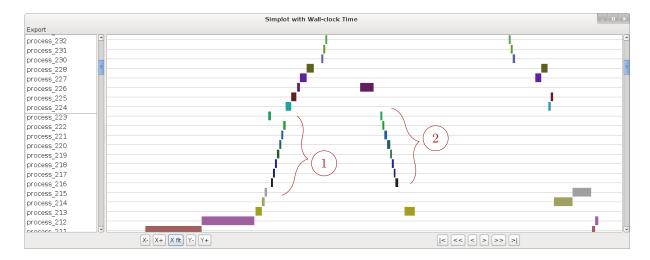

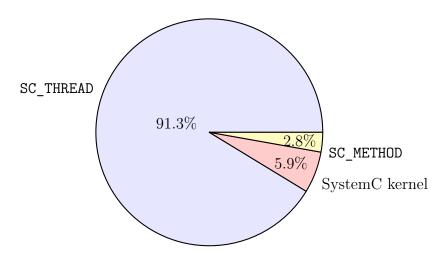

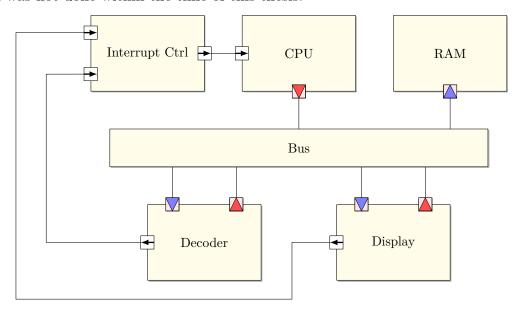

Ce chapitre présente donc ensuite l'outil d'analyse SycView, une contribution de cette thèse. Cet outil d'analyse collecte des traces durant une simulation, à l'aide d'un simulateur SystemC instrumenté, puis permet de visualiser les résultats à l'aide d'une interface graphique. L'outil a été ensuite appliqué à une étude de cas venant d'un vrai modèle utilisé à STMicroelectronics. Ce modèle correspond à une puce pour un décodeur numérique (set-top box) et est utilisé pour le développement du logiciel embarqué dans ce décodeur. Les résultats de l'analyse par SycView ont été publiés, un des principaux résultats étant que le temps de calcul était principalement utilisé dans la simulation de composants matériels réalisant le décodage vidéo.

# Chapitre 4: État de l'Art en Parallélisation de Simulations

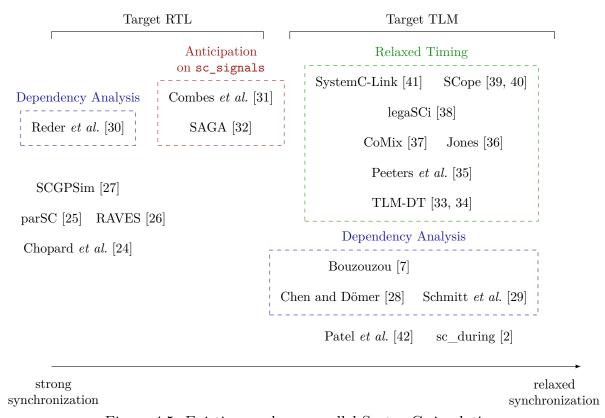

Le chapitre 4 présente l'état de l'art en matière de parallélisation de simulations SystemC. Ce sujet est traité quasiment depuis l'existence de SystemC, et avant SystemC la simulation parallèle de systèmes à événements discrets a déjà été théorisée.

La principale leçon à tirer de cette analyse de l'état de l'art est que chaque approche de parallélisation s'applique particulièrement bien à une catégorie de modèle donnée, mais pas à n'importe quel modèle SystemC. Pour le type de modèles que nous avons étudiés dans le chapitre précédent (l'exemple du décodeur numérique), nous avons identifié qu'aucune approche existante ne répondait pleinement aux problèmes de performances observés. Par exemple, les approches classiques de parallélisation dans le cycle de simulation ne seraient pas efficaces car notre modèle ne présente pas de potentiel de parallélisation au sein des cycles (il n'y a pas beaucoup de processus SystemC éligibles à chaque cycle), et les approches de partitionnement ne proposent pas de méthode permettant de trouver le bon partitionnement à utiliser ou garantissant que les résultats de simulation seront les mêmes qu'en simulation séquentielle.

# Chapitre 5: Infrastructure de Simulation Parallèle

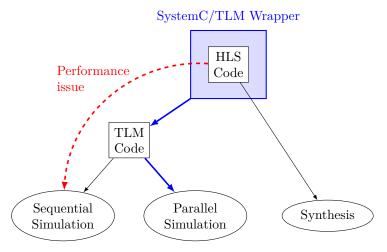

Le chapitre 5 présente une des principales contribution de la thèse, à savoir une infrastructure de simulation parallèle proposée en réponse aux problèmes de performances observés sur l'étude de cas industrielle. Le développement de cette solution fait suite à l'analyse de l'état de l'art en parallélisation de simulation, dont une conclusion était l'absence de solutions pour une catégorie spécifique de modèles. Notre cas est assez complexe, puisque les modèles sont en fait assemblés à partir de plusieurs sources, dont des morceaux de code écrits pour la HLS (présentée au chapitre 2).

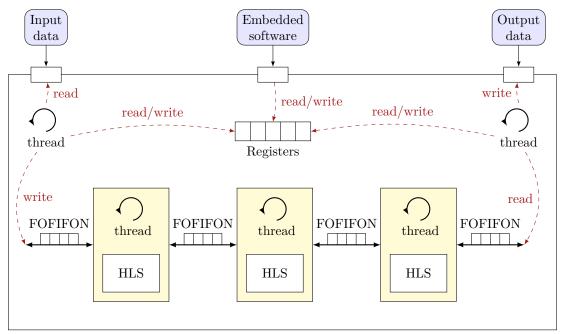

L'idée proposée est d'appliquer le modèle de calcul des processus de Kahn à un sousensemble du modèle SystemC. Ce sous-ensemble correspond aux modèles de composants matériels réalisant des traitements sur des flux de données, ce qui est typiquement le cas d'un décodeur vidéo (auxquels nous avons attributé en partie la cause des lenteurs observées en simulation au chapitre 3). Dans l'industrie, les modèles de ces composants sont généralement issus de descriptions destinées à des outils de HLS, pour des raisons pratiques évoquées plus en détail dans le chapitre 2. Nous avons donc pris en compte à la fois le modèle de calcul de ces composants ainsi que la présence du flot de conception HLS pour proposer l'infrastructure de simulation parallèle DistemC.

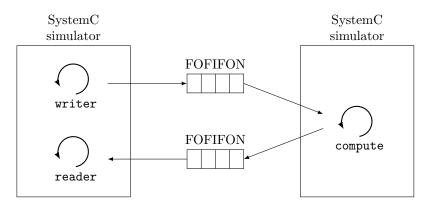

DistemC est une infrastructure de simulation parallèle et une contribution de cette thèse. Avec DistemC, la simulation est partitionnée, et chaque partition est exécutée par un simulateur SystemC différent. La plupart des composants classiques restent sur un simulateur principal (les modèles des processeurs, le bus système, les mémoires, etc) et les composants de traitement de données sont découpés en sous-fonctions et simulés séparément. En réalité, le découpage des composants de traitement de données est déjà fait au moment de l'écriture des modèles pour la HLS, et nous exploitons ceci en enveloppant ces sous-fonctions avec un morceau de code permettant la communication entre sous-fonctions à l'aide d'une structure de données nommée FOFIFON, développée pendant cette thèse. L'utilisation de FOFIFON permet les échanges de données entre différents simulateurs SystemC (exécutés par des processus différents).

# Chapitre 6: Application à un Modèle Représentatif

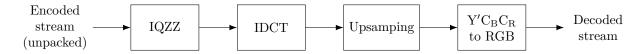

Le chapitre 6 présente l'application de l'infrastructure DistemC/FOFIFON (présentée au chapitre 5) à un modèle représentatif du problème qu'on cherche à résoudre, à savoir l'accélération de simulations de composants de traitement de flux de données. Ce modèle inclut notamment un décodeur JPEG, sur lequel nous avons appliqué l'infrastructure proposée pour étudier les résultats obtenus.

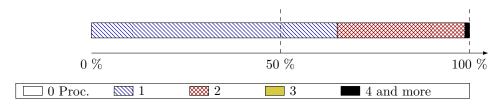

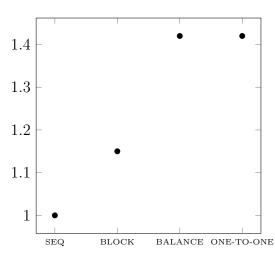

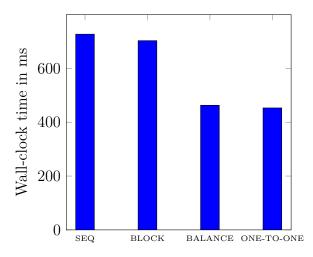

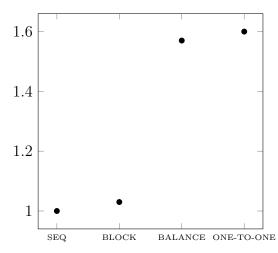

Les résultats observés montrent une amélioration des performances avec notre infrastructure parallèle par rapport à une exécution séquentielle. L'accélération obtenue est d'un facteur 1,6 pour l'utilisation de 4 processus parallèles. Cette accélération peut paraître à première vue peu significative, mais elle est en fait proche du maximum théorique que nous pouvons espérer sur ce type de modèles, et en particulier sur les décodeurs JPEG qui exposent peu de potentiel de parallélisme (à cause du déséquilibre entre les temps de calcul des différentes sous-fonctions du décodage).

### Chapitre 7: Conclusion Générale

Le chapitre 7 est la conclusion générale de la thèse. Nous résumons d'abord les enjeux: étudier le problème de performance observé dans les simulations industrielles en SystemC/TLM et y proposer une solution. Résoudre ce problème est capital, car si les performances continuent de diminuer (ce qui a toutes les chances d'arriver compte tenu de l'augmentation de la complexité des systèmes simulés) il sera bientôt impossible d'utiliser raisonnablement les simulations dans un cycle de développement industriel.

Ensuite, nous rappelons la solution proposée et les résultats obtenus. L'infrastructure DistemC/FOFIFON se propose d'aborder le cas particulier de la simulation parallèle de composants matériels de traitement de données décrits pour la synthèse de haut niveau. Les résultats obtenus sur un modèle représentatif nous montrent qu'une accélération significative est possible, tout en gardant ouverte la possibilité de combiner cette approche à d'autres approches de parallélisation existantes, pouvant s'appliquer sur d'autres sous-ensembles de la simulation.

La dernière partie évoque les perspectives ouvertes par cette thèse. Parmi celles-ci: la combinaison de différentes approches de parallélisation, l'application de DistemC et FOFI-FON à d'autres types de composants, comme des composants de traitement analogique (avec SystemC/AMS) et non plus numérique, ou même à d'autres types de simulations comme la simulation de réseaux de systèmes sur puce.

# Contents

| 1 | Ger | General Introduction |                                                         |    |

|---|-----|----------------------|---------------------------------------------------------|----|

| 2 | Bac | kgrou                | nd and Problem Statement                                | 17 |

|   | 2.1 | Gener                | al Information                                          | 18 |

|   |     | 2.1.1                | Multitasking Concepts                                   | 18 |

|   |     | 2.1.2                | Parallel Description and Parallel Execution             |    |

|   |     | 2.1.3                | Discrete Event Simulation                               | 20 |

|   | 2.2 | The S                | ystemC Library                                          | 21 |

|   |     | 2.2.1                | Presentation of SystemC                                 | 21 |

|   |     | 2.2.2                | SystemC Simulation Kernel                               | 24 |

|   | 2.3 | Transa               | action Level Modeling                                   | 27 |

|   |     | 2.3.1                | The TLM Layer                                           | 27 |

|   |     | 2.3.2                | Time Modeling                                           | 30 |

|   |     | 2.3.3                | History of the STMicroelectronics/Verimag Collaboration | 32 |

|   | 2.4 | High 1               | Level Synthesis                                         | 33 |

|   |     | 2.4.1                | Hardware Acceleration Blocks                            | 33 |

|   |     | 2.4.2                | Principle of High Level Synthesis                       | 34 |

|   |     | 2.4.3                | Studies and Experience on HLS                           | 36 |

|   |     | 2.4.4                | Interface of a Block Designed with HLS                  | 38 |

|   |     | 2.4.5                | Necessity to Split Designs in Sub-Blocks                | 39 |

|   |     | 2.4.6                | Wrapping HLS code for TLM                               | 40 |

|   | 2.5 | Proble               | em Statement                                            | 41 |

| 3 | Sim | ulatio               | n Profiling                                             | 43 |

|   | 3.1 |                      | luction                                                 | 44 |

|   |     | 3.1.1                | Motivation for Developing SycView                       | 44 |

|   |     | 3.1.2                | Existing Tools                                          | 45 |

|   | 3.2 | SycVi                | ew: A Visualization Tool                                |    |

|   |     | 3.2.1                | Trace Recording                                         | 47 |

|   |     | 3.2.2                | Evaluation of the Trace Recording Overhead              |    |

|   |     | 3.2.3                | Visualization                                           | 49 |

|   | 3.3 | Case S               | Study: Model of a Chip for a Set-Top Box                |    |

|   |     | 3.3.1                | Overview                                                |    |

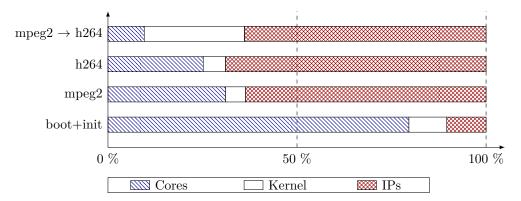

|   |     | 3.3.2                | Simulation Charts                                       |    |

|   |     | 3.3.3            | Wall-Clock Duration                                     | 55  |

|---|-----|------------------|---------------------------------------------------------|-----|

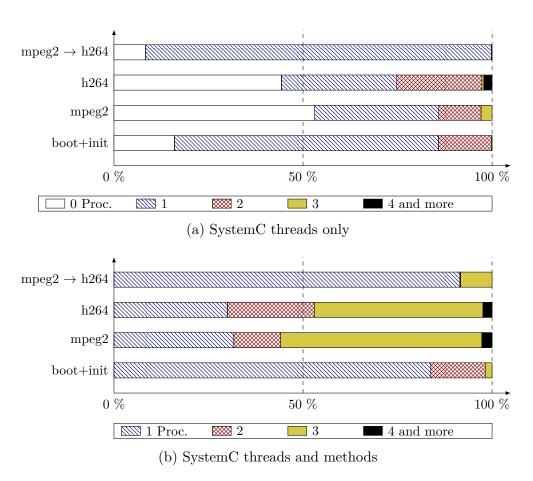

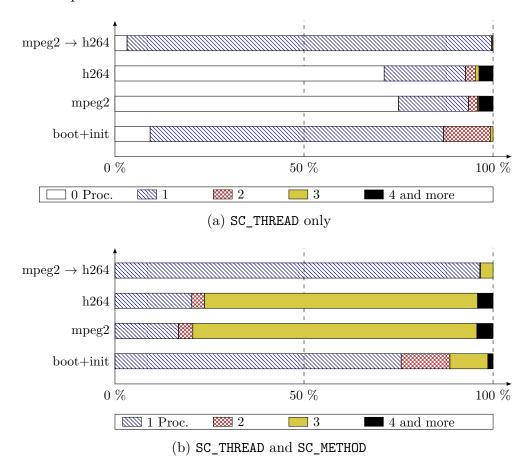

|   |     | 3.3.4            | Number of Runnable Processes per Cycle                  | 57  |

|   | 3.4 | Influe           | nce of Time Ranges on the Number of Processes per Cycle | 59  |

|   |     | 3.4.1            | Discussion on Previous Results                          | 59  |

|   |     | 3.4.2            | Example                                                 | 59  |

|   |     | 3.4.3            | Implementation of a Time Picking Policy                 | 61  |

|   |     | 3.4.4            | Results                                                 |     |

|   | 3.5 | Concl            | usion                                                   |     |

| 4 | Sur | vey: E           | existing Parallelization Approaches                     | 65  |

|   | 4.1 | Introd           | luction                                                 | 66  |

|   |     | 4.1.1            | Different Types of Simulated Architectures              | 66  |

|   |     | 4.1.2            | A Reminder on SystemC Semantics                         | 68  |

|   |     | 4.1.3            | Introductory Example                                    | 68  |

|   | 4.2 | Overv            | iew                                                     | 70  |

|   | 4.3 | Space            | Partitioning                                            | 71  |

|   |     | 4.3.1            | Presentation                                            | 71  |

|   |     | 4.3.2            | Applications to SystemC                                 | 71  |

|   |     | 4.3.3            | Discussion                                              | 72  |

|   | 4.4 | Relax            | ed Parallel Simulation                                  | 73  |

|   |     | 4.4.1            | Common Techniques                                       | 73  |

|   |     | 4.4.2            | Application to SystemC                                  | 75  |

|   |     | 4.4.3            | Approaches Based on Dependency Analysis                 | 79  |

|   |     | 4.4.4            | Exploit Massively Parallel Computing Architectures      | 82  |

|   |     | 4.4.5            | Tasks with Duration                                     | 83  |

|   | 4.5 | Discus           | ssion on Simulation Semantics                           | 84  |

|   | 4.6 | Discus           | ssion on Simulation Replication and Time Partitioning   | 86  |

|   |     | 4.6.1            | Simulation Replication                                  | 86  |

|   |     | 4.6.2            | Time Partitioning                                       | 86  |

|   | 4.7 | Concl            | usion                                                   | 88  |

| 5 | Pro | $\mathbf{posed}$ | Parallel Simulation Infrastructure                      | 89  |

|   | 5.1 |                  | luction                                                 |     |

|   | 5.2 | Wrapj            | ping HLS Code for TLM Simulation                        | 92  |

|   |     | 5.2.1            | Principle                                               | 92  |

|   |     | 5.2.2            | Link with the Kahn Process Network Model                | 92  |

|   | 5.3 | Dister           | nC: a Parallel Simulation Infrastructure                | 94  |

|   |     | 5.3.1            | Multiple Simulators                                     | 94  |

|   |     | 5.3.2            | Presentation of the Infrastructure                      | 94  |

|   | 5.4 | Fast (           | Communication using FOFIFON                             | 97  |

|   |     | 5.4.1            | Lock-Free Programming                                   | 97  |

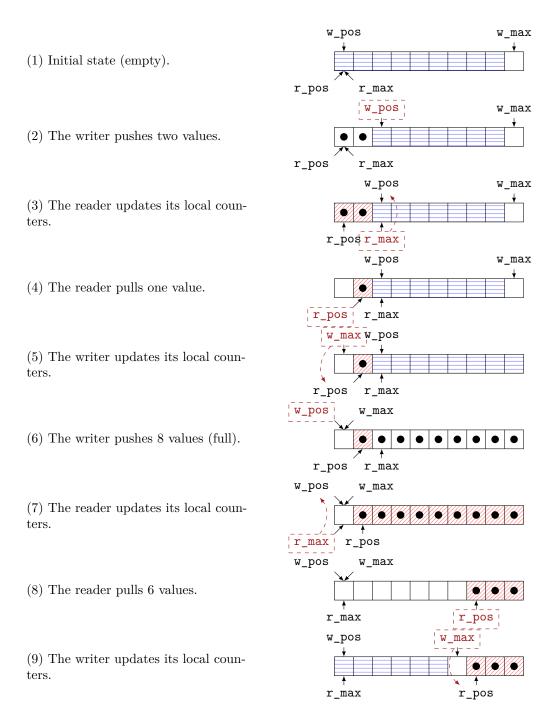

|   |     | 5.4.2            | Presentation of FOFIFON                                 | 99  |

|   |     | 5.4.3            | WeakRB Algorithm                                        | 101 |

|   |     | 5.4.4            | Proposed Changes                                        | 101 |

|   |     | 5.4.5            | Read Mechanism                                          | 103 |

|   |     | 5.4.6            | Illustrative Examples                                   | 103 |

|   |                                                                | 5.4.7 Validation                                     | 106 |  |  |  |  |  |

|---|----------------------------------------------------------------|------------------------------------------------------|-----|--|--|--|--|--|

|   | 5.5                                                            | Preventing Deadlock Situations                       | 107 |  |  |  |  |  |

|   |                                                                | 5.5.1 Dealing with Multiple SystemC Kernel Instances | 107 |  |  |  |  |  |

|   |                                                                | 5.5.2 SystemC Time Support                           | 109 |  |  |  |  |  |

|   | 5.6                                                            | Conclusion                                           | 110 |  |  |  |  |  |

| 6 | Parallel Simulation of a Hardware Component: Example of a JPEG |                                                      |     |  |  |  |  |  |

|   | Dec                                                            | coder Platform                                       | 111 |  |  |  |  |  |

|   | 6.1                                                            | Introduction                                         | 112 |  |  |  |  |  |

|   | 6.2                                                            | Description of the Example Platform                  | 114 |  |  |  |  |  |

|   |                                                                | 6.2.1 Platform                                       | 114 |  |  |  |  |  |

|   |                                                                | 6.2.2 Decoder Block                                  | 114 |  |  |  |  |  |

|   | 6.3                                                            | Block Design with CatapultC                          | 115 |  |  |  |  |  |

|   |                                                                | 6.3.1 Hierarchical Designs                           |     |  |  |  |  |  |

|   |                                                                | 6.3.2 Streaming Behavior                             | 116 |  |  |  |  |  |

|   | 6.4                                                            | Application                                          | 119 |  |  |  |  |  |

|   |                                                                | 6.4.1 Top-Level Module                               |     |  |  |  |  |  |

|   |                                                                | 6.4.2 Sub-Block Modules                              | 121 |  |  |  |  |  |

|   | 6.5                                                            | Performance Evaluation                               | 123 |  |  |  |  |  |

|   |                                                                | 6.5.1 SycView Measurements                           | 123 |  |  |  |  |  |

|   |                                                                | 6.5.2 Results for Parallel Execution                 |     |  |  |  |  |  |

|   | 6.6                                                            | Conclusion                                           |     |  |  |  |  |  |

| 7 | Con                                                            | nclusion                                             | 129 |  |  |  |  |  |

| A | crony                                                          | vms                                                  | 133 |  |  |  |  |  |

|   | ·                                                              |                                                      |     |  |  |  |  |  |

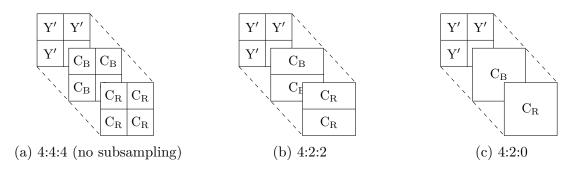

| A |                                                                | EG Decoding Algorithm                                | 135 |  |  |  |  |  |

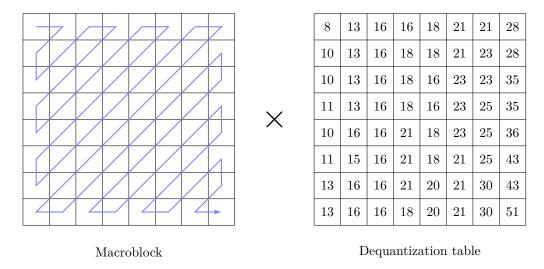

|   |                                                                | Inverse Quantization and Inverse Zig-Zag             |     |  |  |  |  |  |

|   | A.2                                                            | Inverse Discrete Cosine Transform                    |     |  |  |  |  |  |

|   |                                                                | A.2.1 Theory                                         |     |  |  |  |  |  |

|   |                                                                | A.2.2 Implementation Notes for HLS                   |     |  |  |  |  |  |

|   |                                                                | Upsampling                                           |     |  |  |  |  |  |

|   | A.4                                                            | Color Model Change                                   |     |  |  |  |  |  |

|   |                                                                | A.4.1 Theory                                         |     |  |  |  |  |  |

|   |                                                                | A.4.2 Implementation Notes for HLS                   | 138 |  |  |  |  |  |

| В | Det                                                            | ailed Examples                                       | 139 |  |  |  |  |  |

|   | B.1                                                            | Example Code of a Top Module using DistemC           |     |  |  |  |  |  |

|   | B.2                                                            | Example Scenario on a FOFIFON Structure              | 141 |  |  |  |  |  |

|   |                                                                |                                                      |     |  |  |  |  |  |

# — Chapter 1 —

# General Introduction

This manuscript explains the work of my CIFRE¹ thesis, a three-years joint work between STMicroelectronics in Grenoble and Verimag in Saint-Martin d'Hères. At STMicroelectronics, I joined the team "System Design and Services" working on the virtual prototyping of systems on chip, notably to enable debugging the embedded software at early development stages. At Verimag, I joined the team "synchronous" working on formal verification, testing, synchronous languages, and modeling. There has been a long collaboration between both teams, further presented in the next chapter, that presents the technical background. The following introduction presents the general context of my thesis.

# Systems on Chip

STMicroelectronics produces millions of systems on chip yearly. Systems on chip are used in many areas including home automation, autonomous driving, set-top boxes, smartphones, spacecrafts, etc. In short, they are used in places where computing power is required, but where specific constraints prevent the use of a "classic" computer. Most of the time, those constraints are the lack of space, the need for low power consumption, or the need for efficiency, which requires custom components. The "chip" part of the "system on chip" is an integrated circuit including various components: memories, peripherals such as sensors, Wi-Fi or Bluetooth interfaces, hardware acceleration blocks, and so on, but most importantly one or several generic-purpose Central Processing Units (CPUs). This last component, the CPU is what justifies the term "system" on chip. The CPU executes a program, the embedded software. The system results from the execution of the embedded software on the chip.

$<sup>^1{\</sup>rm Convention}$  Industrielle de Formation par la R Echerche — Industrial partnership of learning/training by research.

By definition, the software part can be updated during the lifetime of the product; for example, some set-top boxes were updated to run video games, even though that was not planned at first. Practically, updating the software means changing data in the chip memory. The case of the hardware is very different. The hardware is an integrated circuit, printed on a semiconductor material. To mass-produce this circuit, the process consists in producing a mask of the chip. The mask can be seen as a stamp, used to reproduce the same circuit. The production of a mask costs several million dollars: this step is critical in the production flow. With this in mind, one can easily see why the software can be updated — it costs some man/days of work to develop the new version of a program — and why the hardware cannot be updated.

The miniaturization of transistors (cf. Moore's law) enabled semiconductor companies to put more powerful components, and also more functionalities on a single chip. The ability to produce complex products mainly depends on two factors: abstraction and computer-aided design. The abstraction characterizes the model of a system. A model at a low abstraction level is close to the real system; it models the system in details. Such level requires a comprehensive knowledge of the internal behavior of the system. A high abstraction level does not model the details of the system, an approximate representation is used. High levels enable dealing with very complex systems as they are simpler to understand, but they are not sufficient to actually make the system. The notions of "high" and "low" levels are relative, they depend on the context.

In our context, the Register Transfer Level (RTL) description of a system on chip is considered to be at a low level of abstraction. It represents the system in a detailed way, which enables the generation of plans for an integrated circuit from its RTL description. This generation is done by an automatic tool. This is an example of computer-aided design. Another example of computer-aided design is a High Level Synthesis (HLS) tool. An HLS tool generates an RTL design from a function written in C or C++, written at a high level of abstraction. The functional description of the block is behavioral. It describes what the block does, but not how; the micro-architecture of the RTL design is decided during the generation process, by the hardware designer.

# Simulation of Systems on Chip

The embedded systems market has been growing very fast during the last decades. This growth is a consequence of such systems being in many promising and already successful areas. That includes home automation, smart items (e.g. phones, watches, televisions) and autonomous cars, amongst others. Anticipation is one of the most important quality in a growing market: not only in terms of "what new feature will be the determining factor for our product", but in terms of solving problems before the product is available. Moreover, in systems on chip design, it is not possible to wait for the availability of the physical chip to start testing because the cost of an error is too expensive (several million dollars to produce a mask).

A model of the chip is used to start testing the system on chip (hardware and software) before the chip is available. This model is developed as soon as possible, even though the full specifications of the chip are not available. It must be possible to run the embedded software on the model of the chip, and to identify potential issues that would happen on the real chip. In summary, the essential properties of the required simulations are:

Reproducibility The same inputs must produce exactly the same outputs. With repro-

ducibility ensured, when a bug is encountered, the user can reproduce

it to identify and solve the problem.

**Speed** Simulations must be fast enough to be reasonably used. When software

developers are fixing the code, they need to quickly get a result.

**Debug** A debug environment must be available to quickly find the root cause

of bugs (when a piece of software runs on a chip and a bug occurs, it

is hard to get more information than "it didn't work").

Accuracy The model must be accurate enough to enable the identification of

software bugs or hardware synchronization issues.

The Transaction Level Modeling (TLM) abstraction level has been created specifically to answer those needs. A TLM model is at a high abstraction level, and it is implemented using the SystemC library in C++. In particular, such a simulation satisfies each point: simulations are reproducible thanks to SystemC coroutine semantics (**Reproducibility**); they are fast as they are written at a high level of abstraction, plus it also benefits from the C++ execution speed (**Speed**) and debug environment (**Debug**); and they model enough of the chip by definition (**Accuracy**). The embedded software is run in the TLM model of the chip without any modification.

# Simulation Speed

The development of systems on chip involves many different teams working together. Some components of a chip are bought from external companies, some others are internally designed from scratch, and some others are reused or improved from previous chips. Even for components that are internally designed, the design method is specific to the type of component. For example, an Intellectual Property (IP) block for video decoding, has to be first mathematically designed, described and validated, before it is described in terms of hardware components. We mentioned the HLS process, that generates a hardware description of a component based on a functional description. Such process is typically used for this type of IP blocks. Since this process implies to write C/C++ code, and since a TLM description of a chip also consists in C++ code, developers reuse the first piece of code into the second one. Indeed, the development of a TLM model must be fast (a few months) and there is no time to re-write existing pieces of code. The fact that the same code is re-used also ensures consistency between the different models. This example illustrates that when we say "a model", we actually refer to different models for different components that are simulated together in order to check the whole system.

The growing complexity of systems on chip is reflected in their models. And more complex models lead to slower simulations, while the time-to-market constraints become shorter in a tight market. Reducing the simulation time of models became a major research challenge for more than two decades. One solution to speed up computer programs is to exploit the parallel computation resources available. Indeed, today's computers often have several CPUs, as well as powerful Graphics Processing Units (GPUs). However, exploiting parallel resources for TLM simulations is hard, and is a major research concern; this thesis falls within this context.

This manuscript is organized as follows. Chapter 2 presents technical background information that are part of the state of the art, and exposes the problem statement. Before the presentation of existing parallel simulation approaches for SystemC models, we examine the profile of an industrial case study from STMicroelectronics in Chapter 3. For this profiling, we developed a profiling and visualization tool for SystemC. Then, Chapter 4 presents the existing parallel simulation approaches. Chapter 5 introduces our proposed approach and details a proposed algorithm used for communication between concurrent simulators. Finally, Chapter 6 presents an application of the proposed approach to a representative model. Performance results are presented in this last chapter.

In summary, the contributions of this thesis are:

- Identification of profile metrics on SystemC simulations, and development of a visualization tool and instrumentation of a SystemC kernel in order to obtain the corresponding measurements.

- Profiling results on an industrial case-study from STMicroelectronics and analysis of the results, put in perspective with existing parallel SystemC simulation approaches.

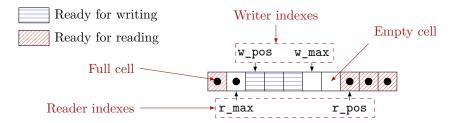

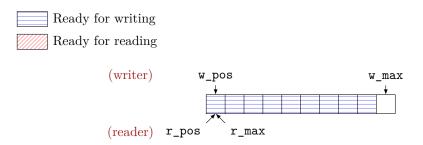

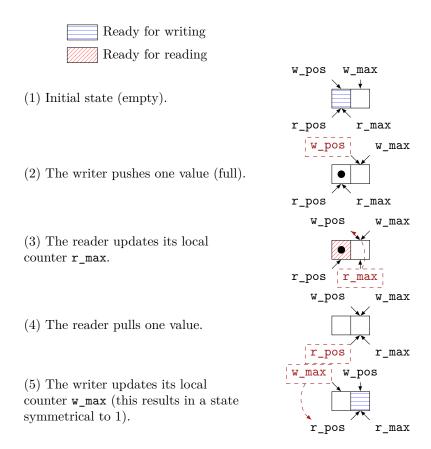

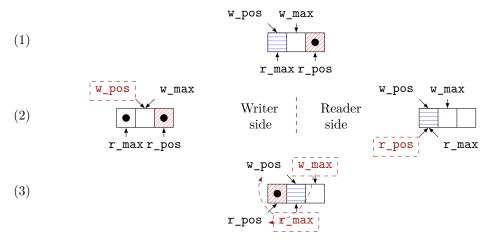

- Identification and implementation of an efficient First In, First Out (FIFO) communication algorithm for intensive data exchanges (unidirectional), and adaptation of this algorithm to SystemC simulations, called Fast Ordered First In, First Out data exchange (FOFIFON).

- Development of DistemC, a non-intrusive multi-process infrastructure of SystemC simulators communicating through FOFIFON structures.

- Application of DistemC, to simulate in parallel the SystemC/TLM model of a hardware acceleration block (a JPEG decoder) whose behavior is described for an HLS design flow.

# — Chapter 2 —

# Background and Problem Statement

| 2.1 | Gener  | al Information                                          | 18 |

|-----|--------|---------------------------------------------------------|----|

|     | 2.1.1  | Multitasking Concepts                                   | 18 |

|     | 2.1.2  | Parallel Description and Parallel Execution             | 19 |

|     | 2.1.3  | Discrete Event Simulation                               | 20 |

| 2.2 | The S  | ystemC Library                                          | 21 |

|     | 2.2.1  | Presentation of SystemC                                 |    |

|     | 2.2.2  | SystemC Simulation Kernel                               |    |

| 2.3 | Transa | action Level Modeling                                   | 27 |

|     | 2.3.1  | The TLM Layer                                           | 27 |

|     | 2.3.2  | Time Modeling                                           | 30 |

|     | 2.3.3  | History of the STMicroelectronics/Verimag Collaboration | 32 |

| 2.4 | High 1 | Level Synthesis                                         | 33 |

|     | 2.4.1  | Hardware Acceleration Blocks                            | 33 |

|     | 2.4.2  | Principle of High Level Synthesis                       | 34 |

|     | 2.4.3  | Studies and Experience on HLS                           | 36 |

|     | 2.4.4  | Interface of a Block Designed with HLS                  | 38 |

|     | 2.4.5  | Necessity to Split Designs in Sub-Blocks                | 39 |

|     | 2.4.6  | Wrapping HLS code for TLM                               | 40 |

| 2.5 | Proble | em Statement                                            | 41 |

|     |        |                                                         |    |

# 2.1 General Information

Simulating systems on chip involves to use multitasking. Indeed, hardware systems are intrinsically parallel. In this section, we remind different multitasking concepts in computer science, necessary to understand SystemC simulations. We also emphasis the difference between describing parallel systems, and executing a program in parallel. This difference is a key to understand why parallel simulation of systems on chip is a major research concern. Finally, we introduce discrete event simulation.

# 2.1.1 Multitasking Concepts

#### 2.1.1.1 Coroutines, Threads and Processes

A task is a generic term that refers to a unit of execution. This unit of execution is a sequence of instructions with context information (local variables, stack of function calls, etc). When a system consists of multiple tasks, a scheduler manages their execution. The scheduler can either be preemptive, which means it has the ability to pause and resume tasks, or cooperative, which means it cannot. In cooperative multitasking, the scheduler must wait until a task pauses itself before having the chance to run another one. The cooperative term comes from the fact that a task must cooperate, i.e. pause itself sometimes, to enable the execution of other tasks. The fact that a tasks suspends itself is called a yield. In cooperative multitasking, tasks are called coroutines. In preemptive multitasking, tasks generally consists in threads or processes.

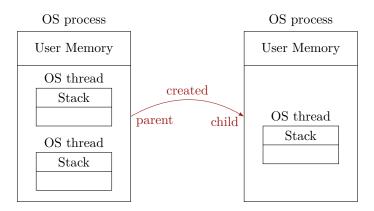

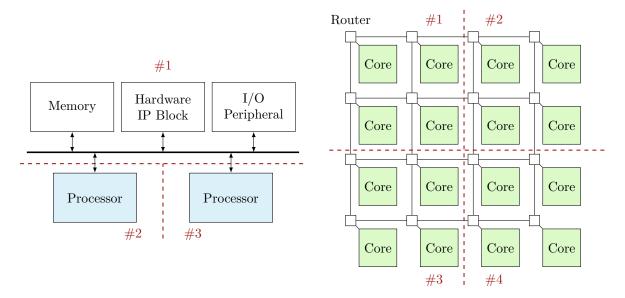

Figure 2.1: OS processes and OS threads.

Figure 2.1 reminds the major differences between OS processes and threads, that lies in the amount of context information. A process (the child) is created by another process (the parent). The child and the parent processes do not share the same memory space. Thus, if the child process modifies the value of a variable, the parent process will not see

the modification. A thread is created by a process. Each thread belonging to the same process share the same memory space. Thus, if a thread modifies the value of a variable, other ones will eventually see the modification. Threads are often referred to as lighter concurrency features than processes, because their creation and context switching are faster, and communication between them is easier because they share the same memory space.

#### 2.1.1.2Atomicity, Race Conditions and Critical Sections

When multiple tasks are running, atomicity is required to build correct functions. Etymologically, something atomic is something that cannot be divided. In computer science, an atomic operation is a set of instructions that either occur completely or does not occur at all. This means that none of the intermediate states of an atomic operation must be observable from the rest of the system (i.e. the scheduler and the other tasks scheduled by the same scheduler).

A race condition is a situation where the observable state of an application changes depending on the execution order of tasks. A typical example of race condition is when two threads increment a shared variable without any "protection". The increments performed on a variable can be translated into load, add and store assembly instructions. Individually, those instructions happen atomically, but they can interleave such as the value is only incremented once at the end. To avoid this race condition, operations on the shared variable should be performed in a *critical section*. At any given time, there can be at most one task that runs code from a critical section. This is called mutual exclusion, and it is typically set up with a *mutex* variable or by using fences.

#### 2.1.2Parallel Description and Parallel Execution

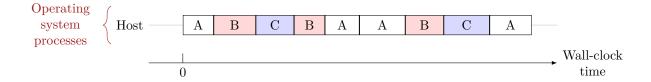

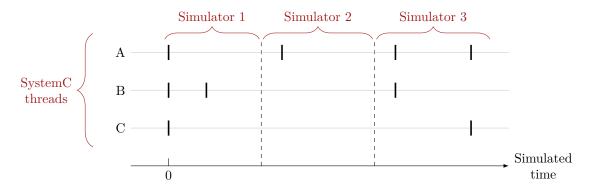

Figure 2.2: Example of parallel description, either executed sequentially or in parallel.

We already stated that hardware systems are parallel: indeed, each component is working at the same time as the others. Thus, in order to describe hardware systems, there is a need for parallel description. However, parallel description does not imply parallel execution: it is completely possible to execute sequentially a model that is described with

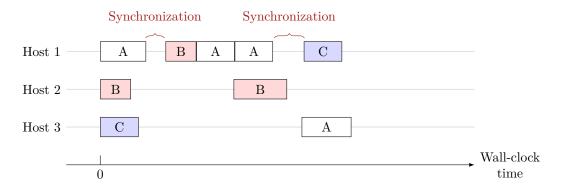

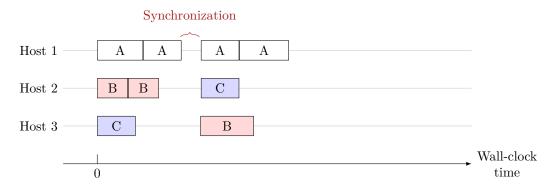

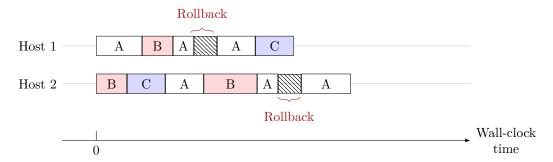

parallel components. Figure 2.2 shows an example on which three processes are described (a), and executed either sequentially (b) or in parallel (c).

## 2.1.3 Discrete Event Simulation

The principle of simulation is to model the *evolution* of a dynamic system through time. Discrete Event Simulation (DES) must be distinguished from continuous simulation. Continuous simulations are time-driven: the simulated time evolves with a specific step (possibly changing during simulation) and the components of the simulation evolve with it. In DES, which is event-driven, the state of components changes in response to event occurrences. Thus, the simulated time "jumps" from one instant to the other, also in response to event occurrences. In summary: time is an input parameter in continuous simulation, while in DES time is an output value. A consequence is that in DES, it is not possible a priori to know the different simulated time instants the simulation will go through.

#### **Algorithm 1** Typical loop of a discrete event simulator.

```

1: sim time \leftarrow 0

2: while runnable_processes not empty do

while runnable_processes not empty do

3:

p \leftarrow runnable processes.pop()

4:

p.run()

5:

end while

6:

7:

if events not empty then

8:

e \leftarrow events.pop()

9:

sim_time \leftarrow e.timestamp()

10:

e.trigger()

▶ Processes sensitive to e are put in runnable processes

end if

11:

12: end while

```

A DES simulator enables the execution of a model. The simulator must maintain a list of processes, a list of events (generally a priority queue), and a variable for the current simulated time value. An event is an object that has a timestamp value, corresponding to the simulated date it occurs. Processes can indicate that they have to run computation when a specific event occurs: in this case, they are called sensitive to such event. The queue of events is sorted in growing timestamps. The general principle of a discrete event simulator is presented on Algorithm 1. It consists in a loop program. First, each process from the model is run. During their execution, they register events to occur at future simulated time instants. When the execution of processes is over, the first event from the list of events is retrieved, the simulated time variable takes the event timestamp as value, and processes that are sensitive to this event are triggered. The simulation stops either when the simulated time has reached a specific value, or when there are no more processes to run.

# 2.2 The SystemC Library

# 2.2.1 Presentation of SystemC

SystemC is a C++ hardware modeling library. Since 2005 it is under IEEE standard, updated in 2011 as IEEE 1666–2011 [1]. The standard notably defines the requirements of a SystemC simulator. A SystemC simulator is a discrete event simulator. The SystemC library can be used to write models of hardware at different levels of abstraction. Each level of abstraction uses different constructs from the SystemC library. Transaction Level Modeling (TLM) is one of them, and is described as a part of the SystemC standard [1, pp. 413–561]. The goal of this section is not to exhaustively define the features of SystemC but some key ones, and to explain how the SystemC simulator works.

#### 2.2.1.1 Elements for Discrete Event Simulation

SystemC offers different types of tasks to describe hardware parallelism: SC\_METHOD, SC\_THREAD and SC\_CTHREAD. The SystemC clocked threads (SC\_CTHREAD) are mentioned for exhaustiveness, but are only used in cycle-accurate models which are not in the scope of this manuscript. Whenever the expression *SystemC process* is used, it means indifferently SystemC threads or methods.

Both SystemC methods and threads enable the description of concurrent behaviors, their only difference lies in how this description is made. SystemC methods are implemented as stackless processes, *i.e.* simple C++ function calls. As a consequence, their state is not recorded from one run to the other. This execution model is relevant for simple behaviors, but for complex ones they are not comfortable to use, because manual recording of the current state would be necessary. For this reason, SystemC also offers threads, which are implemented as stackful processes.

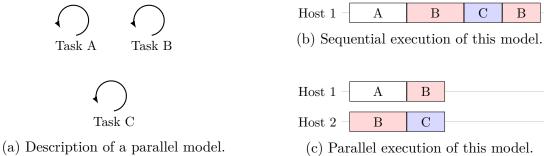

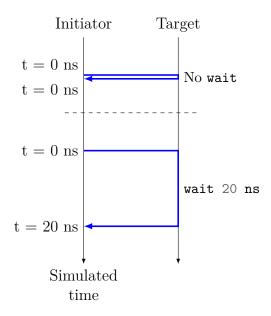

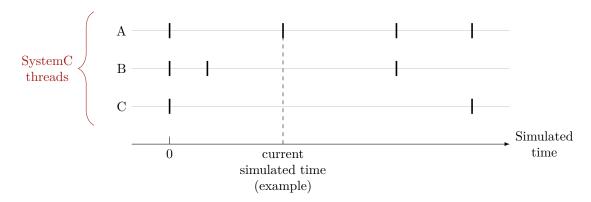

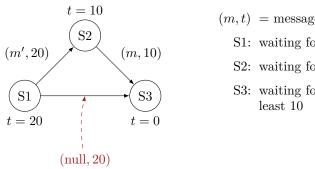

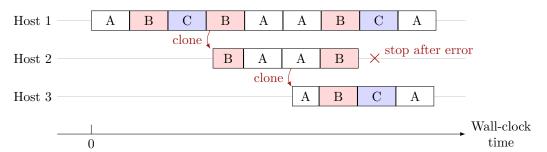

Simulated time is modeled with the sc\_time type. It models the fictional time taken by the simulated platform (i.e. estimated time that the real chip would take). It is completely disconnected from the wall-clock time, which is the human perception of time passed while a simulation is running. Figure 2.3 illustrates the duality between wall-clock time and simulated time. A SystemC method can schedule a future run for itself, after a certain simulated time elapse, using the function next\_trigger. Similarly, a SystemC thread may suspend itself for a certain amount of simulated time, using the function wait.

Events are modeled in SystemC with the sc\_event class. Events can be triggered explicitly in a SystemC process, either immediately or after a simulated time delay. They are used as conditions to wake up suspended SystemC processes. Each SystemC process can have a sensitivity list, which is a list of events. Each time an event present in

Figure 2.3: Evolution of wall-clock time versus simulated time. In SystemC, as in discrete event simulation, computations are "immediate" with respect to simulated time, and simulated time progresses "immediately" with respect to wall-clock time.

a suspended process' sensitivity list is triggered, it causes this process to run. This sensitivity list can be specified both statically when the process is created or dynamically during the process execution. For SystemC methods, the dynamic sensitivity is described with the family of functions next\_trigger. For SystemC threads, it is specified with the family of functions wait.

Finally, the sc\_main function is the equivalent of the main function in a standard C++ program. The role of this function is to instantiate the model components, bind them together and start the simulation by calling the function sc\_start. The instantiation and binding of components is called the *elaboration phase* in SystemC. It stops when sc\_start is called, then starts the *simulation phase*. The hierarchy and bindings of components can only be modified during the elaboration phase.

#### 2.2.1.2 Elements for Hardware Modeling

Hardware systems are represented as a hierarchical set of blocks which are bound together. The C++ language, as an object-oriented language, already has the required constructs for this. Indeed, each kind of hardware component can be described with a C++ class, and each hardware component is an instance of the corresponding class. To encapsulate common behavior of all hardware components, SystemC offers the base class sc\_module. Each part of the hardware system identifiable as a building block will be described in a class inheriting from SystemC's sc\_module, as shown on Figure 2.4.

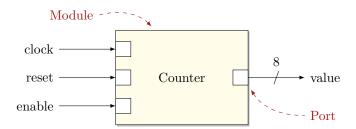

A module communicates with other modules through its ports (sc\_port in SystemC) and exports (sc\_export). A port enables access to a set of services declared in an

Figure 2.4: Example of an 8-bit counter represented in SystemC. This representation is at the RTL abstraction level. This manuscript is about TLM models, however this example is given to illustrate that similar SystemC constructs are used at RTL and TLM. However, we see in further examples (e.g. Figure 2.8) that, for example, a "module" is much more abstract at TLM than at RTL.

sc\_interface. An export is used to enable access to an implementation of a SystemC interface. A SystemC interface is a set of functions.

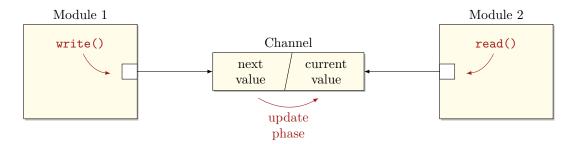

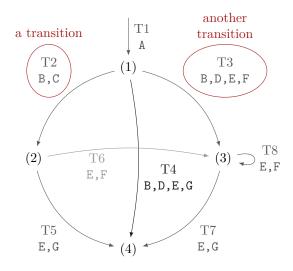

Depending on the level of abstraction of the model, the elements defined for communication in SystemC are used differently. As an example, we compare the two main communication paradigms in SystemC. The first one uses *channels* inheriting from SystemC's sc\_prim\_channel class, as shown on Figure 2.5. In this example, there is a shared channel (called "Channel" on the figure) that stores a state. The channel has a current state (relatively to simulated time) and a next state. When "Module 1" writes on the channel, it modifies its next value. When "Module 2" reads the channel, it reads its current value. Thus, both modules do not access the same memory location. This introduces a specificity of SystemC simulation (with respect to discrete event simulation) called the *update phase*. It consists in affecting the "next" value to the "current" value. This does not correspond to a simulated time progress, but simply as a "delta" progress in the sense of a very small amount of time (in fact, the implementation uses a zero time value). This update phase creates a *delta cycle*. We present how the SystemC simulator handles delta cycles further.

Figure 2.5: Communication between SystemC processes using primitive channels.

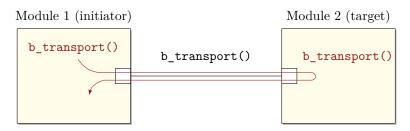

Using such channels creates delta cycles, which slows down the simulation. Consequently, higher abstraction levels use an alternative communication paradigm. At the TLM abstraction level, communication between modules is done with Interface Method Calls (IMCs), as shown on Figure 2.6. This example presents one of the methods defined in the TLM-2.0 interface: the *blocking transport* interface (b\_transport). When "Mod-

ule 1" writes to "Module 2", it *directly* calls a method from "Module 2". This enables faster communication, simply because less operations are done. The blocking transport interface is typical of Loosely-Timed (LT) TLM models. We further present TLM and LT in the next section, but introduced them here to illustrate that the SystemC library is used differently depending on the abstraction level.

Figure 2.6: Communication using IMC, at the TLM abstraction level.

## 2.2.2 SystemC Simulation Kernel

A SystemC simulation kernel is an implementation that enables to run a SystemC model as described in the standard. The Accelera Systems Initiative (ASI), formerly Open SystemC Initiative (OSCI), is the consortium of companies that wrote the SystemC standard. They propose a reference implementation of the SystemC library, including a simulation kernel <sup>1</sup> (under the Apache 2.0 License since 2016). Commercial implementations also exist with different extra features.

A SystemC simulator contains a scheduler. It has to manage the execution of the different SystemC processes described in the model. According to the standard, a SystemC scheduler must fulfill coroutine semantics [1]. This means that each section of code between two yield (wait) statements must be atomic. To do so, a scheduler can either use cooperative multitasking, or use preemptive multitasking but behave as if it was using cooperative. In the latter case, the scheduler must notably ensure that new race conditions are not introduced because of the preemptive scheduling or physical parallelism [2]. This does not prevent multiple processes from running in parallel, but there must exist a sequential scheduling that reproduces the same simulation. In practice, one must ensure that shared variables are not modified concurrently by different processes. This semantic choice has been made to ease the writing of models by avoiding many race conditions between processes of a model. Indeed, it is frequent for modules to have several threads using the module's fields (in C++ terms the class attributes). With coroutine semantics, the different processes can use these shared variables without any protection (such as mutual exclusion). Another rule for a SystemC scheduler is that it must ensure the determinism of simulations: running multiple simulations with the same input must produce the same result. This makes SystemC simulations reproducible, which is a key property for debugging.

<sup>1</sup>http://www.accellera.org/downloads/standards/systemc

The ASI implementation consists in the sequential execution of the processes in the model. An advantage of a sequential implementation is that coroutine semantics are easy to fulfill and the determinism is easy to ensure, provided that multiple runnable processes are always run in the same order. Moreover, sequential implementation leads to a lightweight context-switch because it can be performed without underlying system calls. An obvious drawback is that it does not exploit the multiple cores of the host machine running the simulation. With the increasing size of models, the simulation time is a major issue of complex hardware simulation. Achieving parallel execution of SystemC simulations is not straightforward, notably because of the SystemC scheduler requirements, and is a major research concern.

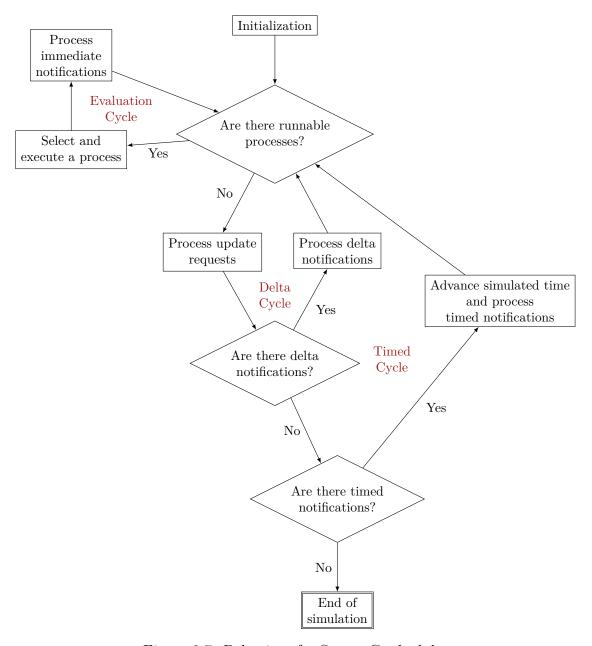

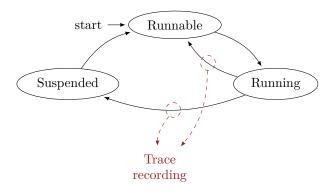

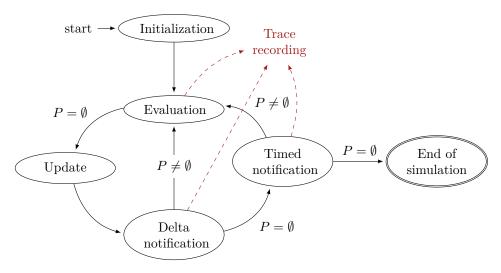

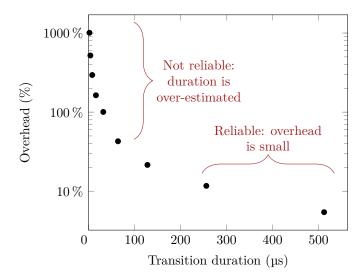

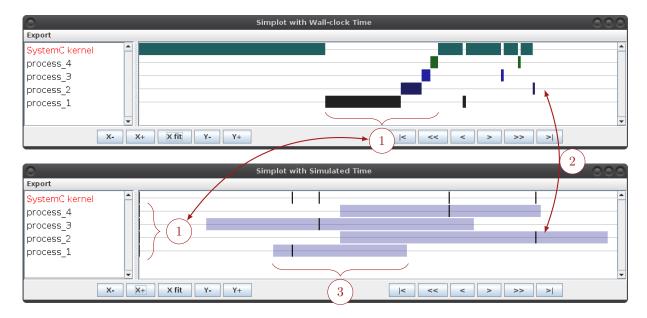

Figure 2.7: Behavior of a SystemC scheduler.

Figure 2.7 shows the expected behavior of a SystemC scheduler during the simulation phase (the elaboration phase has already been done at this point). The scheduler starts with an initialization phase that we do not detail here, but it consists in running the processes of the model once, to let them reach an "initialized" state. Then starts the simulation loop. As long as there are runnable processes, the scheduler remains in the same evaluation phase. During this phase, processes can trigger other ones by notifying immediate events. When there are no more runnable process, update requests are processed: this is the update phase. The value of primitive channels, previously presented, is updated in this phase. If the update phase created delta notifications (i.e. values of channels were actually changed) they are processed, and an evaluation phase starts again. If no such notification exists, the scheduler checks for timed notifications, i.e. notifications that can modify the value of simulated time. If there are timed events, the earliest one is picked, the simulated time is set to its time, and notifications are processed. The evaluation phase starts again. Otherwise, the simulation is over. The simulation also ends if a specific simulated time value has been reached (it can be defined when calling sc start).

# 2.3 Transaction Level Modeling

We previously presented the SystemC library, that can be used to model hardware systems at various levels of abstraction. In this manuscript, we address the case of models at the Transaction Level Modeling (TLM) abstraction level. It has been created to enable modeling systems on chip already at early stages of the development. It answers the need for a fast simulation, quickly made available. But even when the real chip is available, on-chip software or hardware debug is a tedious task because there is little observability of what happens inside the chip. Thus, TLM models are useful during all the lifetime of the product.

Figure 2.8 presents a simple platform as represented at the TLM abstraction level. We present the different elements from this representation in the following section. This figure is "unzoomed" compared to Figure 2.4. Components like bit-adders, counters or clock signals are not represented at this level: they are part of the microarchitecture (which is often not known when the TLM model is written).

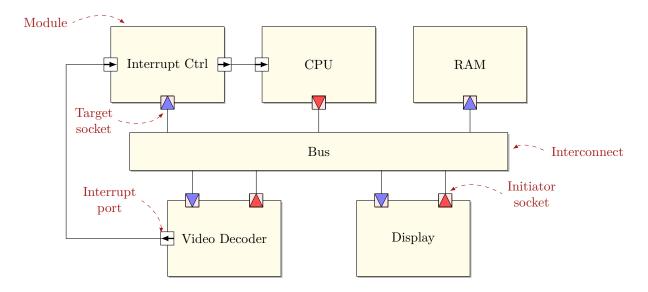

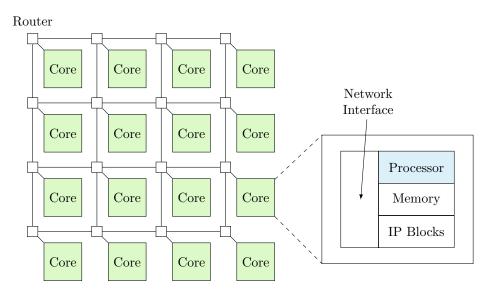

Figure 2.8: Example of a simple platform at the TLM abstraction level.

# 2.3.1 The TLM Layer

The SystemC standard has been extended to define the TLM layer, which adds core interfaces and utilities to the SystemC library, mainly specifying interprocess (in the sense of SystemC processes) communication. The main goal of the TLM standard is to ensure interoperability to enable the use of hardware models coming from different vendors. Two complementary versions of TLM are currently used: TLM-1.0 and TLM-2.0.

#### 2.3.1.1 Key Concepts of TLM

A transaction is an atomic exchange of information between an initiator module and one or multiple targets. Most of the time, a transaction consists in a read or a write operation. Since TLM-2.0, a generic payload is defined to be the base information object. It contains a set of default fields to address most of the bus communication protocols (e.g. address field, data field). Generic payload also support protocol-specific extensions. A transaction is transported from one module to the other through transport methods. We previously presented an example on how transport methods work, using direct method calls in the target module. TLM also supports the modeling of interrupts, which are boolean wires asynchronously triggering actions on a state change.

To send or receive transactions, TLM offers initiator and target sockets, as shown on Figure 2.8. In terms of SystemC, an initiator socket is an sc\_port that contains an sc\_export and a target socket is an sc\_export that contains an sc\_port.

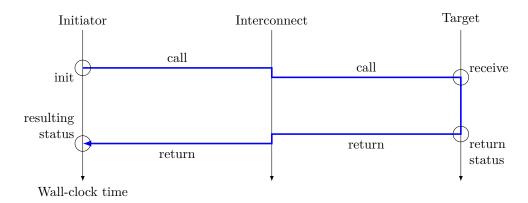

The TLM standard defines initiator, target and interconnect components. An initiator component has at least one initiator socket, a target component has at least one target socket and an interconnect component has at least one of each. For example, the Central Processing Unit (CPU) from Figure 2.8 is an initiator component, the memory is a target component and the bus is an interconnect. Figure 2.9 represents a possible processing of a transaction with an interconnect component. Even in this case, the transport is still a function call, performed *in* the final target *by* the thread from the initiator component.

Figure 2.9: Diagram illustrating the transport of a transaction through an interconnect component.

We remind here that the "wires" represented on Figure 2.8 are modeled in TLM with transport methods, using Interface Method Calls (IMCs). Consequently, performing a TLM transaction is equivalent to calling a function in the final target component.

#### 2.3.1.2 TLM Coding Styles

The TLM standard defines two coding styles: Loosely-Timed (LT) and Approximately-Timed (AT). The major difference between those coding styles are how transactions are performed. In the LT style, transactions only has two timing points: before the transaction (call) and after the transaction (return). For this coding style, the *blocking transport* interface is used, which means that the initiator cannot continue its execution before having received the response to a transaction. Figure 2.10 illustrates how transactions occurs with the LT coding style. In the AT style, transactions can be split in phases, each associated with two timing points (before and after).

Figure 2.10: Two different transactions in loosely-timed style.

Each of those coding styles corresponds to different use cases. Both can be used for embedded software development or software performance analysis. Both can also be used for hardware functional verification and architectural analysis. Moreover, the AT style also enables hardware performance verification. The more transactions are split closely to the real hardware, the more accurate the performance evaluation will be. However, to answer the use cases enabled by both styles, the LT style is used for a simple reason: simulations run faster, because fewer details are specified in the model. Moreover, to develop AT models, more information is required, that is not available at early development stages.

#### 2.3.1.3 Modeling CPUs

The simulation of CPUs is particular compared to other hardware components, as there are two very different approaches. A first approach is to use an Instruction Set Simulator (ISS). An ISS is, as the name indicates, a simulator of the instruction set of the target (*i.e.* the chip) processor architecture. An ISS is an accurate way to simulate a specific

architecture (e.g. ARM) on another one (e.g. x86). With an ISS, the embedded software is compiled for the target architecture (cross-compilation). This approach targets accuracy, in the sense that the software execution on the target processor can be simulated instruction per instruction. An ISS includes a translation mechanism from the simulated architecture to the host machine architecture; in the end, the ISS is a program that runs on the host machine. Another approach is to use native execution of the embedded software. This means that the embedded software is compiled for the host machine. The embedded software is run nearly in the same conditions as the rest of the model, i.e. as a regular program, except that the hardware functionalities (e.g. memory accesses) are captured and translated into transactions on the SystemC/TLM model. Instead of translating each instruction, only bus transactions need to be translated to communicate with the simulated platform. This results in simulations much faster than with an ISS.

The two approaches answer different needs. An ISS is used to simulate the execution of the software instruction by instruction: this can be used for an accurate performance evaluation of the software. Native code execution includes everything for fast simulation at a high abstraction level such as LT TLM.

#### 2.3.2 Time Modeling

#### 2.3.2.1 Temporal Decoupling

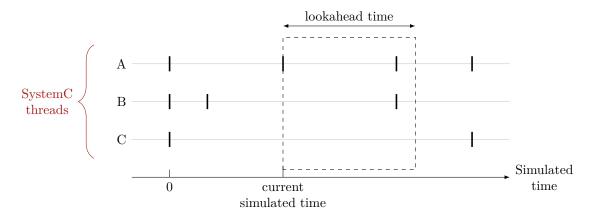

Temporal decoupling has a specific meaning in TLM-2.0, but before presenting this particular case, we introduce the idea. *Temporal decoupling* consists in enabling SystemC processes to run ahead of the current simulated time, thus without actually advancing simulated time. Each process has a local value modeling its own simulated time. Each process may increase its local simulated time without performing a SystemC wait. This is a low-cost timing annotation. To keep time consistency in the whole simulation, each process must at some points yield to the kernel to advance the SystemC simulated time. The purpose of temporal decoupling is to increase computation locality, which reduces the overhead of context switches between processes.

In TLM-2.0, temporal decoupling is implemented in transactions, with a simulated time annotation. This timing annotation is not necessarily transformed into a SystemC wait call. Different strategies for taking such annotation into account are possible. To limit the maximum advance a process is allowed to have (compared to the least advanced process), a time quantum can be defined. If any local time goes further than the quantum, a SystemC wait is performed.

In practice, temporal decoupling was already used in SystemC models, notably at STMicroelectronics, before TLM-2.0. Internally, timing annotations are performed with a family of functions called annotate. The synchronization points can either be implicit (e.g. using TLM-2.0 time quantum, performed in transactions) or explicit (synchronization-on-demand in TLM-2.0) by using a synchronize method.

#### 2.3.2.2 Loose Timing: Time Ranges

One of the purposes of the TLM abstraction level is to enable the modeling and simulation of a chip that is not already fully specified. However, at such early stages of the development, not only the chip is not fully specified, but the micro-architecture is not fixed yet. Consequently, it is not possible to have precise timing information for the operations performed by the chip. Yet, the model can and must still be written, without such information. Different strategies are possible to overcome this issue: not using time, over-specifying or partially specifying.

The first one, not using time, results in an untimed TLM model. It often corresponds to under-specifying the model, because at least some timing information can be derived from the early specifications. The over-specification strategy consists in choosing an arbitrary value. The choice can be constrained in different ways. An example is to use an approximated value, plus or minus a certain percentage. Of course, the approximated value and the percentage are also arbitrary values. This leads to a model that looks like it is specified, but the values that are used do not actually mean a lot, thus it is an over-specification. A third strategy is to add in the model the fact that the information is partially known. Indeed, for most transactions, it is possible to find a minimum and a maximum time value that bounds the actual one (even if at start, this interval is wide). Such annotation indicates a partial information: we do not know the actual timing, but it will be within those bounds.

Among those three strategies, the one that adds the most information on the model is the third one, using time ranges. On one side, it adds information on the model, but on the other side it introduces the need for the simulator to support ranges. That has to do with how those time ranges are implemented. In practice, the SystemC kernel does not support time ranges, it needs time values. This is why, at STMicroelectronics, time ranges are part of the internal implementation of LT TLM, in an overlay on the SystemC kernel. A time range is specified using the function:

#### annotate loose timing(sc time min, sc time max)

In production code, this function picks a random time value within the bounds. We can notice that adding random values in the simulation does not remove the reproducibility: if the random seed, fixed at simulation start, stays the same then the same series of random numbers will be produced.

At first sight, using a random implementation for time ranges seems like the over-specification approach. However, the fact that we define time ranges as bounds for the real value enables the use of this information for other analysis tools. For example, Helmstetter [3] studied different scheduling orders of SystemC processes for different values chosen in time ranges. By studying the consequences of the different scheduling orders, it was possible to establish a list of orders that actually change the simulation results, thus are worth to simulate. We give another example of how those ranges can be exploited in the next chapter.

# 2.3.3 History of the STMicroelectronics/Verimag Collaboration

The Verimag laboratory is specialized in embedded systems, more precisely in improving their development, both in time and quality. In particular, Verimag is specialized in formal verification, testing, synchronous languages and modeling. Those fields are in line with the branch of STMicroelectronics in charge of systems on chip modeling, that has actively contributed to the standardization of SystemC and TLM. Over more than a decade, Verimag and STMicroelectronics have collaborated on SystemC/TLM modeling. The first thesis, by Matthieu Moy, studied the formal verification of SystemC/TLM models [4], i.e. proving properties on models. Claude Helmstetter worked on partial reduction of scheduling orders in the case of loosely timed models [3]. This work also includes study on simulation semantics, further discussed in Chapter 4. Jérôme Cornet worked on the refinement of models [5], by adding non-functional information to models without changing the functionality. Giovanni Funchal studied different aspects of TLM [6], in particular the consistency of models in comparison with the real chip, the semantic signification of TLM constructs and time modeling. Yussef Bouzouzou<sup>2</sup> studied static analysis of SystemC/TLM code, in order to implement a semantics-preserving parallel SystemC simulator for TLM models [7]. This work, as a parallel simulation approach, is further discussed in Chapter 4.

<sup>&</sup>lt;sup>2</sup>Verimag and Silicomp (Orange Business Services), in collaboration with STMicroelectronics.

# 2.4 High Level Synthesis

The High Level Synthesis (HLS) design flow consists in transforming code from a high abstraction level, generally written in C++, into synthesizable code in a Hardware Description Language (HDL), generally at Register Transfer Level (RTL). At STMicroelectronics, HLS is mainly used to design hardware acceleration components containing Intellectual Property (IP), also called IP blocks.

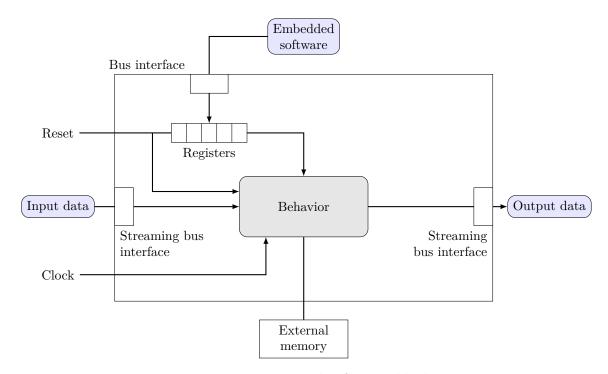

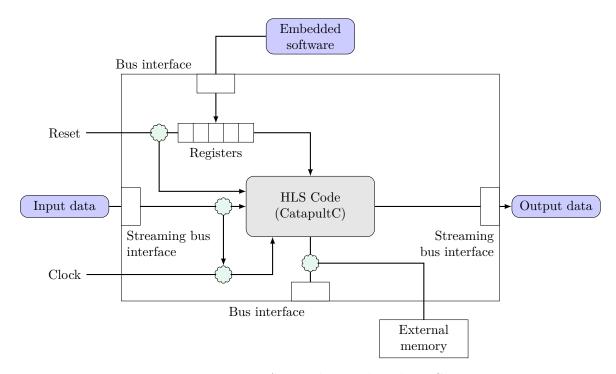

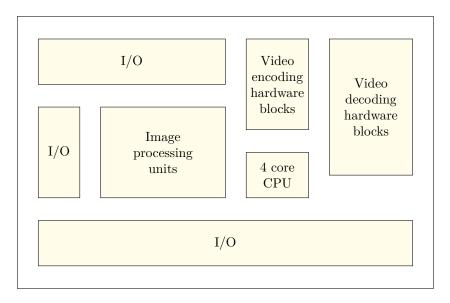

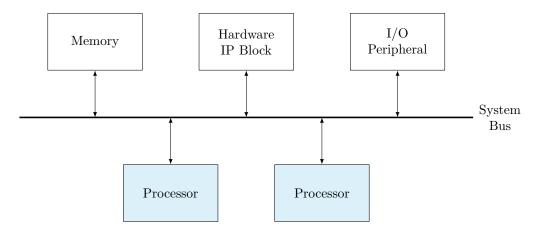

#### 2.4.1 Hardware Acceleration Blocks

Systems on chip are composed of hardware and embedded software, sometimes called firmware. The embedded software runs on one or several Central Processing Units (CPUs), and uses the different hardware blocks available in the system. Communications are made through bus components. We can distinguish application-specific hardware blocks from CPUs and bus components. The first ones are finely tuned (e.g. in terms of area, performance or power consumption) to implement a specific functionality (e.g. video decoding, motion detection, signal handling). They contain hardware intellectual property, and are a key differentiation factor from one vendor's chip to another.

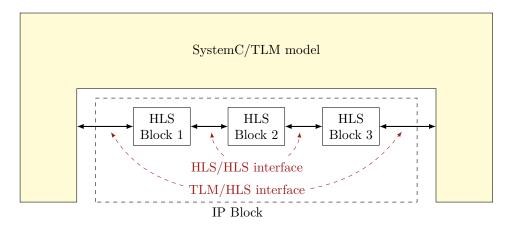

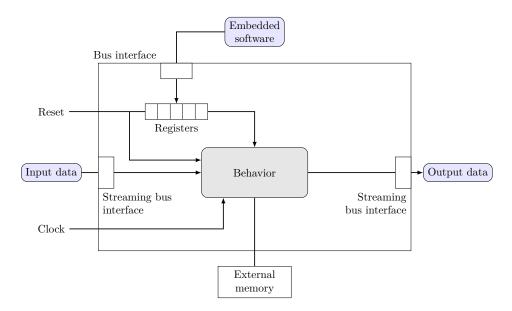

Figure 2.11: Example of an IP block.

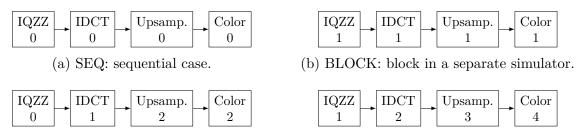

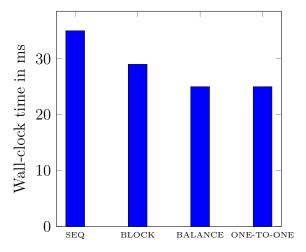

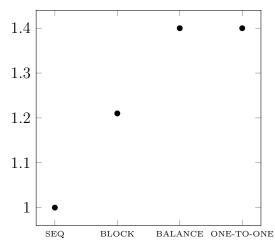

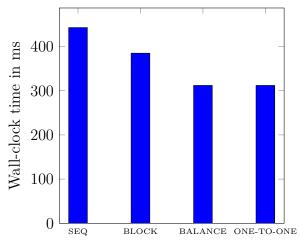

Figure 2.11 shows a typical IP block example. An important point to highlight on this figure is how the embedded software interacts with the block. This communication is