### Performance and Energy Consumption Characterization and Modeling of Video Decoding on Multi-core Heterogenous SoC and their Applications

Yahia Benmoussa

### ▶ To cite this version:

Yahia Benmoussa. Performance and Energy Consumption Characterization and Modeling of Video Decoding on Multi-core Heterogenous SoC and their Applications. Multimedia [cs.MM]. Université de Bretagne Occidentale, 2015. English. NNT: . tel-01313326

### HAL Id: tel-01313326 https://hal.science/tel-01313326

Submitted on 9 May 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

THESE / UNIVERSITE DE BRETAGNE OCCIDENTALE

sous le sceau de l'Université Européenne de Bretagne pour obtenir le titre de

DOCTEUR DE L'UNIVERSITE DE BRETAGNE OCCIDENTALE

Mention : Informatique

École doctorale SICMA

Présentée par Yahia BENMOUSSA

Préparée au Lab-STICC - Laboratoire des Sciences et Techniques de l'Information, de la Communication et de la Connaissance. Brest/Lorient

Performance and Energy

Consumption Characterization

and Modeling of Video

Decoding on Multi-core

Heterogenous SoC

and their Applications

### Thèse soutenue le 16 Juin 2015

devant le jury composé de :

#### Frank Singhoff

Professeur, UBO Brest / Président du jury

### **Daniel Menard**

Maitre de conférences, HDR, Université de Rennes 1 / Rapporteur

### **Daniel Chillet**

Maitre de conférences, HDR, Enssat / Rapporteur

#### **Smail Niar**

Professeur, Université de Valencienne / Examnateur

#### **Mouloud Koudil**

Professeur, École Supérieure d'Informatique/ Examinateur

#### Eric SENN

Maitre de conférences, HDR, UBS Lorient / Directeur de thèse

#### Jalil Boukhobza

Maitre de conférences, UBO Brest / co-encadrant

### **Djamel Benazzouz**

Professeur, Université de Boumerdes / Co-directeur de thèse

To my mother, my father and all my family.

Foremost, I would like to express my gratitude to Jalil Boukhobza for his valuable help and feedback during this thesis. My sincere thanks also goes to Eric Senn and Djamel Benazzouz for their supports.

Many thanks to my thesis committee for accepting to evaluate this work.

I must also acknowledge the Lab-STICC, the computer science department of the University of Western Brittany in Brest and the M'Hamed Bougara University of Boumerdes for their financial support.

Special thanks to Yassine Hadjadj-Aoul from University of Rennes for his numerous comments and suggestions, Michael Lanoe for his help in using Open-PEOPLE platform, and Richard Jouet from Laudren Electronics for his technical help in instrumenting embedded boards used in my thesis experimentations.

Finally, I would like to thank to all those who helped me to achieve this work.

### Abstract

To meet the increasing complexity of mobile multimedia applications, the System on Chip (SoC) equipping modern mobile devices integrate powerful heterogeneous processing elements among which General Purpose Processors (GPP), Digital Signal Processors (DSP), hardware accelerator are the most common ones.

Due to the ever-growing gap between battery lifetime and hardware/software complexity in addition to application computing power needs, the energy saving issue becomes crucial in the design of such systems. In this context, we propose a study aiming to enhance the understanding of the energy consumption behavior of video decoding on these kinds of systems.

Accordingly, an end-to-end methodology for characterizing and modeling the performance and the energy consumption of video decoding on GPP and DSP is proposed. The characterization step is based on an exhaustive experimental methodology for evaluating, at different abstraction levels, the performance and the energy consumption of video decoding. It was achieved on embedded platforms on which were executed a wide range of video decoding configurations. This step highlighted the importance to consider different parameters which may pertain to different abstraction levels in evaluating the overall energy efficiency of a given system.

The measurements obtained in this step were used to build empirically performance and energy models for video decoding on both GPP and DSP. The proposed models gave very accurate estimation ( $R^2 = 97\%$ ) of both the performance and the energy consumption of video decoding in terms of a rich set of parameters including the video quality and the processor frequency. Moreover, based on a multi-level characterization and sub-model decomposition approaches, we show how the developed models, unlike classic empirical models, are easily and rapidly generalizable to other platforms.

Some possible applications using the developed models, in the context of adaptive video decoding, were proposed. In general, it consists to use the capability of the proposed performance model to predict the decoding time of a given video quality in dimensioning/scheduling the processing resources.

Due to the increasing demand on High Definition (HD), the characterization methodology was extended to consider HD video decoding on both parallel multi-cores and hardware video accelerator. This part highlighted the potential of parallelism video decoding to increase the energy efficiency of video decoding and point out some open issues in this domain.

### Résumé

Pour répondre à la complexité croissante des applications multimédia mobiles, les systèmes sur puce équipant les appareils mobiles modernes intègrent des unités de calcul puissantes et hétérogène. Parmi ces units de calcul, on peut trouver des processeurs à usage général, des processeur de traitement de signal et des accélérateurs matériels.

En raison de l'écart toujours croissant entre la durée de vie des batteries et la demande de plus en plus importante en puissance de calcul, l'économie d'énergie devient un enjeu crucial dans la conception des systèmes mobiles. Cette problématique est accentuée par l'augmentation de la complexité des logiciels et architectures matériels utilisés. Dans ce contexte, nous proposons une étude visant à améliorer la compréhension des considérations énergétiques du décodage vidéo sur ce genre de systèmes.

Nous proposerons ainsi une méthodologie pour la caractérisation et la modélisation des performances et de la consommation d'énergie du décodage vidéo, aussi bien sur des processeurs à usage général de type ARM que sur un processeur de traitement de signal. L'étape de caractérisation est basée sur une méthodologie expérimentale pour évaluer de faon exhaustive et à différents niveaux d'abstraction, les performances et la consommation d'énergie du décodage vidéo. Cette caractérisation a été réalisée sur des plates-formes embarquées sur lesquels ont été exécutés un large éventail de configurations du décodage vidéo. Cette étape a souligné l'importance d'examiner différents paramètres qui peuvent se rapporter à différents niveaux d'abstraction dans l'évaluation de l'efficacité énergétique globale d'un système donné.

Les mesures obtenues dans cette étape ont été utilisées pour construire empiriquement des modèles de performance et de consommation d'énergie pour le décodage vidéo à la fois sur des processeurs à usage général type ARM et sur un processeur de traitement de signal. Les modèles proposés peuvent estimer avec une grande précision ( $R^2 = 97\%$ ) la performance et la consommation d'énergie de décodage vidéo en fonction d'un nombre de paramètres comprenant la qualité de la vidéo et la fréquence du processeur. En plus, en se basant sur une caractérisation multi-niveaux et une approches de modélisation par décomposition en sous-modèles, nous montrons comment les modèles développés, contrairement aux modèles empiriques classiques, sont facilement et rapidement généralisables à d'autres plates-formes.

Nous proposerons également certaines applications possibles des modèles développés, dans le cadre du décodage vidéo adaptatif. En général, cela consiste à exploiter la capacité du modèle de performance proposé pour prédire le temps de décodage d'une qualité vidéo donnée afin de mieux dimensionner les ressources de calculs dans un but de réduire leur consommation d'énergie.

En raison de la croissance de l'utilisation des vidéos de haute définition (HD), la méthodologie de caractérisation a été étendu pour considérer le décodage vidéo HD aussi bien sur les architectures multi-coeurs parallèles que sur les accélérateurs vidéo matériels. Cette partie a souligné le potentiel de décodage vidéo parallèle pour augmenter l'efficacité énergétique du décodage vidéo et met en exergue les principaux défis rencontrés dans cet axe.

## Contents

| List of Figures |                                      |        |                                                                 |      |  |  |  |  |

|-----------------|--------------------------------------|--------|-----------------------------------------------------------------|------|--|--|--|--|

| Li              | List of Tables                       |        |                                                                 |      |  |  |  |  |

| Li              | List of Abbreviations & Notations xi |        |                                                                 |      |  |  |  |  |

| Li              | ist of                               | Publi  | cations                                                         | viii |  |  |  |  |

| 1               | Intr                                 | oduct  | ion                                                             | 1    |  |  |  |  |

|                 | 1.1                                  | Conte  | xt                                                              | 2    |  |  |  |  |

|                 |                                      | 1.1.1  | Increase in mobile devices power consumption                    | 2    |  |  |  |  |

|                 |                                      | 1.1.2  | New trends in mobile video applications usage : Implications on |      |  |  |  |  |

|                 |                                      |        | power consumption                                               | 3    |  |  |  |  |

|                 |                                      |        | 1.1.2.1 Increase in mobile video traffic                        | 3    |  |  |  |  |

|                 |                                      |        | 1.1.2.2 Ubiquitous video applications                           | 4    |  |  |  |  |

|                 |                                      | 1.1.3  | Complex multimedia mobile devices                               | 5    |  |  |  |  |

|                 |                                      |        | 1.1.3.1 Multi-core and heterogeneous processing                 | 6    |  |  |  |  |

|                 |                                      |        | 1.1.3.2 Sophisticated embedded operating systems                | 7    |  |  |  |  |

|                 | 1.2                                  | Proble | em statement : Energy consumption modeling of processor-based   |      |  |  |  |  |

|                 |                                      | video  | systems                                                         | 8    |  |  |  |  |

|                 |                                      | 1.2.1  | Low level modeling                                              | 9    |  |  |  |  |

|                 |                                      | 1.2.2  | High level modeling                                             | 10   |  |  |  |  |

|                 | 1.3                                  | Thesis | s scope and approach                                            | 10   |  |  |  |  |

|                 | 1.4                                  | Thesis | s contributions                                                 | 11   |  |  |  |  |

|                 |                                      | 1.4.1  | Experimental methodology                                        | 11   |  |  |  |  |

|                 |                                      | 1.4.2  | Energy characterization methodology                             | 12   |  |  |  |  |

|                 |                                      | 1.4.3  | Energy modeling methodology                                     | 13   |  |  |  |  |

|   |     | 1.4.4  | Applicat   | ions                                                     | 14 |

|---|-----|--------|------------|----------------------------------------------------------|----|

|   | 1.5 | Outlin | e          |                                                          | 14 |

| 2 | Bac | kgrour | nd and r   | elated works                                             | 16 |

|   | 2.1 | Introd | uction .   |                                                          | 18 |

|   | 2.2 | Backg  | round .    |                                                          | 18 |

|   |     | 2.2.1  | Concept    | s on video encoding and decoding                         | 18 |

|   |     |        | 2.2.1.1    | Principles of MPEG standards                             | 18 |

|   |     |        | 2.2.1.2    | Video quality assessment metrics                         | 21 |

|   |     |        | 2.2.1.3    | Video playback QoS assessment metrics                    | 21 |

|   |     |        | Γ          | Oeadline miss rate (DMR)                                 | 22 |

|   |     |        | Γ          | Decoded frames per second (FPS)                          | 22 |

|   |     |        | L          | atency                                                   | 22 |

|   |     | 2.2.2  | Energy     | consumption in electronic circuits                       | 23 |

|   |     |        | 2.2.2.1    | Static vs dynamic energy consumption                     | 23 |

|   |     |        | 2.2.2.2    | Dynamic voltage and frequency scaling (DVFS)             | 24 |

|   |     |        | 2.2.2.3    | Dynamic Power management (DPM)                           | 24 |

|   |     | 2.2.3  | Discussi   | on                                                       | 25 |

|   | 2.3 | Princi | ples of en | ergy saving in video decoding                            | 25 |

|   |     | 2.3.1  | Frequen    | cy scaling: Performance vs energy consumption            | 27 |

|   |     |        | 2.3.1.1    | Frame-by-frame based DVFS                                | 27 |

|   |     |        | 2.3.1.2    | Average workload based DVFS                              | 27 |

|   |     |        | 2.3.1.3    | Video-aware DVFS : Challenges and issues                 | 28 |

|   |     | 2.3.2  | Parallel   | multi-core video decoding                                | 29 |

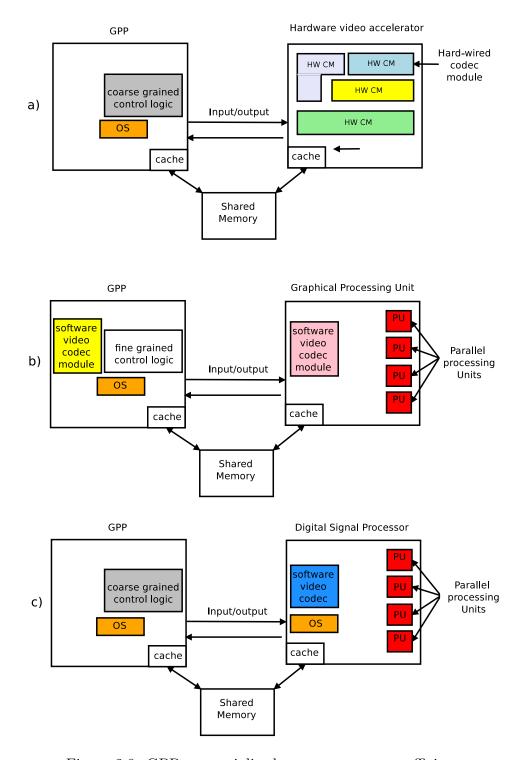

|   |     | 2.3.3  | Specializ  | zed processing                                           | 30 |

|   |     |        | 2.3.3.1    | Hardware video codecs                                    | 30 |

|   |     |        | 2.3.3.2    | Graphical processing unit                                | 31 |

|   |     |        | 2.3.3.3    | Digital signal processor                                 | 33 |

|   |     | 2.3.4  | Discussi   | on                                                       | 33 |

|   | 2.4 | Perfor | mances a   | nd energy consumption characterization of video decoding | 34 |

|   |     | 2.4.1  | Video de   | ecoding performances characterization                    | 34 |

|   |     |        | 2.4.1.1    | Application level                                        | 34 |

|   |     |        | 2.4.1.2    | System level                                             | 35 |

|   |     |        | 2.4.1.3 Architecture level                                | 35                              |  |  |  |

|---|-----|--------|-----------------------------------------------------------|---------------------------------|--|--|--|

|   |     | 2.4.2  | Video decoding energy consumption characterization        | 36                              |  |  |  |

|   |     |        | 2.4.2.1 Application level                                 | 36                              |  |  |  |

|   |     |        | 2.4.2.2 System level                                      | 37                              |  |  |  |

|   |     |        | 2.4.2.3 Architecture level                                | 37                              |  |  |  |

|   |     | 2.4.3  | Discussion                                                | 38                              |  |  |  |

|   | 2.5 | Perfor | rmances and energy consumption modeling of video decoding | 40                              |  |  |  |

|   |     | 2.5.1  | Video decoding performances modeling                      | 40                              |  |  |  |

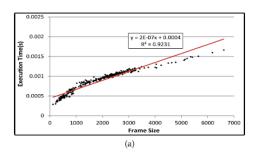

|   |     |        | 2.5.1.1 Frame based models                                | 40                              |  |  |  |

|   |     |        | Empirical models                                          | 40                              |  |  |  |

|   |     |        | Statistical models                                        | 41                              |  |  |  |

|   |     |        | Metadata-based models                                     | 42                              |  |  |  |

|   |     |        | 2.5.1.2 Interval-based models                             | 42                              |  |  |  |

|   |     |        | 2.5.1.3 Memory-aware performance models                   | 44                              |  |  |  |

|   |     | 2.5.2  | Video decoding energy consumption modeling                | 45                              |  |  |  |

|   |     |        | 2.5.2.1 Application level                                 | 45                              |  |  |  |

|   |     |        | 2.5.2.2 System level                                      | 46                              |  |  |  |

|   |     |        | 2.5.2.3 Architecture level                                | 47                              |  |  |  |

|   |     | 2.5.3  | Discussion                                                | 47                              |  |  |  |

|   | 2.6 | Concl  | usions                                                    | 49                              |  |  |  |

| 3 | Mod | thadal | o grv                                                     | 50                              |  |  |  |

| J | 3.1 |        |                                                           |                                 |  |  |  |

|   | 3.2 |        |                                                           | <ul><li>51</li><li>52</li></ul> |  |  |  |

|   | 9.2 | 3.2.1  |                                                           | 53                              |  |  |  |

|   |     | 3.2.1  |                                                           | 54                              |  |  |  |

|   |     | 3.2.3  |                                                           | 56                              |  |  |  |

|   |     | 3.2.4  |                                                           | 56                              |  |  |  |

|   | 3.3 |        | •                                                         | 57                              |  |  |  |

|   | 0.0 | 3.3.1  |                                                           | 58                              |  |  |  |

|   |     | 3.3.2  |                                                           | 59                              |  |  |  |

|   |     | 3.3.3  |                                                           | 59                              |  |  |  |

|   |     | 3.3.4  |                                                           | 60                              |  |  |  |

|   |     | 0.0.4  | MOUGIS VAIIUAUUII                                         | UU                              |  |  |  |

|   | 3.4 | Experimental methodology |           |                                               |    |  |

|---|-----|--------------------------|-----------|-----------------------------------------------|----|--|

|   |     | 3.4.1                    | Hardwa    | re setup                                      | 61 |  |

|   |     |                          | 3.4.1.1   | MistralEVM3530                                | 61 |  |

|   |     |                          | 3.4.1.2   | PandaBoard                                    | 62 |  |

|   |     | 3.4.2                    | Power c   | onsumption measurement                        | 62 |  |

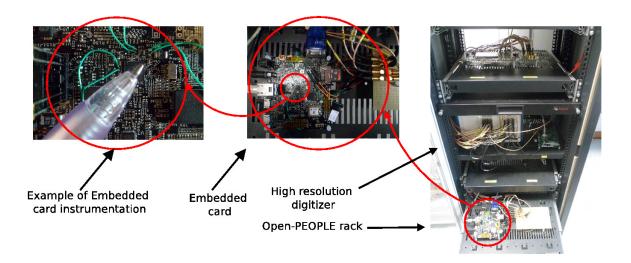

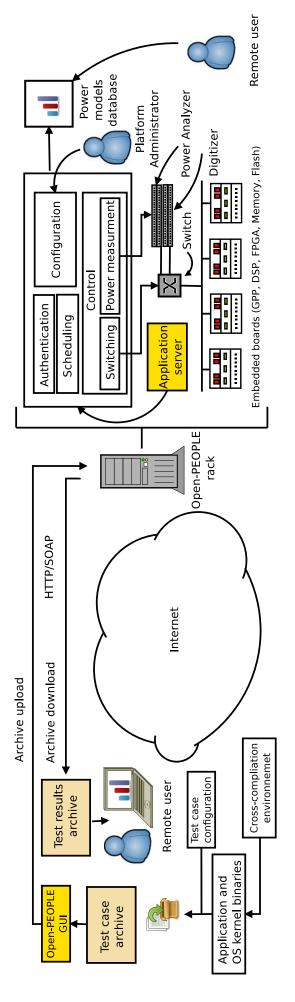

|   |     |                          | 3.4.2.1   | Open-PEOPLE platform                          | 62 |  |

|   |     |                          | 3.4.2.2   | Power consumption measurement methodology     | 65 |  |

|   |     |                          | 3.4.2.3   | Boards instrumentation                        | 66 |  |

|   |     |                          | N         | Mistral OMAP3530EVM                           | 66 |  |

|   |     |                          | F         | PandaBoard                                    | 67 |  |

|   |     | 3.4.3                    | Software  | e setup                                       | 67 |  |

|   |     |                          | 3.4.3.1   | Video encoder                                 | 67 |  |

|   |     |                          | 3.4.3.2   | Operating system                              | 68 |  |

|   |     |                          | Ι         | Oynamic power management                      | 69 |  |

|   |     |                          | F         | Prequency scaling                             | 69 |  |

|   |     |                          | 3.4.3.3   | Video decoder framework                       | 70 |  |

|   |     |                          | E         | Elimination of the I/O interference           | 71 |  |

|   |     |                          |           | Overhead calculation                          | 72 |  |

|   | 3.5 | Concl                    | usion     |                                               | 73 |  |

| 4 | Per | formaı                   | nce and   | Energy Consumption Characterization           | 74 |  |

|   | 4.1 | Introd                   | luction . |                                               | 75 |  |

|   | 4.2 | Video                    | complexi  | ty characterization                           | 75 |  |

|   | 4.3 | Video                    | decoding  | performance and energy characterization       | 76 |  |

|   |     | 4.3.1                    | Operation | ng-system level                               | 77 |  |

|   |     |                          | 4.3.1.1   | ARM processor                                 | 78 |  |

|   |     |                          | 4.3.1.2   | DSP processor                                 | 80 |  |

|   |     |                          | 4.3.1.3   | C-states transition overhead                  | 80 |  |

|   |     |                          | Ι         | Discussion                                    | 82 |  |

|   |     | 4.3.2                    | Video-fr  | rame level                                    | 83 |  |

|   |     |                          | 4.3.2.1   | Inter-processor communication time overhead   | 85 |  |

|   |     |                          | 4.3.2.2   | Inter-processor communication energy overhead | 87 |  |

|   |     |                          | 4.3.2.3   | Discussion                                    | 88 |  |

|   |     | 4.3.3    | Video-sequence level                                     | 3        |

|---|-----|----------|----------------------------------------------------------|----------|

|   |     |          | 4.3.3.1 Decoding time                                    | 3        |

|   |     |          | 4.3.3.2 Power consumption                                | )        |

|   |     |          | 4.3.3.3 Energy consumption                               | 2        |

|   |     |          | 4.3.3.4 Discussion                                       | 2        |

|   | 4.4 | Conclu   | asion                                                    | 1        |

| 5 | Per | formar   | nce and Energy Consumption Modeling of Video Decoding 96 | ;        |

|   | 5.1 | Introd   | uction                                                   | 7        |

|   | 5.2 | Video    | rate sub-model                                           | 3        |

|   |     | 5.2.1    | Parameters discussion                                    | )        |

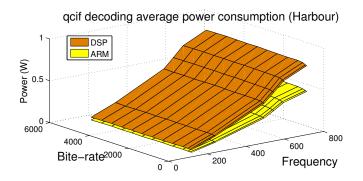

|   | 5.3 | Power    | sub-model                                                | )        |

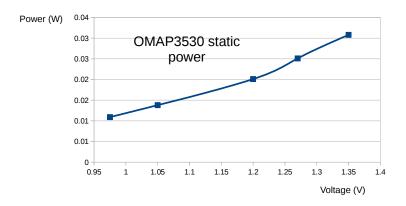

|   |     | 5.3.1    | Static power sub-model                                   | )        |

|   |     | 5.3.2    | Dynamic power sub-model                                  | )        |

|   |     |          | 5.3.2.1 ARM video decoding                               | )        |

|   |     |          | 5.3.2.2 DSP video decoding                               | )        |

|   |     |          | 5.3.2.3 Dynamic power modeling                           | 2        |

|   |     | 5.3.3    | Parameters discussion                                    | 2        |

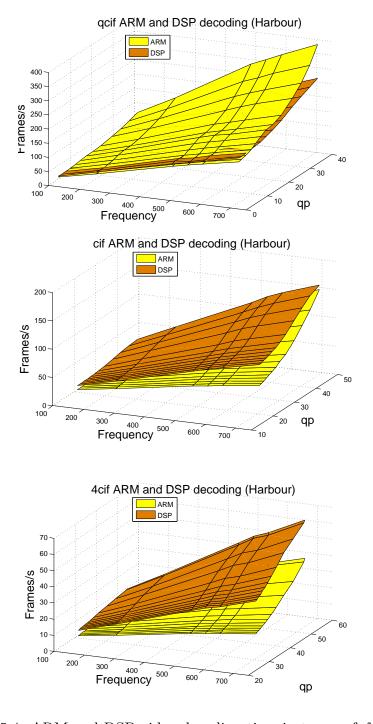

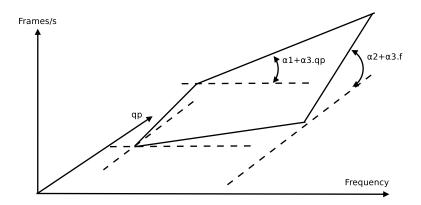

|   | 5.4 | Decod    | ing time sub-model                                       | }        |

|   |     | 5.4.1    | Parameters discussion                                    | <u>,</u> |

|   | 5.5 | Energ    | y model                                                  | 3        |

|   | 5.6 | Model    | s validation                                             | ;        |

|   |     | 5.6.1    | Models accuracy on OMAP3530                              | 7        |

|   |     |          | 5.6.1.1 Decoding time model                              | 7        |

|   |     |          | 5.6.1.2 Energy model                                     | 3        |

|   |     | 5.6.2    | Models generalization: OMAP4460 SoC case study           | )        |

|   |     |          | 5.6.2.1 Decoding time model                              | )        |

|   |     |          | 5.6.2.2 Energy model                                     | L        |

|   | 5.7 | Conclu   | asion                                                    | }        |

| 6 | App | olicatio | ons and open issues 114                                  | Ł        |

|   | 6.1 | Introd   | uction                                                   | 5        |

|   | 6.2 | Energy   | y-aware video decoding in adaptive streaming             | 5        |

|   |     | 6.2.1    | Motivational example                                     | 5        |

| Bi | ibliog | graphy  |                                                     |         | 153   | 3 |

|----|--------|---------|-----------------------------------------------------|---------|-------|---|

| 7  | Cor    | nclusio | ns and future works                                 |         | 135   | 5 |

|    | 6.5    | Concl   | usion                                               |         | . 134 | 1 |

|    |        | 6.4.2   | Processing migration on asymmetric multi-cores      |         | . 133 | 3 |

|    |        | 6.4.1   | Per-core frequency scaling                          |         | . 132 | 2 |

|    | 6.4    | Discus  | ssion                                               |         | . 132 | 2 |

|    |        |         | 6.3.3.2 Video decoding energy consumption           |         | . 128 | 3 |

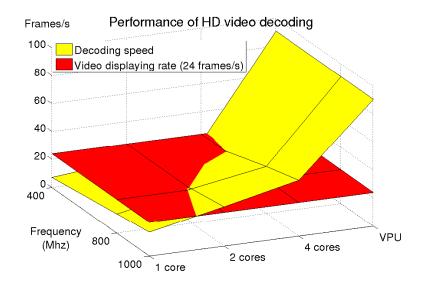

|    |        |         | 6.3.3.1 Video decoding performances                 |         | . 126 | ŝ |

|    |        | 6.3.3   | Experimental results                                |         | . 126 | ŝ |

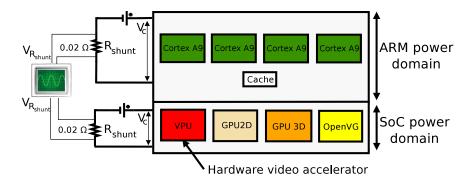

|    |        |         | 6.3.2.3 Energy consumption measurement              |         | . 126 | 3 |

|    |        |         | 6.3.2.2 Performance measurement                     |         | . 125 | 5 |

|    |        |         | 6.3.2.1 Hardware and software setup                 |         | . 124 | 1 |

|    |        | 6.3.2   | Experimental evaluation                             |         | . 124 | 1 |

|    |        | 6.3.1   | Motivation                                          |         |       | 3 |

|    | 6.3    | Energ   | y efficiency of high definition video decoding      |         | . 123 | 3 |

|    |        |         | 6.2.3.2 Proposed solution                           |         | . 121 | 1 |

|    |        |         | 6.2.3.1 Problem description                         |         |       |   |

|    |        | 6.2.3   | Video-quality aware DVFS                            |         |       |   |

|    |        |         | 6.2.2.3 Evaluation                                  |         |       |   |

|    |        |         | 6.2.2.2 Implementation                              |         |       |   |

|    |        |         | 6.2.2.1 Principles                                  |         |       |   |

|    |        |         | multi-core $SoCs$                                   |         |       | ô |

|    |        | 6.2.2   | Energy aware scheduling of video decoding on hetero | ogeneou | lS    |   |

# List of Figures

| 1.1  | SoC consumer portable power consumption trends [1]                       | 2  |

|------|--------------------------------------------------------------------------|----|

| 1.2  | Evolution of mobile video traffic                                        | 3  |

| 1.3  | Energy consumption in a mobile device (Video playback)                   | 4  |

| 1.4  | Ubiquitous wireless video streaming to different mobile devices over di- |    |

|      | verse wireless access networks                                           | 4  |

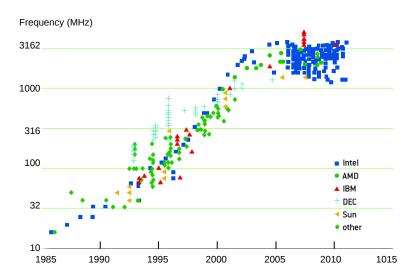

| 1.5  | Evolution of possessor frequencies                                       | 5  |

| 1.6  | Heterogeneous cores in mobile SoC                                        | 6  |

| 1.7  | Energy efficiency $vs$ processor type [2]                                | 7  |

| 1.8  | Energy modeling methodologies and levels                                 | 10 |

| 1.9  | Thesis contributions                                                     | 12 |

| 2.1  | Structure of a video sequence                                            | 19 |

| 2.2  | Principles of video encoding/decoding                                    | 20 |

| 2.3  | Video decoding performance metrics                                       | 22 |

| 2.4  | Frequency scaling in video decoding                                      | 26 |

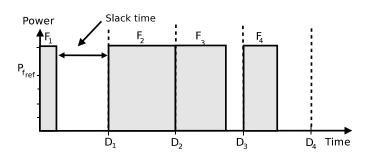

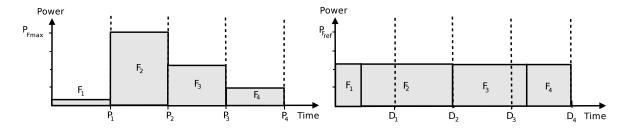

| 2.5  | Just-in-time DVFS                                                        | 27 |

| 2.6  | Workload averaging DVFS                                                  | 27 |

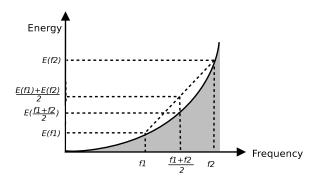

| 2.7  | Energy model convexity                                                   | 28 |

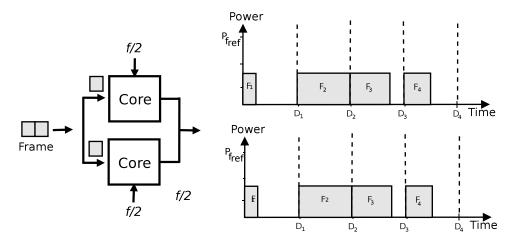

| 2.8  | Energy efficiency of parallel video decoding                             | 29 |

| 2.9  | GPP vs specialized processors energy efficiency                          | 32 |

| 2.10 | Video decoding complexity $vs$ frame size (MPEG2 vs H.264/AVC) [3] .     | 41 |

| 2.11 | Impact of memory latency on performance scaling [4]                      | 44 |

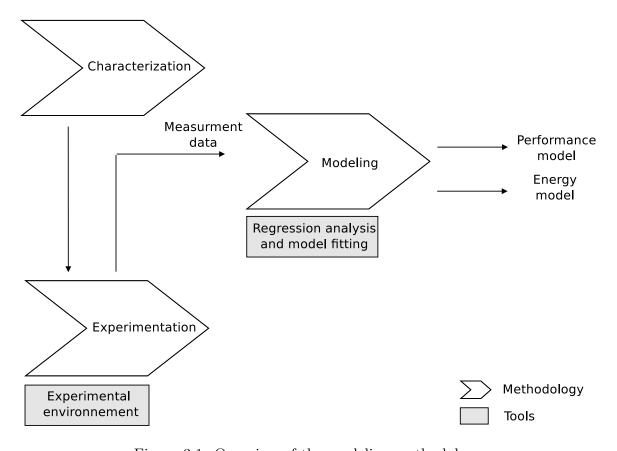

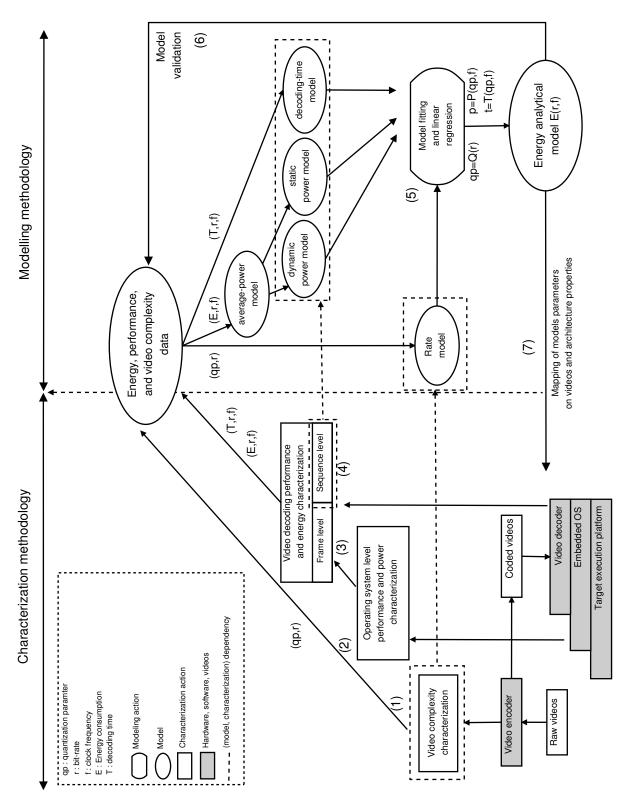

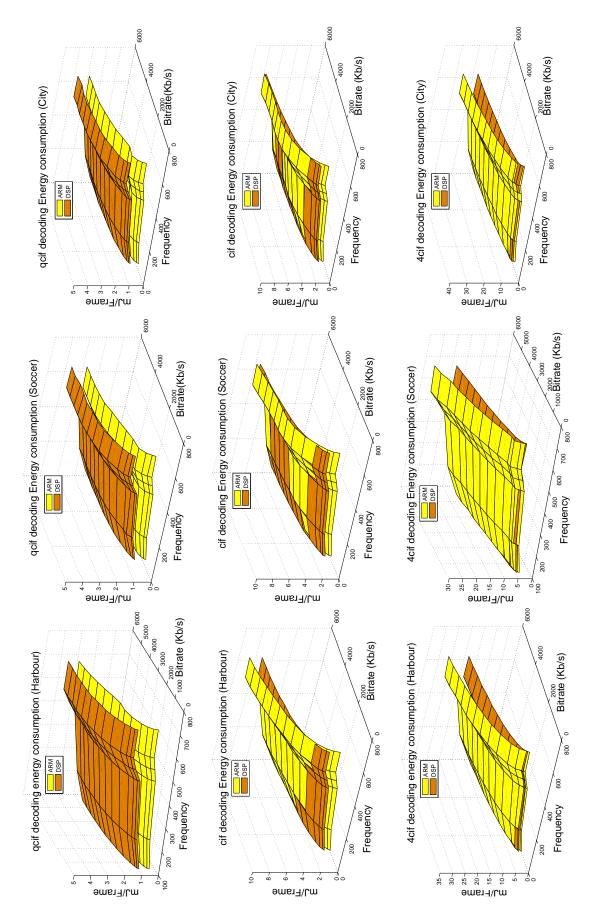

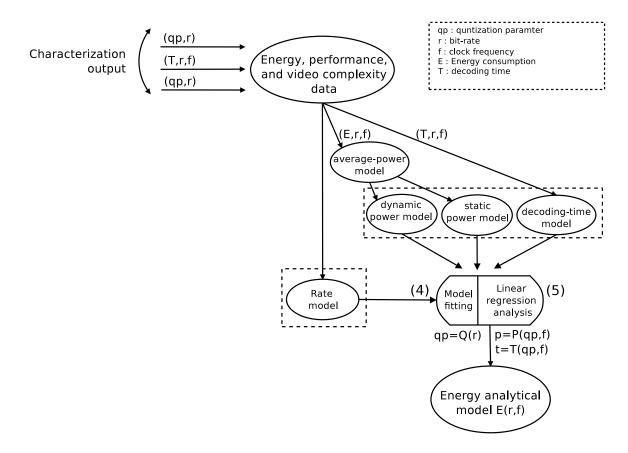

| 3.1  | Overview of the modeling methodology                                     | 51 |

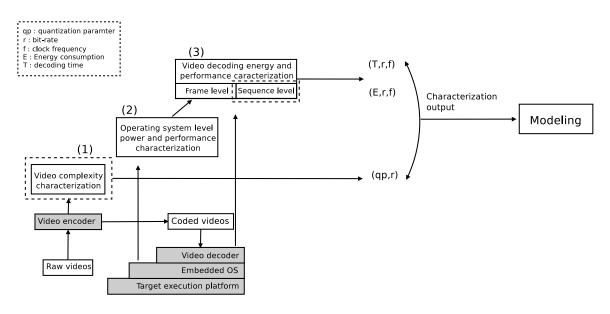

| 3.2  | Characterization and modeling methodology                                | 55 |

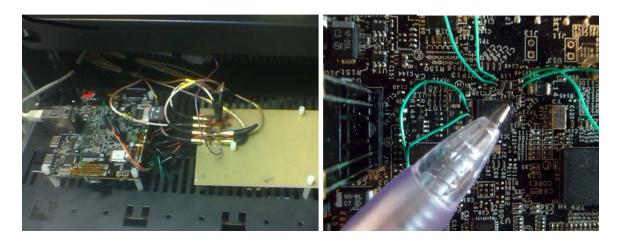

| 3.3  | Mistral EVM3530 Board (left) and PandaBoard ES (right)                   | 62 |

| 3.4  | A view on Open-PEOPLE rack                                               | 63 |

| 3.5  | Open-PEOPLE platform architecture                                                               | 64  |

|------|-------------------------------------------------------------------------------------------------|-----|

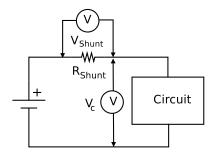

| 3.6  | Power consumption measurement using a shunt resistor                                            | 65  |

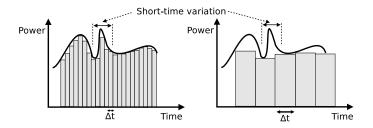

| 3.7  | Sampling rate of the energy consumption measurement                                             | 66  |

| 3.8  | PandaBoard-ES Instrumentation                                                                   | 67  |

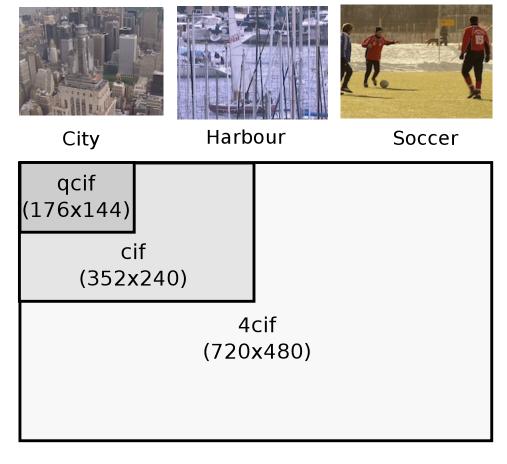

| 3.9  | Used video test sequences                                                                       | 68  |

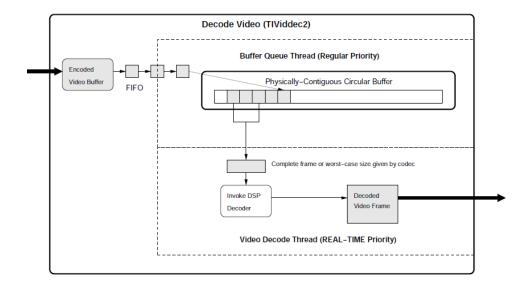

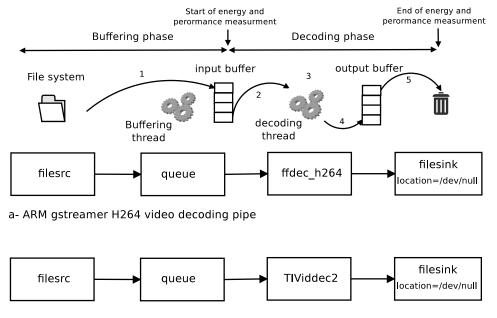

| 3.10 | GStreamer DSP video decoding plug-in                                                            | 70  |

| 3.11 | GStreamer GPP and DSP video decoding pipes                                                      | 72  |

| 4.1  | Characterization methodology                                                                    | 75  |

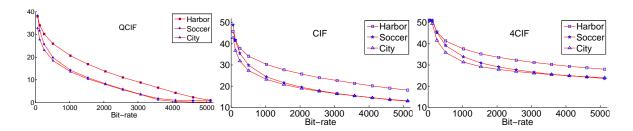

| 4.2  | Mapping between the video $qp_{avg}$ and the bit-rates                                          | 76  |

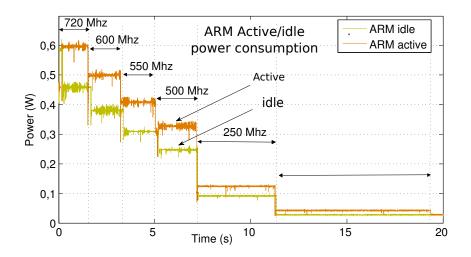

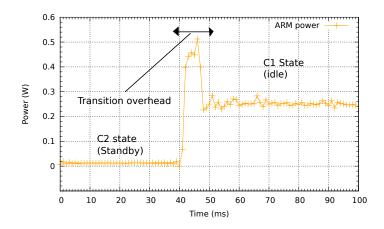

| 4.3  | Cortex A8 power consumption                                                                     | 78  |

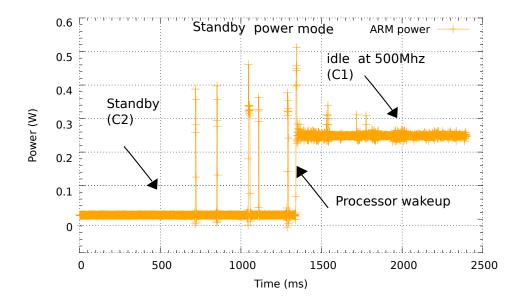

| 4.4  | Power consumption of standby mode                                                               | 79  |

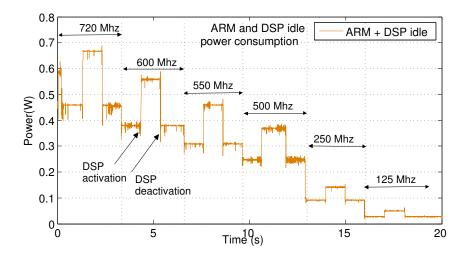

| 4.5  | TMS320C64x DSP power consumption                                                                | 79  |

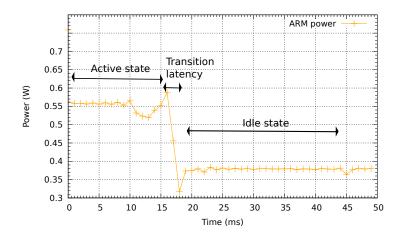

| 4.6  | ARM <i>idle</i> mode transition latency                                                         | 80  |

| 4.7  | ARM standby mode transition latency                                                             | 81  |

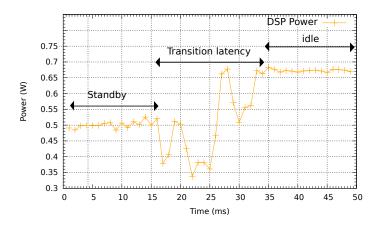

| 4.8  | DSP standby mode transition latency                                                             | 81  |

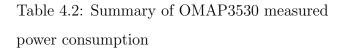

| 4.9  | OMAP3530 power consumption                                                                      | 82  |

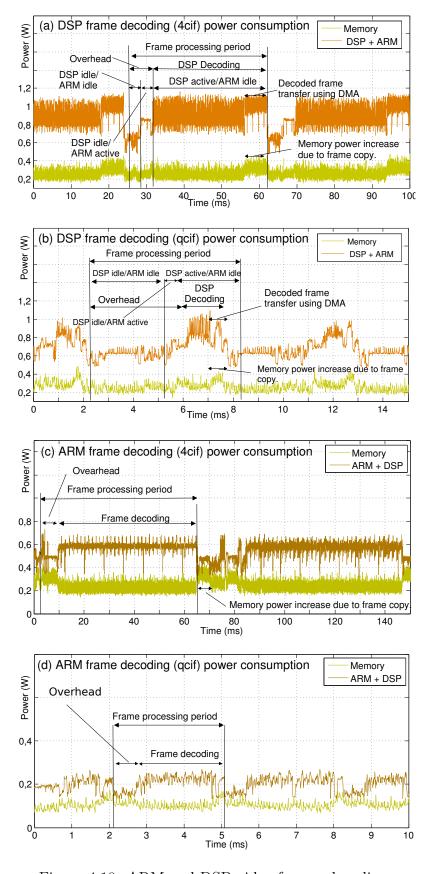

| 4.10 | ARM and DSP video frames decoding                                                               | 84  |

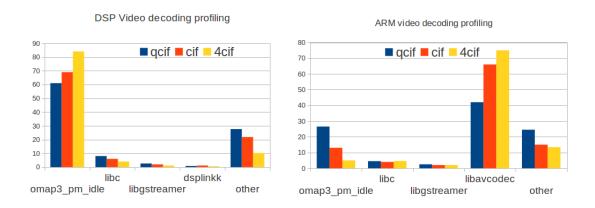

| 4.11 | Profiling result of ARM and DSP video decoding                                                  | 86  |

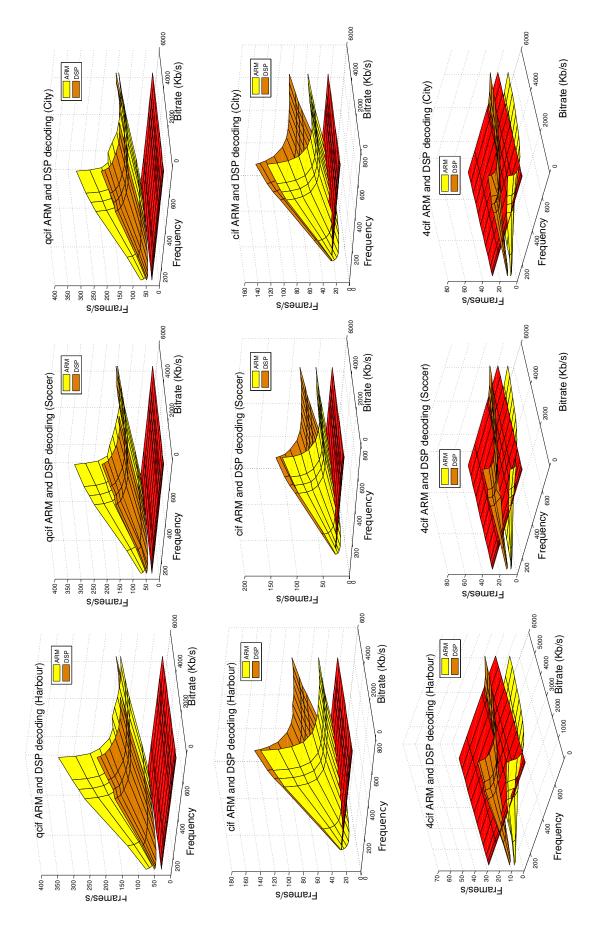

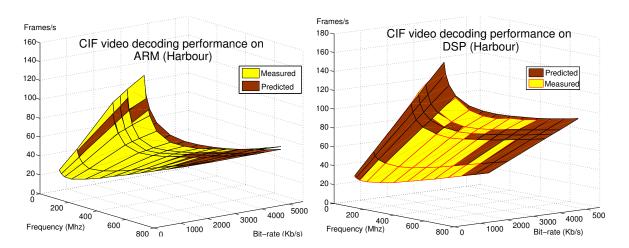

| 4.12 | ARM and DSP video decoding performance                                                          | 89  |

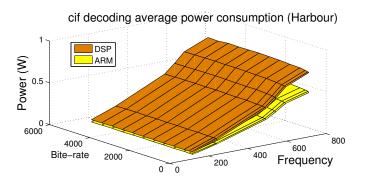

| 4.13 | ARM and DSP video decoding power consumption                                                    | 91  |

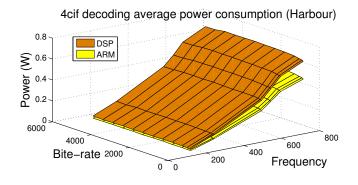

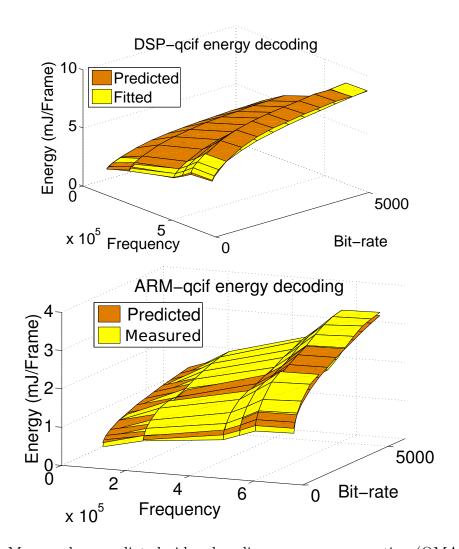

| 4.14 | ARM and DSP video decoding energy consumption                                                   | 93  |

| 5.1  | Modeling methodology                                                                            | 97  |

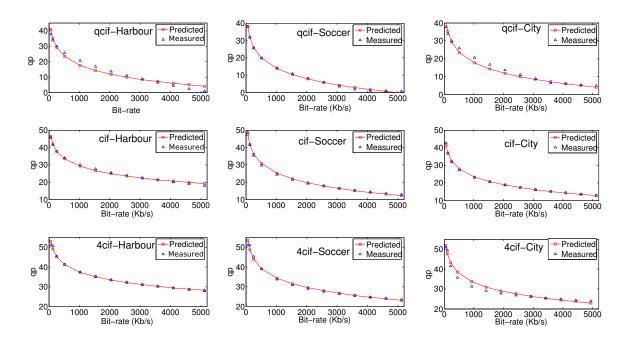

| 5.2  | Rate model fitting                                                                              | 99  |

| 5.3  | OMAP3530 static power                                                                           | 100 |

| 5.4  | ARM and DSP video decoding time in terms of $f$ and $qp$                                        | 103 |

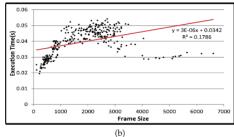

| 5.5  | Performance scaling behavior                                                                    | 106 |

| 5.6  | Measured vs predicted video decoding time (OMAP3530)                                            | 108 |

| 5.7  | Measured vs predicted video decoding energy consumption (OMAP3530)                              | 109 |

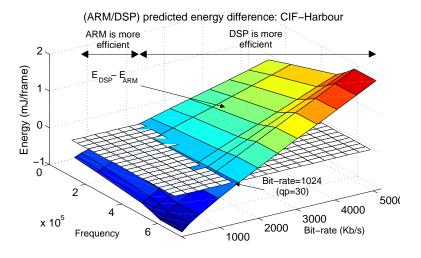

| 5.8  | Difference between ARM and DSP energy consumption (OMAP3530) $% \left( \frac{1}{2}\right) =0$ . | 109 |

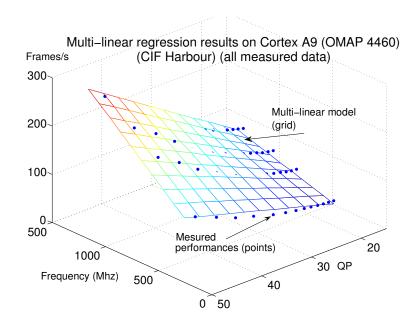

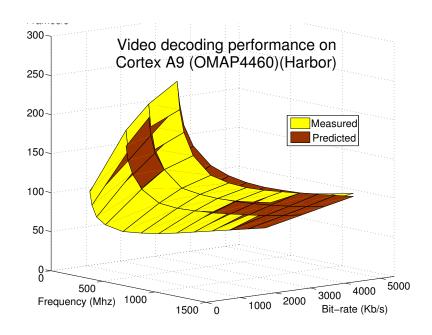

| 5.9  | Multi-linear regression of the video decoding time (OMAP4460) $$                                | 110 |

| 5.10 | Measured vs predicted video decoding time (OMAP4460)                                            | 111 |

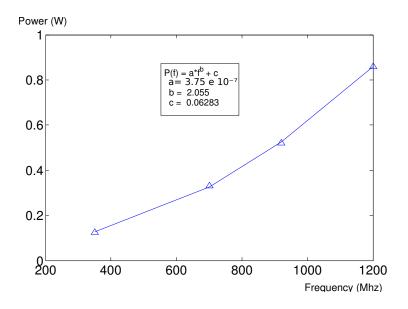

| 5.11 | Cortex A9 power consumption model                                                               | 112 |

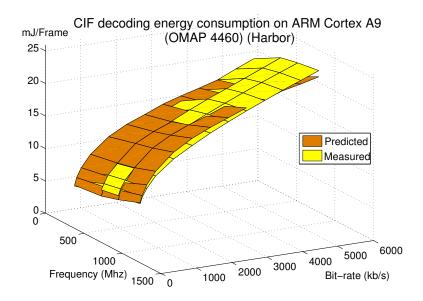

| 5.12 | Measured vs predicted video decoding energy consumption (OMAP4460)    | 112 |

|------|-----------------------------------------------------------------------|-----|

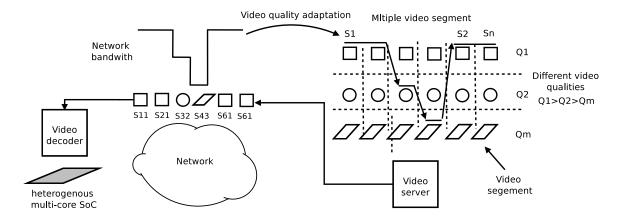

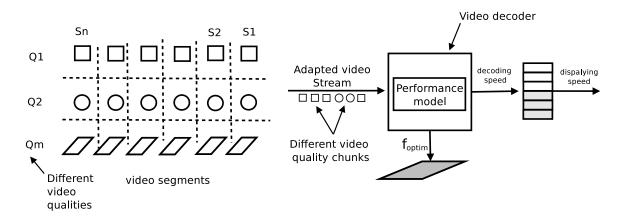

| 6.1  | Adaptive streaming                                                    | 116 |

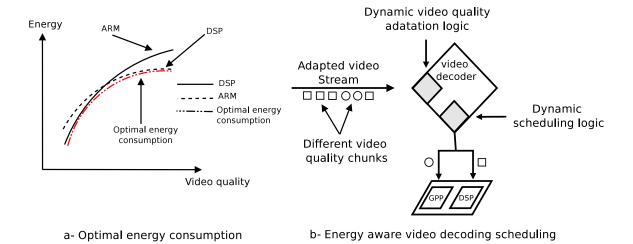

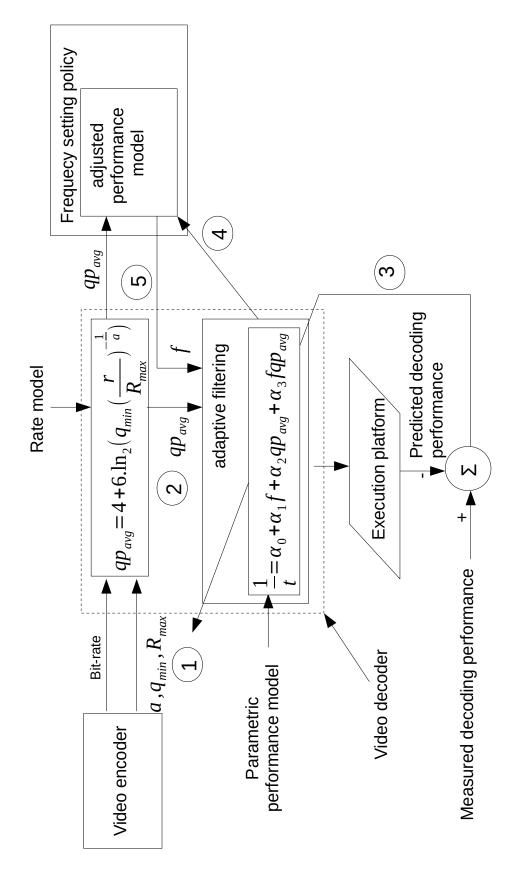

| 6.2  | Video-quality and energy aware video decoding on heterogeneous $SoCs$ | 117 |

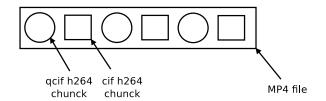

| 6.3  | Embedding video chunks in MP4 file                                    | 118 |

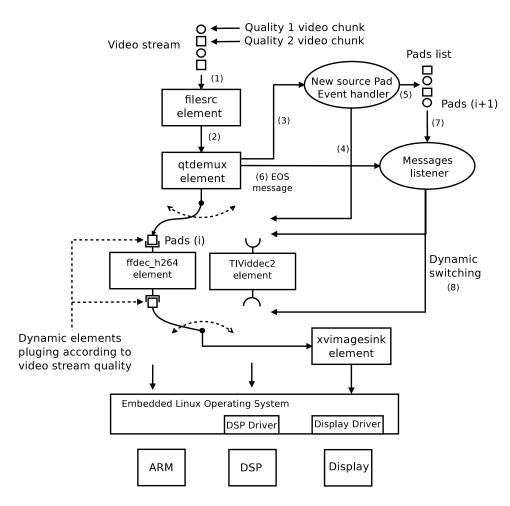

| 6.4  | Dynamic processor switching solution design using GStreamer           | 119 |

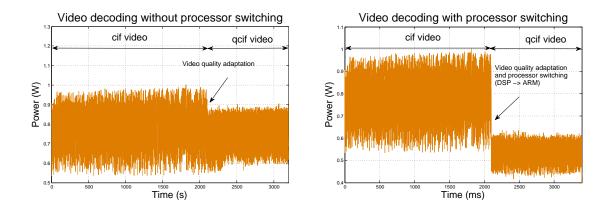

| 6.5  | Impact of dynamic processor switching on video decoding power con-    |     |

|      | sumption                                                              | 120 |

| 6.6  | Video-quality aware DVFS                                              | 120 |

| 6.7  | Performance and energy consumption models building                    | 122 |

| 6.8  | i.MX6 SoC power domains                                               | 125 |

| 6.9  | Performance of HD video decoding (i.MX6)                              | 127 |

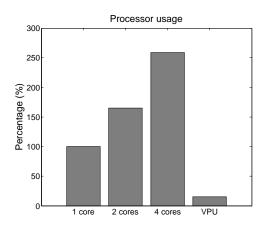

| 6.10 | Processor usage of HD video decoding                                  | 127 |

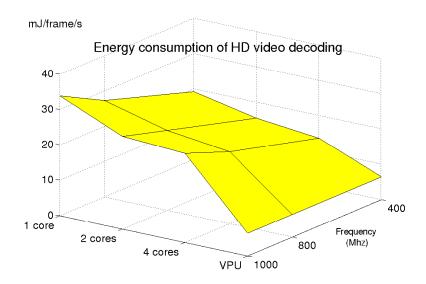

| 6.11 | Energy consumption of HD video decoding (i.MX6 SoC)                   | 128 |

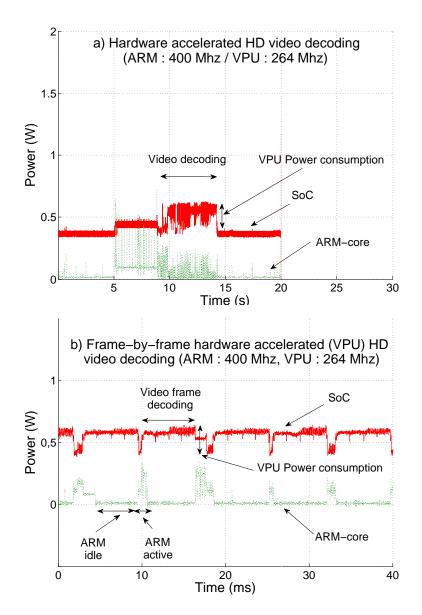

| 6.12 | VPU HD Video decoding power consumption                               | 129 |

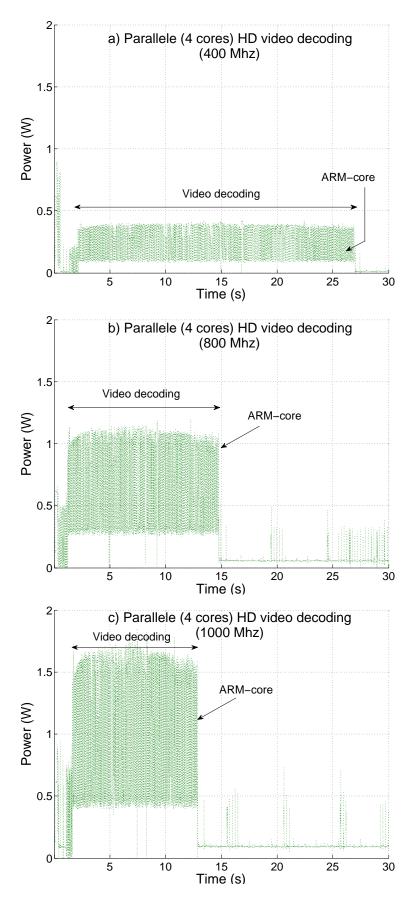

| 6.13 | Parallel multi-core HD video decoding energy consumption              | 130 |

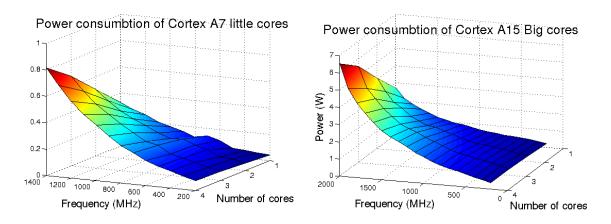

| 6.14 | Power consumption of little and big core in Exynos 5422 SoC           | 133 |

# List of Tables

| 2.1 | Video frame complexities                                                | 26  |

|-----|-------------------------------------------------------------------------|-----|

| 2.2 | Summary of studies on performance and energy characterization of video  |     |

|     | decoding                                                                | 39  |

| 2.3 | Summary of studies on performance and energy modeling of video decoding | 48  |

| 3.1 | Mobile devices using OMAP SoCs                                          | 61  |

| 3.2 | Power measurement materiel                                              | 63  |

| 3.3 | Hardware and software setup summary                                     | 71  |

| 4.1 | Mapping between $qp$ and the bit-rate                                   | 77  |

| 4.2 | Summary of OMAP3530 measured power consumption                          | 82  |

| 4.3 | ARM and DSP decoding time overhead                                      | 85  |

| 4.4 | Results of video decoding profiling                                     | 86  |

| 4.5 | ARM and DSP decoding energy overhead                                    | 87  |

| 4.6 | Energy efficiency $vs$ Processor type $vs$ video quality                | 94  |

| 5.1 | Model fitting results of the bit-rate model                             | 98  |

| 5.2 | Model fitting results of the dynamic power model                        | 101 |

| 5.3 | Multi-linear regression of $1/t$ in terms of $f$ and $qp$               | 104 |

| 5.4 | Summary of the model constant parameters                                | 107 |

| 5.5 | Performance model $R^2$                                                 | 108 |

| 5.6 | Energy model $R^2$                                                      | 108 |

| 6.1 | HD video decoding performances (fps) (i.MX6)                            | 126 |

| 6.2 | HD video decoding energy consumption (mJ/Frame) (i.MX6)                 | 128 |

### List of Abbreviations & Notations

### Abbreviations

ARM Advanced RISC Machines

ASIC Application Specific Integrated Circuit

CBR Constant Bit Rate

CISC Complex Instruction Set Computing

CMOS Complementary Metal-Oxide Semiconductor

DASH Dynamic Adaptive Streaming over HTTP

DCT Discrete cosine transform

DMA Direct Memory Access

DMR Deadline Miss Rate

DPM Dynamic Power Management

DSP Digital Signal Processor

DVFS Dynamic Voltage and Frequency Scaling

EOS Embedded Operating System

ES Embedded System

FPS Frames Per Second

GPP General Purpose Processor

GPU Graphical Processing unit

HD High Definition

HEVC High Efficiency Video Coding

IDCT Inverse Discrete cosine transform

IPC Inter Process Communication

IPTV Internet Protocol television

MB Macroblock

MPEG Moving Picture Experts Group

OMAP Open Multimedia Applications Platform

OS Operating System

PSNR Peak Signal-to-Noise Ratio

QoS Quality of Service

qp Quantization parameter

RISC Reduced Instruction Set Computing

SD Standard Definition

SIMD Single Instruction Multiple Data

SoC System on Chip

VBR Variable Bit Rate

VPU Video Processing Unit

WFI Wait For Interrupt

### **Notations**

a Rate model exponent

$C_{eff}$  Effective capacitance

$E_{dun}$  Dynamic energy

$E_{static}$  Static energy

$E, E_{tot}$  Total energy (static + dynamic)

$E(\ldots)$  Energy model

$f_{arm}$  Frequency of the ARM processor

$f_{dsp}$  Frequency of the DSP processor

f Processor frequency

I Current intensity

$P_{dyn}$  Dynamic power

$P_{idle}$  Idle state power

$P_{static}$  Static power

$P, P_{tot}$  Total power (static + dynamic)

$P(\ldots)$  Power model

$q_{min}$  Minimum step-size

$qp_{avq}$  Average quantization parameter

qp Quantization parameter

q Step-size

$Q(\ldots)$  Rate model

$R_{display}$  Video display rate

$r_{max}$  Maximum bit-rate

$R_{shunt}$  Shunt resistor

r Bite-rate

t Time

$T(\ldots)$  Time model

$V, v_{dd}$  Voltage

$V_{shunt}$  Voltage across a shunt resistor

### List of publications

#### Journals

- Y. Benmoussa, J. Boukhobza, E. Senn, Y. Hadjadj-Aoul, D. Benazzouz. A Methodology for Performance/Energy Consumption Characterization and Modeling of Video Decoding on Heterogeneous SoC and its Applications. Journal of Systems Architecture. Volume 61, issue 1. January 2015.

- Y. Benmoussa, J. Boukhobza, E. Senn, D. Benazzouz. On the Energy Efficiency of Parallel Multi-core vs Hardware Accelerated HD Video Decoding. ACM SIGBED Review, Volume 11 Issue 4 (Special issue on Ewili'14 Workshop). December 2014.

- Y. Benmoussa, J. Boukhobza, E. Senn, D. Benazzouz, Y. Hadjadj-Aoul. DyPS

: Dynamic Processor Switching for Energy-Aware Video Decoding on Multi-core

SoCs. ACM SIGBED Review, Volume 11 Issue 1 (Special issue on Ewili'13 Workshop). February 2014.

### International conferences

- Y. Benmoussa, E. Senn, J. Boukhobza, Michael Lanoe, D. Benazzouz. Open-PEOPLE, A Collaborative Platform for Remote & Accurate Measurement And Evaluation of Embedded Systems Power Consumption. MASCOTS: IEEE 22th International Symposium On Modeling, Analysis and Simulation of Computer and Telecommunication Systems. Paris, France. September 2014.

- Y. Benmoussa, J. Boukhobza, E. Senn, D. Benazzouz. DSP vs GPP: A Performance/Energy Characterization and Evaluation of Video Decoding. MASCOTS: IEEE 21st International Symposium On Modeling, Analysis and Simulation of Computer and Telecommunication Systems. San Fransisco, USA. August 2013.

• Y. Benmoussa, J. Boukhobza, E. Senn, D. Benazzouz. Energy Consumption Modeling of H.264/AVC Video Decoding for GPP and DSP. 16th Euromicro Conference on Digital System Design. Santander, Spain. . September 2013.

### National conferences

- Y. Benmoussa, J. Boukhobza, E. Senn, D. Benazzouz. Evaluation of the Performance/Energy Overhead in DSP Video Decoding and its Implications. Colloque du GDR SoC SiP. Lyon, France. June 2013.

- Y. Benmoussa, J. Boukhobza, L. Lagadec, D. Benazzouz, Y. Hadjadj-Aoul. Behavioral System Level Power Consumption Modeling of Mobile Video Streaming Applications. Colloque du GDR SoC SiP. Paris, France. June 2012.

# CHAPTER 1

## Introduction

### Contents

| 1.1 | Con   | text                                                         |  |

|-----|-------|--------------------------------------------------------------|--|

|     | 1.1.1 | Increase in mobile devices power consumption                 |  |

|     | 1.1.2 | New trends in mobile video applications usage : Implications |  |

|     |       | on power consumption                                         |  |

|     | 1.1.3 | Complex multimedia mobile devices 5                          |  |

| 1.2 | Pro   | blem statement: Energy consumption modeling of               |  |

|     | proc  | cessor-based video systems                                   |  |

|     | 1.2.1 | Low level modeling                                           |  |

|     | 1.2.2 | High level modeling                                          |  |

| 1.3 | The   | sis scope and approach                                       |  |

| 1.4 | The   | sis contributions                                            |  |

|     | 1.4.1 | Experimental methodology                                     |  |

|     | 1.4.2 | Energy characterization methodology                          |  |

|     | 1.4.3 | Energy modeling methodology                                  |  |

|     | 1.4.4 | Applications                                                 |  |

| 1.5 | Out   | line                                                         |  |

This thesis addresses the important issue of the energy consumption of video decoding on low power mobile System on Chip (SoC). It aims to enhance the understanding of the energy saving consideration and implications of video decoding on modern SoC equipping mobile devices.

In this chapter, we present the context which has motivated us to address this issue. Then, we define the scope we are targeting and the position of our work compared to other studies. Finally, we point out various important results obtained in this thesis.

### 1.1 Context

### 1.1.1 Increase in mobile devices power consumption

Mobile devices such as smart-phones and tablets are more and more used in everyday life. One of the most important issue faced by the hardware and software designers of these mobile devices is the drastic increase of their energy consumption.

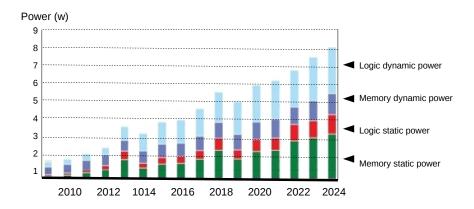

In fact, the increase in mobile applications usage combined with the explosion of the power consumption of the hardware make the energy consumption issue very critical. As illustrated in Fig. 1.1, the International Technology Road-map for Semiconductors (ITRS) forecasts that the power consumption of the SoC equipping mobile devices will increase with a factor of 2.5 during the next decade [1]. In a context where lithium battery technologies are not evolving fast enough to absorb the ever-growing energy requirements of such mobile architectures [7], the autonomy of the mobile devices may be drastically impacted.

Figure 1.1: SoC consumer portable power consumption trends [1]

Figure 1.2: Evolution of mobile video traffic

# 1.1.2 New trends in mobile video applications usage: Implications on power consumption

The following section presents the new trends in mobile video application usage and their relation with the energy consumption issue.

### 1.1.2.1 Increase in mobile video traffic

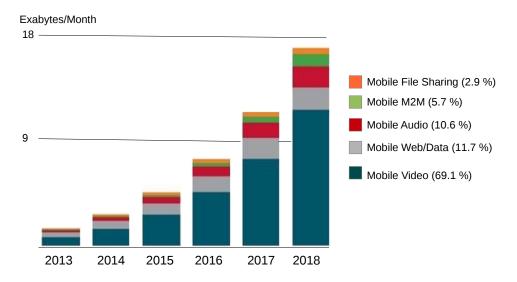

One of the most popular applications running on mobile devices is video playback. This is due to the growing use of video-sharing platforms (e.g. YouTube, Netflix, Dailymotion), social networks (e.g. Facebook, Twitter), mobile IPTV and video-conferencing. As illustrated in Fig. 1.2, it is expected that the video data will represent 70% of the overall Internet mobile traffic in the next few years [8]. Moreover, according to a recent study [9] achieved on 200 millions of mobile users, the average video watching time is 52 minutes per day.

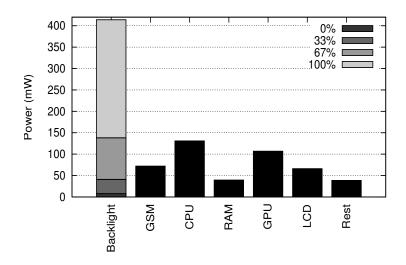

This new trend in using video content further accentuates the energy consumption issue. In fact, modern video codecs use more and more complex and aggressive compression algorithms to fit the ever growing demand on video. While they allow to achieve high compression ratios, they increase the demand on processing resources and thus on the energy consumption at the decoder side. For example, according to [10, 11], the processing resources are responsible of more than 60% of the power consumption during the video playback of a H.264/AVC video as shown in Fig. 1.3.

Figure 1.3: Energy consumption in a mobile device (Video playback)

### 1.1.2.2 Ubiquitous video applications

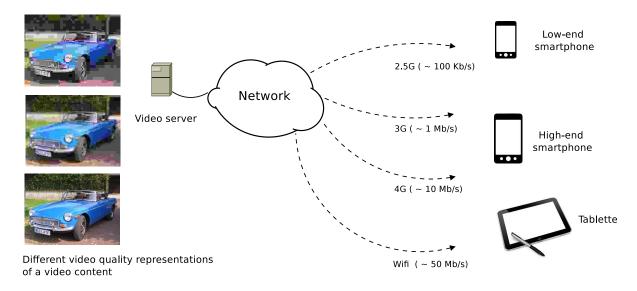

The increase in mobile traffic highlighted in the previous section is boosted by the ubiquitous video applications. These applications are executed in a heterogeneous environment. As illustrated in Fig. 1.4, the video content may be accessed from various mobile devices with different processing and displaying video capabilities. Moreover, the network technologies for transporting the video content may have different bandwidth capacities which range from tens of Kbits to tens of Mbits per second.

To cope with these different capabilities of the mobile devices, the most important video content providers (ex. Youtube and Netflix) support the dynamic quality adap-

Figure 1.4: Ubiquitous wireless video streaming to different mobile devices over diverse wireless access networks

Figure 1.5: Evolution of possessor frequencies

tation of video decoding [12], a technique allowing the video decoder to adjust the video quality at run time. The video quality is no longer a fixed parameter defined statically by the video content provider. It is up to the video decoder to select it depending on its capabilities.

In addition to network bandwidth and displaying capabilities of the mobile device, the energy budget constraint start to be considered as one of the criteria determining the video quality to retrieve from the network [13]. For example, the video decoder may consider the remaining energy budget (battery level) when selecting the video playback quality to increase its autonomy. Switching to a lower video quality playback may allow thus to extend the autonomy.

### 1.1.3 Complex multimedia mobile devices

The above discussed new trends of mobile users make the mobile device manufacturers competing for providing products designed toward multimedia applications and energy efficiency. In fact, multimedia capabilities available on modern mobile devices are close to those of personal computers while consuming much less energy. To make this possible, modern smart-phones and tablets integrates sophisticated embedded systems (ES). These ES includes multi-cores and heterogeneous processing resources running complex embedded operating systems (EOS).

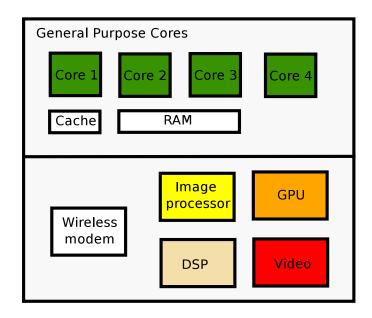

Figure 1.6: Heterogeneous cores in mobile SoC

### 1.1.3.1 Multi-core and heterogeneous processing

The processing capabilities of embedded processors equipping mobile devices have been growing considerably. The clock frequency of current mobile processors exceeds 1 GHz in almost all standard mobile devices. However, the performance of microprocessors tends to stall due to power and frequency wall limitation [14], it is no longer possible to continuously increase processor frequencies. This can be illustrated in Fig. 1.5 showing the processor frequency stall starting from the beginning of last decade [14]<sup>1</sup>.

To continue to scale performance without drastic power dissipation, manufacturers began to include more processor cores within a System on Chip (SoC). These cores may be general purpose processors (GPP) or specialized processing units. Figure 1.6 shows the components of a typical SoC equipping a modern mobile device. It includes multiple GPP cores in addition to Digital Signal Processor (DSP), a Graphical Processing Unit (GPU) and Application Specific Integrated Circuit (ASIC).

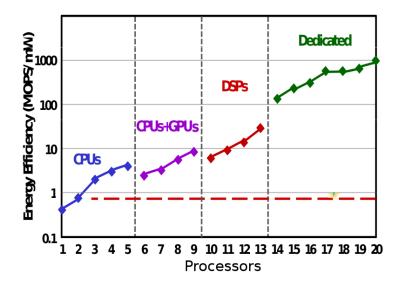

In general, the more a processor is specialized, the more it is energy efficient. Indeed, the use of parallelism in these processors in addition to optimized execution flows increase their performance without requiring higher voltages and frequencies [15]. This makes them an energy-efficient choice in energy constrained devices [16, 17]. This is illustrated in Fig. 1.7, showing the energy consumption (Million of OPeration per

<sup>&</sup>lt;sup>1</sup>The data are extracted from the CPUDB project (http://cpudb.stanford.edu) maintaining a database of hundreds of processor characteristics. The project is mainly focusing on CISC processors; however, the trends are the same for RISC processors equipping mobile devices

Figure 1.7: Energy efficiency vs processor type [2]

Second / mW) of different type of processors including CPU (GPP), GPU, DSP and dedicated circuits (ASIC).

Video decoding application can be implemented on GPP, DSP, GPU, or hardware accelerated video codecs. Each of these processing resources has advantages an draw-backs. For example, hardware video codecs are very energy-efficient [2], however they are not flexible and require a long time to market for new video standards chips design. On the other hand, GPP are not energy efficient while they are easy to program. GPU and DSP provide a balance between energy efficiency and flexibility.

Thus, within a single hardware platform, several heterogeneous processing configuration choices are available including GPP, DSP and ASIC. Each of these elements has different processing capabilities and energy consumption levels.

### 1.1.3.2 Sophisticated embedded operating systems

The increasing complexity of mobile device architectures imposes the use of sophisticated embedded operating systems (EOS) comparable in complexity and functionality to desktop or server ones. In fact, they provide an abstraction mechanism for sharing and managing hardware resources such as processors, storage, multimedia devices and implement almost all standard OS functionalities such as process scheduling, memory management and Input/Output (I/O) support. This central role of the OS in managing mobile devices makes it a very important component to consider when analyzing the energy consumption properties.

From the power consumption viewpoint, the OS is both a source of energy con-

sumption and an energy saving enabler. Indeed, like all the applications running on a mobile device, OS tasks use some part of processing resources and thus contribute in consuming the energy budget [18]. On the other hand, the OS is the component which has the best knowledge of hardware resources utilization which makes it ideal for implementing energy saving policies.

For example, in case of a video application, the OS may be highly involved in the video decoding process to manage the I/O with external video specialized processor (hardware video codec or DSP) or to schedule the decoding over multiple processor cores. These tasks are sources of additional energy consumption. On the other hand, the OS is able to save energy by *idling* the processors or lowering its frequency during low activity periods in the video decoding process.

# 1.2 Problem statement: Energy consumption modeling of processor-based video systems

In general, an energy model allows understanding and predicting the energy consumption in terms of well identified factors or parameters. Understanding how much a given parameter impacts the energy consumption can help in tuning it to reduce the consumed energy. This is especially true when the effects of interactions between the different parameters are understood. On the other hand, the prediction of the amount of consumed energy is extremely useful to dimension the energy budget and estimate the autonomy.

As highlighted previously, the processing resources are a major source of energy consumption in the context of video decoding applications. However, in case of complex processor-based system, well understanding the energy consumption properties should consider in addition to the processing resources, the executed operating system and applications. For example, the above sections show that the energy consumption considerations of video applications are present across different mobile device components.

Ideally, an energy model for the above described systems should consider all the relevant parameters and should estimate accordingly the consumed energy accurately. However, in practice, this is hard to achieve for complex systems and these objectives may be fulfilled partially. Actually, realistic energy consumption models for complex system can consider only a subset of parameters. On the other hand, they may induce

some errors in their predictions as compared to real energy consumption values. The questions which can raise is how to select the most relevant parameters and how to make the developed model as accurate as possible?

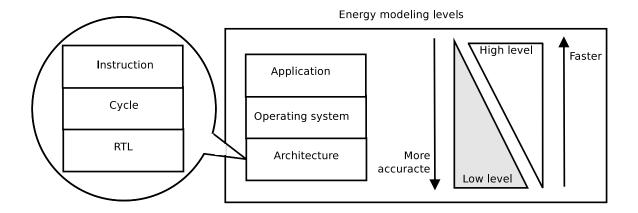

Answering these questions depend mainly on the considered abstraction level of the targeted system. As we will discuss hereafter, there exist two main approaches: 1) Low level modeling and 2) High level modeling.

### 1.2.1 Low level modeling

The energy models at the lower levels (ex. Register Transfer Level (RTL), cycle, Instruction) can provide very accurate estimation because they are able to represent low level details such as fabrication technology, pipelining, parallelism or memory hierarchy.

At these levels, the energy modeling is achieved at hardware design phase to allow hardware architects to explore the energy efficiency of processor architectures early by testing the impact of different hardware configurations. For this purpose, simulation tools are usually used to estimate the energy consumption of these complex systems including hardware and software.

These simulation tools are very flexible and allow representing a wide range of configuration and parameters at different levels of details. As illustrated in Fig. 1.8, the lower are the represented architecture details, the higher is the accuracy of energy modeling. In general, they are based on architecture simulators which feed low level and fine grained analytical power models with timing information to estimate the overall consumed energy [19].

To model application and/or operating system level parameters on these simulation frameworks, one should execute them on the simulators and estimate accordingly the consumed energy.

The drawback of energy simulators is that they are hard to build and require a very deep knowledge of the targeted microprocessors micro-architecture. Moreover, they are far from representing a complete modern low power SoC. For example, for estimating the energy consumption of video application, there is no energy simulation framework supporting a complete heterogeneous SoC including a GPP, DSP, GPU and hardware video codec.

Figure 1.8: Energy modeling methodologies and levels

### 1.2.2 High level modeling

Models at a higher levels do not rely on detailed microarchitectural knowledge of a particular processor. They may consider the targeted processors as a black-box which sacrifices some accuracy in order to avoid relying on detailed knowledge of the hardware implementation [20].

Since these models do not consider low level details, they may be built rapidly upon real platforms based on coarse grained experimental measurements. This lets the model developer focuses on high level parameters related to the executed applications and/or operating system.

For example, modeling the impact of scaling the processor frequency on the energy consumption of video decoding may be easily derived from energy measurement data achieved on a real platform. However, the use of energy simulator to estimate the impact of frequency scaling is not straightforward and may need a considerable integration effort [21].

The drawback of high level models is that they are decoupled from low level details which limits their generality and portability. In fact, an energy model built for a given hardware is difficult to be generalized to other platforms because there is not explicit mapping between the developed model and low level parameters.

### 1.3 Thesis scope and approach

In this thesis, we aim to model the energy consumption of video decoding executed on complex embedded systems including embedded operating systems and heterogeneous processing elements. Accordingly, we propose a high level modeling approach considering a set of parameters at application and operating system and architecture levels.

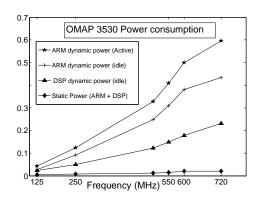

At architecture level, we study the impact on the energy consumption of different processing configuration available on heterogeneous SoC. We particularly focus on modeling the energy consumption of video decoding on two widely used microprocessor architectures on mobile SoC: GPP (ARM) and DSP. We explore also the energy efficiency of video decoding using parallel core and hardware accelerated codecs. At operating system level, we focus on studying the impact on the energy efficiency of the processor clock frequency and the inter-processor communication mechanism implemented by the OS for scheduling video decoding task on heterogeneous processors. At application level, we consider the impact of the video quality (bit-rate and resolution) and the scene complexity on the energy consumption of video decoding. The considered video codec is H.264/AVC, a widely used compression video standard.

To model the energy consumption at the considered levels, we chose to use a high level methodology based on extensive experimental power measurement achieved on real embedded platforms. This is motivated by our desire to build fast energy model which represents very accurately real life scenarios.

As discussed previously, high level models may be hard to be generalized to other architecture since they do not consider low level details. However, we believe that one can find the middle ground and achieve a balance between the advantages of high level approaches and simulation based ones. In our opinion, we could make the experimental based energy models more portable using a deep characterization methodology at all the considered levels to map the developed model with comprehensive relevant parameters.

### 1.4 Thesis contributions

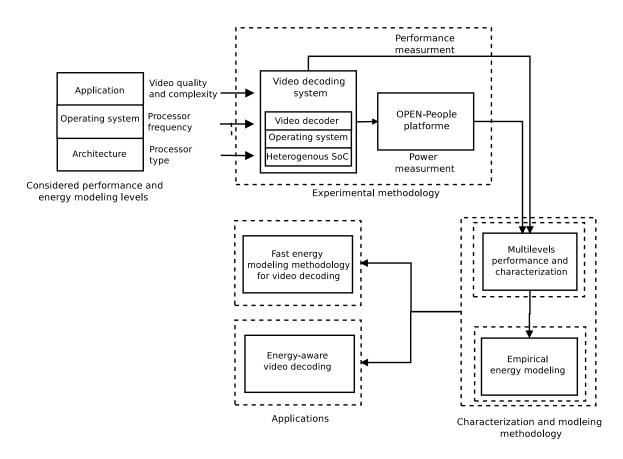

Figure 1.9 illustrates the main steps executed in this thesis. The different proposed contributions we will list below are represented by the dashed-rectangles.

### 1.4.1 Experimental methodology

An experimental methodology for energy consumption measurement of embedded systems was implemented. Open-PEOPLE (Open-Power and Energy Optimization PLatform and Estimator), a high accuracy power measurement platform, was used to mea-

Figure 1.9: Thesis contributions

sure the energy consumption of a set of embedded boards containing SoC similar to those used in mobile devices.

The advantage of the proposed experimental methodology is that it uses a common framework (measurement tools + embedded operating system + video decoder) for evaluating the performance and the energy consumption of video decoding. This allows accurate energy evaluation and objective comparison between the different targeted architectures including GPP, DSP, multi-cores and hardware codecs. This contribution is published in [22, 23].

### 1.4.2 Energy characterization methodology

A performance and energy characterization of video decoding was achieved based on an extensive experimental measurement methodology. In these experimentations, single core and multi-core ARM processors, DSP and hardware video codecs architectures were considered. On these different processor architectures, the processor frequency and video quality (Standard Definition (SD) and High Definition (HD) quality) parameters were considered.

An extensive characterization achieved on GPP and DSP processors for decoding SD video quality revealed that the performance-energy trade-off highly depends on the decoded video quality and the type of processor architecture. It was highlighted that the scheduling overhead over heterogeneous processor impacts the energy efficiency of video decoding when achieved on external specialized processor. Thus, depending on the video quality, it may be more energy efficient to decode a video on a GPP rather than a DSP. This contribution is published in [22, 5].

On the other hand, a performance and an energy characterization of HD video decoding on various processing configuration including of mono-core, multi-core GPP and hardware codec was achieved. It was shown that parallel HD video decoding on multi-core processors reduces considerably the gap between the energy consumption of hardware accelerated decoder and software-based ones. It is thus an interesting solution achieving a balance between the software flexibility and hardware codec energy efficiency. This contribution is published in [24].

### 1.4.3 Energy modeling methodology

Based on the results of the performance and the energy characterization of video decoding on GPP (ARM) and DSP, it was proposed:

- A performance analytical model for video decoding which considers both clock frequency and video quality parameters. This model describes also the impact of the off-chip memory access latency on performance variation of video decoding when varying the processor clock frequency. This contribution is published in [25]

- An energy consumption model for video decoding which estimates analytically the consumed energy as a function of the processor clock frequency, the video bit-rate and a set of comprehensive architecture, system and video related parameters. The developed model has a very good energy consumption prediction properties  $(R^2 = 97\%)$  for the two type of processors. This contribution is published in [25]

- A methodology to generalize and port the proposed energy model to other ARM processor architectures. This contribution is published in [26].

### 1.4.4 Applications

Based on the conclusions emerged from the characterization and the modeling methodologies, a set of applications are proposed:

- A set of guidelines for online performance and energy models building methodology where the model parameters calculation roles are identified within a video systems including the video encoder, the video decoder and the execution platform. We explain how to use such a model to build a proactive DVFS algorithm for energy aware adaptive video decoding in a context of adaptive video decoding. This contribution is published in [26].

- An energy-aware video decoding scheduling technique on heterogeneous SoC which was implemented on top of a video decoder. This scheduling technique consists in selecting the best energy-efficient processor in the context of video quality adaptive video decoding. This contribution is published in [27].

### 1.5 Outline

This thesis report is organized as follows:

Chapter 2, presents an overview of the most important state-of-the-art works studying the impact of the processor architectures on energy efficiency of video decoding. Then, the most common approaches and tools for high level energy modeling and estimation of video decoding are presented.

Chapter 3, is dedicated to explain the used methodology. It contains details about the characterization, the modeling steps in addition to a description of the experimental hardware/software setups used to achieve the experiments.

Chapter 4 contains the detailed description of the measured results of the performance and energy consumption characterization methodology of video decoding according to the execution of the above methodology. Conclusion on the energy efficiency of video decoding on GPP/DSP architecture can be found also in this section.

In chapter 5, the previous characterization results are used to build a performance and energy models for video decoding. This chapter includes also a model validation and generalization discussions.

Chapter 6 proposes some applications of the results emerged from the characterization and the modeling phases and discusses some open issues related to parallel and

hardware accelerated High Definition video decoding.

Chapter 7 draws the conclusions on this study and leaves space for discussion on some future works.

# CHAPTER 2

# Background and related works

## Contents

| 2.1 | Intr  | oduction                                             | 18 |

|-----|-------|------------------------------------------------------|----|

| 2.2 | Bac   | kground                                              | 18 |

|     | 2.2.1 | Concepts on video encoding and decoding              | 18 |

|     | 2.2.2 | Energy consumption in electronic circuits            | 23 |

|     | 2.2.3 | Discussion                                           | 25 |

| 2.3 | Prin  | ciples of energy saving in video decoding            | 25 |

|     | 2.3.1 | Frequency scaling: Performance vs energy consumption | 27 |

|     | 2.3.2 | Parallel multi-core video decoding                   | 29 |

|     | 2.3.3 | Specialized processing                               | 30 |

|     | 2.3.4 | Discussion                                           | 33 |

| 2.4 | Perf  | formances and energy consumption characterization    |    |

|     | of v  | ideo decoding                                        | 34 |

|     | 2.4.1 | Video decoding performances characterization         | 34 |

|     | 2.4.2 | Video decoding energy consumption characterization   | 36 |

|     | 2.4.3 | Discussion                                           | 38 |

| 2.5 | Perf  | formances and energy consumption modeling of video   |    |

|     | deco  | oding                                                | 40 |

|     | 2.5.1 | Video decoding performances modeling                 | 40 |

|     | 2.5.2 | Video decoding energy consumption modeling           | 45 |

| 2.5.3   | Discussion | <br>          | <br>47 |

|---------|------------|---------------|--------|

| 2.6 Con | clusions   | <br>. <b></b> | <br>49 |

#### 2.1 Introduction

This chapter is divided into three parts: first, a background on video decoding and basic concepts on energy consumption are presented. Then, some principles and techniques for saving energy of video decoding are introduced. Finally, the most important studies related to performance and energy characterization and modeling of video decoding are described.

#### 2.2 Background

#### 2.2.1 Concepts on video encoding and decoding

In this section, we describe the principles of video codecs and show how they allow reducing video data size at a cost of a drop in the video quality. Then, we discuss some metrics for evaluating the video quality as well as the quality of service (QoS) of the video playback. Then we introduce from a high level point of view some principles of saving the energy consumption of video decoding. We will show that it is usually a question of balancing the energy efficiency with the video QoS.

#### 2.2.1.1 Principles of MPEG standards

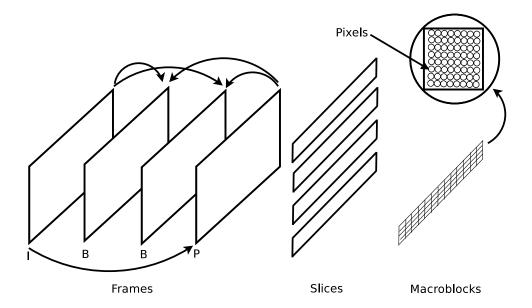

MPEG Video coding standards are a set of techniques for compressing video data to ease their transportation and storage. All of these standards (MPEG2, H.264/AVC, HEVC) make use of temporal (inter-frame) and spatial (intra-frame) redundancy to compress video data. Hereafter, we describe a general concepts shared by all MPEG video standards.

An MPEG video sequence is composed of a set of frames (see Fig. 2.1). Each frame may contain several slices and each slice contains several macroblocks (MB = 16 x 16 pixels). There exists three main types of slices: I, P, and B. In a I slice, the MB are predicted based on other intra-frame MB (intra-prediction). An I slice is thus independent from the slices in other frames. In a P-slice, the MB are predicted based on an intra-frame MB or an inter-frame MB in a past frame. Finally, B-slices use bidirectional inter-prediction where a MB may be predicted based on another MB in a previous or future frame.

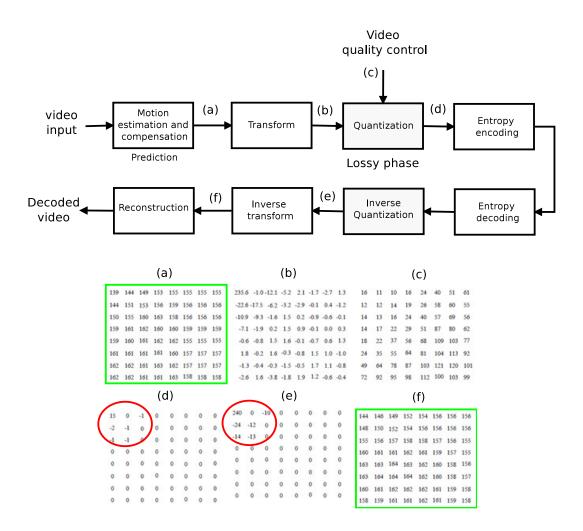

As illustrated in Fig. 2.2, while encoding a video, the first step is the prediction phase which aims to find a correlation between the MB to be encoded (current MB)

Figure 2.1: Structure of a video sequence

and a reference MB. As explained before, the reference MB may be in the same frame (intra-prediction) or in a past or future frame (inter-prediction). The operation of searching the reference MB (the "best matched" MB) is called motion estimation. The coordinates of the reference MB are stored in a motion vector (MV). The data obtained from subtracting the current MB from the reference MB is called a residual MB. The MV and the residual MB allows reconstructing the current MB. Matrix (a) in Fig. 2.2 is an example of (8x8) block extracted from of a residual MB.

In the second step, the residual MB are then transformed into another domain in which they are represented by transform coefficients. After the transformation, the data should be decorrelated and separated into compact group of data with minimal interdependence where most of the information should be concentrated into a small number of values. The transform operation can be achieved, for example, using Discrete Cosine Transform (DCT) or Wavelet transform.

The coefficients obtained from the transform operation (see matrix (b)) are quantized to remove insignificant values, leaving a small number of significant coefficients that provide a more compact representation of the residual data. The quantization reduces the precision of the transform coefficients according to a quantization parameter (qp). For example, the original coefficient values in matrix (b) are divided by a qp in the matrix (c) and rounded to the nearest integer. Typically, the result is a block in which most or all of the coefficients are zero (see matrix (d)), with a few non-zero coefficients. Setting qp to a high value means that more coefficients are set to zero,

Figure 2.2: Principles of video encoding/decoding

resulting in high compression at the expense of poor decoded image quality. Setting qp to a low value means that more non-zero coefficients remain after quantization, resulting in better image quality at the decoder but also in lower compression.

All the obtained data from these steps (transform coefficient, MV, qp) are then compressed using an entropy encoder. This operation is reversible and no data is lost. At this step, the compressed data are ready to be sent to the decoder.

At the video decoder, firstly, the entropy decoding is executed to extract the MV, the residual data and the qp. The inverse quantization is then executed to obtain the transform coefficients. Notice that, only the coefficients concentrating the most relevant information are rescaled. The information associated to the null coefficient are thus lost (see matrix (e)). Consequently, the inverse transform based on the rescaled coefficient is not identical to the original video date (compare matrix (a) and (f)).

#### 2.2.1.2 Video quality assessment metrics

The video encoding/decoding is a lossely process inducing a drop in the video visual quality. In general, the higher is the compression ratio, the lower is the obtained video quality. As explained in the previous section, the quality of the encoded video can be selected by tuning the quantization parameters. The higher is the value of qp, the lower is the video quality and vice versa.

In the case of a constant bit rate encoding mode<sup>1</sup> (CBR), the video bit-rate may provide indication on the video quality. For example, a video encoded at a 1024 Kb/s has a higher quality than one encoded at 512 Kb/s. In fact, the lower is the bit-rate constraint, the more aggressive is the quantization phase which results in a higher quality drop.

There exists other metrics which provide more accurate estimation of the video quality. For example, PSNR (Peak Signal to Noise Ratio) [28] is used to measure the quality of reconstruction of lossy compression codecs. The signal in this case is the original data, and the noise is the error introduced by compression. When comparing compression codecs, PSNR is an approximation to human perception of reconstruction quality.

#### 2.2.1.3 Video playback QoS assessment metrics

In addition to the drop in video quality related to data loss in video encoding algorithm, the visual perception of the video content may be impacted by factors related to the quality of service (QoS) of the video playback process [29].

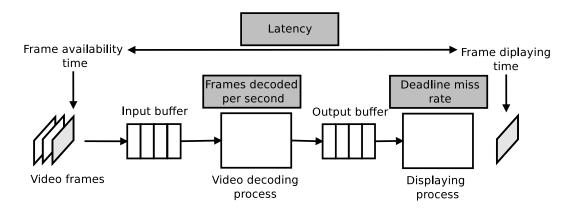

Figure 2.3 illustrates a typical video playback process. First, the video frames are retrieved from a source (network, file system, etc). Then, the video frames may be buffered in an input buffer to decouple the video decoding process from the fluctuation in the network bandwidth or the I/O system. The video decoder processes each frame and transmits it to the displaying process. The decoding time may vary considerably from a frame to another while the displaying process should display the decoded frames at a constant speed corresponding to the video sequence displaying rate  $R_{display}$ . To decouple the constant displaying speed from the fluctuation in the decoding time, an output buffer may be used between the decoder and the displaying device.

<sup>&</sup>lt;sup>1</sup>Constant bit rate encoding means that the rate at which the encoder output data should be produced is constant

Figure 2.3: Video decoding performance metrics

Hereafter, we present some metrics for evaluating the QoS of the above described video decoding process.

#### Deadline miss rate (DMR)

Video decoding is a soft real time application. During the decoding process, each frame should be displayed before a deadline, otherwise, a *deadline miss* occurs. The higher is the *deadline miss rate* (DMR), the lower is the perceived quality by the end-user.

The DMR is an important parameter to be considered to assess the quality of the video playback quality. It may occur due to insufficient processing resources for decoding the video frames or to insufficient network resources in case the video content is retrieved from the network.

#### Decoded frames per second (FPS)