# Design of an analog waveform generator dedicated to software radio transmission

Yoan Veyrac

### ▶ To cite this version:

Yoan Veyrac. Design of an analog waveform generator dedicated to software radio transmission. Electronics. Université de Bordeaux, 2015. English. NNT: . tel-01242809

### HAL Id: tel-01242809 https://hal.science/tel-01242809

Submitted on 26 Sep 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Design of an analog waveform generator dedicated to software radio transmission.

Yoan Veyrac

### ▶ To cite this version:

Yoan Veyrac. Design of an analog waveform generator dedicated to software radio transmission.. Electronics. Université de Bordeaux, 2015. English. <NNT: 2015BORD0444>. <tel-01307914>

HAL Id: tel-01307914

https://tel.archives-ouvertes.fr/tel-01307914

Submitted on 27 Apr 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE

présentée à

### L'Université de Bordeaux

Ecole doctorale des Sciences Physiques et de l'Ingénieur

### par Yoan VEYRAC

Pour obtenir le grade de

### DOCTEUR

SPÉCIALITÉ : ÉLECTRONIQUE

Contribution a l'etude et a la realisation d'un generateur de signaux radiofrequences analogiques pour la radio logicielle integrale

Soutenue le : 4 Décembre 2015

Devant la commission d'examen formée de :

**Dominique** Dallet Professeur Bordeaux INP Président Docteur - HDR Andreia Cathelin ST Microelectronics Rapporteur Patrick Reynaert Professeur KU Leuven Rapporteur Patrick Garrec Thales SA Ingénieur Examinateur Yann Deval Professeur Bordeaux INP Directeur de thèse Francois RIVET MCF Bordeaux INP Co-Directeur de thèse Richard Montigny Thales SA Membre invité Ingénieur Hervé Lapuyade MCF Université de Bordeaux Membre invité

### Remerciements

Les travaux de thèse rapportés dans ce manuscrit sont le fruit de recherches menées au laboratoire IMS, en collaboration avec l'Université de Bordeaux et Thales.

Je tiens en premier lieu à remercier les membres du jury pour l'intérêt qu'ils ont porté à ces travaux et les échanges scientifiques pertinents

Je souhaite également remercier les différentes personnes qui ont relu le manuscrit et contribué à cette version finale.

Je remercie chaleureusement Yann, pour ces trois merveilleuses années, très riches sur le plan scientifique, culinaire et culturel. J'en garderai des souvenirs impérissables.

Je tiens à adresser mes sincères remerciements à François, pour notre étroite collaboration qui a rythmé le déroulement de la thèse dans un esprit de plaisiriosité Monkienne de tous les instants.

Merci à tous mes collègues du laboratoire IMS et de l'Enseirb-Matmeca d'avoir contribué à l'excellente ambiance de travail. Je remercie en particulier les membres de l'équipe CAS.

Un grand merci à tous mes amis, dont le fameux groupe CSI '12 (promotion cheval), pour les très bons moments passés ces dernières années, et les nombreux autres à venir.

Je salue et je remercie mes parents pour l'ensemble de leur oeuvre, mon frère et ma bellesoeur qui m'ont promu au rang de Tonton Mouton, et ma "grande soeur" adorée. J'ai passé un merveilleux premier quart de siècle dans une famille formidable, et le prochain s'annonce sous les plus heureux auspices.

Enfin, j'embrasse Pauline, ma petite puce éponyme, qui a enchanté ma dernière année de thèse et avec qui je partagerai un avenir radieux.

## Contents

| In       | $\mathbf{trod}$ | uction |                                                     | 21 |

|----------|-----------------|--------|-----------------------------------------------------|----|

| 1        | Tra             | nsmitt | ers for ubiquitous network                          | 23 |

|          | 1.1             | Wirele | ess communication paradigm                          | 24 |

|          |                 | 1.1.1  | Radio frequency transceivers architecture           | 25 |

|          |                 | 1.1.2  | Wireless communication media capacity               | 27 |

|          |                 | 1.1.3  | Mobile terminal transceivers compatibility          | 28 |

|          | 1.2             | Softwa | are radio transmitters                              | 29 |

|          |                 | 1.2.1  | Software radio background                           | 29 |

|          |                 | 1.2.2  | Directions of research for flexible transmitters    | 32 |

|          | 1.3             | Data   | conversion schemes                                  | 39 |

|          |                 | 1.3.1  | Pulse code modulation                               | 41 |

|          |                 | 1.3.2  | Pulse density modulation                            | 44 |

|          |                 | 1.3.3  | Conversion efficiency                               | 47 |

|          | 1.4             | Concl  | usion                                               | 49 |

| <b>2</b> | The             | Riem   | ann Pump                                            | 51 |

|          | 2.1             | Differ | ential digital to analog conversion                 | 52 |

|          |                 | 2.1.1  | Differential Pulse Code Modulation (DPCM): Riemann  | 52 |

|          |                 | 2.1.2  | Noise Shaping Riemann conversion (NSR)              | 56 |

|          |                 | 2.1.3  | RF conversion schemes summary                       | 59 |

|          | 2.2             | The R  | tiemann Pump: an integrating DAC                    | 61 |

|          |                 | 2.2.1  | Implementation of the digital to analog integration | 61 |

|          |                 | 2.2.2  | Analog reconstruction features                      | 63 |

|          | 2.3             | Simul  | ation of the Riemann Pump architecture              | 66 |

|          |                 | 2.3.1  | System simulation flow                              | 66 |

|          |                 | 2.3.2  | SNR performances: simulation results versus theory  | 70 |

|          |                 | 2.3.3  | Concurrent transmission                             | 77 |

|                  | 2.4    | Conclu  | asion                              | 82  |

|------------------|--------|---------|------------------------------------|-----|

| 3                | Circ   | cuits d | esign and Implementation           | 83  |

|                  | 3.1    | Integra | ation in GaN technology            | 84  |

|                  |        | 3.1.1   | GaN technology                     | 84  |

|                  |        | 3.1.2   | Riemann Pump in GaN technology     | 86  |

|                  |        | 3.1.3   | Transistor level design            | 88  |

|                  |        | 3.1.4   | Simulation results                 | 94  |

|                  | 3.2    | Integra | ation in CMOS technology           | 97  |

|                  |        | 3.2.1   | Architecture in CMOS technology    | 97  |

|                  |        | 3.2.2   | Core pump circuit design           | 99  |

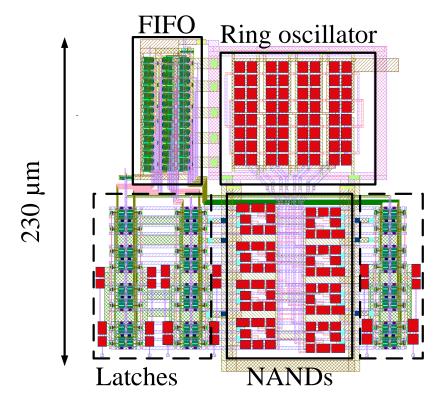

|                  |        | 3.2.3   | Riemann Pump layout                | 109 |

|                  |        | 3.2.4   | Post-Layout Simulations (PLS)      | 110 |

|                  |        | 3.2.5   | Chip design - PAULINA              | 117 |

|                  | 3.3    | Conclu  | asion                              | 122 |

| 4                | Mea    | asurem  | nent results and prospects         | 123 |

|                  | 4.1    | Measu   | rement results                     | 124 |

|                  |        | 4.1.1   | Prototypes Realization             | 124 |

|                  |        | 4.1.2   | Characterization of the prototypes | 126 |

|                  | 4.2    | Prospe  | ects                               | 139 |

|                  |        | 4.2.1   | Complete transmitter architecture  | 139 |

|                  |        | 4.2.2   | Riemann receiver                   | 142 |

|                  | 4.3    | Conclu  | usion                              | 142 |

| $\mathbf{C}_{0}$ | onclu  | ısion   |                                    | 145 |

| Pι               | ublic  | ations  |                                    | 147 |

| Bi               | ibliog | graphy  |                                    | 149 |

| 5                | Anr    | nexes   |                                    | 157 |

|                  | 5.1    | Distrib | oution of the slopes set           | 158 |

|                  | 5.2    | Digita  | l circuits details                 | 163 |

## List of Figures

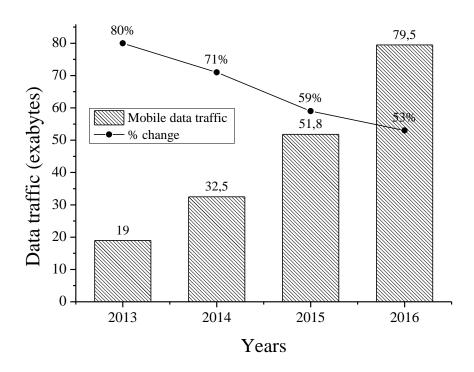

| 1.1  | Global mobile data traffic (source: Gartner 2015)                                               | 25 |

|------|-------------------------------------------------------------------------------------------------|----|

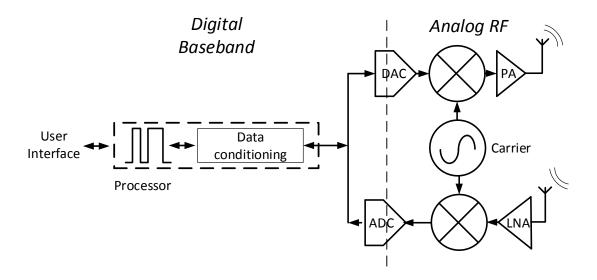

| 1.2  | Classical direct conversion transceiver architecture                                            | 26 |

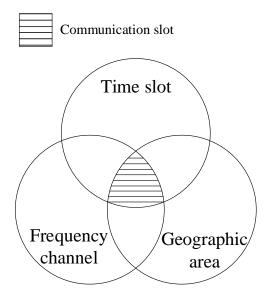

| 1.3  | Venn diagram of the 3-dimensions wireless communication space                                   | 27 |

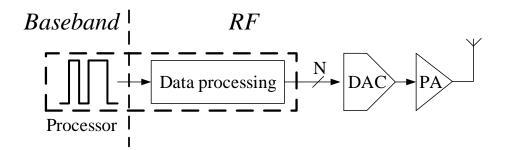

| 1.4  | Software radio transmitter architecture                                                         | 29 |

| 1.5  | Technology tracks of 5G era                                                                     | 31 |

| 1.6  | From software defined to software radio transmitters                                            | 32 |

| 1.7  | Wideband DAC Sot<br>A – Conversion efficiency Vs Nyquist bandwidth $\ \ldots \ \ldots \ \ldots$ | 38 |

| 1.8  | Quantization – the DA interface                                                                 | 40 |

| 1.9  | Spectrum of an ideally sampled signal                                                           | 40 |

| 1.10 | Architecture of overall digital to analog conversion                                            | 41 |

| 1.11 | Nyquist PCM DAC architecture                                                                    | 41 |

| 1.12 | Spectrum of a Nyquist rate quantized signal                                                     | 42 |

| 1.13 | Oversampled PCM DAC architecture                                                                | 43 |

| 1.14 | Spectrum of an oversampled quantized signal                                                     | 43 |

| 1.15 | First order sigma delta block diagram                                                           | 44 |

| 1.16 | First order sigma delta z–transform diagram                                                     | 45 |

| 1.17 | Spectrum of a SDM quantized signal                                                              | 46 |

| 1.18 | Efficiency of global digital to analog conversion                                               | 47 |

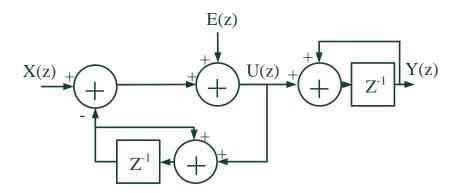

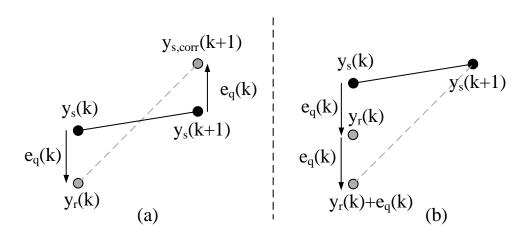

| 2.1  | Open loop DPCM diagram                                                                          | 53 |

| 2.2  | Closed loop DPCM diagram                                                                        | 53 |

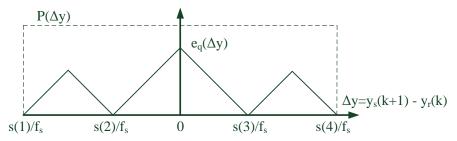

| 2.3  | Quantization error for DPCM                                                                     | 54 |

| 2.4  | DPCM z-transform block diagram                                                                  | 55 |

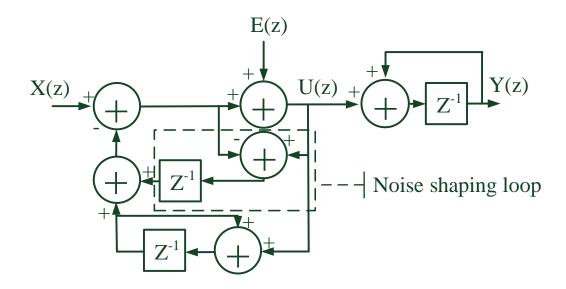

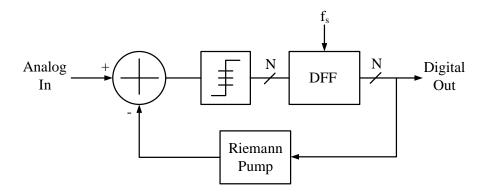

| 2.5  | Noise Shaping Riemann conversion process                                                        | 57 |

| 2.6  | Noise Shaping Riemann Z-transform block diagram                                                 | 57 |

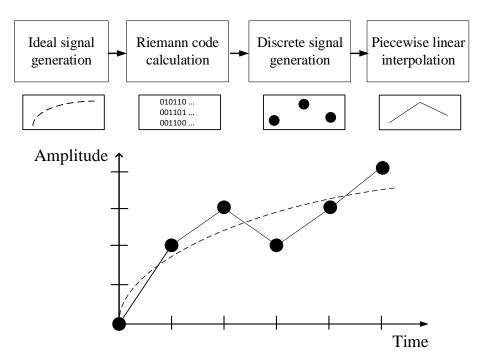

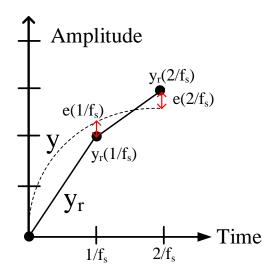

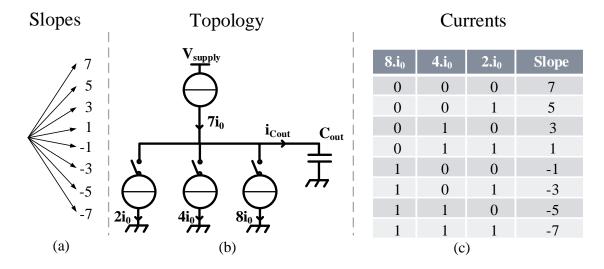

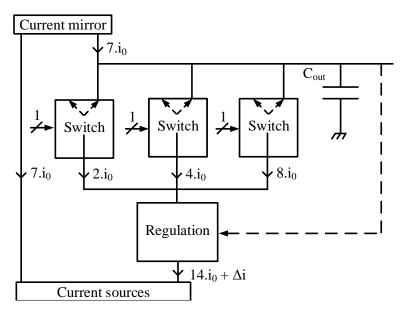

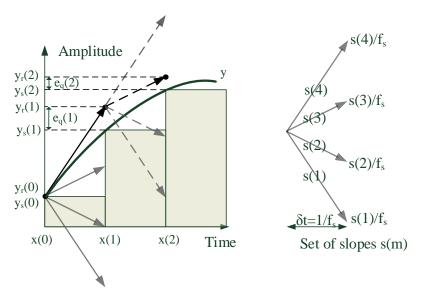

| 2.7  | Signal integration principle                                                                    | 62 |

| 2.8  | Riemann Pump Architecture                                                                       | 62 |

| 2.0  | Convertion of a sine wave with 8 slopes                                                         | 62 |

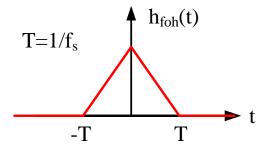

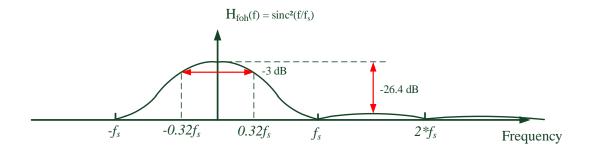

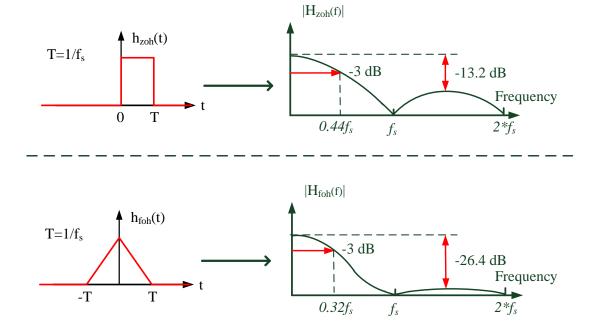

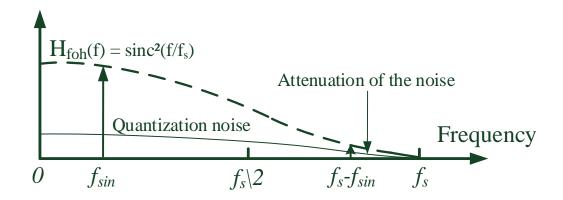

| 2.10 | Impact of the DA reconstruction on the spectrum                                          | 63 |

|------|------------------------------------------------------------------------------------------|----|

| 2.11 | Impulse response of the equivalent first-order hold reconstruction                       | 64 |

| 2.12 | Frequency response of the first-order hold                                               | 64 |

| 2.13 | ${\sf zero}^{th}$ and first-order holds impulse and freuency responses                   | 65 |

| 2.14 | Matlab signal generation                                                                 | 67 |

| 2.15 | Temporal calculation of the SNR                                                          | 68 |

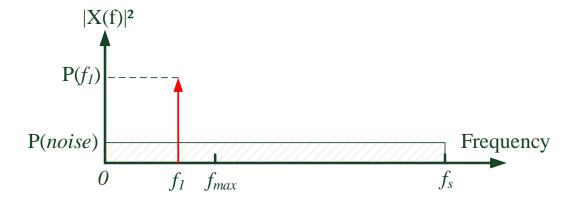

| 2.16 | Spectral representation of a CW signal                                                   | 69 |

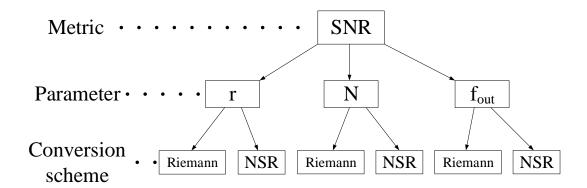

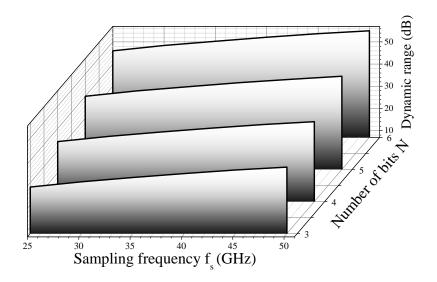

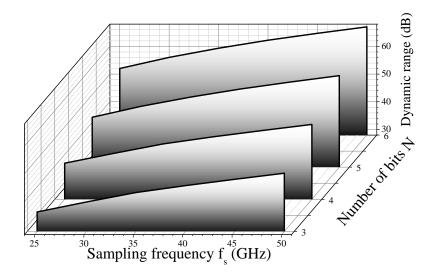

| 2.17 | SNR Simulation chart                                                                     | 71 |

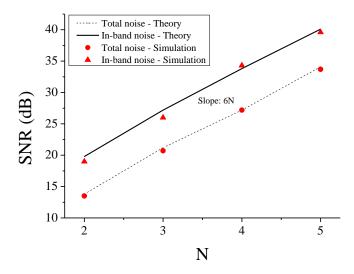

| 2.18 | SNR of the Riemann conversion versus N / r=2                                             | 71 |

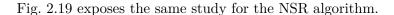

| 2.19 | SNR of the NSR conversion versus N / r=2                                                 | 72 |

| 2.20 | SNR of the Riemann conversion versus r / N=3                                             | 73 |

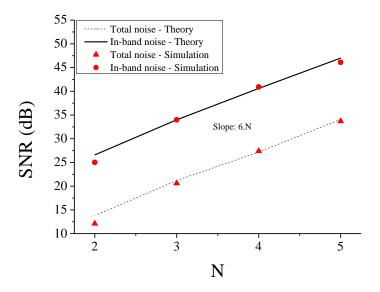

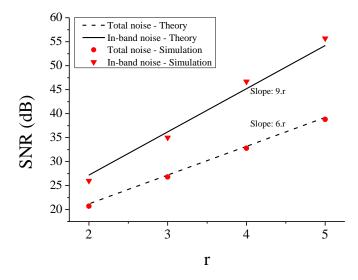

| 2.21 | SNR of the NSR conversion versus r / N=3                                                 | 73 |

| 2.22 | SNR of the Riemann conversion versus frequency $(r,N)=(2,3)$                             | 74 |

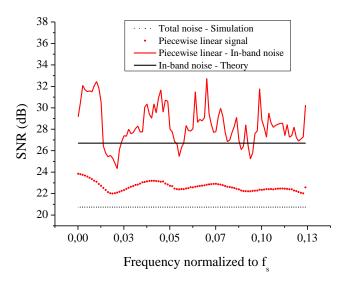

| 2.23 | Piecewise linear CW spectrum – Riemann conversion                                        | 75 |

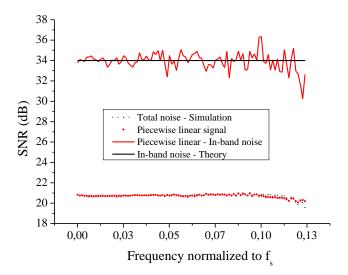

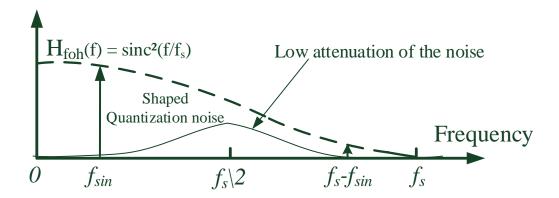

| 2.24 | SNR of the NSR conversion versus frequency $(r,N)=(2,3)$                                 | 76 |

| 2.25 | Piecewise linear CW spectrum – NSR conversion                                            | 76 |

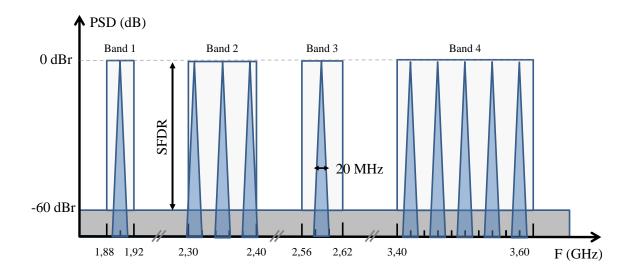

| 2.26 | First phase of the sub-6 GHz 5G spectral mask                                            | 77 |

| 2.27 | Spectrum of 10 aggregated channels – Riemann conversion $(f_s, N)=(50 \text{ GHz}, 6)$ . | 79 |

| 2.28 | SFDR for 10 aggregated channels – Riemann conversion                                     | 79 |

| 2.29 | Spectrum of 10 aggregated channels – NSR conversion $(f_s, N)=(50 \text{ GHz}, 6)$       | 80 |

| 2.30 | SFDR for 10 aggregated channels – NSR conversion                                         | 80 |

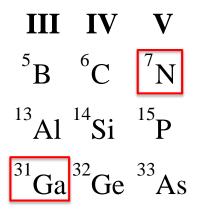

| 3.1  | GaN atomic composition                                                                   | 84 |

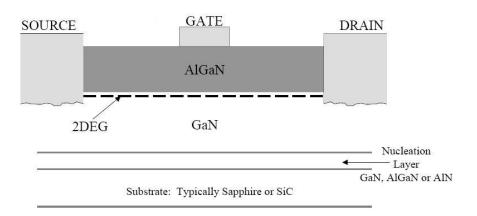

| 3.2  | GaN HEMT sectional view                                                                  | 85 |

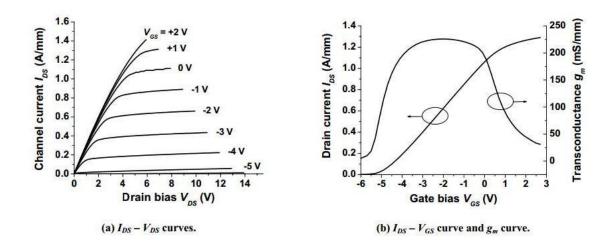

| 3.3  | Electrical characteristics of N-type HEMTs                                               | 86 |

| 3.4  | Slope set generation                                                                     | 87 |

| 3.5  | Riemann Pump topology in GaN                                                             | 88 |

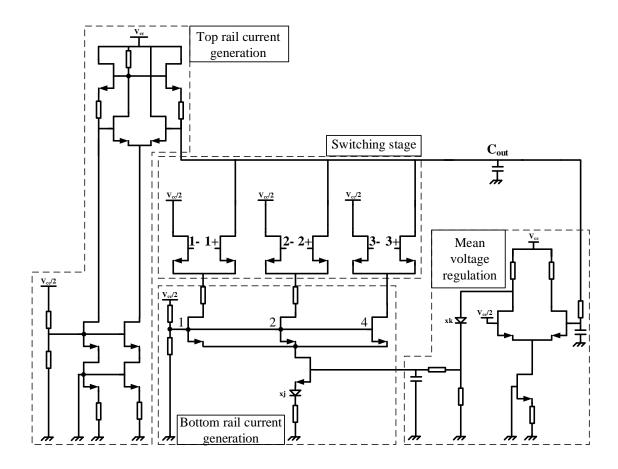

| 3.6  | GaN circuit schematic view                                                               | 89 |

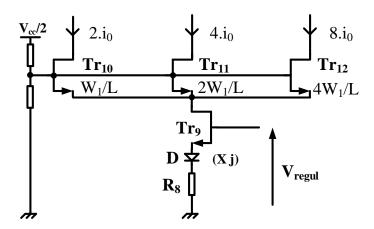

| 3.7  | Top rail current generation                                                              | 90 |

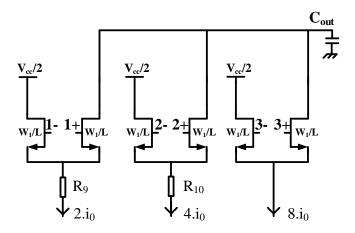

| 3.8  | Bottom rail current generation                                                           | 90 |

| 3.9  | Switching stage                                                                          | 91 |

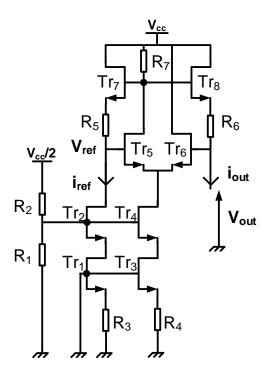

| 3.10 | Regulation loop                                                                          | 92 |

| 3.11 | Input buffer                                                                             | 92 |

| 3.12 | Layout view of the GaN circuit                                                           | 93 |

| 3.13 | Power spectral density of the generated chirp                                            | 95 |

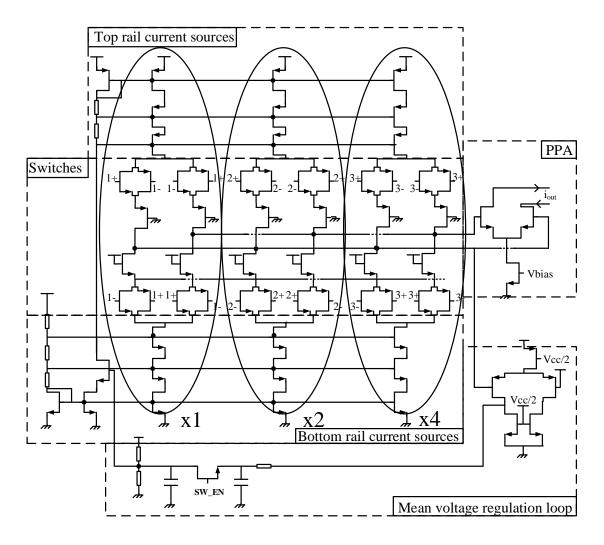

| 3.14 | Topology of the Riemann Pump in CMOS technology                                          | 98 |

|      |                                                                                          |    |

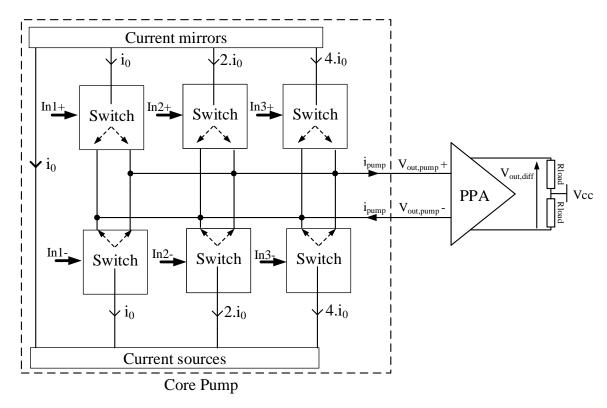

| 3.15 | Schematic view of the core Riemann Pump in CMOS technology 99                                                                                                     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.16 | PPA schematic                                                                                                                                                     |

| 3.17 | Normalized gate capacitance of the PPA differential pair                                                                                                          |

| 3.18 | Static voltage characteristic of the PPA                                                                                                                          |

| 3.19 | Bottom and top rail current sources                                                                                                                               |

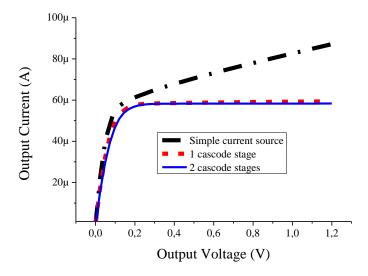

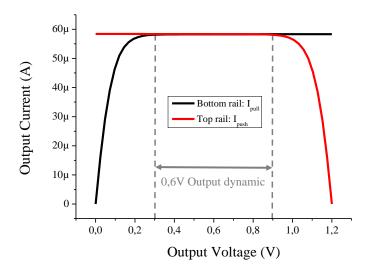

| 3.20 | Current sources characteristics                                                                                                                                   |

| 3.21 | Top and bottom rails current source characteristics                                                                                                               |

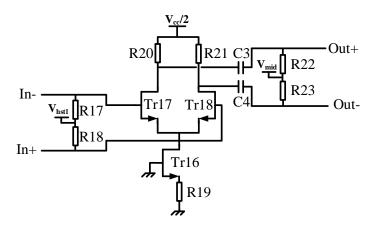

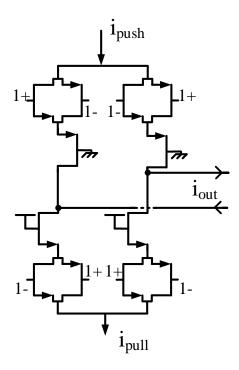

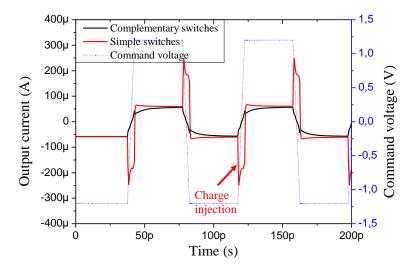

| 3.22 | Switching stage                                                                                                                                                   |

| 3.23 | Transient behavior of the switches                                                                                                                                |

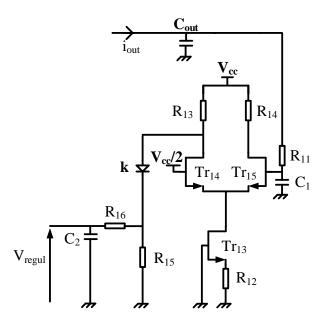

| 3.24 | Common mode regulation loop                                                                                                                                       |

| 3.25 | Block diagram of the regulation loop                                                                                                                              |

| 3.26 | Loop transconductance gain                                                                                                                                        |

| 3.27 | Bode diagram of the open loop transfer function                                                                                                                   |

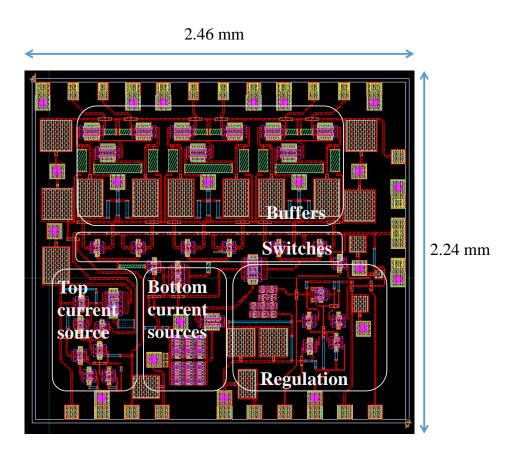

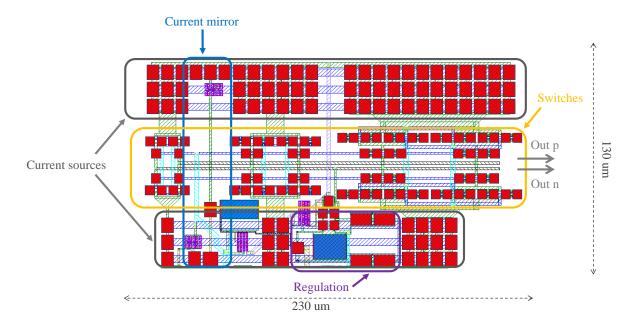

| 3.28 | Layout of the core pump                                                                                                                                           |

| 3.29 | Layout of the PPA                                                                                                                                                 |

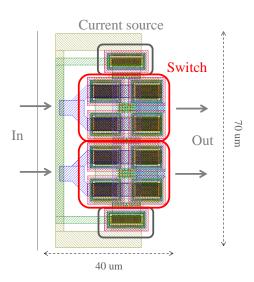

| 3.30 | PLS flow                                                                                                                                                          |

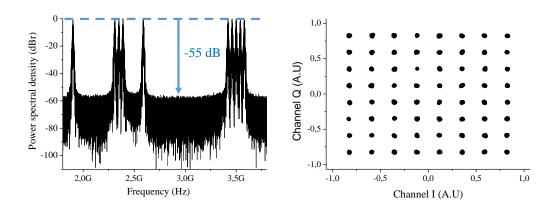

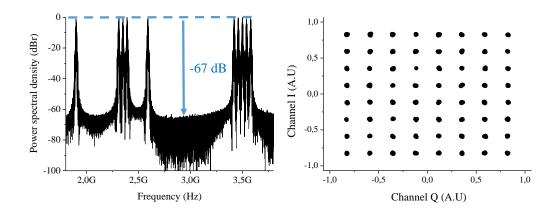

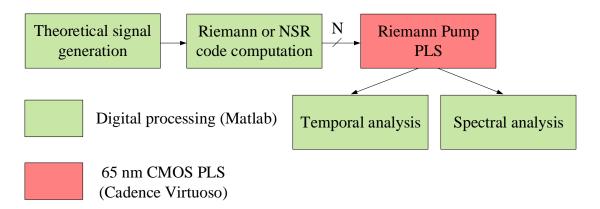

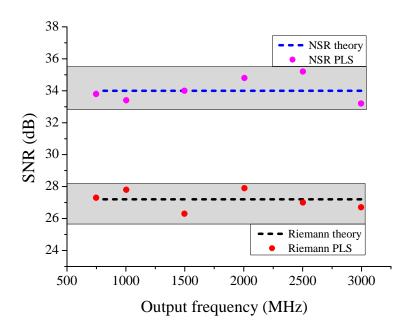

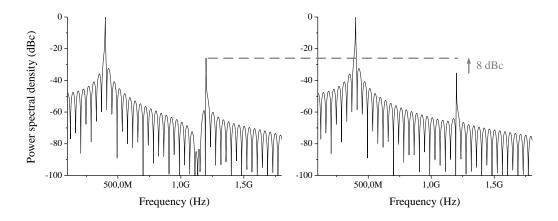

| 3.31 | 3 GHz generated CW - PLS - (a) Riemann and (b) NSR                                                                                                                |

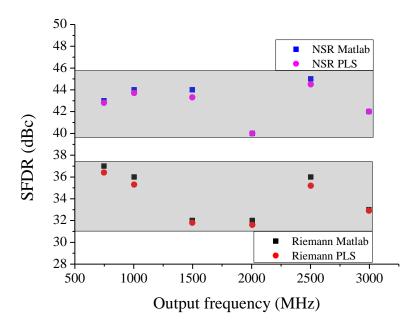

| 3.32 | SFDR - PLS Vs theory - Riemann and NSR                                                                                                                            |

| 3.33 | SNR - PLS Vs theory - (a) Riemann and (b) NSR $\dots \dots \dots$ |

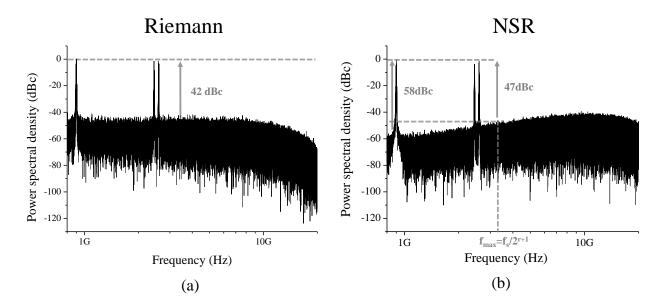

| 3.34 | Spectra of the concurrently transmitted signals - (a) Riemann and (b) NSR $$ 114                                                                                  |

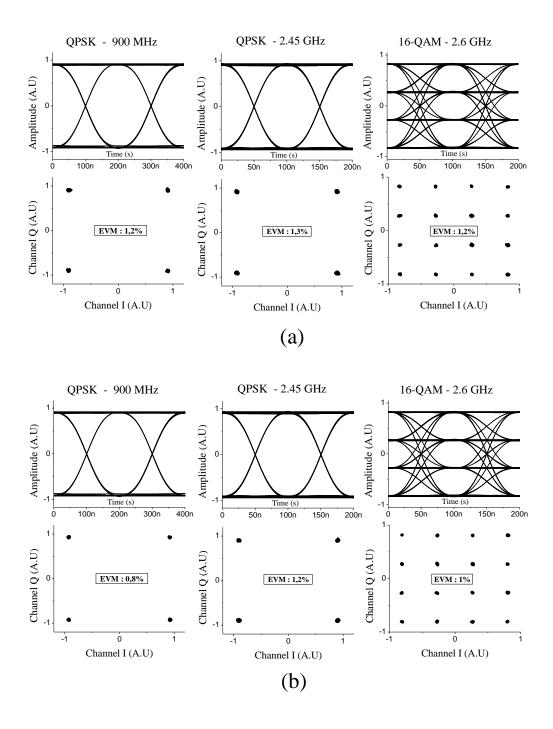

| 3.35 | Eye patterns and constellations for the concurrent modulated signals - (a) Rie-                                                                                   |

|      | mann and (b) NSR                                                                                                                                                  |

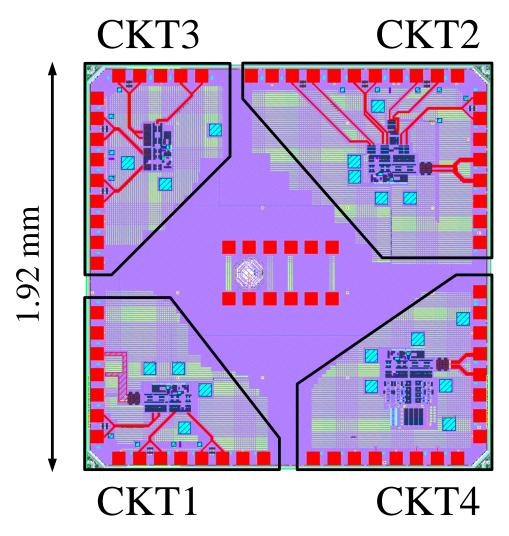

| 3.36 | PAULINA layout view                                                                                                                                               |

| 3.37 | CKT1 Architecture                                                                                                                                                 |

| 3.38 | CKT2 architecture                                                                                                                                                 |

| 3.39 | CKT3 Architecture                                                                                                                                                 |

| 3.40 | CKT4 Architecture                                                                                                                                                 |

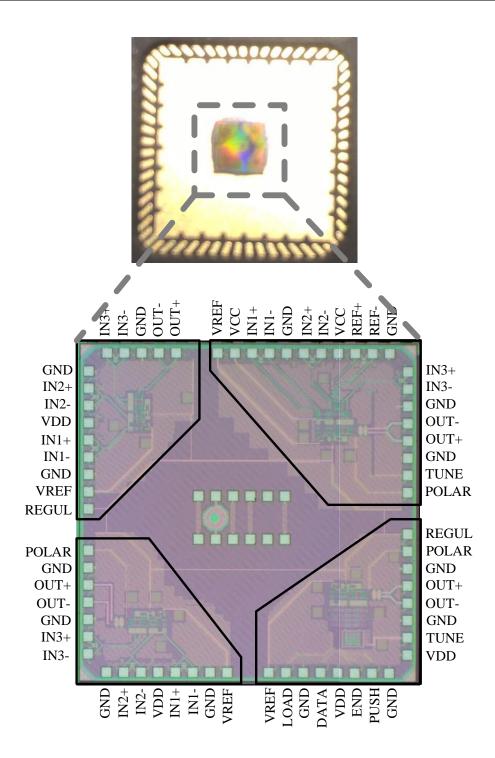

| 4.1  | Micro photogaph of PAULINA                                                                                                                                        |

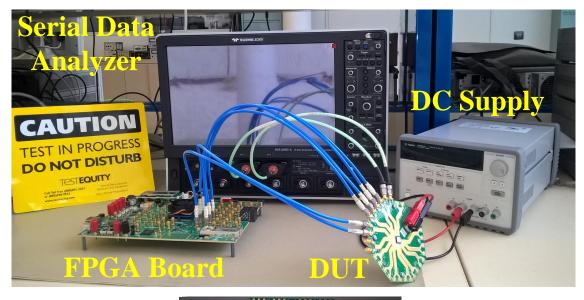

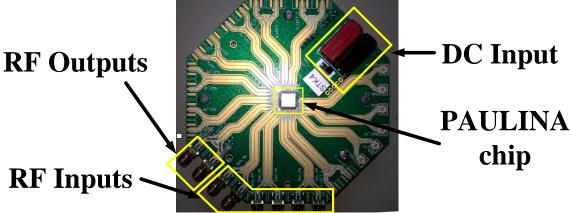

| 4.2  | Photograph of the test board and the experimental setup                                                                                                           |

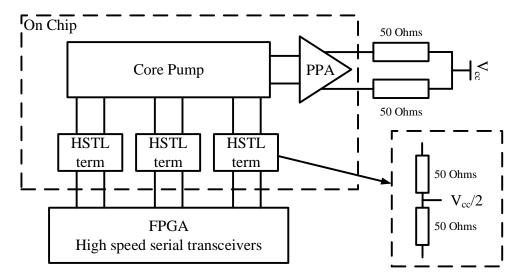

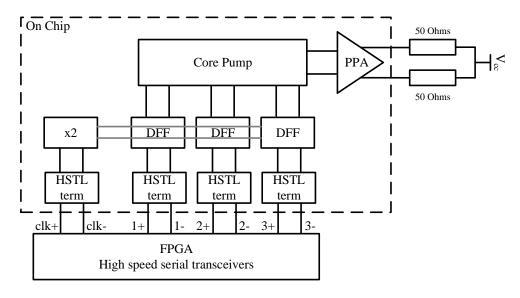

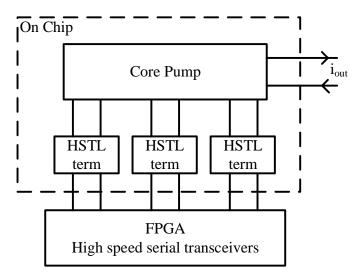

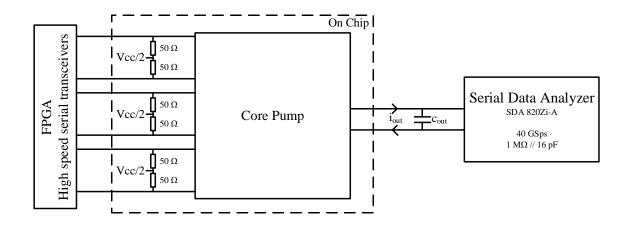

| 4.3  | Test bench of the standalone pump                                                                                                                                 |

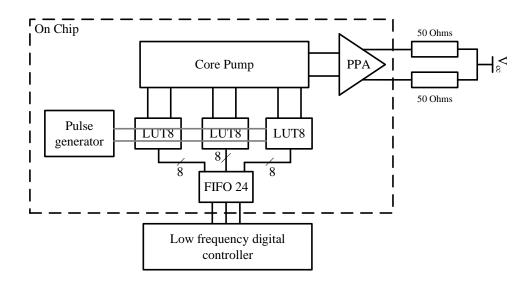

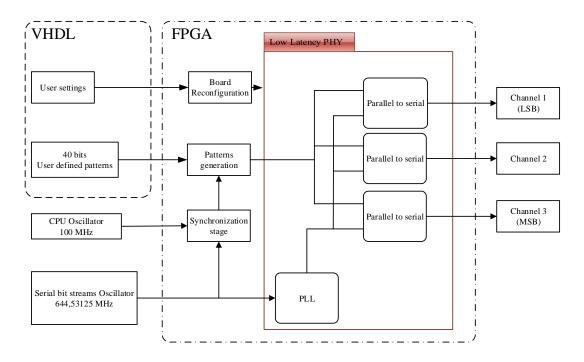

| 4.4  | FPGA bit stream generator architecture                                                                                                                            |

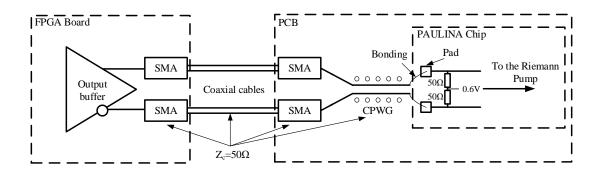

| 4.5  | FPGA-to-chip physical channel                                                                                                                                     |

| 4.6  | DC measurement test bench                                                                                                                                         |

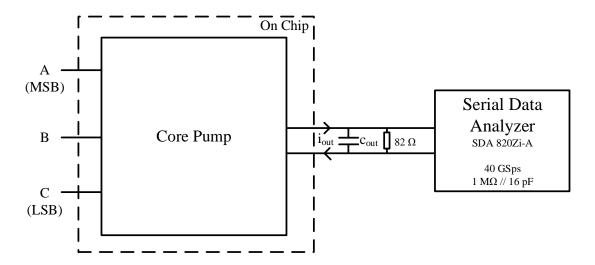

| 4.7  | DC measurement input configuration                                                                                                                                |

| 4.8  | Standalone pump transfer function                                                                                                                                 |

|      |                                                                                                                                                                   |

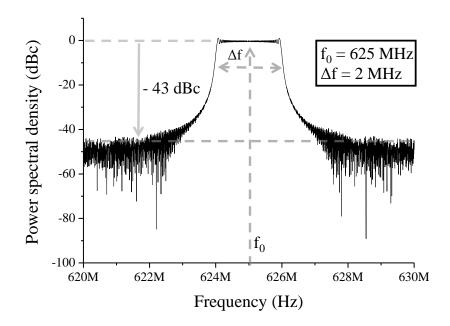

| 4.9 Dual carrier transient waveform                                                                                                                                                |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 4.10 Dual carrier spectrum                                                                                                                                                         |  |

| 4.11 Variation of the oversampling factor r - theoretical spectra                                                                                                                  |  |

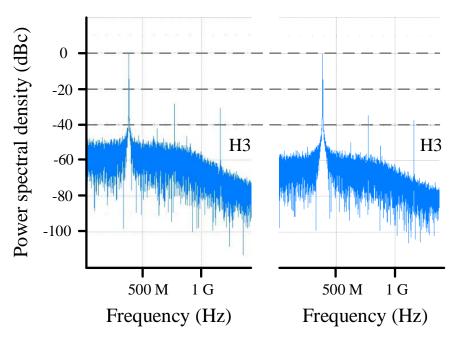

| 4.12 Variation of the oversampling factor r - measured spectra $\dots \dots \dots$ |  |

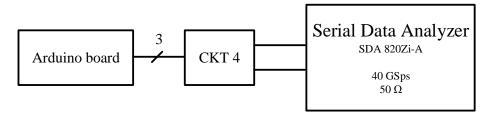

| 4.13 Test bench of the autonomous pump                                                                                                                                             |  |

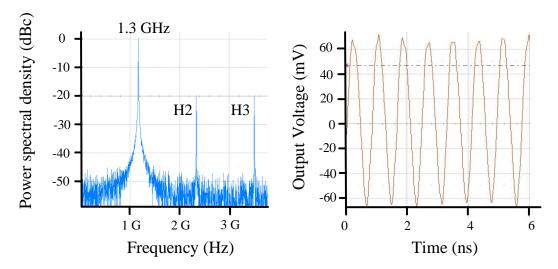

| 4.14 Triangle signal spectrum and waveform                                                                                                                                         |  |

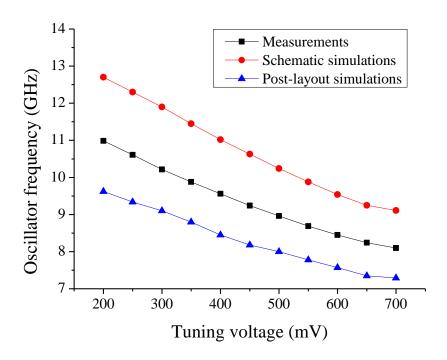

| 4.15 Oscillator frequency versus tuning frequency                                                                                                                                  |  |

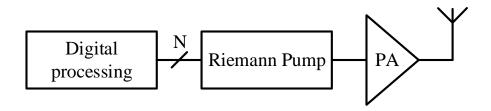

| 4.16 Complete transmitter based on the Riemann Pump                                                                                                                                |  |

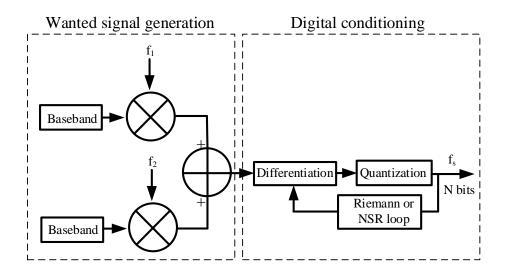

| 4.17 Digital processing and conditioning stage (concurrent generation of 2 channels) . $139$                                                                                       |  |

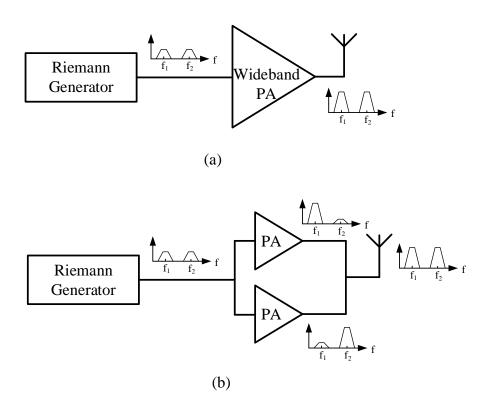

| 4.18 Power amplification stage topology (a) single wideband PA (b) multiple-path PA 141                                                                                            |  |

| 4.19 Differentiating receiver based on the Riemann Pump                                                                                                                            |  |

| T.1. D.                                                                                                                                                                            |  |

| 5.1 Riemann reconstruction process                                                                                                                                                 |  |

| 5.2 Quantization error versus the relative position of the next targeted point $(\Delta y)$ . 159                                                                                  |  |

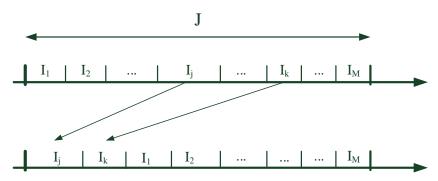

| 5.3 Intervals re-arrangement                                                                                                                                                       |  |

| 5.4 Frequency doubler block diagram                                                                                                                                                |  |

| 5.5 Dynamic flip flops schematic                                                                                                                                                   |  |

| 5.6 Re-synchronization process                                                                                                                                                     |  |

| 5.7 Layout of the re-synchronization block                                                                                                                                         |  |

| 5.8 Block diagram of the pattern generator                                                                                                                                         |  |

| 5.9 Block diagram of the pulse generator                                                                                                                                           |  |

| 5.10 Generation of the pulses - PLS                                                                                                                                                |  |

| 5.11 Loading of the pattern data                                                                                                                                                   |  |

| 5.12 Layout of the pattern generator                                                                                                                                               |  |

|                                                                                                                                                                                    |  |

## List of Tables

| 1.1 | Performances of reconfigurable transmitters                                      |

|-----|----------------------------------------------------------------------------------|

| 1.2 | Performances of direct digital-RF transmitters                                   |

| 1.3 | Performances of all-digital transmitters                                         |

| 1.4 | Performances of RF-DACs                                                          |

| 1.5 | Key features of the classical conversion schemes                                 |

| 2.1 | Modulation features involved in the presented conversion schemes and the related |

|     | impact of the OSR on the SNR                                                     |

| 2.2 | Features of the zero <sup>th</sup> and the first-order holds                     |

| 2.3 | Conversion architectures theoretical features summary                            |

| 2.4 | SFDR versus the number of aggregated carriers - $(f_s, N)$ =(50 GHz,6) 81        |

| 3.1 | GaN principal features for RF electronics                                        |

| 3.2 | Deviation of the output mean voltage with and without regulation loop 94         |

| 3.3 | Output impedance of various current source structures                            |

| 3.4 | Features of the concurrently generated modulations                               |

| 3.5 | CKT1 operating currents                                                          |

| 3.6 | CKT2 operating currents                                                          |

| 3.7 | CKT3 operating currents                                                          |

| 3.8 | CKT4 operating currents                                                          |

| 4.1 | Standalone pump operating current                                                |

| 4.2 | Standalone pump DC linearity                                                     |

| 4.3 | Dual carrier spectral components - measurements versus theory                    |

| 4.4 | Third harmonic level - measurements versus theory                                |

| 4.5 | Autonomous pump operating current                                                |

| 4.6 | Triangle signal harmonic level                                                   |

| 4.7 | State-of-the-art of RF-DACs                                                      |

### List of Abbreviations

**AD** Analog-to-Digital

AC Alternating current

ADC Analog-to-Digital Converter

**AlGaN** Aluminium Gallium Nitride

ASIC Application-Specific Integrated Circuit

**BW** Bandwidth

CA Carrier Aggregation

CMOS Complementary Metal Oxyde Semiconductor

CW Continuous WaveDA Digital-to-analog

**DAC** Digital-to-analog converter

DC Direct CurrentDD Digital to DigitalDFF Delay Flip FlopDK Design Kit

**DNL** Differential Non-Linearity

**DPCM** Differential Pulse Code Modulation

**DSP** Digital Signal Processor

DUT Device Under TestEM Electro-Magnetic

ENOB Effective Number of BitsEVM Error Vector Magnitude

FDSOI Fully Depleted Silicon On Insulate

**FIFO** First In First Out

FIR Finite Impulse ResponseFM Frequency Modulation

FPGA Field Programable Gate Array

FT Fourier TransformGaN Gallium Nitride

**HEMT** High Electron Mobility Transistor

**HSTL** High Speed Transceiver Logic

IC Integrated Circuit

IF Intermediate FrequencyINL Integral Non-Linearity

$\mathbf{I/O} \qquad \qquad \mathrm{Input/Output}$

**IoT** Internet of Things

IQ In-phase & Quadrature

JTRS Joint Tactical Radio System

LNA Low Noise Amplifier

LTE Long Term Evolution

**LPF** Low-Pass Filter

LSB Less Significant Bit

**LUT** Look-Up Table

MIPS Million Instructions Per Second

MOS Metal Oxide Semiconductor

$\mathbf{MSB}$  Most Significant Bit

NSR Noise Shaping Riemann

**NTF** Noise Transfer Function

OSR Oversampling Ratio

PA Power Amplifier

PCB Printed Circuit Board

**PCM** Pulse Code Modulation

**PDM** Pulse Density Modulation

PLL Phase Locked Loop

PLS Post Layout Simulation

**PPA** Pre-Power Amplifier

**PSD** Power Spectral Density

**QFN** Quad Flat No-lead

**QPSK** Quadrature Phase Shift Keying

**QAM** Quadrature Amplitude Modulation

RADAR RAdio Detection And Ranging

RC Resistance-Capacitance

RF Radio-Frequency

SDM Sigma-Delta Modulation

**SDR** Software-Defined Radio

**SFDR** Spurious-Free Dynamic Range

**SMA** SubMiniature version A

**SR** Software Radio

**SNR** Signal to Noise ratio

**SQNR** Signal to Quantization Noise ratio

**TSMC** Taiwan Semiconductor Manufacturing Company

**UMS** United Monolithic Semiconductors

VHDL Very high-speed integrated circuits Hardware Description Language

## List of Notations

V

Maximum frequency of a useful signal  $f_{max}$  $f_{nyq}$ Nyquist frequency Sampling frequency of a DA conversion  $f_s$ NNumber of bits involved in a DA conversion Power of the noise  $P_n$  $P_s$ Power of a useful signal Quantum of a DA conversion scheme qOversampling factor:  $OSR = 2^r$ r

Voltage amplitude of a CW

### Introduction

The air interface that connects the mobile terminals to the wired network is subject to a rigorous regulation enforced through various communication standards. Next generation wireless communications require a smart and agile use of the spectral resources to increase the data handling capacity of the network.

This trend put severe constraints on the design of mobile device transceivers. They should deal with high data rates, multiple carrier frequencies and various modulation schemes within a very restricted power budget imposed by the limited energy storage of handset terminals.

Chapter 1 exposes the radio communication paradigm and the evolution of radio transmitter architectures. It underlines the trend to increase the flexibility of the wireless transmitters through an increasing use of digital electronics according to the Software Radio principle. The major gain in flexibility is contrasted by a prohibitive energy consumption, especially within the digital to analog conversion operation. The classical conversion schemes are studied and challenged.

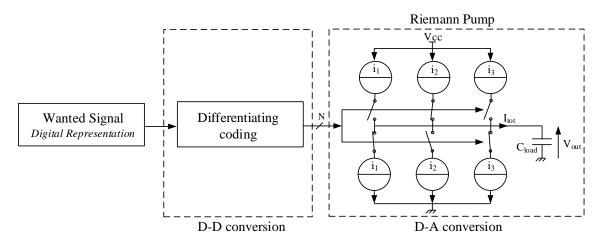

Chapter 2 proposes the theoretical study of disruptive conversion schemes together with a suited digital to analog converter topology. It borrows the principle of Delta modulation involved in some data compression systems. The data conversion process deals with the temporal variations of the signal through a differentiating digital coding to significantly improve the conversion efficiency. The signal reconstruction is performed thanks to a custom integrating digital-to-analog converter named the Riemann Pump. The performances of the proposed system are assessed toward radio frequency signal generation.

Chapter 3 describes the design of the Riemann Pump in two targeted integrated technologies. The first one is a GaN technology dedicated to military applications. The second one is a 65 nm silicon technology adapted to the consumer electronics market. The design of the two circuits is detailed and post-layout simulations are presented to validate the compatibility of the proposed architecture with the chosen technologies and to assess its performances

Chapter 4 presents the measurements carried out on the demonstrator realized in the 65 nm silicon technology. The obtained results bring a physical proof of concept. An extension of the test bench testing capabilities is required to go further in the characterization of the prototypes. Prospects are envisioned to develop a complete transceiver based on the Riemann Pump.

### CHAPTER

1

# Transmitters for ubiquitous network

### Contents

| Comcentes |       |                                                  |    |

|-----------|-------|--------------------------------------------------|----|

| 1.1       | Wire  | eless communication paradigm                     | 24 |

|           | 1.1.1 | Radio frequency transceivers architecture        | 25 |

|           | 1.1.2 | Wireless communication media capacity            | 27 |

|           | 1.1.3 | Mobile terminal transceivers compatibility       | 28 |

| 1.2       | Soft  | ware radio transmitters                          | 29 |

|           | 1.2.1 | Software radio background                        | 29 |

|           | 1.2.2 | Directions of research for flexible transmitters | 32 |

| 1.3       | Data  | a conversion schemes                             | 39 |

|           | 1.3.1 | Pulse code modulation                            | 41 |

|           | 1.3.2 | Pulse density modulation                         | 44 |

|           | 1.3.3 | Conversion efficiency                            | 47 |

| 1.4       | Con   | clusion                                          | 49 |

Chapter 1 presents the architectural trends for next generation RF transmitters. The first part introduces the wireless communication paradigm. It highlights the forthcoming requirements for handset terminal transceivers and the associated technological bottleneck. The second part presents the tracks which tend to overcome this stumbling block, in relation with the state of the art of flexible transmitters. Finally, the associated conversion schemes efficiency is questioned, claiming for disruptive approaches.

Key words: RF transmitters, Data conversion schemes, Software radio, 5G

" The very small value of  $10^{-16}$  of negentropy required per bit of information plays, however, a very important role in modern life, and it makes possible to communicate information at a negligible cost."

Leon Brillouin, Science and Information theory, 1956

In the 50s, Brillouin stated that modern life relies on the possibility to deal with large quantities of information for a minimal cost. In the same decade, the development of the transistor in Bell laboratories led to a physical media allowing to get closer to the theoretical cost of information described by Brillouin. After several decades during which the electronic industry endeavored to follow the Moore's law, standalone devices that can exchange a billion of bits per second fit in one's hand. However, conventional transceiver architectures cannot support the pressing digital convergence while satisfying customer expectations in terms of quality of service, device cost and battery life.

### 1.1 Wireless communication paradigm

In the 2010s, the global amount of information exchanged is still in huge growth, even though it tends to decelerate. In the same time, the proportion of mobile data is rapidly increasing; the connection to the internet becomes more and more nomadic.

Figure 1.1: Global mobile data traffic (source: Gartner 2015)

### 1.1.1 Radio frequency transceivers architecture

The connection of wireless terminals to the network is provided by the mean of radio-frequency (RF) electromagnetic waves. Those terminals are able to transmit and receive information carried at high frequencies, while ensuring the compatibility to various standards which set the traffic rules. The data to be transmitted is conditioned within the transmitter chain to be radiated by the antenna, while the receiver chain recovers the data from the signal picked up by the antenna. The classical simplified architecture of RF direct conversion transceivers is represented in Fig. 1.2.

The transmission chain is composed of four main blocks:

- A baseband processor

- A digital to analog converter (DAC)

- A mixer to convert the signal up to the carrier frequency

- A power amplifier

Figure 1.2: Classical direct conversion transceiver architecture

The baseband processor encodes the user digital information which is then converted into the analog domain thanks to the DAC. The analog signal is up converted to RF within the analog front-end, and then amplified and transmitted through the antenna.

The receiver chain is composed of dual blocks:

- A low noise amplifier

- A mixer to down convert the signal to baseband

- An analog to digital converter (ADC)

- A baseband processor

The RF signal is picked up by the antenna, and amplified by the low noise amplifier. It is then mixed with the carrier frequency so as to recover the baseband data, which is computed by the processor and sent to the user interface. This transceiver architecture is commonly used and implemented in mobile terminals to provide a link to the network.

The growing number of connected terminals and the increasing amount of exchanged data raise congestion issues in the wireless communication space.

### 1.1.2 Wireless communication media capacity

The medium used to convey wireless data is the air. This medium is shared between users along three principal axes, to avoid interferences:

- Geographic areas: the wireless data transmission uses radiofrequency signals transmitted thanks to antennas. The received power decreases with the distance to the transmitter. The network is organized with a cellular pattern, to isolate geographic areas.

- Frequency allocation: the frequency spectrum is divided into channels dedicated to specific services. Several frequency bands are allocated to mobile communications, and those ones are subdivided into channels to handle different users at the same time.

- **Time sharing**: communications on the same channel in the same area can occur by sharing the time. Different portions of time are assigned to users.

Figure 1.3: Venn diagram of the 3-dimensions wireless communication space

The intersection of those three axes defines a communication slot, depicted in Fig. 1.3. To avoid interferences, communication slots must be allocated only once. The capacity and the efficiency of a network depend on the number of communication slots offered, and its adequacy with the local needs. In order to enhance the handling capacity of the wireless network, improving the use efficiency of those three resources will be needed.

• The **geographic areas** obviously depend on the local density of users; cities need a finer mesh than countryside areas. The setting of cells of different size, associated with different transmitting power, allows to locally adapt the capacity of the network to the need.

- The **frequency** allocation is the key resource, controlled and delivered by dedicated authorities. Within the whole spectrum, only a few RF bands are allocated to mobile communications. Those bands are shared between several mobile access providers. Those successive divisions result in relatively narrow bands available for users, in the range of several MHz. The re-allocation of frequency bands will help to meet the need of mobile data communications.

- The **time** is the last dimension to be shared between users. In a same channel, multiple communications can occur thanks to time allocation. However, in the case of intense exchange of data at a given moment, the channel can be saturated. The dynamic allocation of frequency resources along time could improve the traffic fluidity. Instead of the stringent partitioning of frequency bands, those resources could be dynamically re-allocated when needed. It would grant much wider bands when the traffic is sparse, and help to fully use the resources when it is crowded.

Such a radio network is based both on smart network supervision and adaptive radio transceivers.

### 1.1.3 Mobile terminal transceivers compatibility

The classical transceiver architecture depicted in Fig. 1.2 suffers from a lack of flexibility inherent to the conversion performed in the analog front-end. Such a transceiver usually addresses a given standard, corresponding to a relatively narrow frequency band. However, the increase of the access bandwidth relies on the use of large frequency bands distributed all over the RF spectrum. Their introduction comes regularly with new standards and their own requirements. Mobile terminals use different transceivers to address the various standards. This trend to increase the number of parts in the chipset of mobile terminals faces pressing limits related to the industry directions and the consumer expectations.

- Bandwidth: transceivers for handsets have to support more and more data rate, on various frequency bands distributed over a multi-GHz frequency range. They have to ensure an adequate resolution over a very wide frequency band.

- Energy consumption: transceivers are one of the most power hungry part of mobile terminals. They must operate at low power to improve battery life of handsets.

- Cost: to address mass market, the transceivers should be low cost. The cost of a chip is related to the die area and the technology used.

The stacking of chips involved in the handset terminals to address different frequency bands and gather data bandwidth cannot conciliate the previous constraints. The cumulated die area of all

the transceivers turns out large, which impacts the total price of the chips and their integrability in the small volume of a handset terminal. Furthermore, enhancing the total bandwidth thanks to the addition of transceivers would substantially increase the energy consumption since the analog front-end is duplicated for each transceiver. Classical transceivers architectures suffer from a lack of flexibility and they are no more suitable for the expected ubiquitous network. Our purpose is to develop a disruptive architecture of radio transmitter that can take up the challenge.

The next section describes the evolution of wireless transmitter architectures in the past few decades, and the state-of-the-art trends and realizations that tend to overcome the requirements of tomorrow. Then, a come back to the basics of digital to analog conversion will help to apprehend the limits of the commonly used conversion schemes. It raises the need to develop innovative architectures of transmitters.

### 1.2 Software radio transmitters

### 1.2.1 Software radio background

### **1.2.1.1** Principle

In order to meet the need of versatility raised by the new wireless communication perspectives, [1] proposed a new paradigm with the notion of software radio (SR) twenty years ago. The idea is to move the limit between the baseband domain and the RF domain within the digital processor, so as to get rid of the rigid analog front-end. The corresponding ideal architecture is depicted in Fig. 1.4.

Figure 1.4: Software radio transmitter architecture

The ideal SR architecture is composed of 3 blocks:

- A baseband/RF processor

- A wideband digital to analog converter (DAC)

- A wideband power amplifier

This architecture proposes to directly compute the modulated signal (or even a combination of multiple signals) within the digital processor, and to convert the whole transmitting band of several GHz to the analog domain thanks to a wideband converter. The output of the converter then needs to be amplified before transmission through the antenna. Software radio offers a perfect flexibility, since it is virtually compatible with all the existing standards falling into the RF domain, and any new standard can be supported thanks to a simple software update. Furthermore, it allows concurrent transmission of different standards and agile reconfiguration.

### 1.2.1.2 Applications

The works on software radio transceivers are motivated by many applications, involving huge markets.

### Military market

The flexibility of SR transceivers finds a lot of military applications.

- Interoperability: the US military has been seeking a way to improve the ease and flexibility of communications within and between the services. A huge program called joint tactical radio systems (JTRS) has been launched, without success at the time [2].

- Secure communications: the intrinsic flexibility of SR transceivers offers a perfect support to operate dynamic changes of the standards to secure communication links in the battlefield.

- Radar: SR transmitters are able to generate various waveforms, including radar signals.

The accurate control of the waveforms allows to enhance the performances of detection [3].

- Electronic Warfare: To control the electro-magnetic spectrum in a battlefield, the use of versatile transceivers is an asset. A lot of applications rely on the use of agile signals generation (jamming, stealth, countermeasures) [4].

#### Civil market

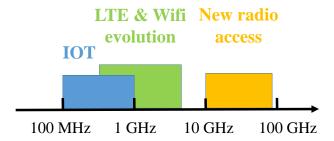

The next generation of wireless communication standards (5G) is expected to offer ubiquitous immersive connectivity, relying on a software upgradable platform. Several researches on the network and communication architectures and techniques are led at the moment [5],[6]. The infrastructures would rely on an heterogeneous network with cells of different sizes [7]. The use of device to device communication is envisioned to virtually densify the network [8], and content caching to reduce data duplication [9]. As for frequency resources, 5G is expected to use as much spectrum as possible [10], divided into 3 frequency ranges for different applications (Fig. 1.5).

Figure 1.5: Technology tracks of 5G era

The sub-6 GHz frequency range ensures a favorable transmission in the air; a data rate higher than 1 Gbps is expected on this band thanks to carrier aggregation. It will be based on an extension of the LTE standard and used by all the devices.

The mmW band has a reduced range and could serve in smaller cells [11], giving access to wide data bandwidth.

The internet of things (IoT) will be deployed in the same time, using the sub-GHz frequency band. The number of connected wireless devices will be in huge growth. Equipping those devices with reconfigurable and low-power transceivers presents a major industrial asset [12].

SR transceivers are in agreement with the implementation of those various techniques which necessitate a high flexibility. Sub-6 GHz and IoT applications are privileged targets for full software radio transmitters. Wireless communication handsets represent the most lucrative market, involving billions of units. It also constitutes one of the most challenging applications.

[13] reminds the technical and technological difficulties to reach high bandwidth and high performances at a reduced power to ensure a longer battery life, and above all with a low cost solution.

A lot of researches are oriented toward the evolution of wireless transmission architectures in the direction of flexible solutions.

### 1.2.2 Directions of research for flexible transmitters

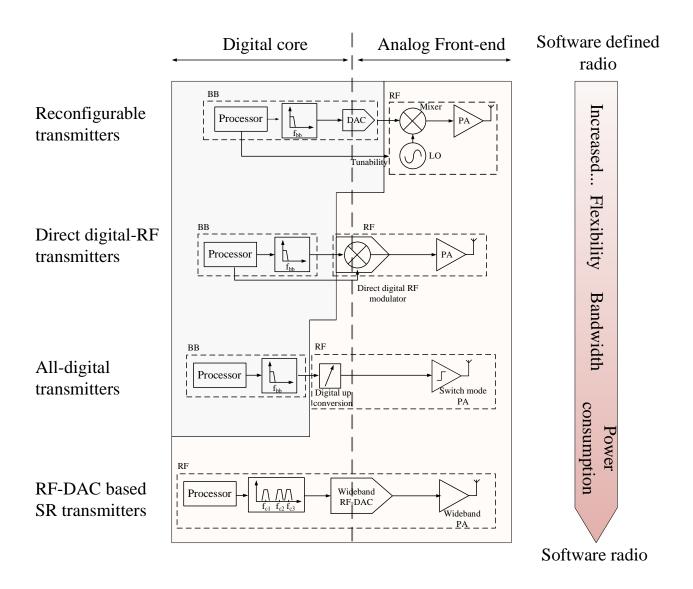

Figure 1.6: From software defined to software radio transmitters

### 1.2.2.1 Reconfigurable transmitters

An intermediate step toward SR is software defined radio (SDR), where the analog front-end is reconfigurable thanks to a digital command. SDR transmitters are based on a baseband or intermediate frequency digital to analog conversion, before a final up-conversion in the analog domain. In those architectures, the reconfigurability of the analog front-end is the tricky point [14]. Various realizations of SDR transmitters are reported in the literature.

[15] proposes a software defined radio transceiver based on direct conversion with a fractional PLL, enabling carrier frequency reconfiguration. The channel bandwidth is tuned up to 16 MHz thanks to reconfigurable low-pass filters.

[16] exhibits a multiband multimode transmitter dedicated to several wireless communication standards. Multiple paths are specifically tailored to meet the precise requirements of the 2G, 3G and 4G standards; only one band group is activated at once.

[17] presents a reconfigurable monolithic transceiver working over [50 MHz - 6 GHz] frequency band. The transmitter operates with direct up conversion for the highest part of the band, and two-step up conversion for the lower part, to filter the local oscillator harmonics.

[18] exposes a SDR transmitter covering the [100 MHz - 6 GHz] band thanks to two distinct paths. The maximal signal bandwidth of 100 MHz can be used to support intra-band dual carrier aggregated signals.

|      | Bandwidth | RF range  | Consumption | CMOS node |

|------|-----------|-----------|-------------|-----------|

|      | (MHz)     | (GHz)     | (mW)        | (nm)      |

| [15] | 16        | 0.15 - 6  | 100         | 130       |

| [16] | 20        | 0.7 - 2.7 | 200         | 90        |

| [17] | 40        | 0.05 - 6  | 900         | 130       |

| [18] | 100       | 0.1 - 6   | 103         | 65        |

Table 1.1: Performances of reconfigurable transmitters.

### 1.2.2.2 Direct digital-RF transmitters

Direct digital-RF transmitters try to merge the DAC and the mixer operation, with only digital inputs. It simplifies the analog front-end and tries to give more flexibility through the increased

use of digital signals. A lot of silicon chips realizations confirm the feasibility to integrate it into handset terminals.

- [19] proposes a direct digital to RF modulator to up-convert a 200 MHz sigma-delta coded base-band signal at 5.25 GHz. An auto-tuned passive band-pass reconstruction filter is placed at the output to cancel the digital images.

- [20] implements an all-digital RF signal generator using low pass sigma delta modulation and digital mixing. It employs redundant logic and non-uniform quantization, and also proposes to use image bands to reach higher frequencies.

- [21] discloses a fully digital multimode polar transmitter. It implements a cartesian to polar converter and a RF-DAC made of current-mode mixers. The local oscillator is generated thanks to a digital PLL.

- [22] presents an all-digital quadrature transmitter where I and Q paths are up-converted within power cells thanks to a digital local oscillator. The two paths are then combined into a differential load.

- [23] addresses the issue of full duplex operation within an RF IQ transmitter. It proposes an embedded FIR filtering of out of band quantization noise to ease full duplex operation.

- [24] employs a digital IQ transmission scheme with 13 bits resolution on each path. The base-band digital signals are digitally mixed and converted into the analog domain thanks to digital to RF amplitude converters.

Table 1.2: Performances of direct digital-RF transmitters.

|      | Bandwidth | RF range   | Consumption | Implementation |

|------|-----------|------------|-------------|----------------|

|      | (MHz)     | (GHz)      | (mW)        |                |

| [19] | 200       | 5.25       | 187         | 130 nm CMOS    |

| [20] | 50        | 0.05 - 1   | 120         | 90 nm CMOS     |

| [21] | 4         | 0.9 & 1.9  | 250         | _              |

| [22] | 80        | 2.2        | 510         | 40 nm CMOS     |

| [23] | 20        | 2.4        | 515         | 65 nm CMOS     |

| [24] | 150       | 0.06 - 3.5 | 560         | 65 nm CMOS     |

Most of the presented works target specific standards. They propose fully integrated solutions, including the power amplification operation. However, the flexibility of the system remains limited and the bandwidth and consumption performances are not sufficient to address forthcoming applications like 5G.

#### 1.2.2.3 All-digital transmitters

Another trend consists in removing most of the analog front-end to propose all-digital architectures. The advancement of CMOS technologies makes digital architectures attractive [25]. The development of FPGA motivated a lot of works on the digital architectures.

[26] uses a pulse width modulation scheme to process the baseband signal and a digital IQ upconversion to carry the signal at 800 MHz. This transmitter architecture is implemented on a FPGA and outputs a 1-bit waveform.

[27] implements an innovative digital architecture and assesses it on a very high speed data signal generator. The idea is to represent a given modulation thanks to a finite state machine and to store all the possible symbol transitions in look-up tables. The baseband bit stream moves within the state machine and triggers the right sequences that are outputted as a 1-bit sequence. A sigma-delta like scheme is employed to perform noise shaping. This approach relies on heavy computational optimizations, but it supposes that the signal is representable by a finite state machine, which limits its applicability.

[28] describes an FPGA-based 1-bit all-digital transmitter using a sigma-delta modulator before digital up-conversion. It demonstrates real-time processing on an FPGA for a signal bandwidth of 2 MHz centered at 0.8 GHz.

[29] implemented a transmitter architecture with sigma-delta baseband processing and digital up-conversion. The baseband scheme is performed with an FPGA which outputs are fed to a multiplexer, together with a high speed clock generated with an external clock generator. The output is then amplified with a switched mode power amplifier.

Most of the presented architectures rely on the use of a digital 1-bit FPGA output to drive a switch-mode power amplifier, with the implementation of different kinds of digital signal conditioning. They demonstrate the interest of such digital techniques to address reconfigurable radiofrequency transmission.

|      | Bandwidth | RF range | Architecture | Implementation         |

|------|-----------|----------|--------------|------------------------|

|      | (MHz)     | (GHz)    |              |                        |

| [26] | 20        | 0.8      | PWM          | FPGA                   |

| [27] | _         | 1 – 13   | SDM-LUT      | Instrumentation        |

| [28] | 2         | 0.8      | SDM          | FPGA                   |

| [29] | 2         | 2.5      | SDM          | FPGA + instrumentation |

Table 1.3: Performances of all-digital transmitters.

On those all-digital transmitters, the digital up-conversion is performed with a multiple of the baseband or intermediate frequency clock, so that the output RF frequency has an integer relationship with the working frequency. This issue has been noticed by [30]; in this reference, a sampling rate adapter is proposed. This constraint of sampling rate and carrier frequency mitigates the flexibility of the system, especially when it comes to multi-standard and multi-band concurrent transmission. Furthermore, the total available bandwidth is limited because the conversion before the digital up-sampling is performed at baseband or intermediate frequency, often involving sigma-delta modulation.

All digital transmitters are attractive because they remove most of the analog components. The proposed architectures are easily implementable and portable to new technological nodes. However, the signal bandwidth is still limited to several tens of MHz, and most of the presented circuits are dedicated to a specific standard. The consumption of the transmitters is difficult to assess because of their implementation on an FPGA.

#### 1.2.2.4 RF-DACs

Even though reconfigurable analog and all-digital transmitters turn out to exhibit features of software defined radio, that is, digital reconfigurability and a relative flexibility, they do not manage to deal with wideband modulated signals or concurrent transmission of a large number of signals in different bands. Those features could be offered by full software radio transmitters, giving an ideal platform to develop large cognitive radio networks [31].

To achieve this kind of architecture, the digital to analog stage has to convert the whole band of transmission, of several GHz. In this way, the complete RF waveform is transmitted, containing any combination of signals with any kind of modulation schemes and bandwidth. Referring to the software radio transmitter basic architecture (Fig. 1.4), it needs a performant digital pro-

cessing core, a wideband digital to analog converter, and a power amplification stage.

The digital to analog converter is particularly critical since it has to ensure a good signal quality over the whole RF spectrum with a low power operation. Plethora of DACs are presented in the literature, with diverse operating frequency and number of bits in the conversion.

[32] implements a 12b current-steering DAC, with specific circuit implementation to limit the mismatching and keep the non-linearities under the LSB level. A segmented architecture is chosen, with 6 binary and 6 unary weighted input bits.

[33] proposes a pseudo segmented current-steering DAC working at 28 GSps, with 6 bits, that implements a time-interleaving technique. This is one of the highest switching frequencies of the state-of-the art. The ENOB falls down to 4.6 bits for the highest part of the band.

[34] uses a 14 bits segmented architecture implemented in a BiCMOS process. Each resampling switch operates on an equivalent current source. A weighting of the 10 LSBs is done through an R-2R ladder.

[35] proposes a current steering DAC architecture, with 14 bits. It implements digital signal conditioning and high speed serialization to control the current array which outputs the differential RF analog signal into resistive loads.

[36] presents a 13 bits current steering DAC working at 9 GSps. It uses specific techniques within the current cells array to reduce code-dependant output capacitance, and a pre-distortion look-up table to improve INL performances.

[37] exhibits a multimode transmitter based on a segmented current steering DAC. The high speed digital interface is embedded to feed the DAC with high speed data.

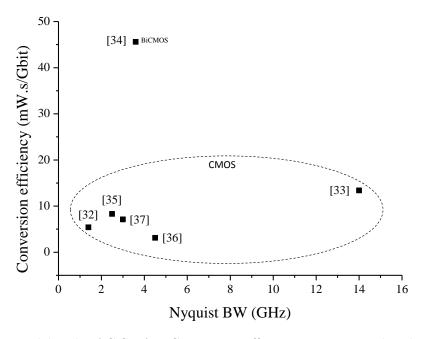

All the presented DACs except one are designed in CMOS technologies. They all implement current-steering topologies, mostly with segmented architectures. Current steering topology is known to be best suited to high speed operation [38].[39] studied the limitations of this architecture in terms of accuracy and speed, the two main characteristics of DACs. The use of time interleaving is an interesting track [40][31][41] to relax the speed of each single path.

The large majority of the DACs presents a too elevated consumption for handset applications,

|      | Data rate | Resolution | Consumption | Efficiency  |

|------|-----------|------------|-------------|-------------|

|      | (Gsps)    | (bits)     | (mW)        | (mW.s/Gbit) |

| [36] | 9         | 13         | 360         | 3.1         |

| [32] | 2.9       | 12         | 188         | 5.4         |

| [35] | 6         | 14         | 600         | 7.1         |

| [37] | 5         | 9          | 375         | 8.3         |

| [33] | 28        | 6          | 2250        | 13.4        |

| [34] | 7.2       | 14         | 4600        | 45.6        |

Table 1.4: Performances of RF-DACs.

ranging from hundreds of milliWatts to the Watt level. The consumption efficiency (mW.s/Gbit) is displayed in Fig. 1.7 versus the Nyquist bandwidth of the listed DACs. It corresponds to the power consumption divided by the data rate involved in the conversion.

Figure 1.7: Wideband DAC SotA – Conversion efficiency Vs Nyquist bandwidth

The DAC realized in BiCMOS process exhibits a substantially higher consumption. The DACs realized in CMOS process are much more efficient, and they have an average conversion efficiency of several mW.s/Gbit. The resulting consumption for a 5 GHz bandwidth 12 bits DAC is around 500 mW, which is far too much for the DAC alone. The power budget of the DAC should be limited to a few tens of mW.

The broadband DAC approach to convert the whole transmitting band is still not integrable in handset terminals, because of a too high power consumption of the DAC itself.

#### 1.2.2.5 Conclusion

Transmitter architectures tend to move from reconfigurable systems still relying on a complex analog front end to more digital solutions. Direct digital-RF transmitters and all-digital transmitters are in constant evolution, and they address present standards. However, the bandwidths are still bounded to several tens of a few hundreds of MHz, and the flexibility is limited. Multi-band concurrent transmission is not always supported.

The development of full SR transmitters would provide the bandwidth and agility required for the future standards. Those systems are based on high speed data processing and a suited RF-DAC. The consumption of state-of-the-art DACs is unfortunately too high to allow the implementation of a full SR transmitter in a handset device. A new kind of RF-DAC is needed to lower the power consumption. It requires an innovative digital to analog conversion scheme to lower the cost of conversion in terms of energy.

In the next section, we propose to come back to digital/analog conversion theory basics. The most classical conversion schemes, involved in the referenced state of the art works, are studied to underline their features toward multi-GHz operation.

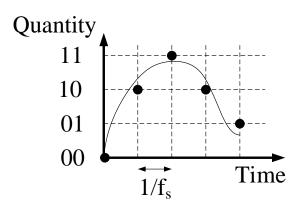

#### 1.3 Data conversion schemes

Quantization is the operation which separates the analog world from its digital counterpart. An analog signal evolves in a 2 dimensions continuous environment, where one is the time. A digital signal is made of a collection of points with discrete coordinates, thus allowing easy representation and storage. The discretization of time is associated with the notion of clock; changes can occur only on clock events. When the clock frequency is constant, the time vector can simply be an index. The binary representation of discrete quantities appears to be the most suitable to electronic implementation. The discretization of quantities thus relies on the use of bits (Fig. 1.8).

The accuracy of the digital representation of an analog signal is tightly related to the involved coding scheme. The two key parameters that drive the accuracy of a conversion are:

- the sampling frequency  $f_s$

- the resolution (number of bits used in the conversion) N

Figure 1.8: Quantization – the DA interface

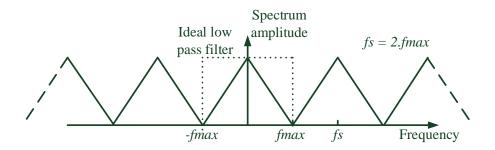

Increasing those two parameters may result in an enhancement of the accuracy of the conversion, at the cost of a higher complexity of the system. As for the electronic implementation, this complexity induces higher component count, energy consumption, die area and design subtlety. A bandwidth limited analog signal of maximum frequency  $f_{max}$  can be perfectly described by an infinite resolution digital signal sampled at the Nyquist frequency ( $f_s = f_{Nyquist}$ ) which is twice  $f_{max}$  (Nyquist-Shannon theorem). That is to say the original analog signal can be recovered without any additive noise; provided the digital signal has a perfect accuracy and the sampling images are ideally filtered (Fig. 1.9). This is theoretically achievable with an infinite number of bits to code the sampled analog levels. Such a signal would exhibit an infinite signal to noise ratio (SNR).

Figure 1.9: Spectrum of an ideally sampled signal

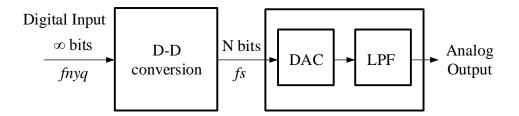

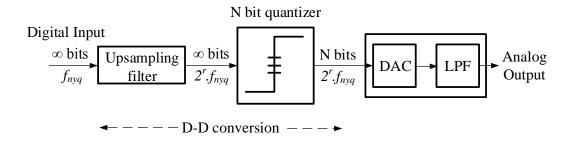

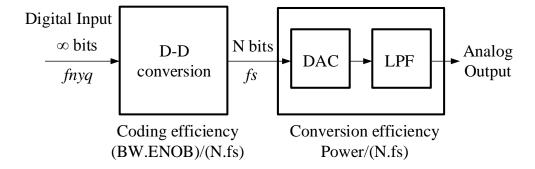

An actual DA conversion obviously involves a digital signal with a limited number of bits to drive the DAC. The overall DA conversion can thus be split into two distinct operations (Fig. 1.10):

• a digital-to-digital (DD) conversion that transforms the ideal digital signal into a resolution-limited digital signal at the working frequency  $f_s$

• a digital to analog converter (DAC) together with an additional low pass filter to retrieve the desired signal

Figure 1.10: Architecture of overall digital to analog conversion

The most popular data coding schemes used for digital-to-analog conversion will be presented hereafter, together with the related quantization noise. Those two widespread techniques are:

- Pulse code modulation (PCM)

- Pulse density modulation (PDM)

#### 1.3.1 Pulse code modulation

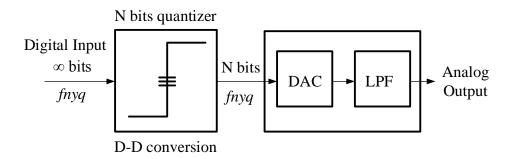

## 1.3.1.1 Nyquist rate pulse code modulation

The most spontaneous way to encode an ideal digital signal with a finite number N of bits is to quantize each sample thanks to a N-bit word at the Nyquist frequency, with a pulse code modulation (PCM) scheme (Fig. 1.11).

Figure 1.11: Nyquist PCM DAC architecture

Such a quantizer disposes of  $2^N$  steps over the whole dynamic [-V, +V]. Considering a uniform repartition of quantization levels, the dynamic is split into  $2^N - 1$  intervals of length  $\frac{2V}{(2^N - 1)}$ , this

length being called the quantum q. Thus, the error  $e_q$  made when quantizing an input sample belongs to [-q/2, +q/2]. The assumption that the probability density function of eq is uniform over this interval is done, which is generally acceptable for full scale signals (e.g modulated signals) [42]. The quantization error can thus be seen as a noise with a power given by:

$$\sigma_e^2 = \int_{-\infty}^{\infty} e_q^2 p(e_q) \, de_q = \int_{-\frac{q}{2}}^{\frac{q}{2}} e_q^2 \frac{1}{q} \, de_q = \frac{q^2}{12}$$

(1.1)

For a large enough N, the quantum q is approximated by  $\frac{2V}{2^N}$ , so that the power of the quantization noise is expressed as:

$$\sigma_e^2 \approx \frac{V^2}{3.2^{2N}} \tag{1.2}$$

This noise is in the general case considered as a white noise lying on the  $\left[\frac{-f_s}{2}, \frac{+f_s}{2}\right]$  frequency band [43]. For further calculations, we consider that the digital input signal represents a full scale sine wave, carrying a power  $\sigma_x^2$  of  $\frac{V^2}{2}$  once reconstructed in the analog domain. The maximum signal to quantization noise ratio (SQNR), is then calculated:

$$SNR_{dB} = 10log_{10}(\frac{\sigma_x^2}{\sigma_e^2}) \approx 6.02N + 1.76$$

(1.3)

This well-known formula is used as a reference to calculate the effective number of bits (ENOB) of converters. Such a SNR could be achieved on the analog output signal with an ideal DAC and an ideal LPF that cuts the frequencies over  $f_{max}$ .

Figure 1.12: Spectrum of a Nyquist rate quantized signal

Most common DAC architectures operate as zero-order holds which generate a staircase signal [44]. From the frequency viewpoint, the zero-order hold multiplies the digital signal spectrum by the cardinal sine function whose first zero is  $2.f_{Nyquist}$ . This has the beneficial effect of providing a first low pass filtering which helps cutting high frequency images. However, it also causes a mild roll-off of gain at the highest frequencies of the desired band, thereby degrading the SNR. An analog low-pass filter is generally added to further attenuate the out-of-band signal, with the same harmful effect on the wanted signal. The technique of oversampling tackles this problem,

through the use of a higher sampling frequency; this opens a frequency gap between  $f_{max}$  and  $\frac{f_s}{2}$  which enables, inter alia, cleaner filtering.

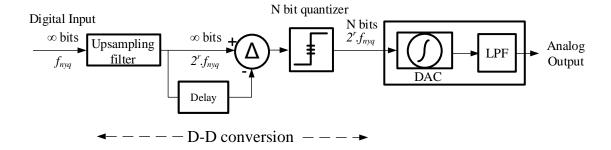

#### 1.3.1.2 Oversampling

Compared to the previously described Nyquist-rate-DD conversion, the oversampled version involves an up-sampling filter that adds samples up to a rate of  $2^r \cdot f_{Nyquist}$  [45]. This operation is considered as ideal, so that it provides samples with infinite resolution without adding any kind of noise.

Figure 1.13: Oversampled PCM DAC architecture

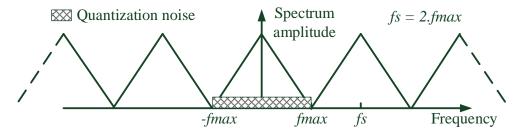

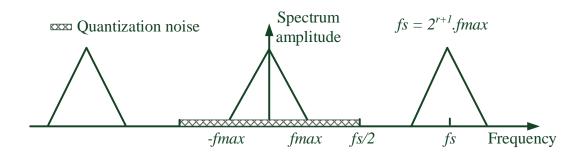

The quantization noise generated by this structure has exactly the same power as before, since the quantizer exhibits the same characteristics and produces the same quantization errors. The difference comes from the repartition of the noise over the spectrum; as mentioned previously, the quantization noise behaves like a white noise for non-peculiar signals. The quantization noise power is thus uniformly distributed over the band  $\left[\frac{-f_s}{2}, \frac{+f_s}{2}\right]$ .

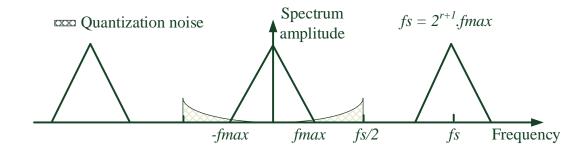

Figure 1.14: Spectrum of an oversampled quantized signal

A part of the quantization noise power stands outside the wanted signal band, and is likely to be filtered out. The in-band quantization noise power is its total power divided by the oversampling ratio (OSR = 2r). Assuming an ideal low pass filtering, the maximum achievable SNR is:

$$SNR_{dB} = 10log_{10}(\frac{\sigma_x^2 \cdot OSR}{\sigma_e^2}) \approx 6.02N + 3.01r + 1.76$$

(1.4)

Oversampling thus allows a slight enhancement of the SNR by partial removal of quantization noise. It also relaxes the constraints on the analog low pass filter since it makes room to filter sampling images without altering the wanted signal; however, in this case, it reduces the amount of quantization noise filtered.

The widespread PCM DAC architecture is able to convert large frequency bands (cf. Tab. 1.4), but it turns out resource intensive to achieve a sufficient SNR, both as far as power consumption and die area are concerned. The reason is that the SNR grows preferentially with the number of bits N used to code quantized levels, and a high N implies a high component count, thereby requesting resources.

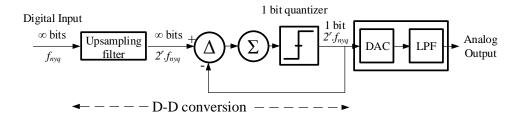

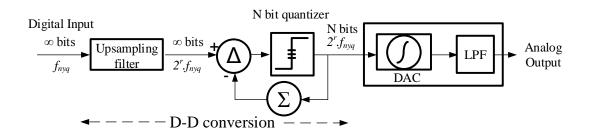

#### 1.3.2 Pulse density modulation

Another way to encode signals is pulse density modulation (PDM), where the relative density of pulses over time represents the amplitude of the corresponding analog signal. Such a modulation can be implemented through the sigma-delta process [46]. It generally uses a one-bit quantizer that outputs a stream of ones and zeros depending on the input signal. A high density of ones corresponds to a high value of the signal and vice versa.

Figure 1.15: First order sigma delta block diagram

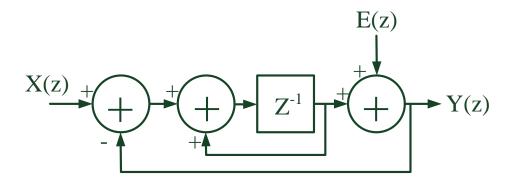

The quantization error produced is fed back in the sigma-delta process so that every error is taken into account into the next sample quantization. This results in the averaging out of the quantization error, so called noise shaping. The description of this phenomenon for a DD sigma-delta modulator is usually done thanks to a linear z-transform block diagram.

Figure 1.16: First order sigma delta z-transform diagram

The input signal X corresponds to the output of the up-sampling filter, which is considered ideal as above; this signal is at a rate of  $2^r.f_{Nyquist}$ , with a virtually infinite resolution. The integrator that sums the difference between X and Y is represented as an adder associated with a delay element. The quantizer is modeled by an additive noise E. The output Y can be calculated versus the two inputs, respectively the wanted signal X and the quantization noise E:

$$Y(z) = X(z).z^{-1} + E(z).(1 - z^{-1})$$

(1.5)

The wanted signal is simply delayed by a sample period, whereas the quantization noise is shaped by a high pass transfer function. The total quantization noise of the system is the one of a one-bit quantizer of dynamic [-V, +V]; it exhibits a quantum q of 2V. The quantization noise power equals  $\frac{q^2}{12}$ , i.e:

$$\sigma_e^2 = \frac{q^2}{12} = \frac{V^2}{3} \tag{1.6}$$

The spectral distribution  $S_e(f)$  of this noise power for the open loop version would be uniform in the range  $\left[\frac{-f_s}{2}, \frac{+f_s}{2}\right]$ .

$$S_e(f) = \frac{\sigma_e^2}{f_s} \tag{1.7}$$

In the sigma-delta configuration, this noise is shaped instead, with the previously calculated noise transfer function. This transfer function can be expressed in the frequency domain as:

$$NTF(f) = 1 - e^{-j2\pi \frac{f}{f_s}}$$

(1.8)

It leads to:

$$|NTF(f)|^2 = (1 - e^{-j2\pi \frac{f}{f_s}})(1 - e^{j2\pi \frac{f}{f_s}}) = 4\sin^2(\pi \frac{f}{f_s})$$

(1.9)

The in-band quantization noise, i.e the part of the noise which lies on the frequency band  $[-f_{max}, f_{max}]$ , is given as:

$$\sigma_n^2 = \int_{-f_{max}}^{f_{max}} S_e(f) \cdot |NTF(f)|^2 df = \frac{\sigma_e^2}{f_s} \int_{-f_{max}}^{f_{max}} 4sin^2(\pi \frac{f}{f_s}) df = 2 \cdot \sigma_e^2 \left[ \frac{1}{OSR} - \frac{1}{\pi} sin(\frac{\pi}{OSR}) \right]$$

(1.10)

Assuming a large enough OSR, the Taylor series expansion of the sinus function can be used, so as to simplify the previous equation:

$$sin(x) \approx x - \frac{x^3}{3!} + \frac{x^5}{5!} + \dots + \frac{(-1)^N x^{2N+1}}{(2N+1)!}$$

(1.11)

And,

$$\sigma_n^2 \approx \sigma_e^2 (\frac{\pi^2}{3.OSR^3}) \tag{1.12}$$

Figure 1.17: Spectrum of a SDM quantized signal

The maximum SNR theoretically achievable with an ideal low pass filtering – when the input corresponds to a full scale sine wave – is thus given as:

$$SNR_{dB} = 10log_{10}(\frac{\sigma_x^2}{\sigma_x^2}) \approx 9.03r - 3.41$$

(1.13)

It is to note that using an N-bit quantizer has the same effect as on the PCM architecture, that is enhancing the maximum SNR of 6 dB per additional bit. Compared with the PCM architecture, the maximum SNR highly improves with the OSR. However, this works only under the

assumption of a high enough SNR. Indeed, in the in-band quantization noise calculation, the inversely proportional to OSR term can be cancelled by the first term of the sinus Taylor series only if the argument of the sinus is small enough. In the case of a low to moderate SNR, this assumption falls and the resulting term lowers the SNR compared with the calculated formula. This observation is relevant with all the more reason for higher order sigma-delta modulators - where the SNR depends even more on the OSR - since their principle is based on the cancellation of the successive terms of the sinus Taylor series.

This architecture is likely to be efficient for baseband signals conversion, up to several tens or hundreds of MHz (cf. Tab. 1.3). Large frequency band conversion (over the GHz range) implies a relatively low OSR because of technological limitations. As a consequence, the frequency gap between  $f_{max}$  and  $\frac{f_s}{2}$  is likely to be thinner than a decade, which makes it difficult to fully benefit from noise shaping. The major problem of this topology under these conditions is that the total quantization noise does not wane as OSR is increasing, it remains constant instead.

## 1.3.3 Conversion efficiency

Figure 1.18: Efficiency of global digital to analog conversion

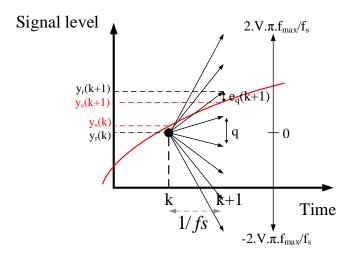

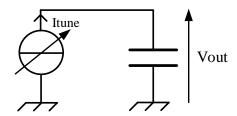

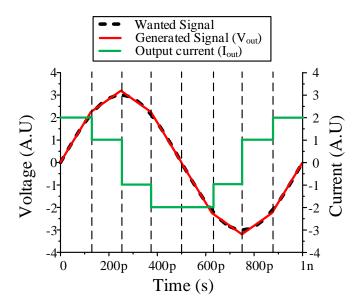

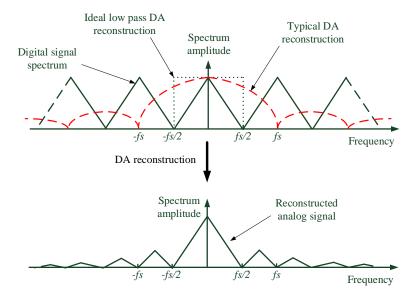

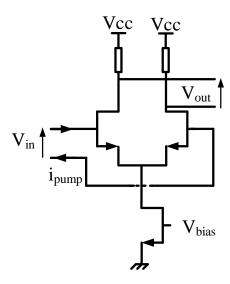

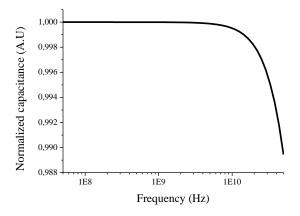

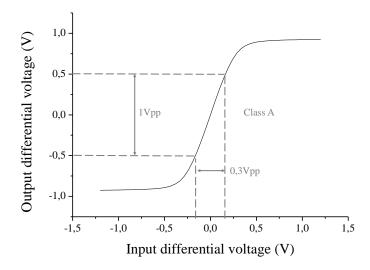

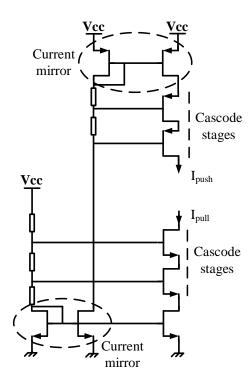

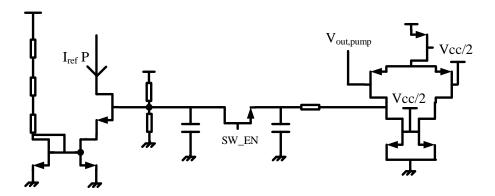

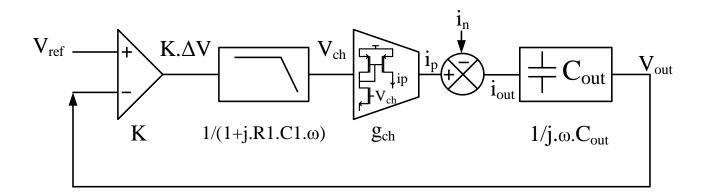

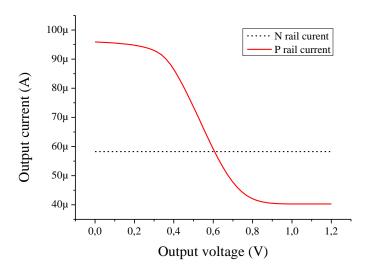

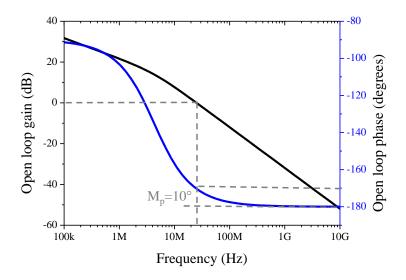

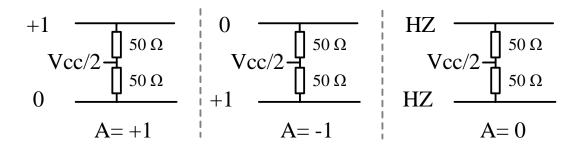

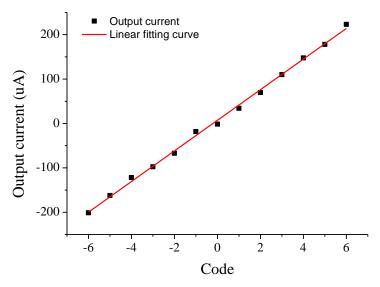

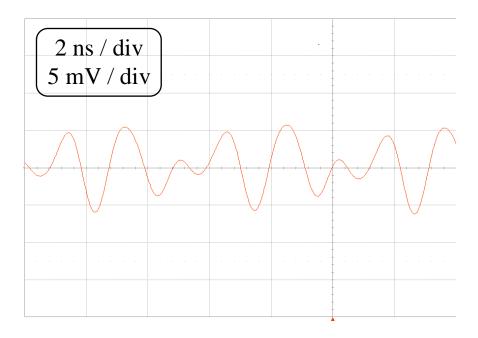

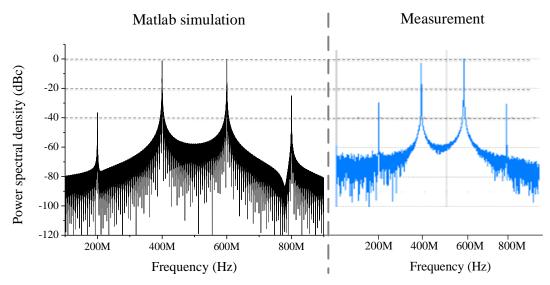

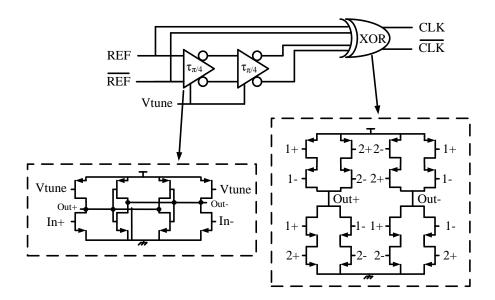

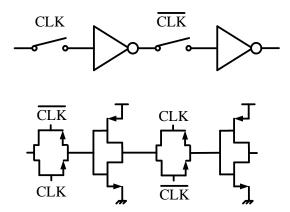

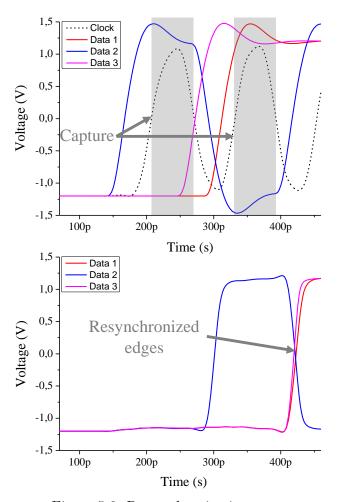

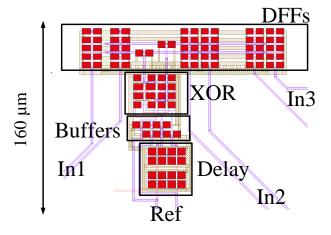

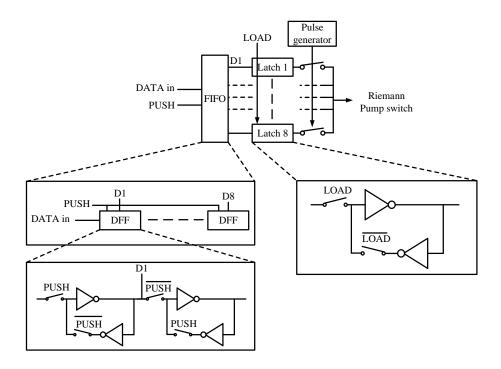

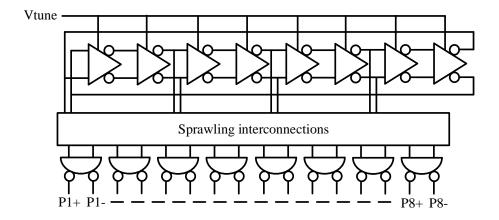

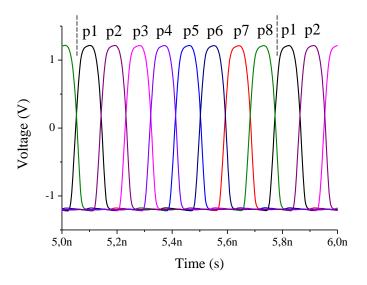

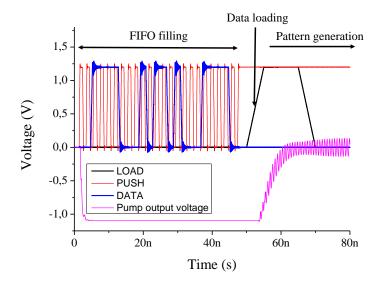

The global efficiency of a digital to analog architecture mainly comes from two origins: