## Solving dense linear systems on accelerated multicore architectures

Adrien Rémy

#### ▶ To cite this version:

Adrien Rémy. Solving dense linear systems on accelerated multicore architectures. Hardware Architecture [cs.AR]. Université Paris Sud - Paris XI, 2015. English. NNT: 2015PA112138. tel-01225745

#### HAL Id: tel-01225745 https://theses.hal.science/tel-01225745

Submitted on 6 Nov 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Université Paris-Sud

#### **THÈSE**

pour obtenir le grade de

DOCTEUR EN INFORMATIQUE DE L'UNIVERSITÉ PARIS-SUD

PRÉPARÉE AU LABORATOIRE DE RECHERCHE EN INFORMATIQUE DANS LE CADRE DE l'École Doctorale 427 : Informatique Paris-Sud

PRÉSENTÉE ET SOUTENUE PUBLIQUEMENT

PAR

#### ADRIEN RÉMY

8 Juillet 2015

# SOLVING DENSE LINEAR SYSTEMS ON ACCELERATED MULTICORE ARCHITECTURES

#### Directeur de thèse :

Mr. Marc Baboulin

#### JURY

M. Stef Graillat Rapporteur Professeur Université Paris 6

M. Paulo Beleza Vasconcelos Rapporteur Professeur Universidade do Porto

M. Philippe Langlois Examinateur Professeur Université de Perpignan

M. Marc Baboulin Directeur de thèse M. Nicolas M.Thiéry Examinateur Professeur Université Paris Sud

#### Solving dense linear systems on accelerated multicore architectures

#### Abstract:

In this PhD thesis, we study algorithms and implementations to accelerate the solution of dense linear systems by using hybrid architectures with multicore processors and accelerators. We focus on methods based on the LU factorization and our code development takes place in the context of the MAGMA library.

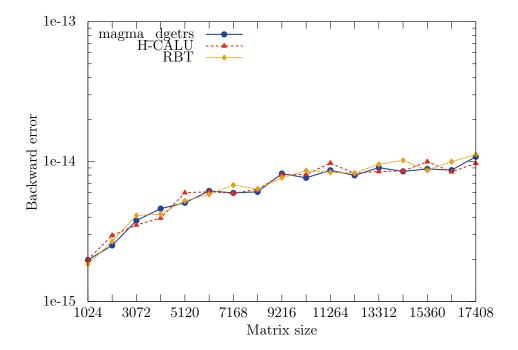

We study different hybrid CPU/GPU solvers based on the LU factorization which aim at reducing the communication overhead due to pivoting. The first one is based on a communication avoiding strategy of pivoting (CALU) while the second uses a random preconditioning of the original system to avoid pivoting (RBT). We show that both of these methods outperform the solver using LU factorization with partial pivoting when implemented on hybrid multicore/GPUs architectures.

We also present new solvers based on randomization for hybrid architectures for Nvidia GPU or Intel Xeon Phi coprocessor. With this method, we can avoid the high cost of pivoting while remaining numerically stable in most cases. The highly parallel architecture of these accelerators allow us to perform the randomization of our linear system at a very low computational cost compared to the time of the factorization.

Finally we investigate the impact of non-uniform memory accesses (NUMA) on the solution of dense general linear systems using an LU factorization algorithm. In particular we illustrate how an appropriate placement of the threads and data on a NUMA architecture can improve the performance of the panel factorization and consequently accelerate the global LU factorization. We show how these placements can improve the performance when applied to hybrid multicore/GPU solvers.

**Keywords:** Dense linear systems, LU factorization, dense linear algebra libraries, MAGMA library, hybrid multicore/GPU computing, graphics process units, Intel Xeon Phi, ccNUMA, communication-avoiding algorithms, randomization, thread placement.

## Résoudre des systèmes linéaires denses sur des architectures composées de processeurs multicœurs et d'accélerateurs.

#### Résumé:

Dans cette thèse de doctorat, nous étudions des algorithmes et des implémentations pour accélérer la résolution de systèmes linéaires denses en utilisant des architectures composées de processeurs multicœurs et d'accélérateurs. Nous nous concentrons sur des méthodes basées sur la factorisation LU. Le développement de notre code s'est fait dans le contexte de la bibliothèque MAGMA.

Tout d'abord nous étudions différents solveurs CPU/GPU hybrides basés sur la factorisation LU. Ceux-ci visent à réduire le surcoût de communication dû au pivotage. Le premier est basé sur une stratégie de pivotage dite "communication avoiding" (CALU) alors que le deuxième utilise un préconditionnement aléatoire du système original pour éviter de pivoter (RBT). Nous montrons que ces deux méthodes surpassent le solveur utilisant la factorisation LU avec pivotage partiel quand elles sont utilisées sur des architectures hybrides multicœurs/GPUs.

Ensuite nous développons des solveurs utilisant des techniques de randomisation appliquées sur des architectures hybrides utilisant des GPU Nvidia ou des coprocesseurs Intel Xeon Phi. Avec cette méthode, nous pouvons éviter l'important surcoût dû pivotage tout en restant stable numériquement dans la plupart des cas. L'architecture hautement parallèle de ces accélérateurs nous permet d'effectuer la randomisation de notre système linéaire à un coût de calcul très faible par rapport à la durée de la factorisation.

Finalement, nous étudions l'impact d'accès mémoire non uniformes (NUMA) sur la résolution de systèmes linéaires denses en utilisant un algorithme de factorisation LU. En particulier, nous illustrons comment un placement approprié des processus légers et des données sur une architecture NUMA peut améliorer les performances pour la factorisation du panel et accélérer de manière conséquente la factorisation LU globale. Nous montrons comment ces placements peuvent améliorer les performances quand ils sont appliqués à des solveurs hybrides multicœurs/GPU.

Mots clés : Systèmes linéaires denses, factorisation LU, bibliothèques logicielles pour l'algèbre linéaire dense, bibliothèque MAGMA, calcul hybride multicœur/GPU, processeurs graphiques, Intel Xeon Phi, ccNUMA, communicationavoiding, randomisation, placement des processus légers.

### Contents

| In | trod | uction |                                                                  | 2  |

|----|------|--------|------------------------------------------------------------------|----|

| 1  | Alg  |        | ns, architectures and libraries                                  | 4  |

|    | 1.1  |        | luction                                                          | 4  |

|    | 1.2  |        | ng dense linear systems                                          | 7  |

|    | 1.3  |        | ctorization                                                      | 8  |

|    |      | 1.3.1  | Gaussian elimination                                             | 8  |

|    |      | 1.3.2  | The issue of pivoting                                            | 9  |

|    |      | 1.3.3  | Partial pivoting                                                 | 9  |

|    |      | 1.3.4  | Block LU factorization                                           | 10 |

|    |      | 1.3.5  | Right-looking block LU                                           | 11 |

|    |      | 1.3.6  | Parallel pivoting strategies                                     | 13 |

|    |      | 1.3.7  | Random Butterfly Transformation (RBT)                            | 16 |

|    | 1.4  | Parall | el architectures                                                 | 18 |

|    |      | 1.4.1  | Distributed memory systems                                       | 18 |

|    |      | 1.4.2  | SIMD extensions                                                  | 18 |

|    |      | 1.4.3  | Multicore processors                                             | 20 |

|    |      | 1.4.4  | Non Uniform Memory Access (NUMA) architecture                    | 20 |

|    |      | 1.4.5  | General Purpose Computation on Graphics Processing Units (GPGPU) | 22 |

|    |      | 1.4.6  | Intel Xeon Phi accelerators                                      | 24 |

|    | 1.5  | Nume   | erical linear algebra libraries for dense matrices               | 26 |

|    |      | 1.5.1  | The historical libraries                                         | 26 |

|    |      | 1.5.2  | Parallel implementations                                         | 27 |

|    |      | 1.5.3  | The MAGMA Library                                                | 28 |

|    | 1.6  | Concl  | usion of Chapter 1                                               | 28 |

| 2  | Hyl  | orid C | PU/GPU algorithms for LU factorization                           | 31 |

|    | 2.1  | Dense  | e linear algebra on accelerated multicore machines               | 31 |

|    | 2.2  | MAG    | MA implementations of LU factorization                           | 33 |

|    |      | 2.2.1  | Mono GPU implementation                                          | 33 |

|    |      | 2.2.2  | Multi GPUs implementation                                        | 35 |

|    | 2.3  |        | d implementation of tournament pivoting LU                       | 36 |

|    | 2.4  | Perfor | rmance comparisons                                               | 38 |

|    |      | 2.4.1  | Experimental framework                                           | 38 |

|    |      | 2.4.2  | Performance for the panel factorization                          | 39 |

|    |      | 2.4.3  | Performance for the hybrid LU implementations                    | 43 |

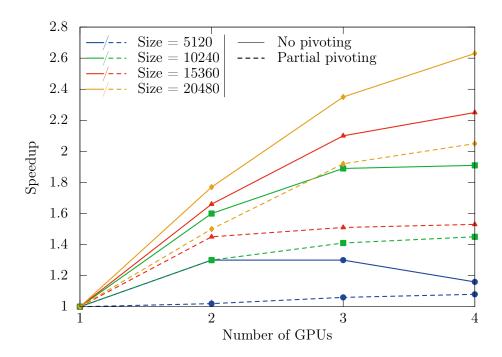

|    |      | 2.4.4  | Performance on multiple GPUs                                     | 46 |

|    | 2.5  | Concl  | usion of Chapter 2                                               | 47 |

Contents

| 3  | A fa   | ast randomized solver for accelerated multicore systems | 49         |

|----|--------|---------------------------------------------------------|------------|

|    | 3.1    | Introduction                                            | 49         |

|    | 3.2    | RBT solver                                              | 50         |

|    | 3.3    | Hybrid RBT algorithm                                    | 52         |

|    | 3.4    | RBT solver using Graphic Process Units                  | 54         |

|    |        | 3.4.1 Implementation                                    | 55         |

|    |        | 3.4.2 Performance                                       | 56         |

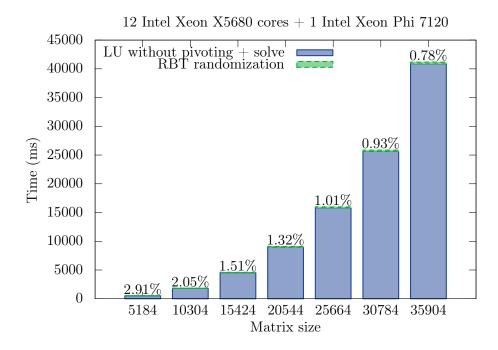

|    | 3.5    | RBT solver using Intel Xeon Phi coprocessors            | 58         |

|    |        | 3.5.1 Implementation                                    | 59         |

|    |        | 3.5.2 Performance                                       | 61         |

|    | 3.6    | Conclusion of Chapter 3                                 | 62         |

| 4  | Loc    | ality optimization for NUMA architectures               | 63         |

|    | 4.1    | Using NUMA architectures for dense linear systems       | 63         |

|    | 4.2    | Application context                                     | 65         |

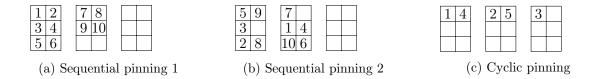

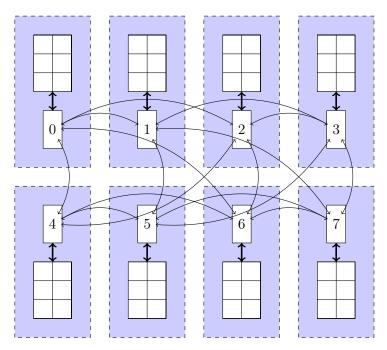

|    | 4.3    | Placement strategies                                    | 65         |

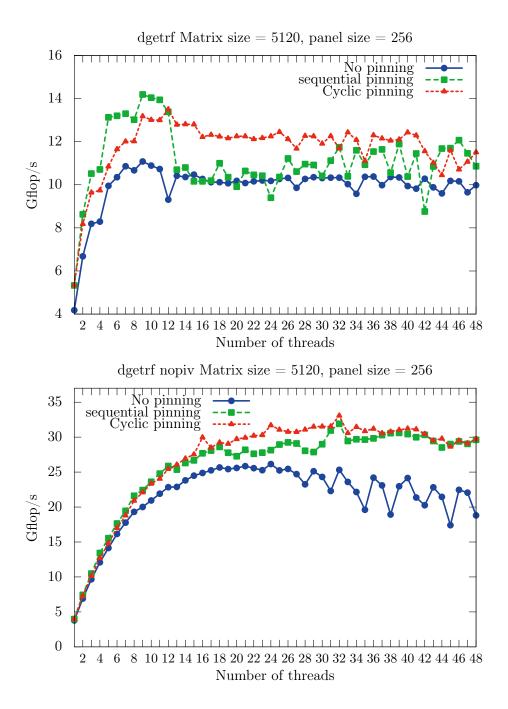

|    | 4.4    | Application to LU factorization                         | 67         |

|    |        | 4.4.1 Experimental framework                            | 67         |

|    |        | 4.4.2 Performance for the panel factorization           | 68         |

|    |        | 4.4.3 Performance for the hybrid code                   | 72         |

|    | 4.5    | Conclusion of Chapter 4                                 | 74         |

| C  | onclu  | asion and future work                                   | <b>7</b> 5 |

| Bi | ibliog | graphy                                                  | 77         |

## List of Figures

| 1.1  | Memory access patterns for variants of LU decomposition from [1] .              | 11 |

|------|---------------------------------------------------------------------------------|----|

| 1.2  | Threads work                                                                    | 15 |

| 1.3  | Example of execution with 4 threads                                             | 15 |

| 1.4  | Principle of the SIMD extensions                                                | 19 |

| 1.5  | A Sandy bridge $E die^1 \dots \dots \dots \dots \dots \dots$                    | 21 |

| 1.6  | Topology of a computer with 2 NUMA nodes                                        | 22 |

| 1.7  | Nvidia Tesla K40 GPU $^2$                                                       | 23 |

| 1.8  | Intel Xeon Phi Coprocessors <sup>3</sup>                                        | 25 |

| 2.1  | Block splitting in hybrid LU factorization                                      | 34 |

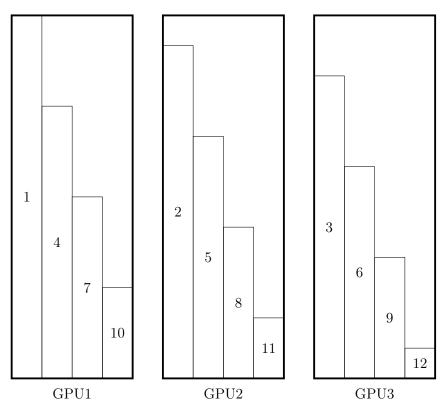

| 2.2  | Example of orders for the panels pactorizations in Magma with 3                 |    |

|      | GPUs and a panel size being $1/12$ of the matrix size                           | 36 |

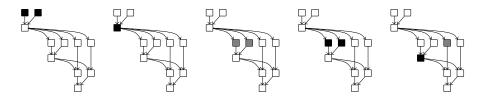

| 2.3  | Example of asynchronous LU factorization using multithreaded CALU               |    |

|      | (2 threads, 3 column blocks) on CPUs                                            | 37 |

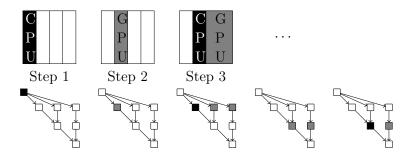

| 2.4  | Hybrid CALU factorization (4 panels)                                            | 38 |

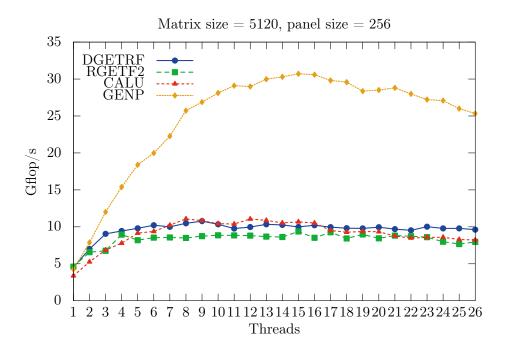

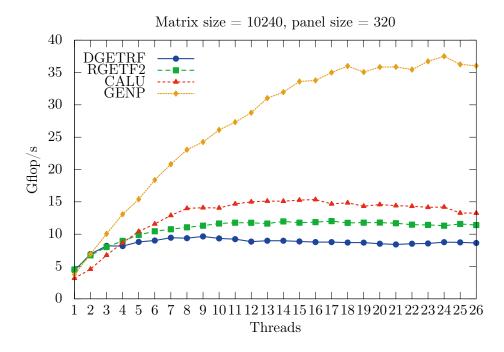

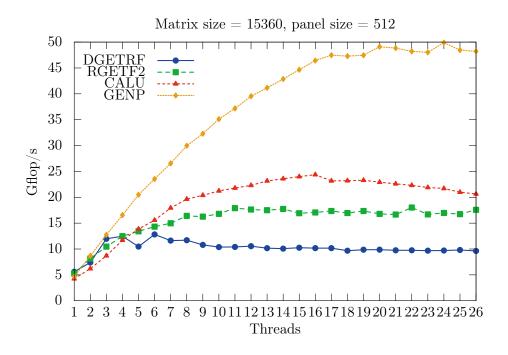

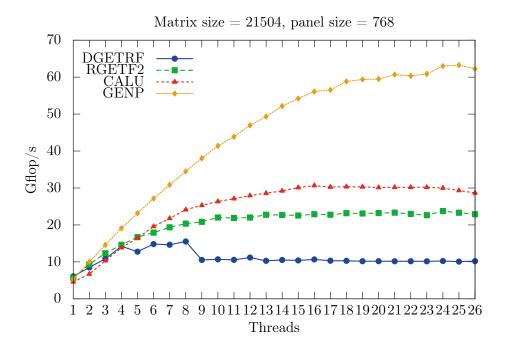

| 2.5  | Comparison of CPU multi-threaded panel factorizations                           | 41 |

| 2.6  | Comparison of CPU multi-threaded panel factorizations                           | 41 |

| 2.7  | Comparison of CPU multi-threaded panel factorizations                           | 42 |

| 2.8  | Comparison of CPU multi-threaded panel factorizations                           | 42 |

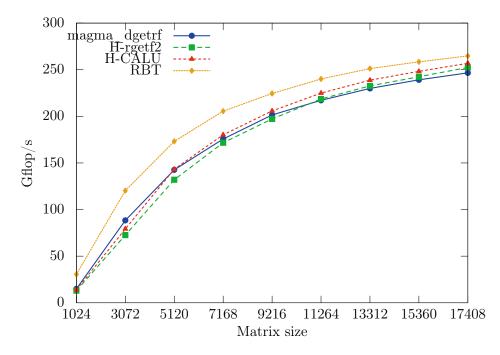

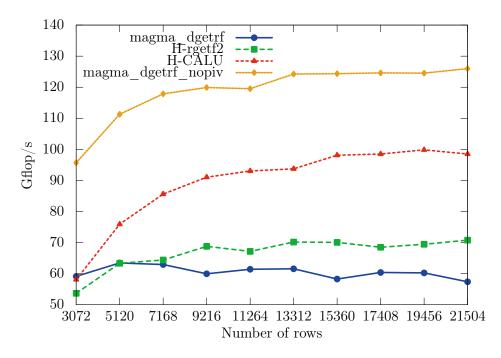

| 2.9  | Performance on square matrices                                                  | 43 |

| 2.10 | Performance on rectangular matrices                                             | 44 |

| 2.11 |                                                                                 | 45 |

| 2.12 | Performance of LU factorizations on multiple GPUs                               | 47 |

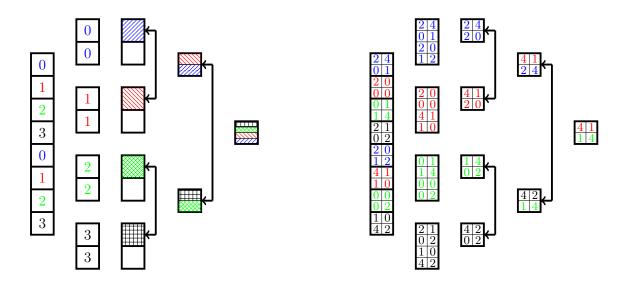

| 3.1  | Packed storage for a recursive butterfly matrix                                 | 51 |

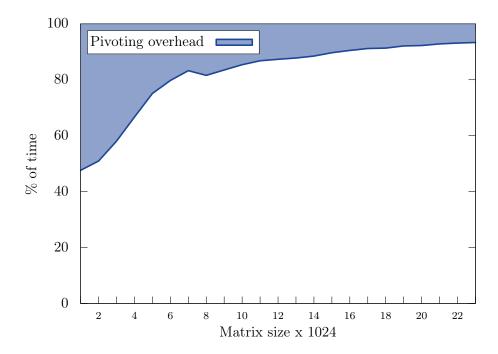

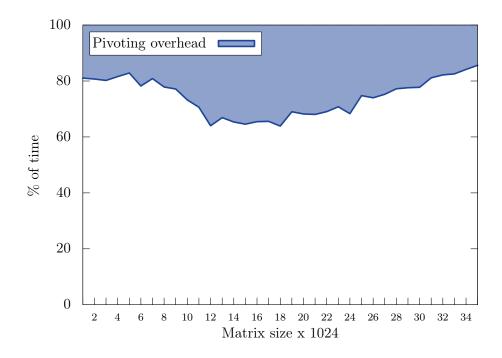

| 3.2  | Pivoting cost of the LU factorization on GPU                                    | 54 |

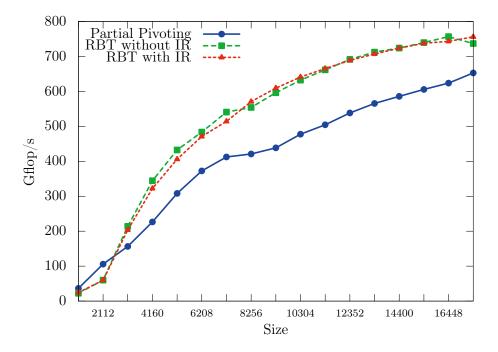

| 3.3  | Performance of the RBT solver on GPU                                            | 57 |

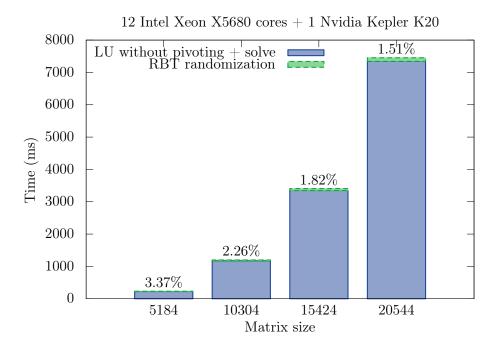

| 3.4  | Time breakdown of the RBT solver on GPU                                         | 58 |

| 3.5  | Pivoting cost in the LU factorization on Xeon Phi                               | 59 |

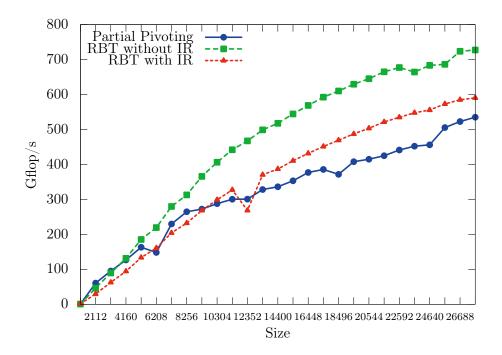

| 3.6  | Performance of the RBT solver on Xeon Phi coprocessor                           | 61 |

| 3.7  | Time breakdown of the RBT solver on Xeon Phi coprocessor                        | 62 |

| 4.1  | Examples of pinning methods                                                     | 66 |

| 4.2  | Architecture representation (8 nodes, 6 cores each)                             | 68 |

| 4.3  | Performance of thread pinning strategies for LU panel factorization             |    |

|      | with pivoting (top) and no pivoting (bottom). Panel sizes: $5120 \times 256$ .  | 69 |

| 4.4  | Performance of thread pinning strategies for LU panel factorization             |    |

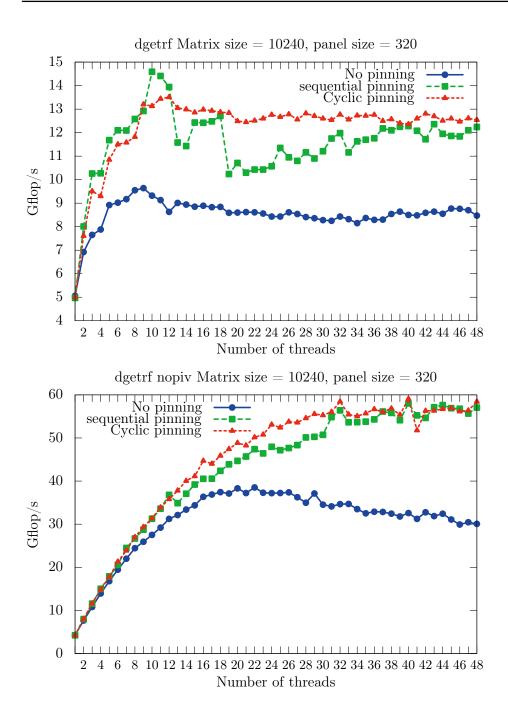

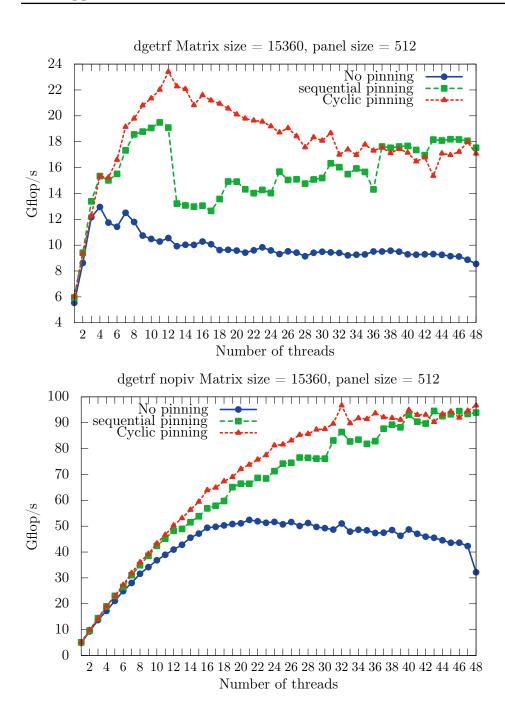

|      | with pivoting (top) and no pivoting (bottom). Panel sizes: $10240 \times 320$ . | 70 |

| 4.5  | Performance of thread pinning strategies for LU panel factorization             |    |

|      | with pivoting (top) and no pivoting (bottom). Panel sizes: $15360 \times 512$ . | 71 |

| $\mathbf{List}$ | of Figures | vii |

|-----------------|------------|-----|

|                 |            |     |

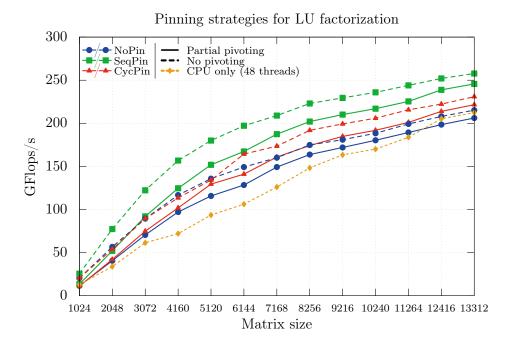

| 4.6 | Performance for hybrid LU factorization with partial pivoting and no |    |

|-----|----------------------------------------------------------------------|----|

|     | pivoting (12 threads)                                                | 73 |

#### Introduction

In many computational applications, the most time and resource consuming task consists in solving a linear system of equations of the form Ax = b. Then the major challenge is to compute a solution x as fast as possible while maintaining a satisfactory accuracy. The main purpose of this PhD thesis is to study solutions to accelerate dense linear solvers using state-of-the-art parallel architectures, which often include accelerators.

In this work we focus on the LU decomposition of dense matrices. We propose different algorithms and implementations to accelerate this factorization. These dense solvers can be used to directly solve systems of equations or as kernels in sparse direct or iterative solvers.

To solve these problems as fast as possible, the algorithms should be adapted to be efficient and scalable on current parallel machines. Moreover the solver implementations should be adapted to the architectural features of these parallel systems. In our work we take into account several characteristics of parallel computers: the use of accelerators such as GPGPUs and Intel Xeon Phi coprocessors, the SIMD parallelism required to program efficiently these accelerators, and Non Uniform Memory Access (NUMA) architectures used in multi-socket shared memory computers.

These parallel architectures provide an increasing computational power and need some special requirements to be exploited efficiently. For example to take advantage of accelerators, we need to consider relatively large problems with a high arithmetic intensity. Also we need to take into account the cost of data transfers between the host and the accelerator through the PCI Express bus which has a limited bandwidth capacity. The use of the SIMD programming requires memory alignment and a very low level programming paradigm. The NUMA architectures require a good management of data locality and thread placement to avoid congestion on the memory links.

Our code developments are made in the context of the MAGMA library which is a dense numerical linear algebra library, designed for hybrid architectures with accelerator (including GPU and Intel Xeon Phi). MAGMA implements the algorithms of the widely used LAPACK library.

We propose different algorithms and implementations to solve large dense linear systems of equations via the LU factorization and some of the resulting code have been integrated into the MAGMA library. We compare the performance of these new optimized implementations to the state-of-the-art methods and discuss their numerical stability.

In Chapter 1, we present an overview of the scientific background of this thesis. We first discuss requirements for solving linear systems of equations and the historical connection with the evolution of computers. We mention the numerical stability issues and explain what are the state-of-the-art solutions used for maintaining sta-

bility thanks to pivoting. We present details on the methods used to solve dense linear systems and emphasize on the LU decomposition, describing the methods of pivoting and parallel algorithms. We then describe the parallel architectures used for High Performance Computing (HPC), discussing their pros and cons and how they can be used in this work. This thesis being closely related with the development of dense linear algebra libraries, we describe the evolution of these libraries and their applications.

In Chapter 2, we discuss different methods of pivoting in the LU factorization algorithm, when performed on hybrid architecture combining multicore processors and GPUs. We describe how the LU factorization is implemented in the MAGMA library and we explain how it can be adapted for different pivoting strategies. We present our implementation of the Communication-Avoiding LU (CALU) factorization for hybrid architecture with GPU and we give details on factorization using multiple GPUs. We then compare the numerical stability and provide performance results.

In Chapter 3, we focus on the use of Random Butterfly Transformation (RBT), in linear system solvers using accelerators. We describe our implementations of the RBT solver for the MAGMA library. We describe the methods we used and how in particular we take advantage of the GPU and Intel Xeon Phi accelerators. We also give some details on the randomization cost and provide performance results.

In Chapter 4, we study and compare different methods to use efficiently Non Uniform Memory Access (NUMA) platforms in the context of dense linear algebra libraries. We propose different methods of thread and data placement to ensure data locality. We apply these methods to the LU factorization comparing their impact on the performance for the panel factorization of the solver and on a global hybrid solver using a GPU as an accelerator.

We finally give some concluding remarks and discuss some ongoing or possible research tracks.

## Algorithms, architectures and libraries

| Contents |                              |                                                                  |           |  |  |

|----------|------------------------------|------------------------------------------------------------------|-----------|--|--|

| 1.1      | Intr                         | oduction                                                         | 4         |  |  |

| 1.2      | Solving dense linear systems |                                                                  |           |  |  |

| 1.3      | $\mathbf{L}\mathbf{U}$       | factorization                                                    | 8         |  |  |

|          | 1.3.1                        | Gaussian elimination                                             | 8         |  |  |

|          | 1.3.2                        | The issue of pivoting                                            | 9         |  |  |

|          | 1.3.3                        | Partial pivoting                                                 | 9         |  |  |

|          | 1.3.4                        | Block LU factorization                                           | 10        |  |  |

|          | 1.3.5                        | Right-looking block LU                                           | 11        |  |  |

|          | 1.3.6                        | Parallel pivoting strategies                                     | 13        |  |  |

|          | 1.3.7                        | Random Butterfly Transformation (RBT)                            | 16        |  |  |

| 1.4      | Para                         | allel architectures                                              | 18        |  |  |

|          | 1.4.1                        | Distributed memory systems                                       | 18        |  |  |

|          | 1.4.2                        | SIMD extensions                                                  | 18        |  |  |

|          | 1.4.3                        | Multicore processors                                             | 20        |  |  |

|          | 1.4.4                        | Non Uniform Memory Access (NUMA) architecture                    | 20        |  |  |

|          | 1.4.5                        | General Purpose Computation on Graphics Processing Units (GPGPU) | 22        |  |  |

|          | 1.4.6                        | Intel Xeon Phi accelerators                                      | 24        |  |  |

| 1.5      | Nur                          | nerical linear algebra libraries for dense matrices              | <b>26</b> |  |  |

|          | 1.5.1                        | The historical libraries                                         | 26        |  |  |

|          | 1.5.2                        | Parallel implementations                                         | 27        |  |  |

|          | 1.5.3                        | The MAGMA Library                                                | 28        |  |  |

| 1.6      | Con                          | aclusion of Chapter 1                                            | 28        |  |  |

#### 1.1 Introduction

Solving linear systems of equations has always been a valued approach to solve real life problems in numerous domains such as physics, biology, geometry... Four

1.1. Introduction 5

thousand years ago, Babylonians had already found out how to solve a  $2 \times 2$  linear system. Around 200 BC, a Chinese book called the "Nine chapters of mathematical art" explained how to solve a  $3 \times 3$  linear system using a method similar to the Gaussian elimination [2].

However the study of linear algebra began in the late  $17^{th}$  century with the study of determinants by Gottfried Leibniz. In the early  $19^{th}$  century, Carl Gauss developed a method called "Gaussian elimination" in order to solve linear systems of equations. Then in 1848, James Joseph Sylvester introduced the word "matrix" and in 1855 Arthur Cayley defined the matrix multiplication. Matrix computations took a turning point around World War II with the emergence of the first computers. This allowed linear algebra methods to solve faster and more accurately large systems of equations. Note that Gaussian elimination is still the best known method to solve a linear system of equations [3].

Then it was possible to solve bigger systems thanks to the development of computers. In 1941, Konrad Zuse designed the Z3 machine, an electromechanic computer, the first electrically driven to use the binary system. Two years later in 1943 was built Colossus which was used during World War II to decipher communications between German officers using the Lorenz cipher. During the same period IBM developed the Harvard Mark I which was the first to be fully automatic. It was used in the Manhattan project to run simulations in the development of the first atomic bomb [4]. In 1948, ENIAC was the first computer designed to be Turing complete, it used vacuum tubes. The same year, the Small-Scale Experimental Machine (SSEM) was the first to be based on the von Neumann architecture which uses a single memory to store the instructions and the data [5].

During the 1950s, transistors, which are much more smaller and more reliable, replaced vacuum tubes in the architectures. During this period, technological breakthrough such as the creation of the microcode and the implementation of the first high level language: Fortran, helped to spread the use of computers in scientific and commercial applications.

The integrated circuit, first produced by Texas Instruments in 1958, would soon be used in computers, for example in the Apollo guidance computer in 1963. One year later IBM announced the IBM 360, that was the first system to be based on integrated circuits. The smaller size and cheaper cost of the integrated circuits-based computer placed them as the new standard of computers.

In 1971, Intel released the 4004, the first commercial microprocessor, uniting all the elements of a processor into a single chip. This processor was slow and contained a relatively small number of transistors, but the evolution of the microprocessors would then follow the prediction of Gordon Moore: their complexity will double every year [6].

In 1976 was introduced the Cray 1, one of the first supercomputers to use vector processors in order to accelerate computations.

Since then, architectural evolution helped to build more efficient processors: Instruction pipelines allow instructions to be streamed and reordered, cache memories speed up memory access, branch predictors improve the pipeline, processor with multiple cores allow local parallelism.

In supercomputers, the number of processors used in parallel increased to thousands and new solutions like accelerators (GPGPU or Intel Xeon Phi) are developed to enhance performance.

To take advantage of these architectural developments, software libraries were released to give the user the possibility to perform efficient linear algebra computations on these architectures. Already with the IBM 360, IBM proposed in 1968 the Scientific Subroutine Package. In 1979, the Basic Linear Algebra Subprograms (BLAS) set of subroutines allowed to perform common linear algebra operations. The same year, LINPACK used BLAS to provide a software library able to perform numerical linear algebra operations on vector-computers. LAPACK appeared as an alternative in 1992, providing optimized routines for cache based architectures. LAPACK had different evolutions during the years, among them ScaLAPACK for distributed architectures, PLASMA for multicores, and MAGMA for hybrid architectures using accelerators like GPGPUs or Intel Xeon Phi.

In this thesis we propose solutions to use or improve some of the current public domain linear algebra libraries so that they exploit the possibilities of modern parallel architectures at their best. We implement different algorithms that are more adapted to some of these architectures to achieve better performance. We also propose methods to optimize memory access in the case of NUMA architectures.

This chapter presents the background of our work. We first review the main issues in solving dense linear systems and we introduce the main methods for solving these systems. We then present the LU factorization and its characteristics, showing the importance of numerical stability and presenting different methods of pivoting. We also present different existing block algorithms and parallel strategies for pivoting in the context of the LU decomposition, focusing on the Communication Avoiding LU factorization (CALU). Next we present the evolutions in parallel architectures and the recent trends in this domain.

In the last part of this chapter we present the development progress in dense numerical algebra libraries.

#### 1.2 Solving dense linear systems

Large dense linear systems are encountered in various scientific fields such as:

- **Electromagnetics:** when problems are solved using Boundary Integral Equations using the "Moment Methods" in the context of the Helmholtz equation. This arises for example in the military domain for stealth airplane technology.

- **Fluid mechanics:** also to solve Boundary Integral Equations but using the "Panel Methods" in the context of the Laplace equation. This is used to understand and model the flow of a fluid passing an object, with applications in aeronautics, construction, etc.

- Quantum mechanics: As expressed in [7]: "In quantum mechanical scattering, the goal is to predict the probability that a projectile will scatter off a target with some specific momentum and energy." In [8] they had to solve dense linear systems with 6500 unknowns and they foresee the need to solve systems with 100000 unknowns.

Dense linear systems are also encountered for example in tomography, for noise reduction or for supercomputer benchmarking [9]. Moreover, routines for dense linear systems are commonly used as kernels in more general methods for solving sparse linear systems using direct or iterative methods [10, 11, 12].

Solving these problems generally consists of solving a linear system of equations: Ax = b. Thus our goal is to solve such systems as efficiently and accurately as possible.

To solve such systems, there are two classes of methods: direct and iterative methods. The direct methods use a finite sequence of operations to solve the problem while the iterative methods use an initial guess of the result, and generate approximate solutions and tries to make the iterations converge. Iterative methods can be interesting if the system is large and sparse. In our work we are concerned with dense matrices and we focus on direct methods.

Direct methods generally involve the decomposition of matrices followed by the successive resolution of triangular systems. Different methods of decomposition exist such as QR factorization, Cholesky, LDL<sup>T</sup> or LU [13].

- **LU:** is used to solve general systems and decompose a matrix A in a product of a unit lower triangular matrix, L and an upper triangular matrix, U. It requires about  $2/3 \times n^3$  floating point operations (flops).

- **LDL**<sup>T</sup>: is used for symmetric matrices. A symmetric matrix A is decomposed as follows,  $A = LDL^T$  where L is a unit lower triangular matrix and D a diagonal (or block-diagonal) matrix. It requires about  $n^3/3$  flops.

- **Cholesky:** for symmetric positive definite matrices (i.e. all the eigenvalues of the matrix are positive). A is factored as  $A = GG^T$  with G a lower triangular matrix with positive diagonal entries. It requires about  $n^3/3$  flops.

**QR:** to solve full rank least square problems in the case of overdetermined systems (the system has more equations than unknowns). A m by n matrix A is factored as A = QR with Q being an m by m orthogonal matrix and R an m by n upper triangular matrix. It requires about  $2n^2(m-n/3)$  flops.

In the remainder, we focus on the LU decomposition.

#### 1.3 LU factorization

#### 1.3.1 Gaussian elimination

If A is square, dense and unstructured, the method usually chosen to solve Ax = b is Gaussian elimination. Gaussian elimination consists of a sequence of basic operations on the rows of the matrix to fill the coefficients under the diagonal with zeros making the matrix upper triangular, and thus allowing the system to be solved easily. The LU factorization is a modified form of Gaussian elimination where the matrix A is expressed as a product LU, with L a unit lower triangular matrix and U an upper triangular matrix.

Then the system is easy to solve by forward substitution for L and backward substitution for U:

$Ly = b, Ux = y \Rightarrow Ax = LUx = Ly = b$ . This requires  $\mathcal{O}(n^2)$  flops.

We compute L and U such as  $A = L \times U$  as in the following example:

$$A = \begin{pmatrix} a_{11} & a_{12} & a_{13} \\ a_{21} & a_{22} & a_{23} \\ a_{31} & a_{32} & a_{33} \end{pmatrix}, L = \begin{pmatrix} 1 & 0 & 0 \\ l_{21} & 1 & 0 \\ l_{31} & l_{32} & 1 \end{pmatrix} \text{ and } U = \begin{pmatrix} u_{11} & u_{12} & u_{13} \\ 0 & u_{22} & u_{23} \\ 0 & 0 & u_{33} \end{pmatrix}.$$

Algorithm 1 shows how the LU factorization can be performed in place which means that the input matrix A is overwritten by the output factors L and U.

#### **Algorithm 1** In place LU factorization without pivoting

```

Input: A is a n \times n matrix

1: for k \leftarrow 1 to n-1 do

for i \leftarrow k+1 to n do

2:

A(i,k) \leftarrow A(i,k)/A(k,k)

3:

end for

4:

for i \leftarrow k+1 to n do

5:

6:

for j \leftarrow k+1 to n do

A(i,j) \leftarrow A(i,j) - A(i,k) * A(k,j)

7:

end for

8:

end for

10: end for

```

#### 1.3.2 The issue of pivoting

With the method described previously, if a 0 is found on the diagonal of the matrix, a division by zero will occur and the factorization will fail. Also if elements of small magnitude are on the diagonal, entries on the triangular factors will grow significantly. Moreover the numerical precision is limited on a computer, when finite precision arithmetic is used. Consequently rounding errors are unavoidable. These errors due to limited precision will be propagated and amplified by the division by very small values. The larger systems are more prone to rounding errors.

The stability of the Gaussian elimination can be measured by the growth factor which measures how large the entries of the matrix become during the elimination steps comparing to the largest entries of the input matrix. The growth factor of a  $n \times n$  matrix A under Gaussian elimination is defined as:

$$g_n(A) = \frac{\max_{i,j,k} |a_{ij}^{(k)}|}{\max_{i,j} |a_{i,j}|},$$

where  $a_{ij}^{(k)}$  is the element of index (i,j) after the step number k of the elimination [14].

For this reason we move the largest element of the column on the diagonal by swapping rows. This method is called partial pivoting. It is also possible to swap rows and columns, using the largest element of the matrix (complete pivoting), or of the current line and column (rook pivoting), as the pivot. Other parallel pivoting strategies will be addressed later.

An alternative method is the threshold pivoting which consists in choosing any pivot among the column if this pivot's absolute value is larger than a predetermined threshold value chosen in [0, 1]. First introduced in the context of sparse matrix computations [15, Chapter 5.4], it can be used for dense matrices as shown in [16].

Even though pivoting increases the stability and requires no additional floating point operations, it involves irregular data movements due to the comparisons performed in the process of finding the pivot. If n is the size of the matrix, complete pivoting requires  $\mathcal{O}(n^3)$  comparisons, partial pivoting  $\mathcal{O}(n^2)$  comparisons and rook pivoting between  $\mathcal{O}(n^2)$  and  $\mathcal{O}(n^3)$ . Therefore, even if complete pivoting has the best stability with a growth factor bound of  $cn^{1/2}n^{1/4\log n}$  [17] comparing to rook pivoting  $(1.5n^{3/4\log n})$  [18] and partial pivoting  $(2^{n-1})$  [17], it will be time-consuming, due to the comparisons and data movements. The choice of the pivoting strategy is then the result of a compromise between the numerical stability and the performance.

#### 1.3.3 Partial pivoting

In the following, we consider partial pivoting, described in algorithm 2.

The growth factor upper bound is  $2^{n-1}$  can be reached for certain problems [19]. However, partial pivoting is stable in practice.

#### Algorithm 2 In place LU factorization with partial pivoting

```

Input: A is a n \times n matrix

1: for k \leftarrow 1 to n do

index \leftarrow k

2:

for i \leftarrow k+1 to n do

3:

if |A(i,k)| > |A(index,k)| then

4:

index \leftarrow i

5:

end if

6:

end for

7:

swap rows k and index

8:

for i \leftarrow k+1 to n do

9:

A(i,k) \leftarrow A(i,k)/A(k,k)

10:

end for

11.

for i \leftarrow k+1 to n do

12:

for j \leftarrow k+1 to n do

13:

A(i,j) \leftarrow A(i,j) - A(i,k) * A(k,j)

14:

end for

15:

16:

end for

17: end for

```

The decomposition is of the form PA = LU, where P is the permutation matrix corresponding to the row swaps performed during the factorization.

#### 1.3.4 Block LU factorization

To allow parallelism and a more optimal use of hierarchical memory, we can organize the LU factorization so that matrix multiplications become the dominant operations. For that we perform the factorization by block.

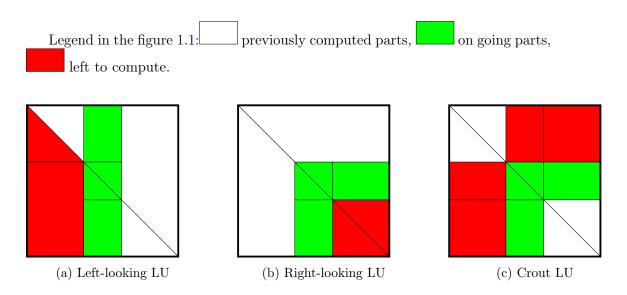

The three common algorithms for the block LU factorization are left-looking LU, right-looking LU and Crout LU.

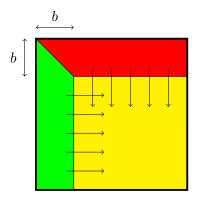

- The left-looking variant in Figure (1.1a) consists, for each step, in computing a block column using the previously computed ones.

- The right-looking variant in Figure (1.1b) computes for each step a block of rows and columns and then updates the trailing submatrix.

- Crout in Figure (1.1c) is a hybrid version in between left and right looking, a block row and a block column are computed on each step using the previously computed rows and columns.

These variants, due to the arrangements of the loops are also called i, j, k variants. More details can be found in [20].

Figure 1.1: Memory access patterns for variants of LU decomposition from [1]

#### 1.3.5 Right-looking block LU

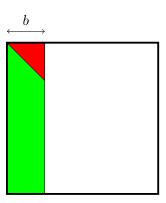

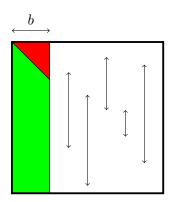

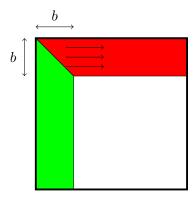

We describe here the right-looking block LU factorization.

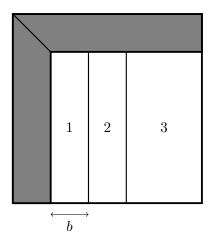

We compute the factorization of a matrix A of size  $m \times n$ . The matrix A is partitioned as follows ,

$$A = \begin{pmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{pmatrix},$$

where  $A_{11}$  is of size  $b \times b$ ,  $A_{21}$  is of size  $(m-b) \times b$ ,  $A_{12}$  is of size  $b \times (n-b)$  and  $A_{22}$  is of size  $(m-b) \times (n-b)$ .

The right looking LU factorization involves 4 steps:

Legend: original matrix, L matrix, U matrix, updated matrix,

1. The LU factorization of the panel  $\begin{pmatrix} A_{11} \\ A_{21} \end{pmatrix}$  is computed by applying a Gaussian elimination with partial pivoting (GEPP) to  $\begin{pmatrix} A_{11} \\ A_{21} \end{pmatrix}$  (the pivot selection is done on the whole panel)

2. We apply the permutation to the rest of the matrix:  $\begin{pmatrix} A_{12} \\ A_{22} \end{pmatrix}$

3. We compute  $U_{12}$  by solving the triangular linear system  $U_{12}=L_{11}^{-1}A_{12}$

4. We update  $A_{22}$ :  $A_{22} = A_{22} - L_{21}U_{12}$

5. We apply the same method to  $A_{22}$  (yellow part)

#### 1.3.6 Parallel pivoting strategies

The design of efficient parallel algorithms for the LU factorization requires other strategies of pivoting than the ones described in section 1.3.2.

A pivoting strategy called pairwise pivoting is studied in [21]. This method consists in selecting the largest element in the column pairwise to annihilate the smaller in magnitude values to triangularize the matrix. This method requires 2n-3 steps, in which a maximum of n/2 independent transformations are performed, allowing parallelism. The parallelism pattern can be represented by a reduction tree. The growth factor upper bound of this method is  $4^{n-1}$  but this pivoting strategy is shown to be stable in practice.

Derived from pairwise pivoting, incremental pivoting was introduced in [22]. This method divides the panel into tiles, factors the diagonal tile using partial pivoting and then eliminates the subdiagonal tiles pairwisely. Contrary to partial pivoting it does not factor a complete block column at a time. The matrix is divided into tiles and first the diagonal tile is factored using GEPP. Then this tile is combined with the tile below and factored again. A new factored diagonal tile is obtained and combined with the next tile below and the operation is repeated until the bottom of the matrix is reached. At each step the tiles on the right of the tile being factored with the diagonal tile are updated according to the operations performed on the panel tile. In this way the updates of the submatrix can be performed in parallel and in the same time as the panel factorization.

#### 1.3.6.1 Communication avoiding technique

On parallel architectures, searching the pivot in the block LU decomposition generates a large volume of data movements for which the communication time may be longer than the effective computing time, if the computation does not overlap the communication.

By reducing communication to its minimum, it is possible to achieve better performance despite a larger number of floating point operations. In [23], the authors proposed the so-called communication avoiding algorithms for some matrix factorizations such as LU and QR. We will focus more specifically on the CALU algorithm (Communication Avoiding LU) as described in [23, 24, 25, 26]. This algorithm proposes a new strategy for selecting the pivot. This algorithm minimizes communication while keeping the numerical stability of GEPP in practice [26].

The particularity of this algorithm is mainly the factorization of the panel, the other steps of the block decomposition are identical to the right looking LU (see 1.3.5). The factorization of the panel is performed using the TSLU (Tall Skinny LU) algorithm also described in [23, 24, 25, 26].

#### The TSLU algorithm

TSLU is a parallel algorithm that computes the LU factorization of a  $m \times b$  matrix with  $m \gg b$ . The matrix is distributed over P processors following a row-wise block cyclic distribution. The preprocessing step is performed as an all-reduction operation: a tree of GEPP factorizations.

Below are the steps of the algorithm:

- 1. Each thread performs a local LU factorization of the  $m/P \times b$  block-rows (b is the size of the block) that it owns. This is not performed in place so it requires an extra storage of size  $m \times b$  for the resulting matrix and a vector of size m for the permutation vector.

- 2. The threads copy the b pivot rows of their decomposition in the work matrix.

- 3. Half of the threads perform the same operation on the matrix composed by the two matrices built with the pivots lines found at the previous step, stacked one upon the other.

- 4. Whenever we reach the root of the reduction tree, we have the b pivot rows.

- 5. The permutation is applied to the original matrix to have the previously found pivot rows in first positions.

- 6. The Gaussian elimination without pivoting is performed on the  $m \times b$  columns.

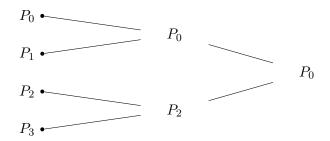

The binary tree representing the work done by the threads (here four) can be seen in Figure 1.2 and an example of the execution in Figure 1.3.

In this example with 4 threads, the matrix is distributed over,  $P_0$ ,  $P_1$ ,  $P_2$  and  $P_3$ . Each of them computes the GEPP on their  $m/4 \times b$  working matrix so that they can find the b pivot rows from this part of the matrix. They copy the pivot rows from the original matrix to the working matrix, then  $P_0$  computes GEPP (using LAPACK function) on a matrix composed of the pivot rows from  $P_0$  stacked on the pivot rows from  $P_1$ , this is done identically by  $P_2$ . At the final step of the preprocessing,  $P_0$  does the same computing on the 2b pivot rows resulting from the previous steps.

A more detailed version of the algorithm can be found in [25, 26].

Figure 1.2: Threads work

Figure 1.3: Example of execution with 4 threads

#### 1.3.7 Random Butterfly Transformation (RBT)

To avoid pivoting or extra computation that comes along as for example in CALU, it is possible to randomize the matrix and then factorize it using Gaussian Elimination without pivoting. By making the matrix "random enough" the probability that pivoting is not needed will be close to 1. The statistical properties for the stability of Gaussian elimination without pivoting have been studied in [27]. The method for randomizing has been described in [28, 29]. It consists in multiplying a matrix A as  $A_r = U^T AV$ , where U and V are recursive butterfly matrices. A butterfly matrix is a matrix of the form ,

$$B^{\langle n \rangle} = \frac{1}{\sqrt{2}} \begin{pmatrix} R_0 & R_1 \\ R_0 & -R_1 \end{pmatrix},$$

where n is the size of the matrix  $(n \ge 2)$  and  $R_0$  and  $R_1$  are two random diagonal and non singular  $n/2 \times n/2$  matrices. A recursive butterfly matrix of size n and depth d is defined recursively as,

$$W^{< n, d>} = \begin{pmatrix} B_1^{< n/2^{d-1}>} & & & \\ & \ddots & & \\ & & B_{2^{d-1}}^{< n/2^{d-1}>} \end{pmatrix} \times W^{< n, d-1>},$$

where  $W^{\langle n,1\rangle}=B^{\langle n\rangle}$  and the  $B_i^{\langle n/2^{d-1}\rangle}$  are random butterflies matrices, and  $B^{\langle n\rangle}$  is a butterfly matrix of size n. Then we can perform the LU factorization of  $A_r$  using Gaussian Elimination without pivoting. Explanations of how the random butterfly transformations change the growth factor can be found in [28]. Solving the general linear system follows these steps:

- 1. A randomized matrix  $A_r$  is computed:  $A_r = U^T A V$  where U and V are recursive random butterfly matrices.

- 2.  $A_r$  is decomposed into LU using Gaussian elimination without pivoting.

- 3. The system is solved using: $A_r y = U^T b$ .

- 4. The solution is x = Vy.

In [28] Parker uses recursive random butterfly of depth  $d = \log_2 n$  but in [30] Baboulin et al. showed that in practice a depth of 1 or 2 is enough if iterative refinement is added. Iterative refinement is a method that allows to improve a computed solution of a linear system. If we try to solve a system Ax = b, we obtain a computed solution  $\hat{x}$ . Then the process consists of the 3 following steps (see e.g. [31]):

- 1. Compute  $r = b A\hat{x}$ .

- 2. Solve Ad = r.

#### 3. Update $y = \hat{x} + d$ .

The process is repeated with  $\hat{x}$  replaced by y until the accuracy of the computed solution is satisfactory.

Due to their particular sparse structure, the butterfly matrices  $B^{< n>}$  can be stored in a vector of size 2n and the recursive butterfly matrices  $W^{< n,d>}$  can be stored in a matrix of size  $n \times d$ . With this structure the computational cost to apply the multiplicative transformation  $(U^TAV)$  is  $4dn^2$  flops when U and V are recursive random butterfly matrices of depth d. In the case of PRBT of depth 1 or 2 the computational cost will be respectively  $4n^2$  and  $8n^2$  [30]. When n is not a multiple of  $2^d$ , we "augment" the matrix A with additional 1s on the diagonal.

Some preliminary results in [30] using CPU to perform the randomization and an hybrid CPU/GPU code to perform the LU factorization without pivoting showed promising result with a 20% gain of performance for matrices of size varying from 4000 to 8000.

#### 1.4 Parallel architectures

In the domain of modern high performance computing (HPC), parallelism is a critical issue. In this section we present an overview of the current architectural solutions developed for HPC.

Since 1945 the Von Neumann architecture is used as a model for building computers. This model subdivides a processing unit into four parts: an arithmetic logic unit, a control unit, a memory which contains data and instructions, and input/output devices [5]. The separation of these elements allows to exploit different types of parallelism. The pipeline was one of the first step toward parallel machines. An early example of pipelined computer is the UNIVAC I (1951) which was able to overlap program execution with some I/O activities. Heavily pipelined processors started with the IBM system/360 Model 91, which was one of the first to use a hierarchy of pipelines [32]. Supercomputers from the 70's to the 90's were mostly designed with vector processors (e.g., the Cray platforms). Different types of parallel architectures exist. The Flynn taxonomy proposes four categories of architectures [33]:

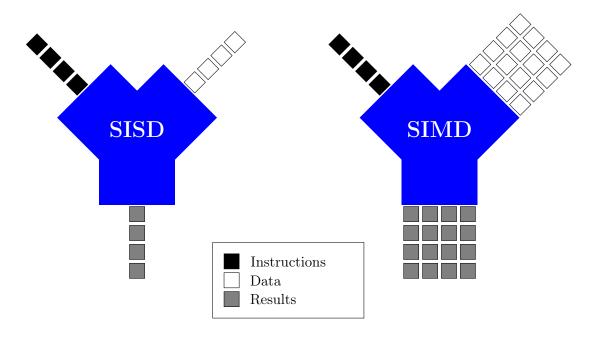

**SISD:** (Single Instruction, Single Data) where a datum is processed by a single process unit.

**MISD:** (Multiple Instruction, Single Data) where a single datum is processed by multiple process units at the same time.

**SIMD:** (Single Instruction, Multiple Data) where multiple data are processed by a single process unit.

**MIMD:** (Multiple instruction, Multiple Data) where multiple data are processed by multiple process units.

The MIMD model is also completed by Johnson [34] to differentiate the shared memory and distributed memory systems. In the following, we present the architectural components that we used during this PhD thesis.

#### 1.4.1 Distributed memory systems

Many of the current supercomputers are based on distributed memory systems. A distributed memory system consists of multiple independent nodes connected by a given network. Each node has its own private memory and autonomous computational capabilities. The nodes connected together form a cluster. The nodes exchange data by passing messages between processors using the network. Each node can be composed of multiple CPUs and contains accelerators.

#### 1.4.2 SIMD extensions

Single instruction multiple data (SIMD) extensions also called multimedia extensions were introduced in the processors in the late 90's. They provide special registers that can store multiple data. Then instructions can be applied to these registers,

Figure 1.4: Principle of the SIMD extensions.

processing each element of data inside a register simultaneously, which creates parallelism. Figure 1.4 shows the principle of the SIMD extensions, when compared to the SISD model.

SIMD instructions were first used in vector supercomputers, which could apply a single instruction to a vector of data but one word at a time. In 1994, Hewlett-Packard introduced the Multimedia Acceleration eXtensions (MAX) for the PARISC instruction set [35] and Sun Microsystems the Visual Instruction Set (VIS) as an extention for the SPARC V9 instruction set [36]. They paved the way for other companies to design their own extensions like Intel with the MMX extension [37] and Motorola with Altivec [38]. MMX can only process integers and uses the float registers to store the values, not allowing to use the SIMD extensions in parallel with scalar computation. Intel released the Streaming SIMD Extensions (SSE) in 1999 for the Pentium III to overcome these limitations. Since then, manufacturers proposed bigger and bigger registers and a larger set of instructions for their SIMD extensions. For example, today's Intel Xeon Phi coprocessor uses AVX-512 that can process 8 double-precision or 16 single-precision floating-point numbers at the same time.

In the domain of dense linear algebra, exploiting the parallelism offered by the SIMD extensions is critical to obtain optimal performance. Most basic operations on matrices or vectors exist in vectorized versions in different implementations of the BLAS libraries such as Intel MKL [39] (more details on these libraries will be given in Section 1.5).

In our work, we used SIMD low level instructions to implement some random-

ization techniques as it will be detailed in Chapter 3.

#### 1.4.3 Multicore processors

On single core processors, manufacturers have developed architectural optimizations such as providing more cache memory, instruction set pipelines and SIMD extensions. The other way to improve the performance of a processor is to increase its frequency. Increasing the frequency is very advantageous for the user because it improves the performance of the programs executed proportionally to the frequency raise. On the other side, for the manufacturer, increasing the frequency rapidly becomes a problem because of the heat generation and the power consumption. The power consumed by a CPU is  $P = CV^2f$ , with C being the capacitance, V the voltage and f the frequency [40]. The power consumed is proportional to the frequency and the more power is consumed the more thermal power will be produced because of power leakage. The solution favored by manufacturers to continue to improve processor performance without increasing the processor frequency was to introduce multicore processors [41].

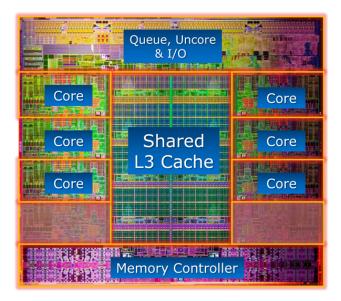

IBM developed the POWER4 processor in 2001, the first "on chip" multicore processor. It contains two cores at 1GHz and a shared L2 cache memory [42]. It was followed by SUN and HP releasing respectively the UltraSPARC IV and the PA-8800, both using two cores. AMD and Intel produced the first x86 multiprocessors in 2006 with the AMD Opteron and the Intel Core architectures. Since then, "multicore processor" has become a standard for desktops, servers or mobile platforms. On the desktop market AMD provided 8 core processors working at a frequency up to 4.7 GHz (AMD FX 9590), Intel with the I7-4960X (similar to the architecture depicted in Figure 1.5) provides a 6 core (12 threads with hyper-threading) processor working at up to 4 GHz. On the server side, the AMD Opteron 6386SE provides 16 cores at 2.8 GHz and the Intel Xeon E7-8890v2 15 cores (30 threads) at 2.8 GHz also. Even current smartphones contain processors like the Snapdragon 800 by Qualcomm containing 4 cores based on the ARM V7 architecture up to 2.5 GHz.

Apart from the architecture of the cores used, a multicore processor can be described by [43]:

- The number of processor cores on the chip,

- The number of levels of cache memory,

- The amount of cache memory shared.

#### 1.4.4 Non Uniform Memory Access (NUMA) architecture

Since 1968, computers have been build with multiple processors to perform parallel processing [44]. These machines called symmetric multiprocessor systems (SMP) are composed of multiple identical processors and a single shared main memory. These

<sup>&</sup>lt;sup>1</sup>Picture from www.anandtech.com

Figure 1.5: A Sandy bridge E die<sup>1</sup>

architectures are also referred to as Uniform Memory Access (UMA) architectures. The number of processors in a SMP system is limited, and the memory access is serialized, creating concurrency over the memory bus. The cache coherency mechanisms also send signals on the bus, which increases the traffic. At some point, the memory bus congestion becomes an issue for the performance [45]. A solution to this problem is the use of distributed memory clusters. However distributed memory programming creates constraints for the developer who has to manage data transfers explicitly. Also the granularity of the memory distributed between the different nodes degrades the performance.

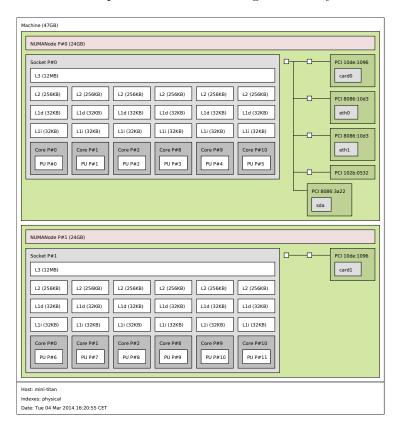

Another solution was developed during the 90s to overcome the scalability limits of SMPs: Non Uniform Memory Access (NUMA) or cache coherent NUMA (ccNUMA) architectures as most of today's systems maintain cache coherency. CcNUMA systems are generally composed of several multicore processors and their memory banks (considered as multiple SMPs used as NUMA nodes). Each processor core is able to access any memory part. The cost of the memory access will be different, depending on the location of the data requested, but the whole memory is shared seamlessly for the developer, like for SMP architectures. This is supported by the Operating System (OS) which provides a virtual address space to the program. Figure 1.6 shows the topology of a NUMA system composed of two 6 core multiprocessors and their dedicated memory, forming two NUMA nodes.

CcNUMA architectures offer a better scalability than SMP systems and do not require the user to use message passing tools to explicitly distribute the data as it would be the case when using clusters. However, to achieve good scalability, parallel programs on ccNUMA systems should make good use of the cache memory to minimize memory access and ensure a good data locality (the data computed by

a thread on a core are in a local bank of memory inside the same NUMA node) in order to avoid remote access [43].

Performing efficiently dense linear algebra computations on ccNUMA systems requires to take into account the locality of the data and the memory access pattern of the algorithms. In Chapter 4, we will introduce some methods to efficiently use NUMA architectures on top of the dense linear algebra library MAGMA.

Figure 1.6: Topology of a computer with 2 NUMA nodes.

## 1.4.5 General Purpose Computation on Graphics Processing Units (GPGPU)

The graphics processing units (GPU) are specialized electronic circuits designed to create or accelerate the generation of images to be displayed. Before the 2000's, GPUs were only used to compute or accelerate the computation of 2D and 3D pictures. In 2001, Larsen developed one of the first example of non-graphical computation on a GPU with a matrix-matrix product [46] using the 8-bits integer texture maps. In 2003, the introduction of 32-bits floating-point values allowed not only a real progress in graphical processing but also in matrix computations on GPUs [47]. In 2005, Galoppo and al. developed an efficient LU factorization on GPU outperforming the optimized CPU implementations at that time. This was performed

using the languages and methods initially designed for graphics processing. In 2007, Nvidia released the Compute Unified Device Architecture (CUDA) programming platform [48] providing a virtual instruction set, allowing the development of general purpose applications without using the tools and languages designed for graphics processing only.

There are other GPGPU solutions such as DirectCompute [49], specific to Microsoft Windows, released in 2008 by Microsoft as a part of DirectX 11, and OpenCL [50] a framework maintained by the Khronos Group<sup>2</sup> consortium. OpenCL is designed to program parallel heterogeneous systems mostly CPUs and GPUs. It has also the advantage to work on GPUs other than Nvidia's ones (e.g., ATI).

Figure 1.7: Nvidia Tesla K40 GPU <sup>3</sup>

GPGPU has become a common occurrence in HPC and is often used in supercomputer architectures. GPGPUs offer a big computational capacity at a low cost and a good energetic efficiency. Out of the ten most powerful supercomputers in the latest TOP500 [51] ranking (November 2014), three use GPGPU accelerators. Today's Nvidia Tesla GPGPU Kepler K40 (showed in Figure 1.7) offers a theoretical performance of 4290 Gflop/s in single precision and 1430 Gflop/s in double precision.

The drawback of GPGPUs comes from their hybrid programming model that does not allow as much efficiency as CPU-only architectures due to its SIMD-only nature and the PCI-Express bandwidth limitations. As an example, in the LINPACK benchmark [52], the Titan supercomputer<sup>4</sup> using hybrid CPUs/GPUs architecture achieves 17590 Tflop/s out of 27112.5 Tflop/s, the theoretical peak performance corresponding to an efficiency close to 65%. While the Sequoia supercomputer<sup>5</sup>

<sup>&</sup>lt;sup>2</sup>www.khronos.org

<sup>&</sup>lt;sup>3</sup>Picture from www.nvidia.com

<sup>4</sup>www.olcf.ornl.gov/titan/

<sup>&</sup>lt;sup>5</sup>http://computation.llnl.gov/computers/sequoia

(using only CPUs) achieves 17173.2 Tflop/s out of 20132.7 Tflop/s (around 85% efficiency).

Their highly parallel architecture model makes GPGPUs a suitable solution for matrix computations and dense linear algebra programs. However, programming efficiently on GPU-based architectures is a critical challenge for high performance computing. In this thesis we showed some solutions to efficiently solve dense linear systems, using GPGPUs as accelerators.

#### 1.4.6 Intel Xeon Phi accelerators

In 2010 Intel announced their Many Integrated Core Architecture (Intel MIC) a highly parallel coprocessor architecture consisting of several x86 processor-cores and it's own GDDR5 integrated memory. The first prototype board called *Knights Ferry* consisted of 32 cores with 2GB of GDDR5 memory. In 2012 Intel released the *Knights Corner* product line branded as "Xeon Phi" [53].

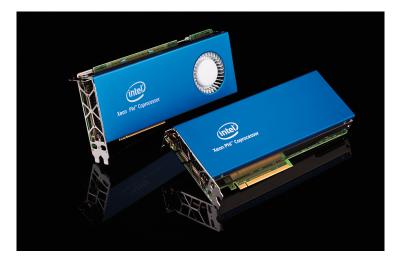

The current Xeon Phi 7120 (like the ones in Figure 1.8) posses 61 cores with four threads per core, running at 1.238 GHz. It has 16 GB of GDDR5 memory on 16 channels for a maximum bandwidth of 352 GB/s. Each core has 512 KB of Level 2 cache memory for a total of 30.5 MB of cache memory. The cornerstone of the Xeon Phi performance is the Vector Processing Units (VPU) of each core, using 512 bits wide SIMD registers allowing to perform 16 single-precision (SP) or 8 double-precision (DP) operations per cycle. The SIMD instruction set also includes Fused Multiply-Add (FMA) allowing to perform 32 SP or 16 DP operations per cycle [54].

Using the FMA instructions, the peak performance of the Xeon Phi 7120 can be computed as:

Clock Frequency  $\times$  Number of cores  $\times$  size of the lanes  $\times$  2(FMA) Flops

We have then 1064.8 Gflop/s in DP and 2129.6 Gflop/s in SP [55].

In November 2014, two out of the ten most powerful supercomputers were using Intel Xeon Phi accelerators, including the number 1 of the TOP500 ranking, Tianhe-2 that uses 48000 Xeon Phi coprocessors and achieves a performance of 33862.7 Tflop/s out of a theoretical peak performance of 54902.4 Tflop/s (around 62% efficiency).

Multiple tools can be used to program the Intel Xeon Phi with efficiency: OpenMP can be used to lever the parallelism between threads, the Intel compiler can perform some simple auto vectorizations, and preprocessor directives can be used to handle the hybrid computing issues such as the memory transfers etc. Nevertheless, for advanced programs with non trivial parallelism, achieving high performance with the Xeon Phi can be challenging. In practical cases, advanced low level optimizations such as hand-written SIMD code are required [56].

The combination of wide SIMD registers and a high level of shared memory core-based parallelism allows the Intel Xeon Phi to perform dense linear algebra computation with a high level of performance. To achieve such a level of performance the implementation must take advantage of these architectural features. Like for

the GPGPU, in this thesis we provide an efficient dense linear solver using the Intel Xeon Phi as an accelerator.

Figure 1.8: Intel Xeon Phi Coprocessors  $^6$

<sup>&</sup>lt;sup>6</sup>Picture from www.intel.com

#### 1.5 Numerical linear algebra libraries for dense matrices

The evolution of computer architectures has been followed by the software libraries. A different architecture requires a different implementation to be able to perform at the best of the capabilities of the machine. In dense linear algebra, the computational efficiency is a major challenge. Therefore an optimized implementation of the programs is essential.

Before the 70s, the optimized computational routines were directly coded in machine code. In 1964, Sweeney [57] collected statistics about the floating-point operations in various programs, in order to determine what kind of operations were mostly used [31].

The most usual operations were then included in black box libraries, offering the programmer optimized functions for different tasks such as matrix and vector operations (copies, swaps, rotations, etc).

#### 1.5.1 The historical libraries

In the mid 60s, IBM distributed the Scientific Subroutine Package [58], a collection of FORTRAN Subroutines optimized for the IBM System/360 machine. In 1974, Garbow published EISPACK [59], a package of FORTRAN subroutines to compute eigenvalues and eigenvectors of matrices. The Basic Linear Algebra Subprograms (BLAS) package was first the result of a collaborative project of the ACM-SIGNUM committee carried between 1973 and 1977 [60]. Based on a proposal made in 1973 [61].

The LINPACK library proposed, in 1979 a set of subroutines designed for the supercomputers of the 70s and 80s, mostly based on vector processors, to solve linear equations and linear least-square problems [62]. LINPACK used BLAS for the basic matrix manipulations. The LINPACK user's manual included a benchmark. It used a LU factorization with partial pivoting to solve a problem of size 100, allowing users to estimate the performance of their memory and processors. This size of the test and its implementation has evolved but is still in use today. It is known as High Performance LINPACK (HPL) [52, 63] and allows to establish the ranking of the most powerfull supercompters referred to as the TOP500 [51].

The first version of BLAS (Level 1 BLAS) implemented scalar-vector and vector-vector operations. BLAS2 (Level 2 BLAS) was developed in 1988 as an extension to BLAS1 to take advantage of the capabilities of vector processors [64, 65]. BLAS2 allows to perform matrix-vector operations.

In 1990 BLAS3 [66, 67] added another extension to be "cache friendly". This extention takes into account the memory hierarchy of the new computers (global memory, cache memories, vector registers etc). It implemented matrix-matrix operations such as matrix products or solving triangular systems of equations.

Released in February 1992, LAPACK [68] supersedes LINPACK and EISPACK and achieves better performance. LAPACK focuses on solving: systems of linear equations, linear least squares problems, eigenvalue problems and singular value

problems. To perform these operations it also implements the associated computation such as matrix factorizations (LU, QR, LDLT, Cholesky etc) or the estimation of condition numbers. LAPACK uses BLAS routines as much as possible to perform all the matrix, vector, scalar computation. Therefore the performance of the LAPACK libraries depends on the implementation of the BLAS used.

Most of the numerical linear algebra libraries developed afterwards are based on BLAS and LAPACK, offering different implementations of the same routines and operations.

## 1.5.2 Parallel implementations

Some vendor libraries such as ACML [69] for AMD processors, MKL [39] for Intel processors and ESSL [70] for IBM provide optimized implementations of BLAS and LAPACK for their processors. These optimizations include multithreaded (for the multicore processors) and vectorized (for the SIMD extensions) functions.

Open source projects also exist such as ATLAS [71], Goto BLAS [72] or Open-Blas [73]. ATLAS uses a tuning step during its installation to determine the best parameters for the kernels, with respect to the target architecture. GotoBLAS possesses a collection of hand written assembly kernels optimized for different architectures and uses vectorization and multithreading. OpenBLAS is based on GotoBLAS2 and proposes optimizations for more recent architectures since the development of GotoBLAS stopped.

For GPUs, NVIDIA proposes CuBLAS [74], an implementation of BLAS on top of the NVIDIA CUDA runtime, and EM Photonics, their CULA [75] solution as a CUDA implementation of LAPACK.

ScaLAPACK [76] (Scalable LAPACK) is an implementation of LAPACK for distributed architectures. It is based on different libraries. BLAS and LAPACK for the computation on each node, Basic Linear Algebra Communication Subprograms (BLACS) for the communication tasks. BLACS uses MPI for communication between the nodes. ScaLAPACK uses block-partitioned algorithms for the computation and two-dimensional block-cyclic distribution for the storage of the matrices.

Solutions using different programming approaches exist, such as the Formal Linear Algebra Methods Environment (FLAME) [77] offering a more user-friendly Application Program Interface (API) to represent the algorithms using algorithmic skeletons. The contributors also developed the BLAS counterpart BLIS [78] using the same approach.

The Parallel Linear Algebra Software for Multicore Architectures (PLASMA) is a software library designed to be efficient on homogeneous multicore processors and multi-socket systems of multicore processors. PLASMA [79] achieves a much greater efficiency than LAPACK but does not support band matrices and does not solve eigenvalue and singular value problems. It does not replace ScaLAPACK since it does not support distributed architectures.

PLASMA uses BLAS kernels for its internal computation, so an optimized BLAS implementation is required to achieve good performance. PLASMA implementation

is based on tiled algorithms. The idea is to divide the matrices into small enough square tiles so that a tile fits into the cache memory of one core. This method minimizes the number of cache misses, improving the performance. To make a tile to be stored in the cache memory efficiently, each tile has to occupy a contiguous memory region. We note that the storage used in PLASMA is different from LAPACK in which the matrices are stored column wise. Here a tile layout is used where each tile is continuously laid out in memory.

Another principle of PLASMA is related to the dynamic task scheduling. The scheduler called QUARK [80] (QUeueing And Runtime for Kernels) uses task graphs or Direct Acyclic Graphs (DAG), which are generated and explored at runtime.

## 1.5.3 The MAGMA Library

Similarly to LAPACK, MAGMA<sup>7</sup> [81, 82, 83], is being build as a community effort, incorporating the newest developments in hybrid algorithms and scheduling, and aiming at minimizing synchronizations and communication in these algorithms. The goal of these efforts is to redesign the dense linear algebra algorithms in LAPACK to fully exploit the power of current heterogeneous systems of multi/manycore CPUs and accelerators, and deliver the shortest possible time to an accurate solution within given energy constraints. Indeed, the algorithms included so far in MAGMA 1.6 manage to overcome bottlenecks associated with just multicore or GPUs, to significantly outperform corresponding packages for any of these components taken separately. MAGMA's one-sided factorizations for example on a single Fermi GPU (and a basic CPU host) can outperform state-of-the-art CPU libraries on high-end multi-socket, multicore nodes (e.g., using up to 48 modern cores). The MAGMA library exists in three versions: one for Nvidia GPUs using CUDA, one using OpenCL and one dedicated to Intel Xeon Phi accelerators.

More details about the MAGMA library will be given in Chapters 2 and 3. In this thesis, we used MAGMA as a framework to develop new solvers. Some of these solvers have been included in the latest release of the GPU and Intel Xeon Phi versions of MAGMA.

## 1.6 Conclusion of Chapter 1

In this chapter, we discussed the different methods for solving dense linear systems of equations, and focused on the dense solvers based on the LU factorization. We addressed the issue of pivoting in Gaussian elimination and described existing pivoting strategies to improve the stability of the LU algorithm.

We also discussed the architectures used in high performance computing and their challenging exploitation for the programmer, due to the different types of parallelism and programming paradigms.

<sup>&</sup>lt;sup>7</sup>Matrix Algebra on GPU and Multicore Architectures, http://icl.cs.utk.edu/magma/

We described the evolution of the numerical libraries used to solve dense linear systems, and showed the adaptations performed to offer the best performance as possible, depending on the targeted architectures.

In the next chapter we present our contributions in designing and implementing different algorithms to perform LU factorization on hybrid architectures using CPUs and GPUs. We also describe the behavior of the resulting routines in terms of performance and accuracy.

## Hybrid CPU/GPU algorithms for LU factorization

## Contents

| L |

|---|

| L |

| 3 |

| } |

| 5 |

| 3 |

| 3 |

| 3 |

| ) |

| } |

| 3 |

| 7 |

| 3 |

## 2.1 Dense linear algebra on accelerated multicore machines

There has been several main changes in the development of dense linear algebra libraries over the years. These changes have always been triggered by major hardware developments. For example, LINPACK [62] in the 70's targeted the vector machines at the time for which cache reuse was not essential, and as a result LINPACK had relied on just Level 1 BLAS. In the 80's LINPACK had to be rewritten, leading to LAPACK [68], that would rely on Level 3 BLAS for cache based machines. In the 90's it was extended to ScaLAPACK [76] for parallel platforms, relying on the PBLAS [84] message passing. Now, in the 00's, with the explosion in parallelism and heterogeneity as well as the ever increasing data-communication costs, the old libraries had to be redesigned once again. An example of these new generation libraries is the MAGMA library [85, 86, 82] (see Section 1.5.3) that has been designed from 2008 to address heterogeneous parallel architectures based on accelerators.

In parallel to the development of hybrid algorithms, there has been a number of new developments related to minimizing communication in one-sided factorizations (e.g. [87]). Such improvements have become essential due to the increasing gap between communication and computation costs.

For the linear system solvers on current multicore or GPU architectures, a bottleneck in terms of communication cost and parallelism comes from the pivoting, a technique used to prevent divisions by too-small numbers in the Gaussian Elimination (GE) process (see Sections 1.3.2 and 1.3.3). The commonly used method of Gaussian Elimination with partial pivoting (GEPP) is implemented in current linear algebra libraries for solving square linear systems Ax = b resulting in very stable algorithms (see 2). These systems are in general solved using the well-known LU factorization that decomposes the input matrix A into the product  $L \times U$ , where L is a lower triangular matrix and U is an upper triangular matrix. Current libraries like LAPACK implement GE using a block algorithm, which factors the input matrix by iterating over its blocks of columns (panels), as described in Section 1.3.5. Pivoting not only requires communication (or synchronization in a shared memory environment), but it also limits the exploitation of asynchronicity between block operations. This is because the update of the trailing submatrix can be performed only when the panel factorization is completed. We can find in [30] an evaluation of communication overhead due to partial pivoting using MAGMA on a given CPU/GPU architecture. This cost can represent on some hybrid architectures up to 40% of the global factorization time, depending on the matrix size. Communication cost of GEPP is asymptotically larger than the lower bounds on communication [24]. Other classical pivoting strategies can be used (see Section 1.3.2), but they always require between  $\mathcal{O}(n^2)$  and  $\mathcal{O}(n^3)$  comparisons to search for the pivot. In this chapter, we consider two alternative strategies to these pivoting techniques, that have the property of reducing communication in the LU factorization while providing a satisfactory accuracy.

The first alternative, already described in Section 1.3.6.1, is tournament pivoting. It was introduced in the context of CALU, a communication-avoiding LU factorization algorithm [26]. It has been shown in [24] that tournament pivoting is as stable as partial pivoting in practice and that CALU minimizes communications. With this strategy, the panel factorization, referred to as TSLU (Tall and Skinny LU), can be efficiently parallelized.

The second alternative is proposed in [30] where the communication overhead due to pivoting is completely removed by considering a randomization technique referred to as Random Butterfly Transformation (RBT) (see Section 1.3.7). More details on this method will be given in Chapter 3.

Note that, since in this approach we know in advance that we are not going to pivot, GENP that follows randomization is implemented as a very efficient fully BLAS 3 algorithm. Note also that when the initial matrix is randomized, we systematically add iterative refinement in the working precision for better stability, as indicated in [31, p. 232]. We show in this chapter that the usage of these techniques in the context of hybrid CPU/GPU architectures lets us to take advantage of each computational unit.