# Preparing depth imaging applications for Exascale challenges and impacts

Asma Farjallah

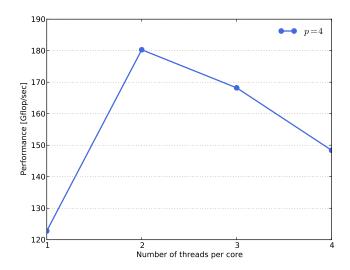

#### ▶ To cite this version:

Asma Farjallah. Preparing depth imaging applications for Exascale challenges and impacts. Performance [cs.PF]. Université de Versailles-Saint Quentin en Yvelines, 2014. English. NNT: 2014VERS0050 . tel-01165085

# HAL Id: tel-01165085 https://theses.hal.science/tel-01165085

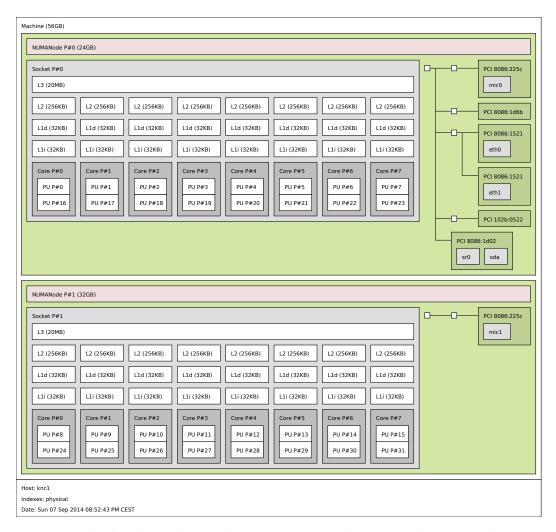

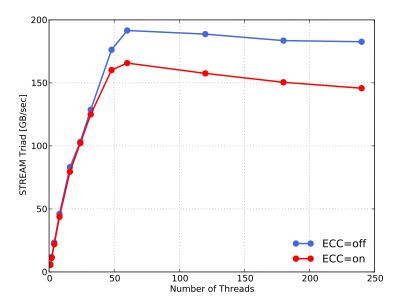

Submitted on 18 Jun 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Université de Versailles Saint-Quentin-en-Yvelines

# Preparing Depth Imaging Applications for Exascale Challenges and Impacts

# Étude de l'adéquation des machines Exascale pour les algorithmes implémentant la méthode du Reverse Time Migration

# **THÈSE**

présentée et soutenue publiquement le 16 Décembre 2014 pour l'obtention du

# Doctorat de l'université de Versailles Saint-Quentin-en-Yvelines (spécialité informatique)

par

Asma Farjallah

#### Composition du jury

Directeur de thèse : William Jalby - Professeur, Université de Versailles

Président : Nahid Emad - Professeur, Université de Versailles

Rapporteurs: François Bodin - Professeur, Université de Rennes 1

Jean-Luc Lamotte - Professeur, Université Pierre & Marie Curie

Examinateurs: Henri Calandra - Expert, Total E&P, USA

Philippe Thierry - Docteur, Intel, Paris

# Remerciements

Je tiens à remercier mon directeur de thèse, William Jalby, pour son accueil au laboratoire Exascale Computing Research et son aide tout au long de ma thèse. Je remercie également Henri Calandra pour m'avoir fait confiance et pour ses précieux conseils.

Je remercie du fond du cœur mes collègues et mes copains qui m'ont épaulé pendant ses quatre années. Eric et Sylvain, merci d'être toujours présents dans les pires et les meilleurs moments. Thomas et Marc, merci pour tout ce que vous m'avez appris et pour les longues discussions au tableau. Omar et Othman, merci pour vos encouragements et votre soutien pendant la préparation de la soutenance. Philippe, merci pour ta patience et tes conseils qui ne tarissent jamais. Issam, merci de toujours penser à moi.

A ma famille, j'offre cette thèse. Mon papa et ma maman, j'espère que cette thèse est à la hauteur de vos sacrifices et vos efforts sans lesquels je ne serais pas devenue celle que je suis. Je pense très fort à mes sœurs Emna et Eya et leur souhaite la réussite et le bonheur.

A l'élu de mon cœur, Wassim, j'offre cette thèse aussi. Merci d'être toujours là pour moi, pour m'encourager et m'aider. J'espère que la vie nous réserve que le bonheur et la joie de vivre.

## **Abstract**

As we are expecting Exascale systems for the 2018-2020 time frame, performance analysis and characterization of applications for new processor architectures and large scale systems are important tasks that permit to anticipate the required changes to efficiently exploit the future HPC systems. The objective is to assess the portability of the application and identify the key challenges for both the application and the architecture. This thesis focuses on seismic imaging applications used for modeling complex physical phenomena, in particular the depth imaging application called Reverse Time Migration (RTM). The study follows two main axes. The first one is FDTD, the computational core of RTM, the second one is the communication and IO of the full RTM application. A deep understanding of the interaction of these kernels with the underlying architecture is the key to predict the behavior of the overall application.

My first contribution consists in characterizing and modeling the performance of the FDTD kernel. I identify and explore the major tuning parameters influencing performance and the interaction between the architecture and the application.

The second contribution is an analysis to identify the challenges for a hybrid and heterogeneous implementation of FDTD for manycore architectures. We target Intel's first Xeon Phi co-processor, the Knights Corner. This architecture is an interesting proxy for our study since it contains some of the expected features of an Exascale system: concurrency and heterogeneity.

My third contribution is an extension of the performance analysis and modeling to the full RTM. This adds communications and IOs to the computation part. RTM is a data intensive application and requires the storage of intermediate values of the computational field resulting in expensive IO accesses.

My fourth contribution is the final measurement and model validation of my hybrid RTM implementation on a large system. This has been done on Stampede, a machine of the Texas Advanced Computing Center (TACC), which allow us to test the scalability up to 64 nodes each containing one 61-core Xeon Phi and two 8-core CPUs for a total close to 5000 heterogeneous cores.

The performance analysis and characterization study of RTM on a cluster hosting manycore architecture allow us to alleviate the hardware features that significantly impact the performance of the computational part. Furthermore, the modeling of the influence of the increasing concurrency and heterogeneity on the full RTM seismic imaging application is an important step to pave the way for the required code modernization and to pin-point the critical architectural bottlenecks

in the process for future Exascale systems co-design.

*Keywords.* Exascale systems, seismic imaging applications, co-design, modeling, performance characterization, Intel Knights Corner.

# **Contents**

| In | trodu | ıction  |                                            | vii  |

|----|-------|---------|--------------------------------------------|------|

| 1  | Mot   | ivation | ıs                                         | 1    |

|    | 1.1   | Exasca  | ale Challenges                             | . 1  |

|    |       | 1.1.1   | Hardware Challenges                        |      |

|    |       | 1.1.2   | Software Challenges                        |      |

|    |       | 1.1.3   | Algorithmic Challenges                     |      |

|    |       | 1.1.4   | Co-Design                                  |      |

|    |       | 1.1.5   | Previous Feasibility Studies               |      |

|    | 1.2   | Geopl   | hysical Applications                       |      |

|    |       | 1.2.1   | Seismic Imaging Applications               |      |

|    |       | 1.2.2   | Seismic Exploration Work Flow              |      |

|    |       | 1.2.3   | Challenges in Seismic Imaging Applications | . 19 |

| 2  | Seis  | mic M   | odeling                                    | 21   |

|    | 2.1   | Seism   | ic Waves                                   | . 21 |

|    |       | 2.1.1   | Body Waves                                 | . 21 |

|    |       | 2.1.2   | Surface Waves                              |      |

|    | 2.2   | Wave    | Equations                                  |      |

|    |       | 2.2.1   | Elastic Wave Equation                      |      |

|    |       | 2.2.2   | Acoustic Wave Equation                     |      |

|    | 2.3   | Nume    | erical Methods for Seismic Modeling        |      |

|    |       | 2.3.1   | Integral methods                           |      |

|    |       | 2.3.2   | Asymptotic methods                         | . 27 |

|    |       | 2.3.3   | Direct methods                             | . 27 |

|    | 2.4   | Appli   | cation to the Acoustic Wave Equation       | . 29 |

|    |       | 2.4.1   | Isotropic Media                            |      |

|    |       | 2.4.2   | Anisotropic media                          | . 31 |

|    |       | 2.4.3   | Stability Condition and Dispersion         | . 32 |

| 3  | Peri  | orman   | ce Study of FDTD Applications              | 33   |

|    | 3.1   |         | view of Performance Modeling Techniques    | . 33 |

|    |       | 3.1.1   | Analytical Models                          |      |

|    |       | 3.1.2   | Trace-based Models                         |      |

|    |       | 3.1.3   | Roofline Models                            |      |

|     | 3.2     | Performance Modeling of FDTD                              | . 36 |

|-----|---------|-----------------------------------------------------------|------|

|     |         | 3.2.1 FDTD Algorithm                                      |      |

|     |         | 3.2.2 Modeling Theoretical Peak Performance               |      |

|     | 3.3     | Performance Optimizations of FDTD                         |      |

|     |         | 3.3.1 NUMA-Awareness                                      |      |

|     |         | 3.3.2 Prefetching                                         |      |

|     |         | 3.3.3 Cache Optimizations                                 |      |

|     |         | 3.3.4 Z-order Curve                                       |      |

|     | 3.4     | ASK: Adaptive Sampling Kit                                |      |

|     |         | 3.4.1 ASK experimental setup                              |      |

|     |         | 3.4.2 Performance characterization of stencil computation |      |

| 4   | Men     | nory Bandwidth Cost Model for FDTD                        | 55   |

|     | 4.1     | Isotropic Kernel                                          | . 55 |

|     | 4.2     | Performance Model for Extra DRAM Traffic                  |      |

|     |         | 4.2.1 Data Reuse Histogram                                | . 58 |

|     |         | 4.2.2 Applying the Reuse Distance Histogram to FDTD       |      |

|     |         | 4.2.3 Updated Formulation of the Performance Model        |      |

| 5   | FDT     | TD Applications on Manycore Architectures                 | 67   |

|     | 5.1     | Intel Many Integrated Core Architecture                   |      |

|     |         | 5.1.1 Performance Gain Expectations                       | . 70 |

|     |         | 5.1.2 Programming Models on MIC                           | . 72 |

|     | 5.2     | Single-node Implementation of FDTD Applications           | . 72 |

|     |         | 5.2.1 FDTD Implementations Without Absorbing Conditions   |      |

| 6   | Rev     | erse Time Migration on Large Scale Systems                | 81   |

|     | 6.1     | Related Work on Reverse Time Migration                    | 81   |

|     |         | 6.1.1 State-of-the-art Implementations                    | . 82 |

|     |         | 6.1.2 Velocity Models                                     |      |

|     |         | 6.1.3 Snapshots and I/O Strategies                        |      |

|     | 6.2     | Performance Modeling of RTM                               | . 86 |

|     |         | 6.2.1 Computation Costs                                   |      |

|     |         | 6.2.2 Communication Costs                                 |      |

|     |         | 6.2.3 Snapshot Strategy Costs                             |      |

|     | 6.3     | Implementation of RTM for Multi-node of Many-Core         |      |

|     |         | 6.3.1 Test System                                         |      |

|     |         | 6.3.2 RTM Implementations                                 | . 94 |

| Co  | nclu    | sion and Future Work                                      | 99   |

| Bil | oliog   | raphy                                                     | 109  |

| Lis | st of l | Figures                                                   | 114  |

| Lis | st of A | Algorithms                                                | 115  |

| Contents |

|----------|

|          |

List of Tables 117

# Introduction

Given the expected changes affecting the HPC systems and the constraints that may tailor their conception, application scientists need to lead off studies defining the main changes affecting the development of their future applications. They also need to define the new challenges they aim to overcome thanks to the increasing compute capability of the Exascale machines. These upstream studies also concern the current applications in order to be sure that their porting on Exaflopic systems is relevant.

This thesis is a feasibility study of porting seismic imaging applications as Reverse Time Migration (RTM) to the Exascale. Co-design is the approach we rely on to predict the behavior of these applications and anticipate solutions to remedy to the expected hardware and software challenges in Exascale systems. Algorithms and numerical schemes may consequently change in order to response to these challenges. My contributions are the following:

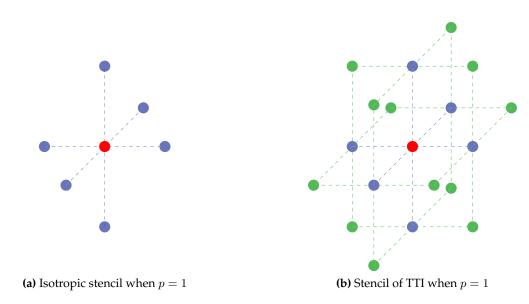

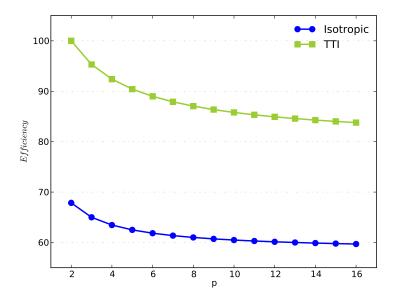

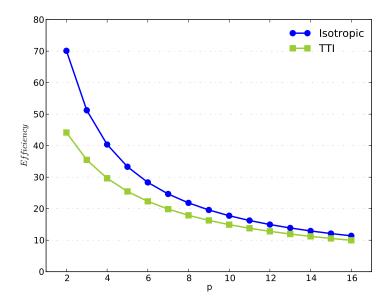

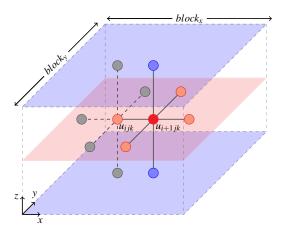

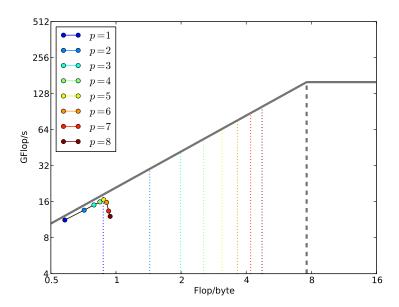

- Performance modeling and characterization of FDTD. We characterize the performance of finite-difference time-domain (FDTD) implementations widely used in seismic imaging applications like RTM since they represent their computational core. We consider two implementations. One in isotropic media as an introductory example and one in transverse anisotropic media tilted transverse isotropy (TTI) as it is commonly encountered in exploration campaigns. This study was made possible using analytical models, Roofline models and a sampling-based tool called Adaptive Sampling Kit (ASK).

- Memory bandwidth cost modeling. We demonstrate that the memory bandwidth has a great impact on the performance of the FDTD applications and we developed an analytical model predicting the DRAM traffic of these applications. This model can be used to predict performance on future Exascale systems.

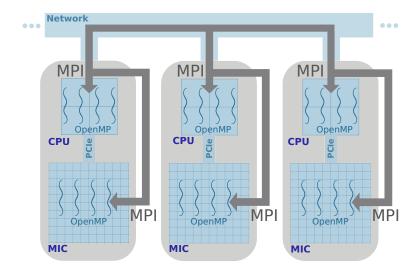

- **FDTD** on manycore architectures. We then focus on the Intel Many-Integrated Core (MIC) architecture as it introduces new hardware features compared to Nehalem and Sandy Bridge. This highly parallel architecture is representative of the manycore technology trend in Exascale. We study the impact of concurrency using native implementations of the FDTD kernels. For this particular architecture, we highlight the optimizations performed in terms of data access and alignment, vectorization and cache blocking.

- Exploring symmetric execution of RTM. We also developed symmetric implementations in order to highlight the impact of heterogeneity on these kernels. We use two programming models, MPI and OpenMP and perform static load balancing in order to reduce communications overhead.

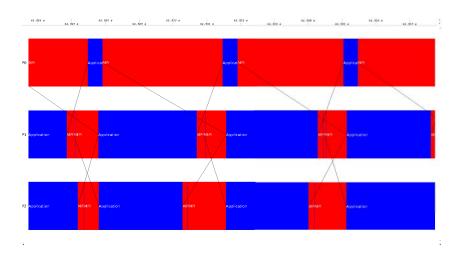

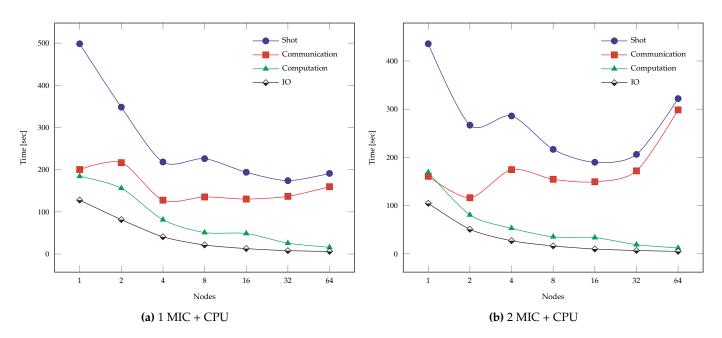

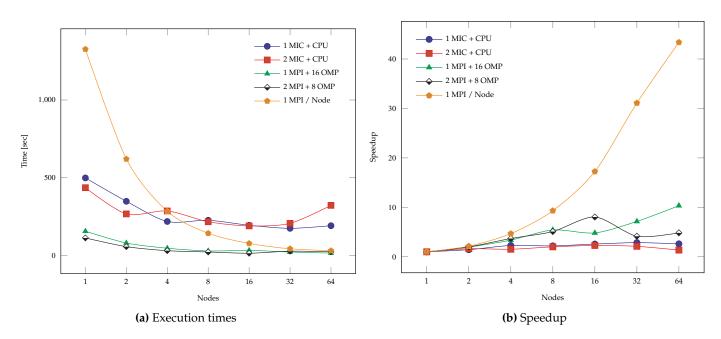

- **Performance analysis of RTM on large scale cluster.** We then focus on the multi-node implementation of the full application RTM. We develop analytical models that accounts for computation, communications and I/O as a prior study to porting on large scale systems. We make extrapolations based on these models for these systems and considering a simple velocity model a real velocity model. We also highlighted the bottlenecks, we encountered on Intel Xeon Phi nodes before the actual porting on a real system and we identified the impact of the small memory available on these co-processors and the need to over-decompose the compute grid which results in an overhead due to communications.

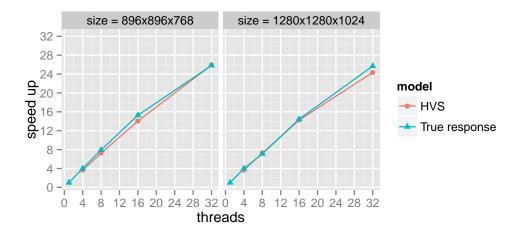

- Full scale experimental validation. We give a proof of concept of a hybrid heterogeneous implementation of RTM for cluster containing manycore architectures and give measurements on Stampede. We give strong scalability tests up to almost 16400 threads on 5000 heterogeneous core and compare with other implementations of RTM.

In the following paragraphs, we give the outline of the thesis.

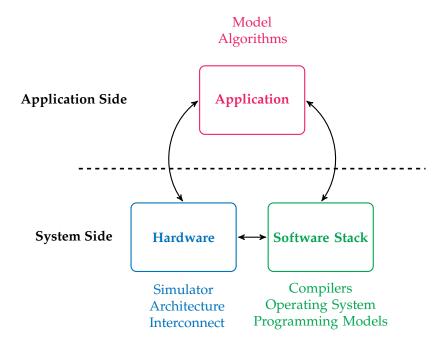

We start with an introductory chapter 1 where we describe the challenges brought along the Exascale Era. It concerns hardware, software and algorithms levels. Due to constraints on power consumption and cost in order to ensure the feasibility of an Exascale machine, we can expect revolutionary changes on the hardware. As a consequence and to guarantee the efficient use of the available resources, software and algorithms will also know great modifications. The way around study is also important. The existing algorithms and software stack may have constraints that need to be considered while building a new system. This mutual interaction between all levels constituting a high performance machine is called the co-design process and is considered as a key step towards the Exascale.

In the following chapter 2, we give an overview of the different numerical methods used in seismic imaging. These various methods respond to different needs in terms of the image resolution, time to solution, the available computational resources, the accuracy of the input models, etc. We provide in chapter 2 the equations governing wave propagation in isotropic and anisotropic media and the resulting approximations using the finite-difference time-domain (FDTD) approach.

The third chapter 3 is a deep insight on performance study and characterization. We give state-of-the-art performance modeling techniques and give a first model for FDTD applications considering theoretical peak performances. We then go through state-of-the-art optimizations approaches applied to FDTD and give

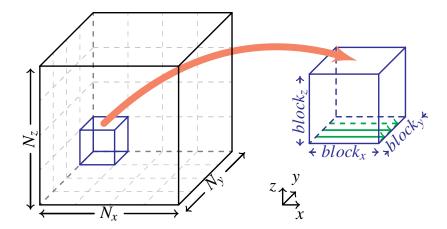

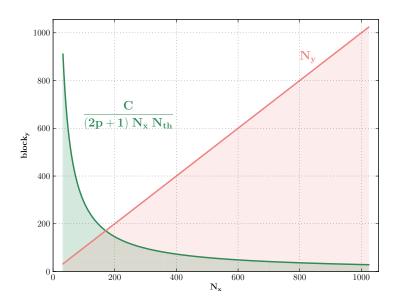

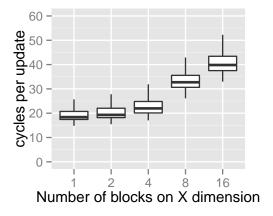

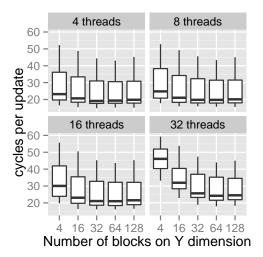

an analytical model for cache blocking based on previous works. We also use a sampling-based tool Adaptive Sampling Kit (ASK) in order to tune input and optimization parameters for FDTD. We consider the grid size, number of threads, cache blocks sizes, the order of the numerical scheme and the variant of the kernel where we apply some loop modifications or not.

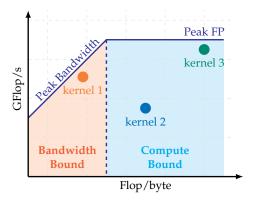

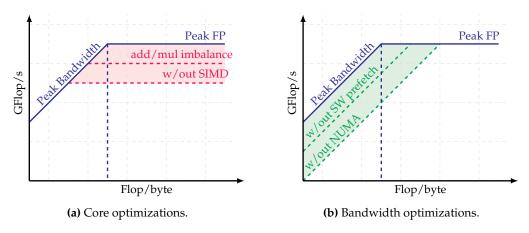

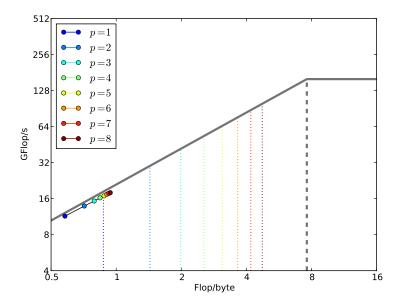

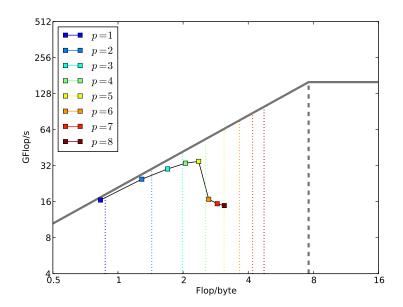

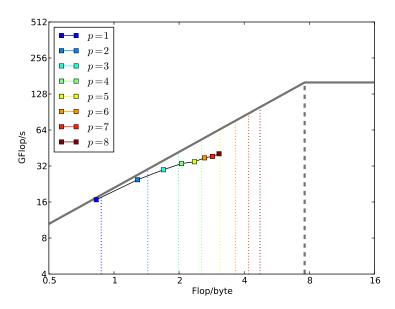

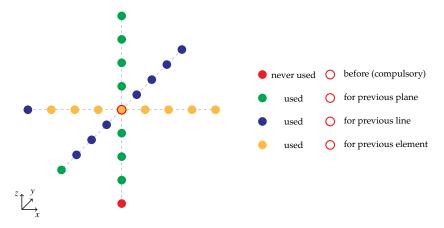

Chapter 4 applies the Roofline model introduced in chapter 3 to FDTD applications. Optimizations are also applied gradually on our applications and demonstrate their impact using the Roofline model. We implement a model of the DRAM traffic based on the data reuse histogram. We have an updated formulation for cache blocked versions since we had an over-estimation using the initial model in this particular case.

In chapter 5, we implement heterogeneous and hybrid version of the FDTD applications. We study the impact of the increasing parallelism and heterogeneity on these application through the use of Intel's Xeon Phi as representative of a future Exascale node.

The last chapter 6 is a feasibility study applied to an implementation of the Reverse Time Migration (RTM) application. We extend the performance model to communications and I/O for large scale systems. We also make prior modeling for a heterogeneous system containing Xeon Phi which enabled us to identify the expected bottlenecks on such systems. We then give measurements on the machine Stampede.

Finally, we conclude by summarizing the different contributions and lessons learned and we suggest some future work.

# **Motivations**

### 1.1 Exascale Challenges

After the race to reach the Petascale performance and the tremendous impact it had on the current HPC systems, scientists are facing another challenge with the Exascale machines expected for the 2018-2020 time-frame. An Exascale machine delivers  $10^{18}$  floating point operations per second, that is to say 1000x the performance of the most powerful machines currently available. We think that we have come to a turning point of computing technology evolution since merely augmenting the number of the computing units in a machine is unlikely to ensure an exaflopic performance. High performance computing (HPC) systems including the computing, storage, interconnect and cooling systems need to be reviewed for the Exascale era based on constraints fixed by the HPC community in order to ensure the feasibility of these future machines from an economical and environmental point of view. As a consequence, power and cost factors will be determining characteristics in building systems for the Exascale.

Challenges will affect all conception levels of a computing machine from hardware to software stack and applications. Hardware level includes the node architecture, interconnect and memory systems. The software stack concerns the operating systems, compilers, runtimes and programming models. Applications and algorithms need to evolve in order to leverage the new hardware features offered by the system. Resiliency and errors management are new constraints imposed by the increasing number of cores and limitations on power consumption. The current approaches of fault tolerance will be inefficient. More practical recovery mechanisms need to be developed.

Another aspect of the Exascale transition is the co-design process. HPC experts seem to agree that efficiently building such systems is conditioned by the collaborative effort conducted by the previously cited communities [Kogge et al., 2008; Ashby et al., 2010; Dongarra et al., 2011]. Interacting mutually will help architects to define new architectures that can be used efficiently by the applications and algorithms communities. On the other hand, applications and software stack need to be adapted to the constraints of the future hardware.

In the following paragraphs, we are going to detail all these challenges for the

hardware, software and application communities and will describe the co-design process.

#### 1.1.1 Hardware Challenges

We present the hardware constraints we need to handle when designing an Exascale machine. The role of these constraints is to guarantee a feasible and maintainable system. We start with the energy efficiency challenge since it is expected to drive the design of nodes, memory systems and interconnects. Resiliency is another aspect that we should consider in an Exascale system. The recovery time should be maintained the shortest possible in order to limit the system's unavailability.

Table 1.1 gives the characteristics of the top two machines, Tianhe-2 and Titan, according to the ranking in the Top500 <sup>1</sup> list of June 2014. In this 43rd edition of the Top500 project, Tianhe-2, installed by China's National University of Defense Technology, is the most powerful system. It uses Intel Ivy Bridge sockets and Intel Xeon Phi coprocessors. On the other hand, Titan, ranked second, is a Cray system installed in the Oak Ridge National Laboratory based on AMD Opteron Interlagos sockets and NVIDIA Tesla K20x GPUs. The features of these two machines and their performances summarized in table 1.1 will be used as a reference for the comparison with the potential Exascale machine as described in the upcoming paragraphs.

|                  | Titan          | Tianhe-2       |          |

|------------------|----------------|----------------|----------|

| System peak      | 27             | 54.9           | [PFlops] |

| HPL benchmark    | 17.59          | 33.86          | [PFlops] |

| System nodes     | 18,688         | 16,000         |          |

| System cores     | 560,640        | 3,120,000      |          |

| System memory    | 0.710          | 1.4            | [PByte]  |

| Node performance | 1.4            | 3.4            | [TFlops] |

| Node concurrency | 30             | 195            |          |

| Node memory      | 32/CPU + 6/K20 | 64/CPU + 8/Phi | [GByte]  |

| Power            | 8.2            | 17.8           | [MWatt]  |

|                  |                |                |          |

**Table 1.1** Characteristics of the top 2 machines according to the ranking of top500 in June 2014.

The values of power consumption in table 1.1 corresponds to the power needed by the processors, memory systems and interconnect only. Cooling is not included in these values. We also give the theoretical system peak performance and the effective peak performance measured by the High-Performance Linpack <sup>2</sup> (HPL) benchmark [Dongarra et al., 2003].

<sup>1</sup>www.top500.org

<sup>&</sup>lt;sup>2</sup>www.netlib.org/benchmark/hpl

#### 1.1.1.1 Power Management

For this paragraph, we consider the peak performance of Tianhe-2 and Titan machines measured by the HPL benchmark and their power consumption as reported in table 1.1. Exascale machines are expected to deliver a HPL peak performance equal to 10<sup>18</sup> floating-point operations per second. A linear extrapolation of the power consumption of Tianhe-2 and Titan estimates over 500 MW of power only for processors, memory and interconnect to attain exaflopic performance. This prohibitive value proves that extending the actual petaflopic systems while only adding computational resources is unlikely to deliver a maintainable system. For obvious economical and environmental reasons, minimizing the power consumption of Exascale systems is a major concern.

The US Defense Advanced Research Projects Agency (DARPA) launched in 2010 the Ubiquitous High Performance Computing (UHPC) program [DARPA, 2010; Carter et al., 2013]. It aims at building computing systems that respect an energy efficiency constraint fixed to 50 GFlop/Watt for 2018 time frame. Therefore, power consumption for Exascale systems will be equal to 20 MW without counting the cooling consumption. As recommended by [Shalf et al., 2011b; Kogge et al., 2008], exceeding this value is likely to hinder the system performance and it can have a great influence on the machine cost.

Given the limitation on power consumption of an Exascale machine, a floating-point operation requires 20 pJ of heat on this machine [Borkar, 2013]. Table 1.2 compares the amount of heat required to perform floating-point operations and DRAM reads on current machines with expected values in Exascale. We await for a reduction by at least a factor of 4 to ensure energy efficiency.

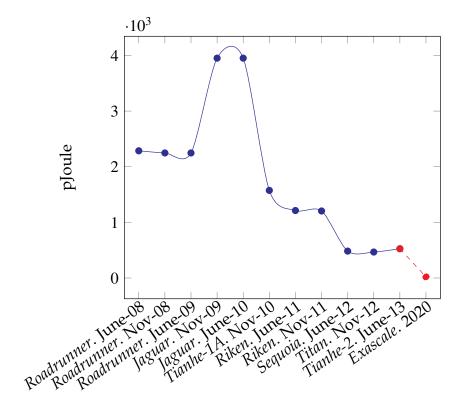

Figure 1.1 presents the evolution of power consumption considering only floating-point operations for top machines since June 2008.

|                    | 2011    | 2018 Expectations |

|--------------------|---------|-------------------|

| DP FMA Flop        | 100pJ   | 20pJ              |

| DP DRAM Read       | 2000 pJ | 1000pJ            |

| Local interconnect | 7500 pJ | 1000pJ            |

| Cross System       | 9000 pJ | 1500pJ            |

Table 1.2 From Shalf et al., 2011b. Data movement cost in term of power consumption.

Contribution of data movements between memory hierarchies to power consumption in current systems is high as shown in the listing 1.2. It is even higher when it comes to use the network in order to move data from one node to another. Predicted costs for Exascale machines are expected to increase. Reducing data movements is consequently mandatory to reduce the power consumption. Leveraging data locality mechanisms is necessary as it enables the reuse of the data fetched in the faster memory levels. It is also important to rethink applications in order to reduce communications between nodes and therefore limit the use of the network. This results in a decrease of the demand on bandwidth and the impact of latency of both memory and network.

**Figure 1.1** Cost of a floating point operation in term of energy consumption for machines ranked first in top500 from June 2008 to June 2013.

This leads us to the following paragraph where we depict the challenges related to memory systems design while maintaining low power consumption.

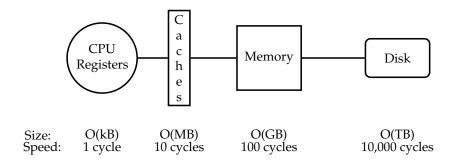

#### 1.1.1.2 Memory Systems

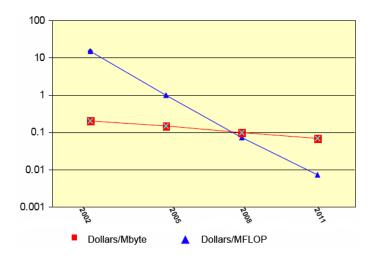

As described in figure 1.2, memory hierarchies in computing systems are mainly characterized by their latency, bandwidth and capacity. The cost per bit of memory is also an important feature in computing systems since it can guide the trade-off between capacity and speed. The figure 1.3 illustrates the evolution of dollars/M-Byte and dollars/MFlop rates from 2002 to 2011 and shows a clear drop of flops cost compared to the modest decrease of bytes cost. This explains the gap between processing units and memory which results in the inefficacy of a wide range of applications bounded by memory bandwidth or latency. This gap is expected to be even wider in Exascale systems.

A machine balance is a metric expressing the number of bytes transferred per a floating-point operation. The value of this metric gives an idea on the behavior of an application on a given architecture. Depending on the arithmetic intensity of this application, we can figure out if the memory bandwidth is going to be a bottleneck or if it is the processing units. Rethinking the current memory systems is important to maintain a low machine balance in Exascale and ensure a larger number of applications running efficiently on these machines.

**Figure 1.2** Memory system hierarchy.

In the following paragraphs, we give possible solutions in order to attenuate the limitations on memory bandwidth, latency and capacity.

Figure 1.3 From Dave Turek, 2009. Reduction of Flops and Bytes costs.

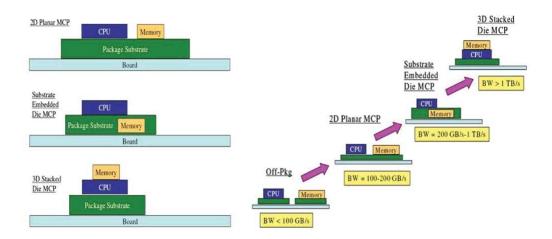

**Packaging** Packaging of the memory and the processing unit can greatly influence the bandwidth rates. Re-defining the architecture of current systems may result in an improvement of the bandwidth and thus increase the overall system performance. The figure 1.4 is a roadmap proposed by Camp et al., 2010 describing trends in CPU and memory packaging likely to surpass the hardware limitations we are facing today in increasing the bandwidth. Ultimately, a 3D stacked packaging is expected to deliver a bandwidth greater than 1 TB/s at the cost of challenging integration issues. [Coteus et al., 2011; Loh, 2008; Woo et al., 2010]

**Memory Bandwidth** As the number of cores per node is expected to increase as we are moving towards the Exascale, the memory bandwidth will clearly be a bottleneck that can greatly impact the application performance. New packaging techniques as described previously give solutions to solve the bandwidth issue on

**Figure 1.4** From Camp et al., 2010. Roadmap for memory and CPU packaging in order to respond to the bandwidth demand.

the hardware side. Data locality is another solution to get around the bandwidth limitations on the applicative side which implies some modifications of the existing implementations.[Stevens et al., 2009].

**Memory Capacity** Figure 1.3 illustrates the evolution of the cost of floating point operations and bytes in term of dollars. In 2011, flops are 1000 times cheaper than in 2002. This is not the case of bytes barely 10 time cheaper in 2011 than in 2002. Increasing of the aggregate memory capacity contributes greatly to the cost of the whole system (see figure 1.3). Taking into consideration the economical constraints for Exascale systems, this tendency observed on figure 1.3 is expected to continue on Exascale systems, resulting in a great augmentation of the number of FPU compared to the memory capacity. Shalf et al., 2011c estimate an improvement factor of 100x in memory capacity compared to a factor of 1000x in the system peak floating point performance.

#### 1.1.1.3 Node Architecture

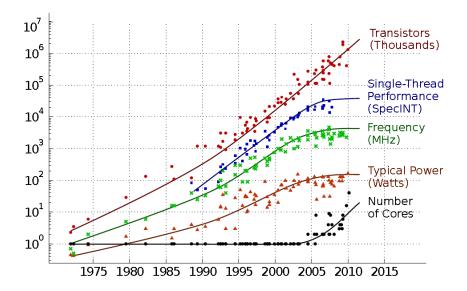

Figure 1.5 describes the scaling of general-purpose processors from 1975 to 2012. We notice that since 2005 the frequency and the single-thread performance are witnessing a slow-down of their evolution. On the contrary, the number of cores is increasing greatly starting from 2005. It is the response to the decrease of the single thread performance and frequency. An extrapolation to the Exascale systems and taking into consideration to power limitations described in paragraph 1.1.1.1, the number of cores will continue to increase and as a consequence we expect unprecedented changes of the node architecture. In paragraph 1.1.1.2, we considered the widening gap between memory system and the processing units. A possible solution in order to hide latencies due to this gap is the use of multi-threading as it permits to reschedule a second thread while the first one is, as an example, waiting for data [Borkar et al., 2011].

**Figure 1.5** From Batten, 2010. General-purpose processors trends in terms of power consumption, number of transistors, frequency and number of cores.

**Parallelism** It is reflected by the increase of the number of computing units which are expected to double every 18-24 months [Hall et al., 2011]. As a consequence, we need to compensate the need to higher compute capacities by the mean of parallelism at the node level using many cores and threads.

This leads us to two major trends in the node architectures and consequently the whole system as described in Kogge et al., 2008. We can expect to have heavy-weight nodes with relatively restricted number of cores but having advanced features. On the other hand we can have lightweight nodes with a high number of cores with less sophisticated capabilities but offering the possibility to use parallelism to compensate the latencies.

**Heterogeneity** It is another opportunity to enhance computational capabilities of the node while maintaining a reasonable power consumption. Current accelerators are connected to the host via a PCIx interconnect and have separate memory spaces. Therefore data movements between the two devices are not supported explicitly and data placement should be done at a high level in the application in order to minimize the cost of data movements.

AMD fusion project is an example of the willing to get rid of the PCIx interconnect and to homogenize the memory accesses in order to facilitate the programming of these architectures while maintaining a lower bound on power consumption.

#### 1.1.1.4 System Resiliency

The increasing number of cores and the need to use a threshold for power may be the reason for frequent fault accidents. The recovery time, known as the Mean Time To Repair (MTTR), is expected to increase in an Exascale machine. Fault accidents and time needed to recover them are also expected to grow. Resiliency can be permanent and in this case it occurs in the hardware or transient and it happens in the software level. In this last case, It can be recovered relatively quickly.

Mechanisms such as I/O checkpointing to prevent these failures are extremely important but they should not be intrusive and degrade the application performance.

#### 1.1.1.5 Network Interconnect

Many applications need domain decomposition techniques in order to remedy to shortage in memory capacity on the computing nodes.

This implies massive utilization of the communication network. Consequently, latency and bandwidth of the network have great impact on performance on applications and neglecting the I/O may induce issues for data intensive applications.

For Exascale machines, the issue of I/O bounded applications will persist and even worsen. Overlapping I/O with computations and the use of asynchronous accesses will be probably used but they won't be enough in reducing the overhead generated. New technologies such as Photonics introduced by Intel and Fujitsu are needed to alleviate this issue [Coteus et al., 2011; Camp et al., 2010].

#### 1.1.1.6 Potential Exascale System

As a summary, the potential Exascale systems can have two possible configurations as described in the DARPA's report on Exascale transition [Kogge et al., 2008].

- **First Lane** where cores are expected to be complex. These systems will be the earlier version of Exascale machines and are expected around 2018. This configuration will induce reduced number of nodes.

- **Second Lane** where cores are rather lightweight and their number will increase per compute node. This is the long term version of an Exascale system where thread level parallelism will be an important mechanism to hide latencies.

Table 1.3 summarizes of the potential characteristics of an Exascale system as described in the technical reports of the US Department of Energy (DOE). These are a preliminary results subject to modifications with the upcoming machines [Kogge et al., 2011].

A profusion of architectures is emerging in order to study the possibilities of saving energy while performing the required floating-point performance to reach an exaflopic performance. The Echelon architecture implemented by Nvidia and described in Keckler et al., 2011 is an example of architectures that aim to limit energy consumption to 20 pJ per floating-point operation. We can also name Runnemede an Intel architecture that is a response to the UHPC project. This architecture leverages a co-design process in order to respect the architectural constraints

|                  | Tianhe-2             | 1st Lane           | 2nd Lane            |

|------------------|----------------------|--------------------|---------------------|

| System peak      | 54.9 Pf/s            | -                  | -                   |

| HPL benchmark    | 33.86 Pf/s           | $1  \mathrm{Ef/s}$ | 1 Ef/s              |

| System nodes     | 16,000               | $O(10^6)$          | $O(10^5)$           |

| System cores     | 3,120,000            |                    |                     |

| System memory    | 1,4 PB               | 32-64 PB           | 32-64 PB            |

| Node performance | $3.4\mathrm{TF/s}$   | 1 TF/s             | $10  \mathrm{TF/s}$ |

| Node concurrency | 195                  | $O(10^3)$          | $O(10^4)$           |

| Node memory      | 64 GB CPU + 8 GB Phi | 32-64 GB           | 0.32-0.64 TB        |

| Power            | 17.8 MW              | 20 MW              | 20 MW               |

Table 1.3 Potential Exascale systems.

fixed by DARPA for a feasible Exascale system. Another example of architecture enabling energy efficiency in order to facilitate the transition to Exascale systems, we can also name the Green Wave architecture introduced in Krueger et al., 2011 to study hardware/software co-design for seismic modeling applications.

#### 1.1.2 Software Challenges

Exascale is not only a matter of hardware features. It also implies tremendous modifications of the current software stack as discussed in [Barrett et al., 2012; Dongarra et al., 2011]. We are going to expose the possible modifications affecting the operating systems, compilers, runtimes and programming models and debugging tools in order to prepare them to the expected hardware constraints in Exascale systems. We need to take into account the increase of concurrency and parallelism, the expected limitations on main-memory and networks in terms of bandwidth and latency, the power efficiency requirements and the resiliency considerations. This is an important task to undertake to ensure an efficient use of the hardware.

#### 1.1.2.1 Operating Systems

Operating systems are important components of the software stack on the current machines. On Exascale systems also, their role will be essential in maintaining an efficient use of the hardware resources since inadequate operating systems can result in dramatic impact on performance.

Two approaches are possible either rewrite from scratch a new operating system or upgrade an existing implementation based on the expected architectural features of the future systems. In both cases, we should take into considerations few constraints such as the increasing concurrency and the need to hide the system latencies using many threads per core. The execution of a single task using many threads will be therefore a common technique. We need also to think of new mechanisms to unburden the shared resources between the computing cores. The memory bus, for example, can cause great performance issues.

#### 1.1.2.2 Programming Models & Runtimes

As the number of cores per node are expected to increase greatly, we need to maximize parallelism in applications and have a reliable runtime in order to ensure an efficient scheduling of tasks among the workers. This important feature needs to be handled transparently by the programming model. Developer's concern is focused on programming the scientific application.

For Exascale, we might also need more than a programming model to handle the increasing number of cores per node and ensure interoperability between them. As an illustration, we can consider hierarchical programming where we perform communications using message passing interface MPI and computation using a shared memory model such as openMP. The combination of these two models depend on the needs of the application. We can have a master-slave model where the MPI communication is performed by a single thread, the master, and the openMP threads compute. An other configuration consist of multiple communications performed by multiple threads simultaneously. For this case, the MPI implementation should be thread safe. On the other hand, MPI implementations should support a more sophisticated manner to identify threads rather than tags which cannot offer sufficient flexibility for all applications.

Partitioned Global Address Space (PGAS) programming models such as Co-Array Fortran (CAF) represent an interesting opportunity. Open64 compiler supports an implementation of CAF. [Eachempati et al., 2012] is a proof of concept that this programming model can easily included in an industrial code. Scalability and performance reported on Reverse Time Migration give an encouraging start to adopt these programming models in industry but CAF is more suitable for applications with regular communication patterns. I/O are also a challenge to consider as they represent one of major bottlenecks for these data-intensive applications

#### 1.1.2.3 Compilers

Compilers have a great impact on applications performance since they guarantee the efficient use of the underlying architecture. Low level optimizations such as loop modifications like padding and tiling, vectorization, software prefetching are architecture-dependent optimizations and are fastidious implementing within the application code. For Exascale, we will be facing heterogeneity on one hand in order to profit from the low power consumption of some devices such as accelerators. On the other hand, we need to ensure the efficient use for every single architecture since they can have different vector widths and different instructions.

#### 1.1.3 Algorithmic Challenges

As section 1.1.1.1 suggests, data movements in Exascale systems are expected to be extremely expensive in terms of pJoule/Byte. The main reason is the growing gap between arithmetic units and the memory system and the increasing power consumption that it will generate. As a consequence, neglecting data locality may hinder extremely the performance of applications on Exascale systems. Algorithms need to enhance data locality in time and space in order to reuse as much

as possible data fetched in caches and avoid unnecessary memory traffic.

Extrapolations to Exascale predict that floating operations are going to be available in abundance and compared to memory traffic they will be almost free. We can use these arithmetic units to introduce more complexity in our computations when overlapped with communications, we can hide network latencies. [Dongarra et al., 2012]

Communication-avoiding Algorithms. Many applications are bounded by the time spent in communications and in memory traffic. Since the gap between the processing units and memory systems is exponentially increasing and since the latency on network can be penalizing, we need to limit the data movements for the current Petascale systems and more urgently for the Exascale machines. Communication-avoiding algorithms aim to minimize the impact of these communications on performance by minimizing the number of messages transferred and their volume. They also can rely on redundant computations. These algorithms are mainly dense and sparse linear algebra algorithms which require the implementation of new numerical methods while ensuring the stability of these new solutions [Khabou, 2013]. For example, the Strassen algorithms are a communication-avoiding variant of matrices multiplications [Lipshitz et al., 2012]. Apart from the impact on performance, minimizing the data movements in these new algorithms will reduce the power consumption compared to the usual implementations.

**Fork-join Model.** This technique is extensively used in scientific applications. Programming models such as OpenMP permit to use multi-threading capabilities in order to accelerate the computing loops. As the number of cores per node in Exascale machines is expected to greatly increase, the overhead due the initialization of these parallel sections and due to the synchronization will consequently increase and deteriorate the overall performance of applications.

**Load Balancing.** As heterogeneous architectures are expected to be extensively used in Exaflopic machines, we need to implement algorithms that enable load balancing in order to avoid stalls that are inherent to this heterogeneity. In some cases, handling the load balancing may require the implementation of hardware specific modules and even the modification of the whole algorithm in order to introduce new mechanisms such as scheduling and tasks queuing. The aim is a better management of available resources.

Multi-scale algorithms also require load balancing. We can name multi-grid algorithms applied to seismic modeling. The mesh refinement is performed only in the area where the simulation needs more precision.

**Auto-tuning.** This refers to a set of tools used to determine the best combination of optimization factors for an application class depending on the targeted architecture. It involves the number of threads, cache blocking factors, padding length, etc. Since heterogeneity is inevitable in Exascale systems, machines will be more

complex. As a result, the optimization process will be tedious and time consuming task which explains the need to auto-tuning tools in order to use efficiently the architecture.

**Performance Metrics.** New metrics are emerging as we are preparing Exascale systems. Considering the constraints on power consumption, usual performance metrics reporting the number of operations performed per a unit of time for example will not be considered as the unique reference on the efficiency of a given application. Metrics such as pJoule/Byte or pJoule/operation are going to be determinant in illustrating an application behavior on Exascale systems [Camp et al., 2010].

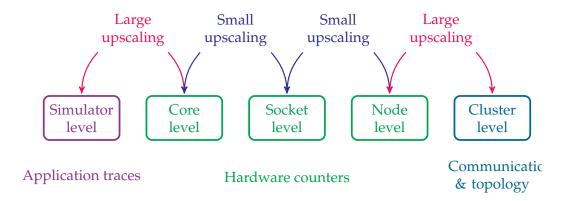

#### 1.1.4 Co-Design

The Department of Energy (DOE) Exascale Computing program is an initiative to gather efforts in hardware and software areas and work jointly in order to build efficient Exascale systems. This is the opportunity to establish a co-design process applied to Exascale. In this study, the applications design take part in the improvement of the hardware. Interaction between developers and architects is a key element to elaborate new architectures that take into consideration algorithmic requirements. On the other hand, an Exascale system is expected to introduce various changes on the hardware. It may concern the node architecture, interconnect and the cooling of the whole system. Consequently, algorithms will need to adapt in order to efficiently run on these architectures. This includes data management, the use of memory system and the arithmetic-unit and IO bandwidth. The figure 1.6 is a high level illustration of co-design. For applications side, we need to consider the algorithms, the underlying performance models and the implementation. On the system side, we need simulators, building of new micro-architectures and interconnects. We also need the development of an adapted software stack that enables an efficient use of the hardware.

The Co-Design for Exascale (CoDEX) project [Shalf et al., 2011a] is a response to the DOE initiative. It combines a bunch of tools that range from cycle accurate simulator to node architecture to an extrapolation of memory and interconnect for the Exascale. These tools allow a software/hardware co-design illustrated in [Krueger et al., 2011] for an energy study applied to seismic modeling.

In order to facilitate the co-design process, applications are not studied as a whole. We instead consider lighter versions of these applications ranging from simple kernels capturing the computational core of the application to more sophisticated versions gradually including physic considerations and I/O operations since they are extensively use in real applications. The classification of the different versions leading to real applications are explained in table 1.4 as described in [Shalf et al., 2011c] where the word *surrogate* was used to designate this light versions. They are extremely useful in a co-design process since they permit to highlight the architectural features impacting the performance at each level.

For the feasibility study in Exascale applied to seismic imaging applications, we will rely on these surrogates in order to overcome the burden in production

**Figure 1.6** High level description of the co-design process. We emphasize on the interaction between the application side and the system side in order to enable the design of the adequate hardware and algorithms.

| Surrogate            | Description                                                                                           |

|----------------------|-------------------------------------------------------------------------------------------------------|

| Compact application  | Small app with fewer features and simplified boundary conditions relative to a full app               |

| Mini-application     | Small, self-contained program that embodies essential performance characteristics of key apps         |

| Skeleton application | Program that captures an app's control flow and communication pattern; can be run only in a simulator |

| Proxy application    | General term for all other surrogates                                                                 |

| Mini-driver          | Small programs that act as drivers of performance-impacting library packages                          |

| Kernel               | Program that captures an algorithm's node-level aspects                                               |

**Table 1.4** From Shalf et al., 2011c. Definition of application surrogates.

codes. We will start with kernels highlighting the computational behavior of imaging applications on the node level. We will particularly focus on an application called Reverse Time Migration (RTM) as it is widely used by Oil & Gas companies. We will then consider a compact-application version of RTM to facilitate the port-

ing on a representative architecture of the trend in Exascale systems. It's the Intel Many-Integrated Core (MIC) architecture. This will enable us an extrapolation to a larger scale system with representative features of an Exascale machine.

#### 1.1.5 Previous Feasibility Studies

In [Bhatele et al., 2011] and [Gahvari et al., 2010], we can find feasibility studies of Exascale systems based on extrapolations of hardware features and performance models of representative application classes commonly used in scientific computing.

Gahvari et al., 2010 conducted a study on FFTs and basic geometric multigrid. Scalability was studied in both cases for the Exascale and an evaluation of the requirements in terms of latency and memory bandwidth on such systems was presented based on performance models of these applications.

A similar work was presented by Bhatele et al., 2011 where the applications considered are molecular dynamics, cosmological simulations and finite element solvers. The study concerns the weak and strong scalability of these applications on Exascale machines. It also considers memory requirements and the volume of communications compared to computation requirements.

Further co-design studies can be found in [Czechowski et al., 2011a], for example, where authors revisited simple metrics commonly used by the HPC community such the balance principle, Little's law, Amdahl's law, etc.

The co-design principle can also be applied to the energy efficiency challenge. Krueger et al., 2011 give a study that aims to minimize the power consumption. They consider a seismic imaging application called Reverse Time Migration RTM. Co-design studies also focused on other applications such as FFT [Czechowski et al., 2011b; Czechowski et al., 2012], molecular dynamics, finite-element solvers and cosmological simulations [Bhatele et al., 2011].

# 1.2 Geophysical Applications

The establishment of the theories governing geophysical phenomenons started since 1960. As the methods developed are mainly compute intensive, the computing technologies evolution in the 80's was extremely promising since they made possible their effective application in a real context such as seismic exploration. They also prove to be beneficial to study earthquakes and to image the earth layers in order to facilitate the localization of hydrocarbon deposits.

As a consequence, the evolution of the seismic applications is historically related to the evolution of computers and afterward HPC systems. The growth of the compute capacities and the amount of the data they handle permitted the utilization of new numerical methods with complex physics and the exploration of wider area with higher resolutions.

Given the actual HPC context, seismic applications constitute an important class that we need to consider in the co-design process. Classification and characterization of the major approaches in seismology using modeling is an interesting task that permits the extrapolation of the performance on different architectures and herein determines which methods are more suitable for Exascale machines.

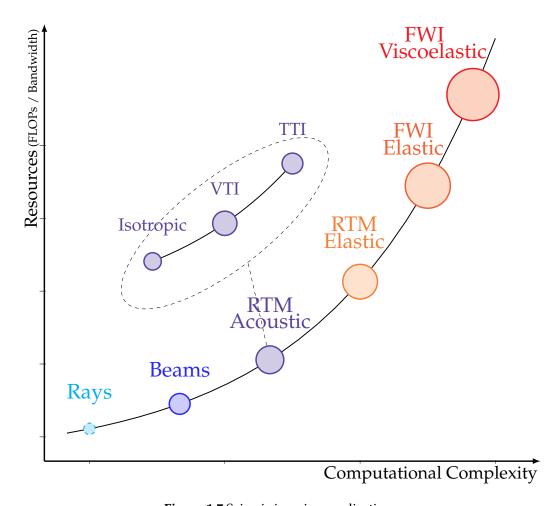

Figure 1.7 depicts the resource requirements as a function of the complexity in terms on computation. Resource needs increase exponentially as the media studied is complex and as the method is compute demanding. The figure is also an illustration of the trends in seismic imaging. It shows that the increase in compute capacity permits to tackle geophysical complexity easily. It enables more accurate modeling of wave physics, higher grid resolution and wider frequency content.

Figure 1.7 Seismic imaging applications.

#### 1.2.1 Seismic Imaging Applications

Exploration seismology techniques are widely studied by the scientific community. One can find detailed descriptions of these techniques in a multitude of studies such as [Sheriff et al., 1995; Biondi, 2006] to name few. In the following paragraphs, we define some of these seismic imaging applications.

#### 1.2.1.1 Seismic Modeling

Seismic modeling applications build a synthetic image of the earth based on a model of the velocity making assumptions on the physical properties of the medium studied. In order to approximate the wave equation, seismic modeling can rely on a multitude of numerical methods such as integral methods, asymptotic methods and direct methods presented in chapter 2.

#### 1.2.1.2 Reverse Time Migration

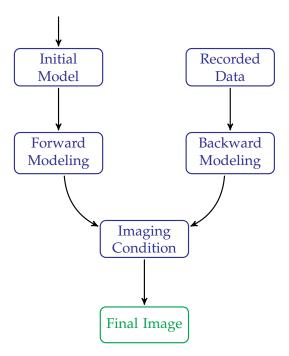

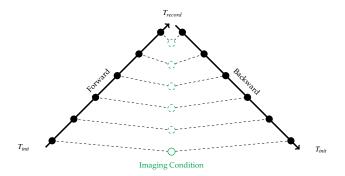

The Reverse Time Migration (RTM) is an application widely used by Oil and Gas companies in order to build an image of the earth crust. Figure 1.8 depicts from a high level point of view the 3 steps in RTM.

We start with a forward modeling using an initial model of the velocity. Then, we perform a retro-propagation of the wave equation using the recorded data. It is the backward modeling. Finally, we produce the final image using a cross-correlation applied on the computed values in the previous steps.

Figure 1.8 Reverse time migration work flow.

#### 1.2.1.3 Full Wave Inversion

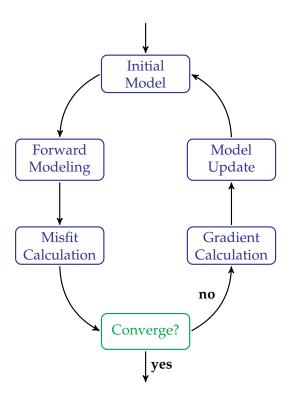

The Full Wave Inversion (FWI) aims to build a velocity model of the subsurface studied. As described in figure 1.9, we compute the misfit between the computed wavefield and the observed data and iterate on the corrected data until we converge.

**Figure 1.9** Full wave inversion work flow.

#### 1.2.2 Seismic Exploration Work Flow

Seismic exploration surveys are long processes that aim to have a precise localization of hydro carbon deposits in a given area which enables quick and precise drilling. This is an important process for Oil and Gas companies because it permits to significantly save time and money.

The data acquisition during these surveys is followed by other steps before obtaining a final image. It consists in : velocity modeling, wave field migration and interpretation.

#### 1.2.2.1 Data Acquisition

Data acquisition is performed during exploration campaigns. These campaigns occur whether on land or in marine. The approach is the same in the two environments but involve different tools. The process consists of four steps.

The creation of a wave propagation using seismic vibrators or explosive sources in land or compressed air guns in marine. The wave generated propagates into the earth crust. At discontinuities, reflections occur. The reflected waves are recorded using geophones in land and hydrophones in marine. Preprocessing is the last step. It aims at preparing the collected data during the survey. It consists in removing the noise contained in the raw data since it can interfere in the final image and result in misinterpretation. Figure 1.10 explains the different steps required

during seismic acquisition in marine and in land. The previous four steps are illustrated in both cases.

(a) Marine seismic acquisition

(b) Land seismic acquisition

**Figure 1.10** Seismic acquisition steps in marine and in land: 1) acoustic source emits energy 2) seismic waves propagate in subsurface layers 3) reflected waves are recorded by geophones or hydrophones 4) raw data is processed. Courtesy of Sercel, 2014.

#### 1.2.2.2 Migration/Imaging

Migration places geometrically the discontinuities of the subsurface encountered during the wave propagation. It aims at reconstructing an image of the crust. The migration complexity depends on the nature of the area explored. Therefore, as described in [Sheriff et al., 1995], we have the following approaches:

- *Time migration.* It produces an image function of time. It is used when contrasts are small and when the geological structure is simple. This explains why it is mainly used for sedimentary basins.

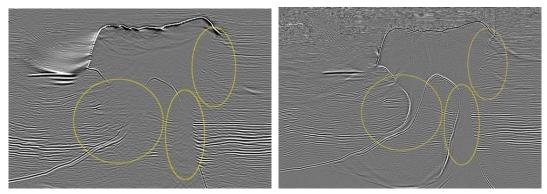

- Depth migration. It gives an image function of depth. It's more appropriate for complex structures with sharp slopes. It is also used in subsurfaces containing salt domes. As described in [Farmer et al., 2009], depth migration can be ray-based like Kirchhoff migration and beam migration. These approaches are used for steep structures but are inefficient when strong velocity variations are encountered. Wave equation migration techniques are another family of depth migration. We have the one-way wave equation migration which is unable to image accurately salt structures with strong dipping flanks. This limitation is removed in the two-way wave equation migration which is more efficient in imaging steep structures and extreme velocity variations especially on the surfaces neighboring salt structures. Figure 1.11 illustrates the one-way and two-way migrations using the BP 2004 benchmark [Billette et al., 2005]. The yellow circles depicts the weaknesses of the one-way migration next to the salt dome flanks.

We call seismic trace the data recorded by the receivers during the recording time of the seismic acquisition. The migration can occur before the summation of

**(a)** One-way wave equation migration: split-step**(b)** Two-way wave equation migration: reverse Fourier plus interpolation.

**Figure 1.11** Images showing the difference of imaging for two different depth migration algorithms. Courtesy of Farmer et al., 2006.

these traces and it is called pre-stack migration in this case. Or, it can be applied on the result of their summation and then we call it post-stack migration. Pre-stack migration gives more accurate results but requires more computations compared to the post-stack migration.

#### 1.2.2.3 Interpretation

The image produced by the migration algorithms need to be studied in order to localize the possible hydrocarbon deposits. The quality of the image depends on the algorithm used for the migration.

#### 1.2.3 Challenges in Seismic Imaging Applications

Challenges in seismic imaging applications are related to the nature of the subsurface studied and the available resources to give a precise image of the subsurface in a reasonably short time.

**Time-to-solution vs cost-to-solution** Time-to-solution is the time needed for an application to converge while cost-to-solution includes the necessary resources needed in terms of compute capabilities, energy, maintenance, etc. Among major concerns when it comes to production codes, such as RTM and FWI, is to find a trade-off that minimizes both time- and cost-to-solution.

**Data management and I/O issues** When implementing a time domain approach, the wavefield produced by the forward step has to be available while resolving the backward step. For real cases, the data generated needs to be stored on disk and results in I/O accesses which can constitute a bottleneck. In order to reduce the amount of data stored during the forward propagation, checkpointing methods can be applied as described in **Dussaud et al.**, 2008 for example. We will give more details on these methods in the last chapter 6.

#### 1. Motivations

In the case of frequency domain implementations, we avoid this I/O issues since each frequency can be treated separately. For this approach, we need instead an efficient solver. The choice of the time domain or the frequency domain depends on the problem we are solving.

**Efficiency of the numerical scheme** The choice of the numerical scheme is also important. Their efficiency and the quality of the image they produce depend closely of the nature and the characteristics of the subsurface imaged. Chapter 2 gives in details the advantages and limits of each numerical method.

# Seismic Modeling

This chapter is an overview of the numerical methods used for seismic modeling. This introduction to these methods is important in order to understand the algorithms and challenges faced during the implementation. This understanding offers also the opportunity to pick the appropriate method according to the underlying architectures we are studying. Usually, we have a specific numerical method widely used in a discipline. In seismic imaging, the choice of the method depends on the aims of the study, the available resources and the environment. This resulted in a multitude of methods each has its advantages and its drawbacks. In this chapter, we begin with defining to the seismic waves and describe the difference between them. Then, we introduce the main families of numerical methods approximating the equations governing wave propagation in elastic and acoustic media: integral methods, asymptotic methods and direct methods. These methods were widely studied for seismic imaging and one can find more details in [Carcione et al., 2002; Virieux et al., 2011] for example. In the last section, we give more details on finite-difference techniques since we implement them in our applications. We will go through dispersion and convergence studies. Finally, we will introduce the boundary condition methods such as the Absorbing Boundary Conditions (ABCs) and Perfectly Matched Layer (PML) methods since we approximate the wave equation in a limited domain and we need to eliminate the artifacts due to reflections on boundaries.

#### 2.1 Seismic Waves

#### 2.1.1 Body Waves

We distinguish two types of body waves. Compressional waves also known as the P-wave since they correspond to the first event recorded when an earthquake occurs. Then we have shear wave also called S-wave and they are recorded in second place in earthquake. Figure 2.1 illustrates the propagation directions of P-and S- waves. The S waves can be decomposed into two components: SV vertical component and SH horizontal component.

Figure 2.1 Body waves: P and S.

In a homogeneous and isotropic media the velocities of P and S waves are the following:

$$V_p = \sqrt{\frac{\lambda + 2\,\mu}{\rho}} \qquad V_s = \sqrt{\frac{\mu}{\rho}} \tag{2.1}$$

Where  $\lambda$  and  $\mu$  are the coefficients of Lamé and  $\rho$  is the density. As the shear modulus  $\mu$  is equal to 0 in fluid, S waves don't propagate in water. Also, given the expressions of velocities  $V_p$  and  $V_s$ , we notice that the P waves have always greater velocity than S waves.

#### 2.1.2 Surface Waves

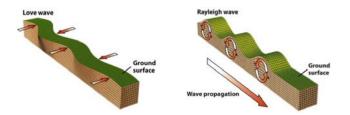

We have two types of surface waves: Rayleigh waves and Love waves. Rayleigh waves, also called ground roll, propagate when the surface of the medium is free or considered as free like air since the elastic constants and density are very low compared to their values in rocks. Rayleigh waves are dissipative this means that their amplitude diminishes with depth. Love waves, also known as Q waves, apply horizontal transformations to the surface of the earth.

Figure 2.2 depicts the behavior of the Rayleigh and Love waves in comparison to the propagation direction of the seismic wave.

Figure 2.2 Surface waves: Rayleigh and Love.

# 2.2 Wave Equations

In Virieux et al., 2011 and Carcione et al., 2002, we find overviews of the different approaches to resolve wave equation depending on the needs and the application domain. We can adopt a time-domain approach or a frequency-domain approach depending on the computational needs and on the available resources.

## Time Domain Approach

It simulates the variation in time of the wavefield u from sources to receivers. A usual work flow in a time domain approach consists of 3 majors steps. We first introduce a source term to create a wavefield. We then advance in time using the numerical approach chosen. When the wavefield has propagated from all sources to all the receivers used during the acquisition, we stop the computation.

The numerical methods commonly used for time-domain approaches are finite-difference and finite-element methods. They are popular for their efficiency and their straightforward implementation.

## Frequency Domain Approach

This approach expresses the seismic modeling problem in the frequency domain using a Fourier transformation in time. As a result, the wave equation becomes a set of linear systems, one for each frequency. Also, the time-dependency is eliminated which permits the resolution of each systems independently.

In order to solve these systems, we can use direct solvers or iterative solvers. For direct solvers, LU and incomplete LU can be used but can cause prohibitive storage requirements in 3D cases. For the iterative solvers, we can opt for the multigrid-preconditioned Krylov methods. The main difficulty of these approaches is the convergence of the solver.

#### 2.2.1 Elastic Wave Equation

The elastic wave equation is established using the Newton's second law of motion and Hooke's law.

Newton's law states that the acceleration of a particle when multiplied by its mass is equal to the sum of forces applied on it. We assume that we are in the case of small displacements in order to satisfy the elasticity condition.

Applying the previous laws leads to the system 2.2 which is the velocity-stress first order equation of wave propagation.

$$\rho \frac{\partial v_i}{\partial t} = \frac{\partial \sigma_{ij}}{\partial x_j} + f_i^v$$

$$\frac{\partial \sigma_{ij}}{\partial t} = c_{ijkl} \frac{\partial v_k}{\partial x_l} + f_{ij}^\sigma$$

(2.2)

Where  $v_i$  components of velocity vector;  $\sigma_{ij}$  components of stress tensor;  $c_{ijkl}$  components of stiffness tensor;  $\rho$  density;  $f_i^v$  components of force source vector and  $f_{ij}^{\sigma}$  components of moment rate source tensor.

The displacement second-order elastodynamic equation

$$\rho \frac{\partial^2 u_i}{\partial t^2} = \frac{\partial c_{ijkl}}{\partial x_i} \frac{\partial u_k}{\partial x_l} + f_i \tag{2.3}$$

Where  $u_k$  are the components of the displacement vector.

# 2.2.2 Acoustic Wave Equation

Through the following sections, we use the notation  $\mathbf{x}=(x,y,z)\in\mathbb{R}^3$  to denote spatial position and  $t\in\mathbb{R}^+$  to denote time.

Let u denote the acoustic pressure field and  $\rho$  the density of the medium in which the acoustic wave travels. In its scalar form, the second-order partial differential equation in time can be written as follows

$$\frac{1}{\rho(\mathbf{x})c^2(\mathbf{x})} \frac{\partial^2 u(\mathbf{x},t)}{\partial t^2} - \nabla \left( \frac{1}{\rho(\mathbf{x})} \nabla u(\mathbf{x},t) \right) = 0$$

(2.4)

Where  $\nabla = (\partial/\partial x, \partial/\partial y, \partial/\partial z)^T$ ;  $\rho$  is the density and c is the compressional wave velocity. Density and velocity are strictly positive functions of the position  $\mathbf{x}$ .

#### 2.2.2.1 Isotropic Media

An isotropic media has the same physical characteristics independently of the direction. As a consequence, the density  $\rho$  is constant and the wave equation 2.4 can be rewritten like in 2.5.

$$\frac{1}{c^2} \frac{\partial^2 u(\mathbf{x}, t)}{\partial t^2} - \Delta u(\mathbf{x}, t) = 0$$

(2.5)

#### 2.2.2.2 Anisotropic media

Transverse isotropy is the common form of anisotropy encountered in exploration campaigns. In this case, we have an axis of symmetry orthogonal to planes of isotropy. This can be the case for layered subsurfaces [Alkhalifah, 2000; Fletcher et al., 2009].

The equation 2.6 is the second-order coupled equation governing the acoustic wave propagation in a homogeneous TTI media. In this equation 2.6, we have p the pressure wavefield and q an auxiliary wavefield. We consider P and SV wave modes and denote  $v_{pz}$  the P-wave velocity in the direction normal to the symmetry plane, whereas  $v_{sz}$  designates the SV velocity normal to the symmetry plane. We also use  $\varepsilon$  and  $\delta$  the anisotropic parameters. The angles  $\theta$  and phi are the dip measured to the vertical and the azimuth of the axis of symmetry respectively.

$$\frac{\partial^2 p}{\partial t^2} = v_{pz}^2 (1 + 2\varepsilon) H_2 p + \alpha v_{pz}^2 H_1 q + v_{sz}^2 H_1 (p - \alpha q)

\frac{\partial^2 q}{\partial t^2} = \frac{1}{\alpha} v_{pz}^2 (1 + 2\delta) H_2 p + \alpha v_{pz}^2 H_1 q - v_{sz}^2 H_2 (\frac{1}{\alpha} p - q)$$

(2.6)

Where the operator  $H_1$  and  $H_2$  are defined as follows

$$H_{1} = \sin^{2}\theta \cos^{2}\phi \frac{\partial^{2}}{\partial x^{2}} + \sin^{2}\theta \sin^{2}\phi \frac{\partial^{2}}{\partial y^{2}} + \cos^{2}\theta \frac{\partial^{2}}{\partial z^{2}}$$

$$+ \sin^{2}\theta \sin^{2}\phi \frac{\partial^{2}}{\partial x \partial y} + \sin^{2}\theta \sin\phi \frac{\partial^{2}}{\partial y \partial z}$$

$$+ \sin^{2}\theta \cos\phi \frac{\partial^{2}}{\partial x \partial z}$$

$$H_{2} = \frac{\partial^{2}}{\partial x^{2}} + \frac{\partial^{2}}{\partial y^{2}} + \frac{\partial^{2}}{\partial z^{2}} - H_{1}$$

$$(2.7)$$

#### 2.2.2.3 Boundary Condition: Perfectly Matched Layer

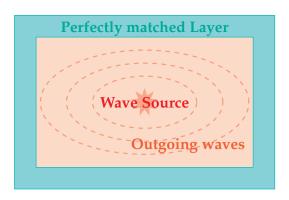

Truncating the domain where the wave propagation occurs introduce artifacts to computations. This is due to reflections of the wave on the boundaries. We add an Absorbing Boundary Condition (ABC) to blur the boundaries and thus avoid reflections.

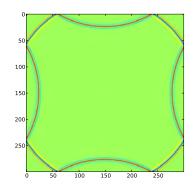

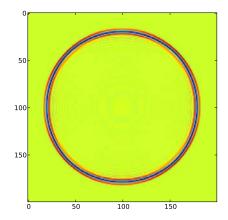

In the finite-difference time-domain implementations we are studying, we use the Perfectly Matched Layer (PML) method as a boundary condition. This technique was designed by Jean-Pierre Berenger in 1994 for Maxwell's equation. He suggested to add an artificial layer placed adjacent to the edges of the grid as shown on the figure 2.3. The wave will be attenuated in this layer.

Figure 2.3 Computation Domain Truncated by a Perfectly Matched Layer.

On figure 2.4, we illustrate the impact of the PML layer on the incident wave front in an isotropic medium.

(a) Isotropic wavefield without absorbing condi-(b) Absorbing conditions, PML in this example, retions on boundaries.

Figure 2.4 Impact of the PML method.

# 2.3 Numerical Methods for Seismic Modeling

Numerically, wave equation can be approximated using the spectral formulation or a strong formulation or a weak formulation.

Spectral formulation produces efficient results for simple geological structures whereas the strong formulation via finite-difference methods can give a good compromise between the quality of images and the computational cost. On the other hand, weak formulation via finite-elements e.g. continuous or discontinuous Galerkin methods are more suitable for areas with complex subsurfaces.

For our study, we consider a time-domain approach and approximate the wave equation using finite-difference. We will also consider two formulations of the equation. One in isotropic media and one in tilted transverse isotropic media (TTI).

#### 2.3.1 Integral methods

These methods are based on Huygens principle that stipulates that every point in the wavefield can be considered as a secondary source.

For the integral form of the scalar wave equation in homogeneous media we use the Green function G

$$G(\mathbf{x}, \mathbf{x_s}, t) = \frac{\delta(t - |\mathbf{x} - \mathbf{x_s}|/c_0)}{4\pi |\mathbf{x} - \mathbf{x_s}|}$$

(2.8)

$$p(\mathbf{x},t) = \int G(\mathbf{x}, \mathbf{x_s}, t - t') \ q(\mathbf{x_s}, t') \ d\mathbf{x_s} \ dt'$$

(2.9)

Green function are used as a response to a source in the studied media. The source location is  $x_s$ . p is the pressure generated by the particles displacement in media.

These approaches are more efficient in homogeneous medium.

## 2.3.2 Asymptotic methods

They are also called ray-tracing methods and are used when the medium is heterogeneous. In such media, the Green's functions cannot be computed simply.

An example of the asymptotic approch is the Kirchhof approximation widely used in migration as described in Biondi, 2006.

Kirchhof approximations are based on the assumption of high frequencies.

#### 2.3.3 Direct methods

Direct methods are based on a discretization of the computational domain. The approximation of wave equation can be done using strong formulations such as finite-difference and pseudo-spectral approaches. We can also rely on weak formulations like finite-element and finite-volume methods.

We also need a time integration in order to approximate the wave equation. Depending on the formulation chosen for the equation, the space and time derivatives can be either second or first order.

The source term is added to the right hand part of the equation in order to be able to resolve the equation.

#### 2.3.3.1 Pseudo-Spectral Methods

Pseudo-spectral (SP) methods also known as the Fourier methods are strong formulations of partial differential equations. Using these approaches, pressure values  $p(\mathbf{x})$  are approximated using basis functions  $\psi_j$  like in equation 2.10

$$p(\mathbf{x}) = \sum_{j=1}^{N} p(\mathbf{x}_{j}) \psi_{j}(\mathbf{x})$$

(2.10)

In the case of regular grids, one can use Fourier polynomials as basis functions. On the other hand Chebychev polynomials are used for irregular grids. In Kosloff et al., 1982, we have a description of the Fourier methods applied to forward modeling with comparison with finite-difference and finite-element methods. Contrary to finite-difference, pseudo-spectral methods are global. Modifications when they occur affect the whole computing grid. When we opt for the pseudo-spectral methods, we reduce the number of unknowns. We also reduce the number of grid points compared to finite-difference while achieving the same accuracy.

Pseudo-spectral methods can show some limitations when the topography is complex. Finer grid discretization in order to adapt to the complexity of the surface results in higher computational cost. This impacts the efficiency of this numerical method. Restraining it to relatively simple topographies.

#### 2.3.3.2 Finite-Difference Methods

Finite-difference (FD) approaches are also a strong formulation of partial differential equations. They are based on the discretization of the computation grid where we compute values of the wavefield. For finite-difference, we have approximations of spatial derivatives using for example the equation 2.11 where  $\Delta x$  is the spacing between two values of the field u.

$$\frac{du}{dx} = \lim_{\Delta x \to 0} \frac{u(x + \Delta x) - u(x)}{\Delta x} \tag{2.11}$$

The derivative can be approximated by the value given in equation 2.12. This is a forward difference approximation.

$$\frac{du}{dx} \approx \frac{u(x + \Delta x) - u(x)}{\Delta x} \tag{2.12}$$

One can have a backward difference approximation of the derivative like described in equation 2.13

$$\frac{du}{dx} \approx \frac{u(x) - u(x - \Delta x)}{\Delta x} \tag{2.13}$$

Combining the forward 2.12 and backward 2.13 approximations one can have a central approximation given by the equation 2.14.

$$\frac{\partial u}{\partial x} = \frac{u(x + \Delta x) - u(x - \Delta x)}{2 \Delta x} \tag{2.14}$$

For higher order approximations, Taylor expansion enables the computation of the derivatives as well as an estimation of the error.

In Moczo et al., 2007 and Kelly et al., 1976, we have detailed studies of the finite-difference methods applied in isotropic and anisotropic medium. All aspects ranging from the grids used to the boundary conditions are discussed.

Major difficulties in FD methods are due to the discretization grids. The space steps are constrained by the minimal value of the velocity in the media. For heterogeneous medium, the space discretization requires lots of computations.

FD methods are inefficient when the topography is complex. In order to have a precise approximation, space discretization steps need to be very small which results in a huge computational demand.

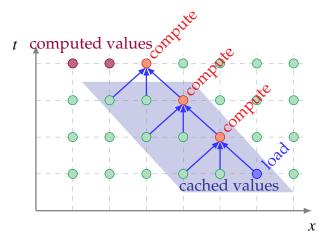

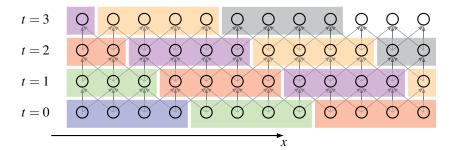

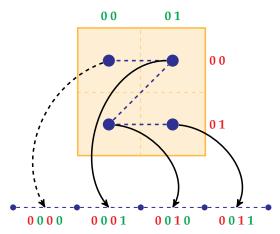

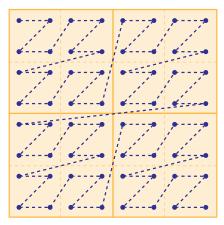

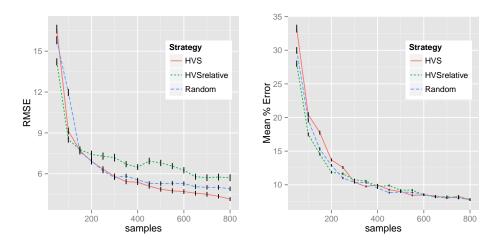

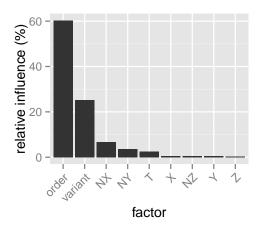

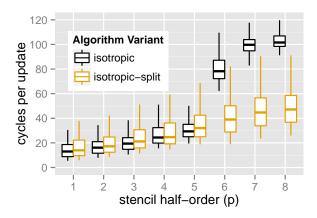

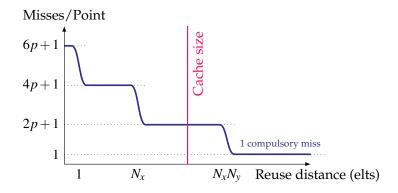

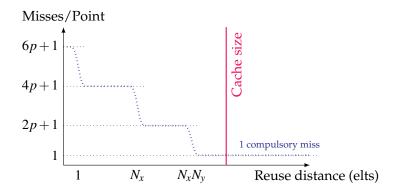

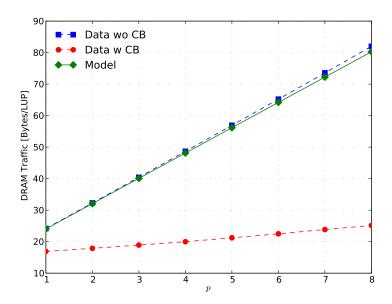

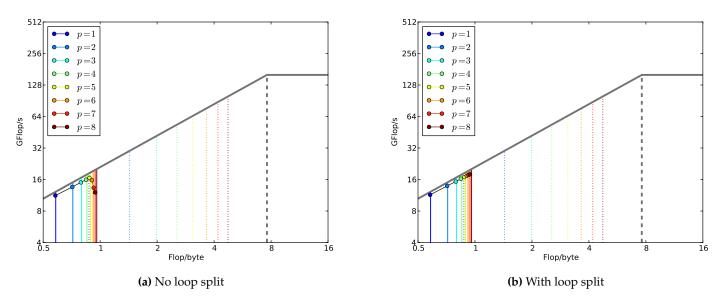

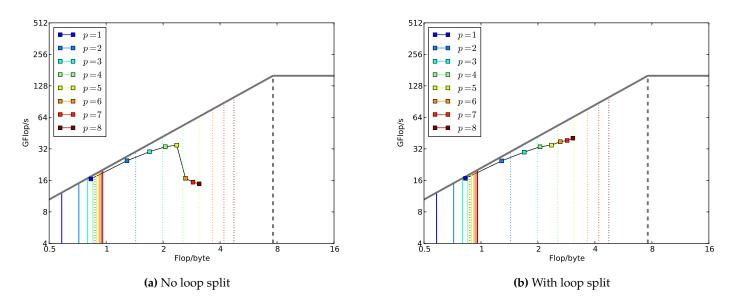

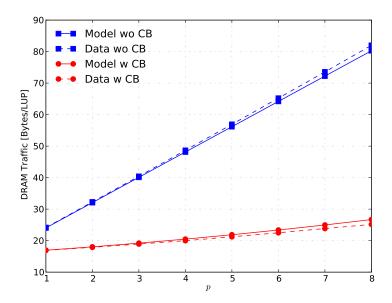

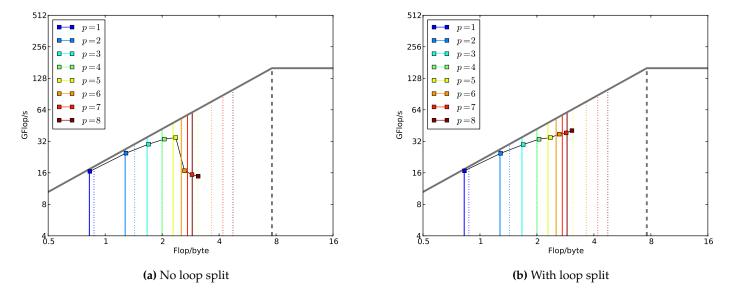

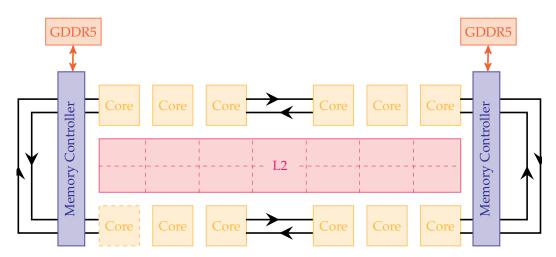

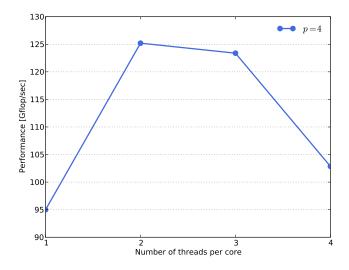

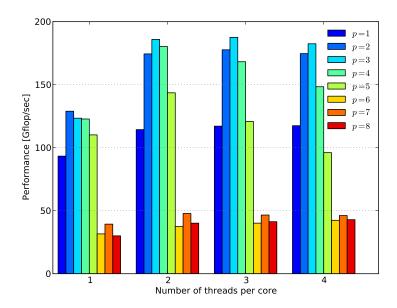

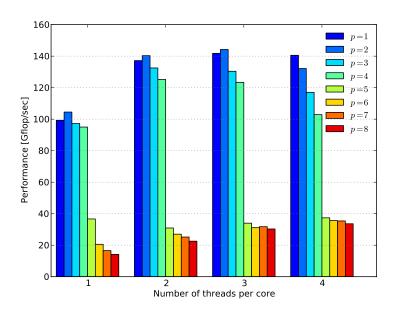

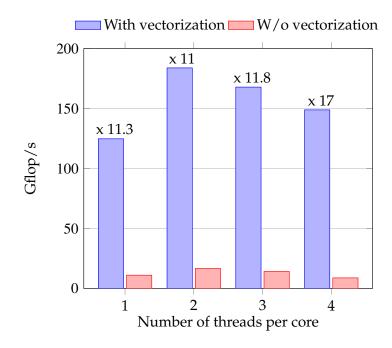

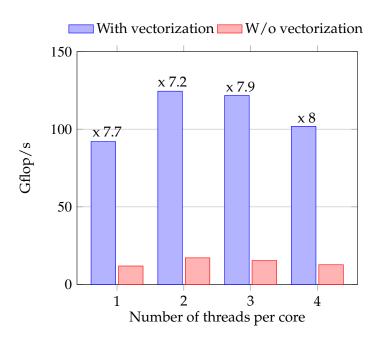

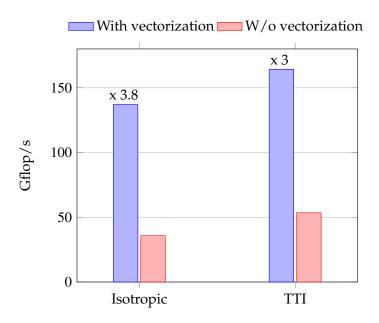

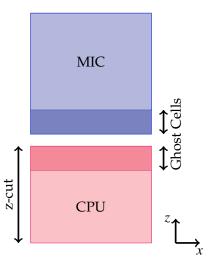

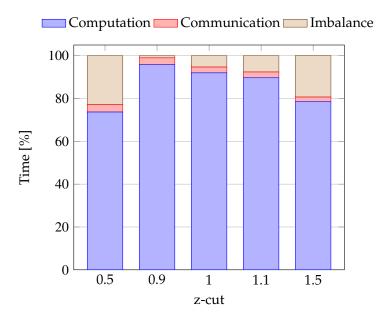

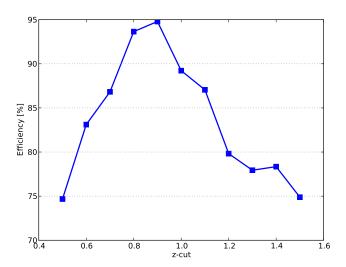

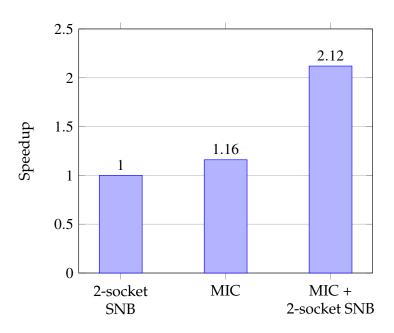

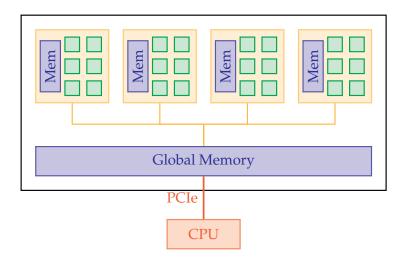

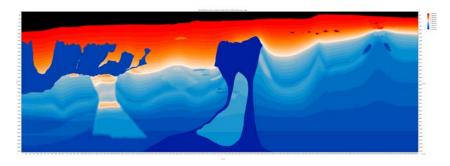

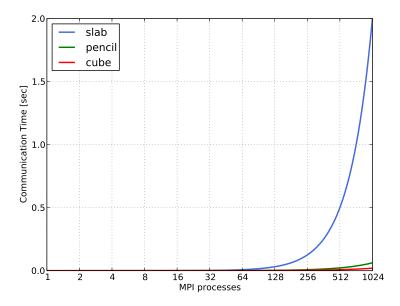

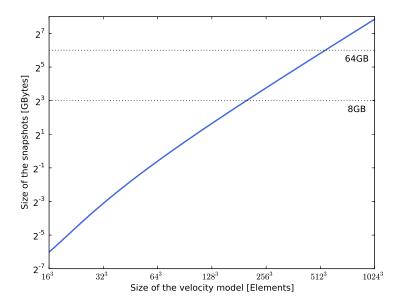

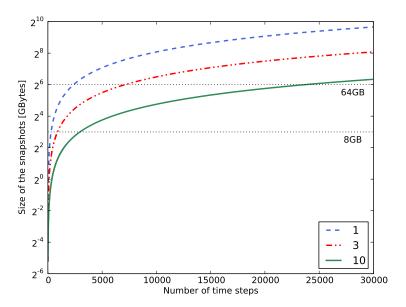

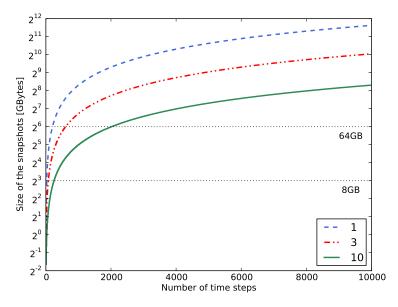

Finite-difference methods can be applied in both frequency and time domains. Frequency domain may be more efficient in inversion problems than time domain when multiple source locations are used [Pratt, 1999; Virieux et al., 2009; Operto et al., 2009]. In the case of forward modeling, time domain is widely used since it is more adapted to the computation requirements of such applications [Moczo et al., 2007; Virieux et al., 2011].