# Bipartite edge coloring approach for designing parallel hardware interleaver architecture

Sani Awais Hussein

#### ▶ To cite this version:

Sani Awais Hussein. Bipartite edge coloring approach for designing parallel hardware interleaver architecture. Hardware Architecture [cs.AR]. Université de Bretagne Sud, 2012. English. NNT: . tel-00790045

### HAL Id: tel-00790045 https://theses.hal.science/tel-00790045

Submitted on 19 Feb 2013

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre: 261

#### **THESE**

pour obtenir le grade de :

#### DOCTEUR DE L'UNIVERSITE DE BRETAGNE SUD

**Spécialité** : Sciences de l'ingénieur **Mention** : Electronique et Informatique Industrielle

#### **AWAIS HUSSAIN SANI**

# Bipartite edge coloring approach for designing parallel hardware interleaver architecture

Soutenue publiquement le 11 mai 2012

#### **COMPOSITION DU JURY**

| E. Casseau      | Rennes 1 / ENSSAT            | Rapporteur            |

|-----------------|------------------------------|-----------------------|

| C. Jego         | ENSEIRB                      | Rapporteur            |

| J-L. Danger     | Telecom ParisTech            | Examinateur           |

| D. Gnaedig      | Turboconcept                 | Examinateur           |

| F. Kienle       | Technical University of      | Examinateur           |

|                 | Kaiserslautern               |                       |

| Cyrille Chavet  | Université de Bretagne Sud   | Encadrant             |

| Philippe Coussy | Université de Bretagne Sud   | Co-directeur de Thèse |

| Eric Martin     | Recteur Académie de Besançon | Direction de Thèse    |

Laboratoire en sciences et techniques de l'information, de la communication et de la connaissance (Lab-STICC) Université de Bretagne Sud

# Acknowledgment

First of all, i want to thank my Ph.d. supervisors Philippe COUSSY and Cyrille CHAVET for providing me a change to work on this thesis and for guiding me to complete it. Looking back the three years in my PhD program, now I can actually sense the beauty behind the research of new approaches. I gratefully acknowledge Philippe and Cyrille for their advice, supervision, and crucial contributions, which made them a backbone of this thesis work. I have learnt a lot both professionally and personally from their involvement in my PhD, their originality has triggered and nourished my intellectual maturity which I will benefit from for a long time to come. I express all my gratitude to prof. Christophe JEGO and prof. Emmanuel CASSEAU for honoring us by accepting the difficult task of being reviewer of this thesis.

I would also like to thank my family especially my mother who inspired and supported me all these years of my life, my wife for being a constant source of support throughput my stay in France. I would also like to acknowledge all my colleagues at Lab-STICC in France for making my PhD a enjoyable experience. In particular, I'd like to thank Saeed ur REHMAN at Lab-STICC for helping me during my research on LDPC codes. Lot of thanks to my pakistani friends who worked in Lorient for making my stay a wonderful experience with their love. Finally i would like to thank Life for providing me with this opportunity to explore myself more and grow as a person.

.

## **Table of Contents**

| Chapter 1       | PROBLEMATIC                                                  | 3  |

|-----------------|--------------------------------------------------------------|----|

| 1. Forward Erro | or Correction (FEC) Coding                                   | 5  |

| 2. Convolutiona | l Codes                                                      | 5  |

| 2.1. Convolu    | ıtional Encoder                                              | 6  |

| 2.2. Convolu    | tional Code state and Trellis Diagram                        | 7  |

|                 | g Convolutional Codes                                        |    |

|                 | odes                                                         |    |

| 2.4.1. Turbo    | Encoder                                                      | 10 |

| 2.4.2. Interle  | aver                                                         | 11 |

|                 | Decoder                                                      |    |

| 2.4.4. Paralle  | elism in Turbo Codes Decoding                                | 12 |

|                 | rsive Unit Parallelism                                       | _  |

|                 | is Level Parallelism                                         |    |

|                 | Decoder Level Parallelism                                    |    |

|                 | lusion                                                       |    |

| 3. Block Codes  |                                                              | 15 |

|                 | g of Linear Block Codes                                      |    |

|                 | nsity Parity Check (LDPC) Codes                              |    |

|                 | Graph Representation                                         |    |

|                 | g                                                            |    |

|                 | entation of LDPC Decoder                                     |    |

| •               | Parallel Implementation                                      |    |

| •               | Serial Implementation                                        |    |

|                 | ly Parallel Implementation                                   |    |

| 4. Memory conf  | •                                                            | 22 |

|                 | conflict problem for Turbo Codes                             |    |

|                 | conflict problem for LDPC Codes                              | 24 |

| 5. Conclusion   |                                                              | 26 |

| Chapter 2       | STATE OF THE ART                                             | 27 |

| 1. Introduction |                                                              | 29 |

|                 | o tackles memory conflict problem for turbo and LDPC codes - |    |

| 2.1. Conflict   | Free Interleaving laws                                       | 30 |

|                 | ecture aware Turbo Codes                                     |    |

|                 | ured LDPC Codes                                              |    |

|                 | ne Conflict Resolution                                       |    |

|                 | ime Conflict Resolution for Turbo Codes                      |    |

|                 | ime Conflict Resolution for LDPC Codes                       |    |

| 2.3. Design     | Γime Conflict Resolution                                     | 38 |

| 2.3.1. Design                                         | Time Conflict Resolution for Turbo Codes                   | 38              |  |

|-------------------------------------------------------|------------------------------------------------------------|-----------------|--|

| 2.3.2. Design Time Conflict Resolution for LDPC Codes |                                                            |                 |  |

| 2.4. Conclusi                                         | on                                                         | 41              |  |

|                                                       | e Coloring of Graph                                        |                 |  |

|                                                       | heory                                                      |                 |  |

|                                                       | Graph                                                      |                 |  |

|                                                       | ct Graph for Turbo Codes                                   |                 |  |

|                                                       | et Graph for LDPC Codes                                    |                 |  |

|                                                       | Graph                                                      |                 |  |

| -                                                     | te Edge Coloring                                           |                 |  |

|                                                       | g Method to color the edges of Bipartite Graph             |                 |  |

|                                                       | w Method to color the edges of Bipartite Graph             |                 |  |

|                                                       | n Problem                                                  |                 |  |

| Chapter 3                                             | METHODS BASED ON BIPARTITE GRAPH FOR SOLV                  | VING            |  |

|                                                       | MEMORY MAPPING PROBLEMS                                    | 55              |  |

| 1. Introduction                                       | 1                                                          | 57              |  |

| 2. A Methodolo                                        | ogy based on Transportation Problem Modeling for Designin  | ıg Parallel     |  |

| Interleaver Arch                                      |                                                            | 57              |  |

| 2.1. Problem                                          | Formulation for Memory Mapping Problem of Turbo codes      | 58              |  |

|                                                       | g                                                          |                 |  |

| · · · · · · · · · · · · · · · · · · ·                 | uction of Bipartite Graph                                  |                 |  |

|                                                       | ormation of bipartite graph into Transportation Matrix     |                 |  |

|                                                       | m to find semi 2-factors in Turbo Bipartite Graph          |                 |  |

|                                                       | ical Example to explain algorithm                          |                 |  |

|                                                       | s Based on Bipartite Graph to find conflict Free Memory Ma |                 |  |

|                                                       |                                                            |                 |  |

| 3.1. Problem                                          | Formulation for Memory Mapping Problem of LDPC codes       | 66              |  |

| 3.2. Modeling                                         | g                                                          | 67              |  |

| 3.3. Algorithm                                        | m                                                          | 68              |  |

| 3.3.1. Partition                                      | on the Bipartite Graph                                     | 69              |  |

| 3.3.2. Colorii                                        | ng edges of Bipartite Graph                                | 70              |  |

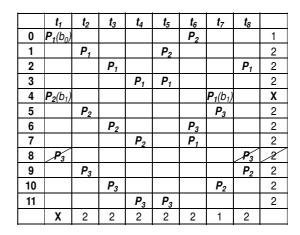

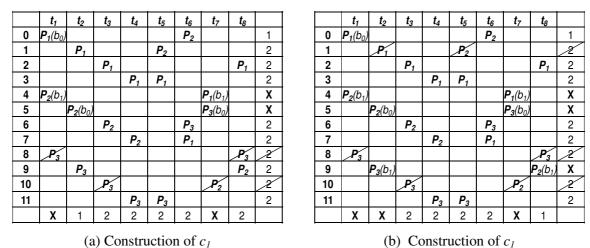

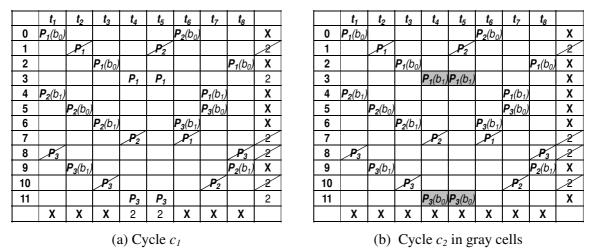

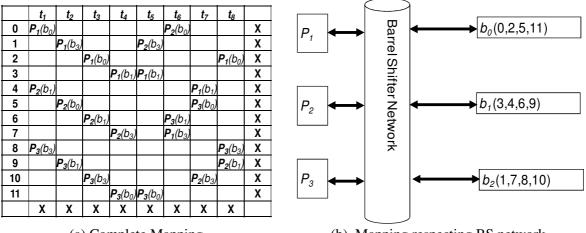

|                                                       | ical Example to explain algorithm                          |                 |  |

| 4. Conclusion                                         |                                                            | 75              |  |

| Chapter 4                                             | METHODS BASED ON TRIPARTITE GRAPH FOR SOIL                 |                 |  |

|                                                       | MEMORY MAPPING PROBLEMS                                    | 77              |  |

| 1. Introduction                                       |                                                            | 79              |  |

| 2. Methodology I<br>LDPC                              | Based on Tripartite Graph to find conflict Free Memory Ma  | pping for<br>79 |  |

| 2.1. Modeling                                         | g                                                          | 80              |  |

| 2.2. 2-Step C                | oloring Approach                                            | 82       |

|------------------------------|-------------------------------------------------------------|----------|

| •                            | ical Example to explain algorithm                           |          |

|                              | Bipartite Graph for Turbo and LDPC Codes                    | 87       |

| 3.1. Construc                | tion of Bipartite Graph for Mapping Problem of Turbo Codes  | 88       |

| 3.2. Construc                | tion of Bipartite Graph for Mapping Problem of LDPC Codes   | 89       |

|                              | Edge Coloring Algorithm                                     |          |

|                              | ical Example to explain algorithm                           | 93       |

| 4. Complexity co             | mparison of Different algorithms                            | 96       |

| 5. Conclusion                |                                                             | 97       |

| Chapter 5                    | EXPERIMENTS                                                 | 99       |

| 1. Introduction              |                                                             | 101      |

| 2. Design Flow for           | or Memory Mapping Tool                                      | 102      |

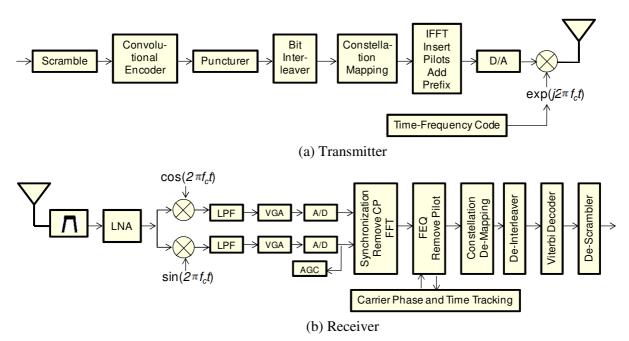

| 3. Ultra Wide Ba             | and Communication System                                    | 103      |

| 3.1. Bit Interl              | eaver used in WPAN IEEE 802.15.3a Physical Layer            | 103      |

| 3.2. Experiments and Results |                                                             |          |

| _                            | allel Interleaver Architecture for Turbo Decoder            | 107      |

| 4.1. Interleav               | er used in HSPA Evolution                                   | 107      |

| 5. Designing Par             | tially Parallel Architecture for LDPC Decoder               | 112      |

| 5.1. Partially               | Parallel Architecture for structured LDPC codes             | 112      |

| 5.2. Decoder                 | Architecture for Non-Binary LDPC codes                      | 116      |

| 6. Case Study: D             | esigning Parallel architecture for Quadratic Permutation Po | lynomial |

| Interleaver                  |                                                             | 119      |

|                              | ations used in this study                                   |          |

| -                            | ents and Results                                            | 121      |

| 7. Conclusion                |                                                             | 124      |

| Conclusion an                | d Future Perspectives                                       | 125      |

| Bibliography                 |                                                             | 129      |

| Annexure                     |                                                             | 135      |

# **List of Figures**

| Figure 1. 1. Communication System                                                                 | 5    |

|---------------------------------------------------------------------------------------------------|------|

| Figure 1. 2. Convolutional Encoder                                                                | 7    |

| Figure 1. 3. State Diagram                                                                        | 8    |

| Figure 1. 4. Trellis Diagram                                                                      | 9    |

| Figure 1. 5. Turbo Encoder                                                                        | 11   |

| Figure 1. 6. Turbo Decoder                                                                        | 12   |

| Figure 1. 7. Serial Implementation of Turbo Decoder                                               | 12   |

| Figure 1. 8. Recursive Unit Parallelism                                                           |      |

| Figure 1. 9. Trellis Level Parallelism                                                            | 14   |

| Figure 1. 10. SISO Decoder Level Parallelism                                                      | 14   |

| Figure 1. 11. Systematic format of a codeword                                                     | 16   |

| Figure 1. 12. Encoder circuit for the (7, 4) Systematic code                                      | 17   |

| Figure 1. 13. Tanner Graph representation of H                                                    | 19   |

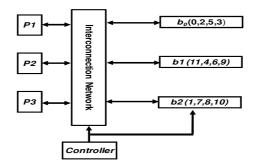

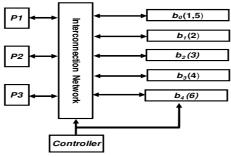

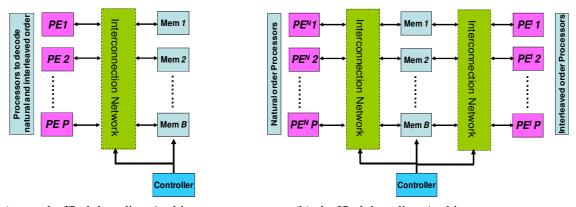

| Figure 1. 14. Partially Parallel Architecture                                                     | 23   |

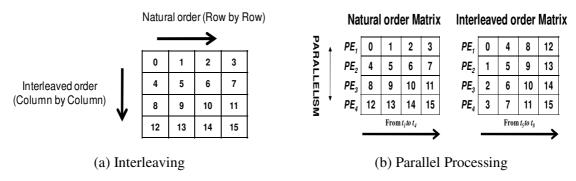

| Figure 1. 15. Parallel Processing of Turbo Codes                                                  | 24   |

| Figure 1. 16. Memory Conflict Problem in Parallel Turbo Decoder                                   | 24   |

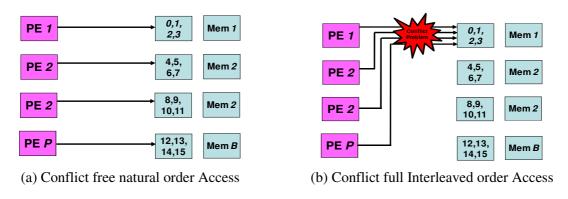

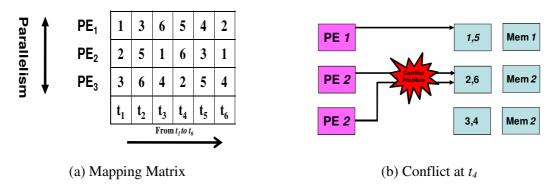

| Figure 1. 17. Memory Conflict Problem in Partially Parallel LDPC Decoder                          | 25   |

| Figure 2. 1. Temporal and Spatial Permutation for interleaver construction                        |      |

| Figure 2. 2. H matrix Representation                                                              | . 32 |

| Figure 2. 3. $H_{Base}$ Matrix for WiMax Standard of code word size = 576, $Z = 24$ and $r = 1/2$ | . 33 |

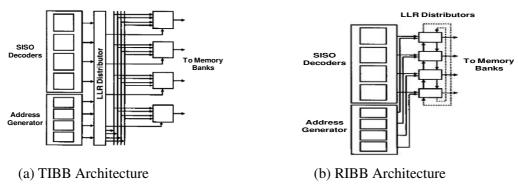

| Figure 2. 4. LLR Distributor Architecture                                                         | 34   |

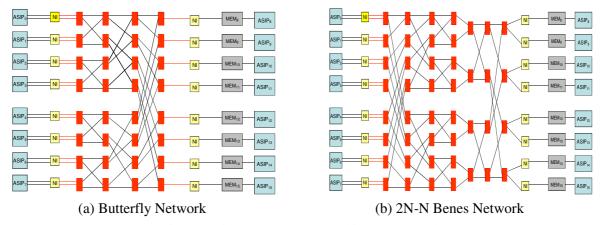

| Figure 2. 5. Heterogeneous Multistage Network                                                     |      |

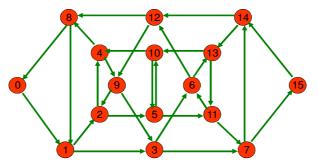

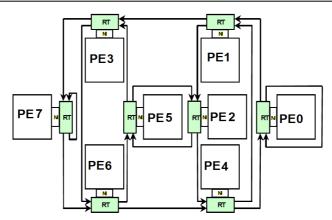

| Figure 2. 6. Binary de Bruijn graph with 16 nodes                                                 | 36   |

| Figure 2. 7. 8-Processor de Bruijn network with processors, routers and network interfaces        |      |

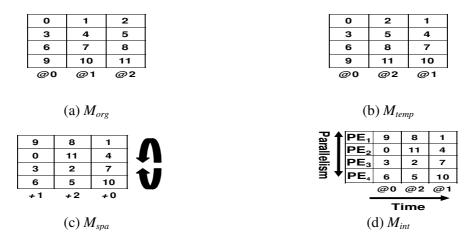

| Figure 2. 8. Matrices used in [TAR04]                                                             |      |

| Figure 2. 9. Matrices used in SAGE                                                                | 40   |

| Figure 2. 10. MAP matrix for Multiple Read Multiple write (MRMW) approach                         | 41   |

| Figure 2. 11. Graph Representation                                                                |      |

| Figure 2. 12. Conflict Graph for Turbo Decoder                                                    |      |

| Figure 2. 13. Resultant architecture                                                              | 45   |

| Figure 2. 14. Conflict Graph for LDPC Decoder                                                     | 46   |

| Figure 2. 15. Resultant Architecture                                                              | 46   |

| Figure 2. 16. Graph Representation                                                                |      |

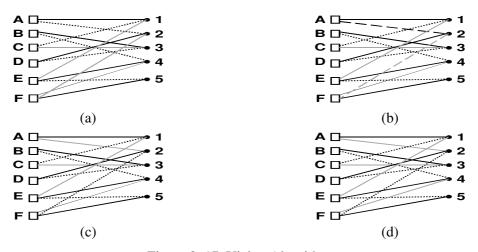

| Figure 2. 17. Vizing Algorithm                                                                    |      |

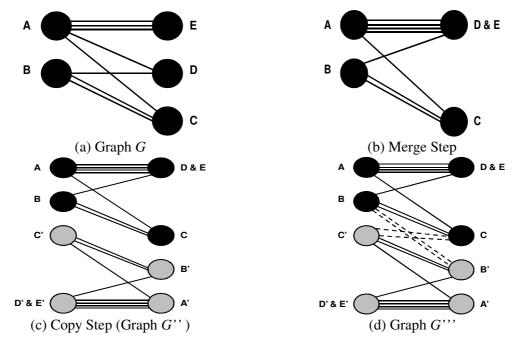

| Figure 2. 18. Constructing $\Delta$ -regular graph                                                |      |

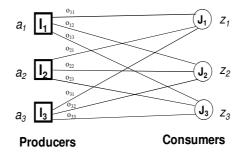

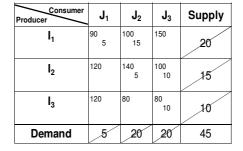

| Figure 2. 19. Network Model of Transportation Problem for 3 producers and 3 consumers             |      |

| Figure 2. 20. Matrix Model of Transportation Problem for 3 producers and 3 consumers              |      |

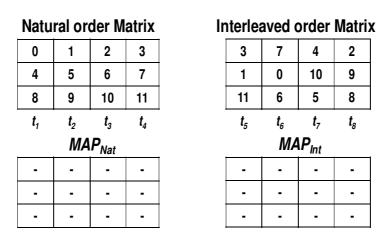

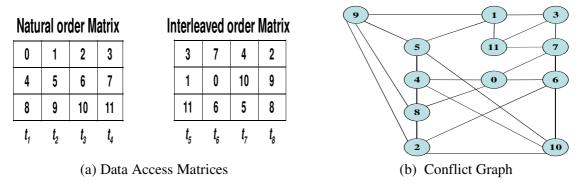

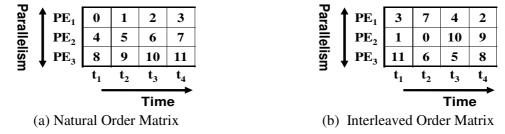

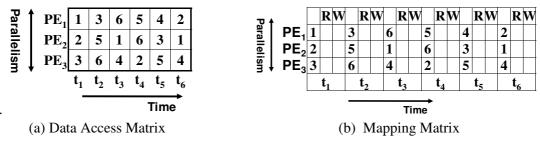

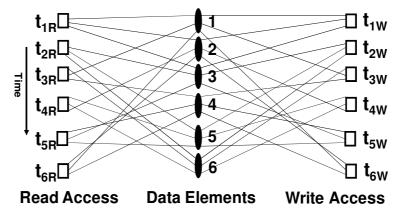

| Figure 3. 1: Data Access Matrices for Turbo Codes                                                 |      |

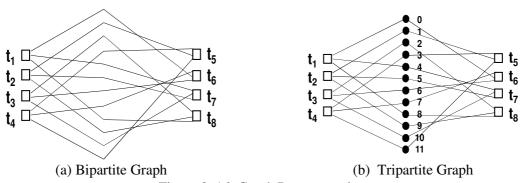

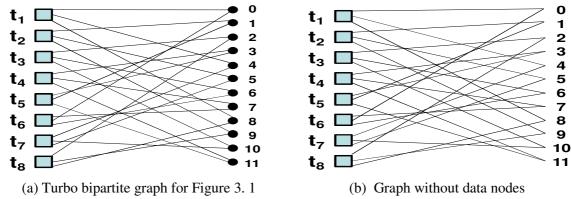

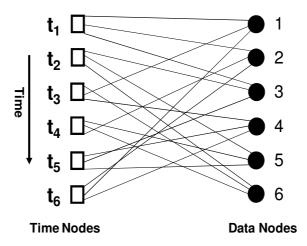

| Figure 3. 2: Bipartite Graph representation                                                       |      |

| Figure 3. 3: Matrix Model for Transportation Problem of Figure 3. 2.a                             |      |

| Figure 3. 4: partitioning algorithm                                                               |      |

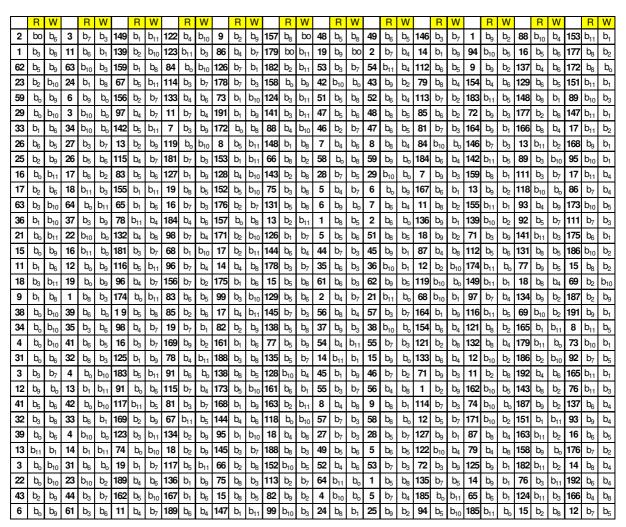

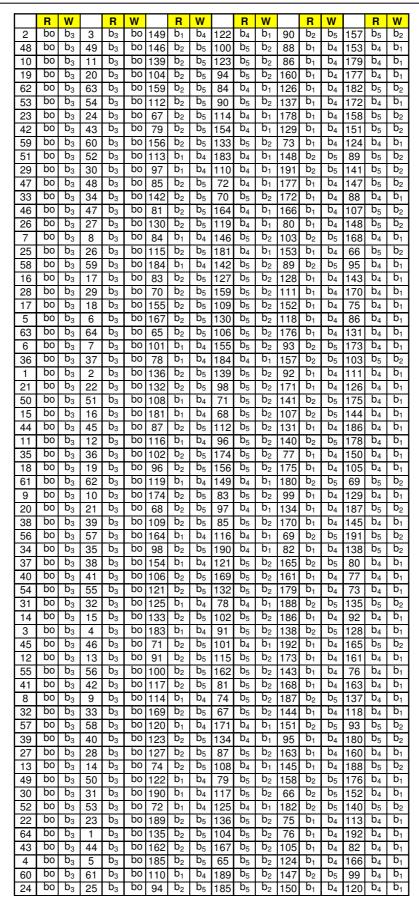

| Figure 3. 5: Assignment of memory banks in Transportation matrix                                  |      |

| Figure 3. 6: Assignment of memory banks in Transportation matrix                                  | 64   |

| Figure 3. 7: Assignment of memory banks in Transportation matrix                                | 64  |

|-------------------------------------------------------------------------------------------------|-----|

| Figure 3. 8: Resultant Memory Mapping                                                           | 65  |

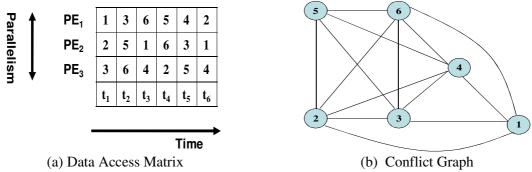

| Figure 3. 9: Data Access Matrices for LDPC Codes                                                | 67  |

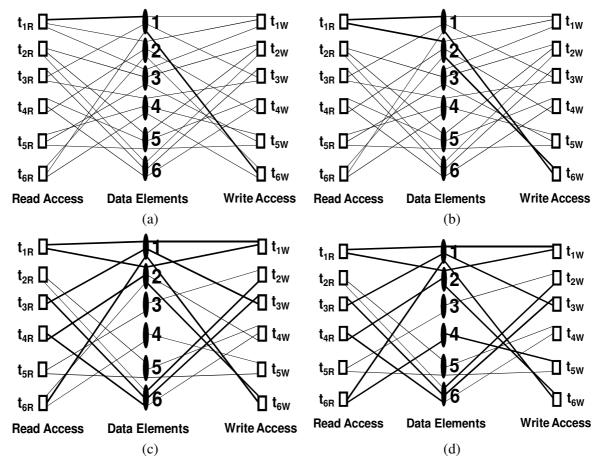

| Figure 3. 10: Bipartite Representation of Data Access Matrix of Figure 3. 9.a                   | 68  |

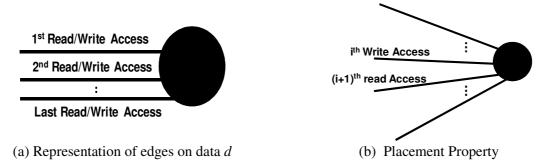

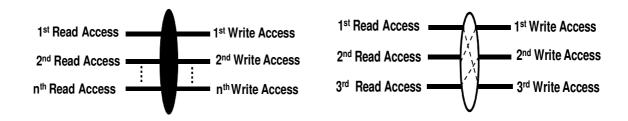

| Figure 3. 11: Representation of edges on data node <i>d</i>                                     | 68  |

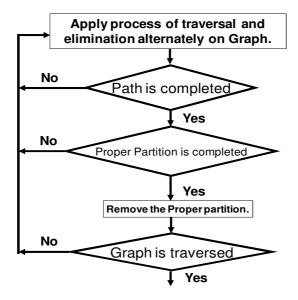

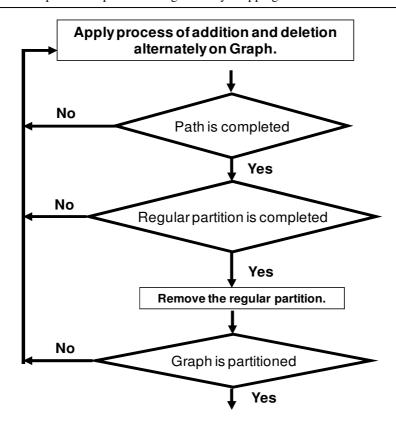

| Figure 3. 12: Partitioning Algorithm                                                            | 70  |

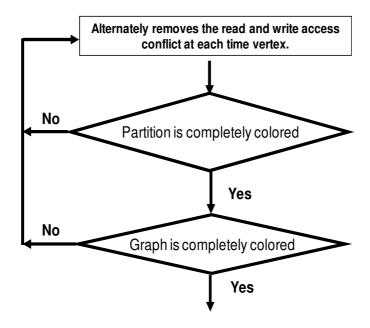

| Figure 3. 13: Coloring Algorithm                                                                | 71  |

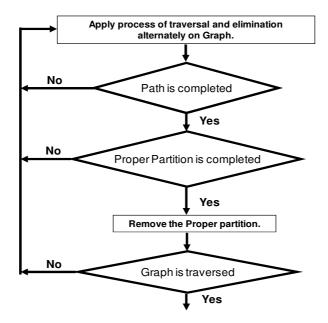

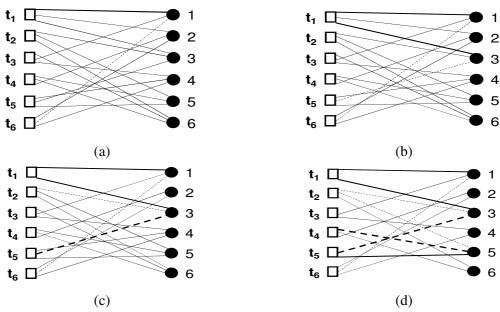

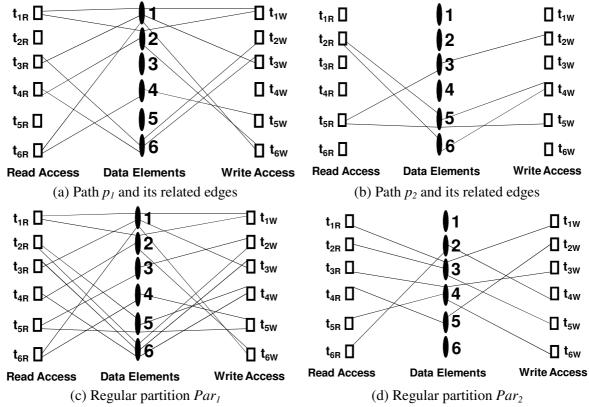

| Figure 3. 14: Path construction through Partitioning Algorithm                                  | 72  |

| Figure 3. 15: Path construction through Partitioning Algorithm                                  | 73  |

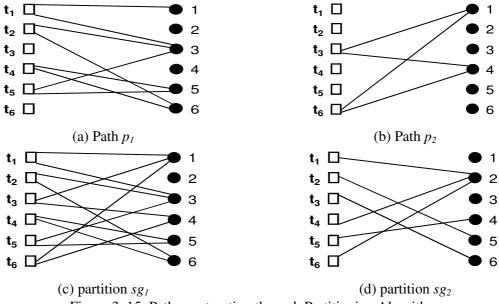

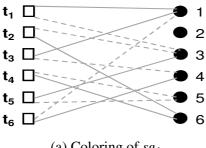

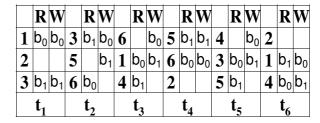

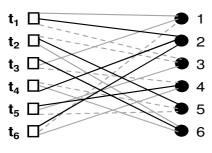

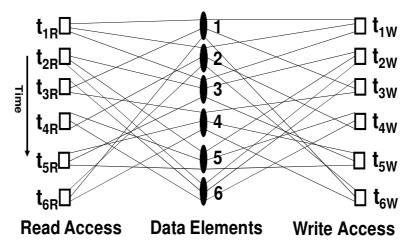

| Figure 3. 16: Conflict free edge coloring of $sg_1$                                             | 74  |

| Figure 3. 17: Conflict free edge coloring of $sg_1$                                             | 74  |

| Figure 3. 18: Conflict free edge coloring of <i>G</i> and corresponding mapping                 | 74  |

| Figure 4. 1: Tripartite graph for mapping matrix of Figure 3.9                                  | 80  |

| Figure 4. 2: Single Node Representation on Tripartite graph                                     | 81  |

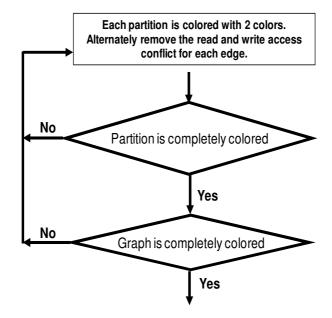

| Figure 4. 3: Partitioning Algorithm                                                             | 83  |

| Figure 4. 4: Coloring Algorithm                                                                 | 84  |

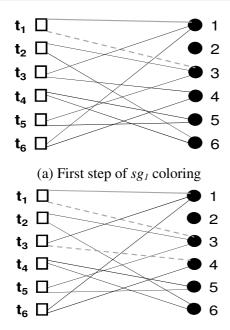

| Figure 4. 5: Path construction through Partitioning Algorithm                                   | 85  |

| Figure 4. 6: Path construction through Partitioning Algorithm                                   | 86  |

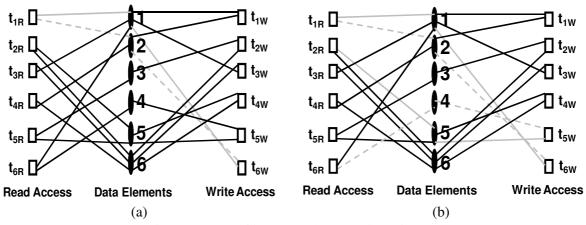

| Figure 4. 7: Conflict Free Edge Coloring of <i>Par</i> <sub>1</sub>                             | 86  |

| Figure 4. 8: Conflict Free Edge Coloring of <i>Par</i> <sub>1</sub> and <i>Par</i> <sub>2</sub> | 87  |

| Figure 4. 9: Conflict free edge coloring of <i>G</i> and corresponding mapping matrix           | 87  |

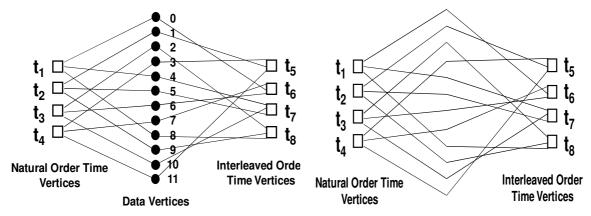

| Figure 4. 10: Bipartite Graph representation                                                    | 88  |

| Figure 4. 11: Tripartite graph for mapping matrix of Figure 3.9                                 | 89  |

| Figure 4. 12: Bipartite graph for mapping matrix of Figure 3.2.b.                               | 90  |

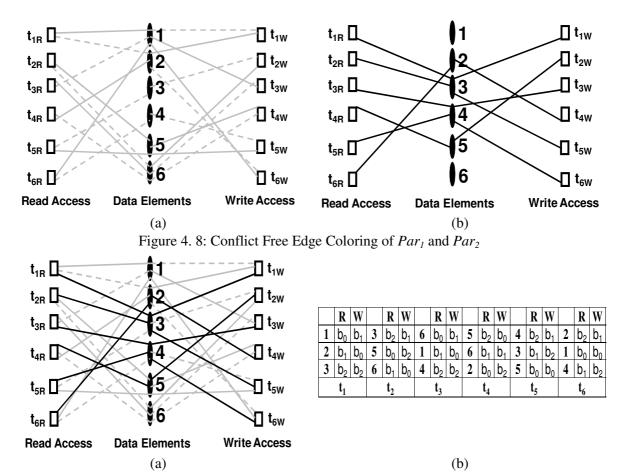

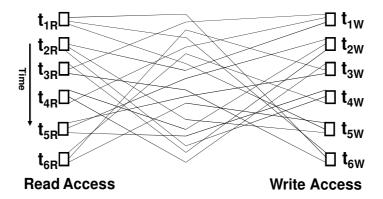

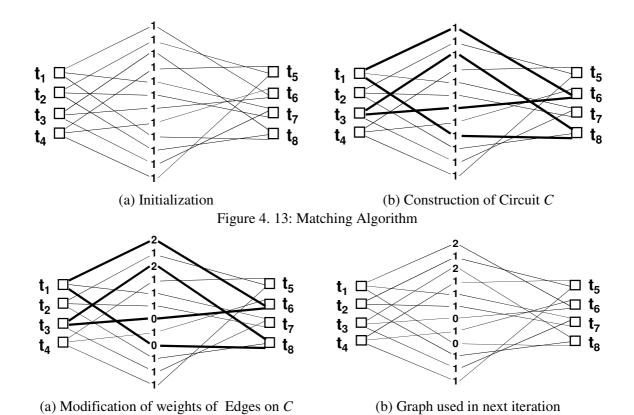

| Figure 4. 13: Matching Algorithm                                                                | 93  |

| Figure 4. 14: Matching Algorithm                                                                | 93  |

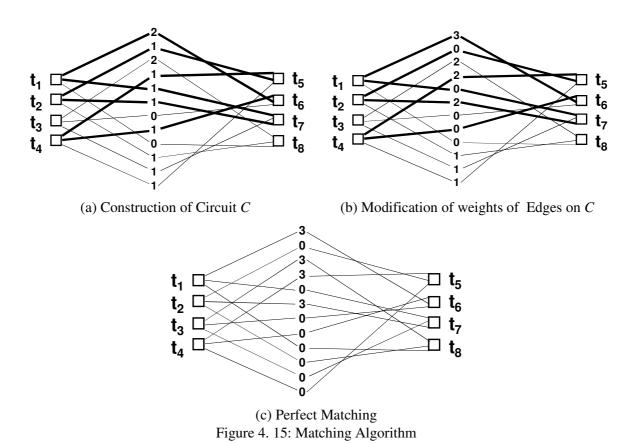

| Figure 4. 15: Matching Algorithm                                                                | 94  |

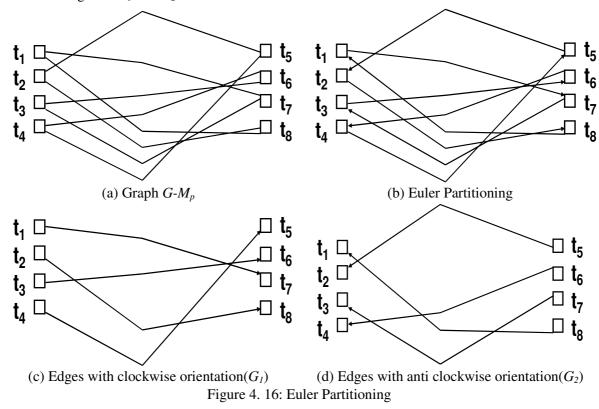

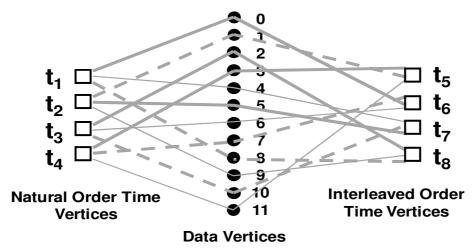

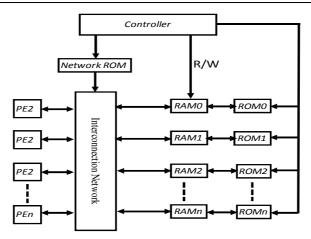

| Figure 4. 16: Euler Partitioning                                                                | 95  |

| Figure 4. 17: Edge Coloring of Bipartite Graph                                                  | 95  |

| Figure 5. 1. Design Flow for performing experiments                                             | 102 |

| Figure 5. 2. Resultant generated architecture                                                   | 103 |

| Figure 5. 3. Multiband OFDM System [BAT04] (Copyright @ 2004 IEEE)                              | 104 |

| Figure 5. 4. Input and Interleaved order for 30 bits                                            | 105 |

| Figure 5. 5. Implementation of Bit Interleaver                                                  | 105 |

| Figure 5. 6. Comparison of two different architectures                                          | 107 |

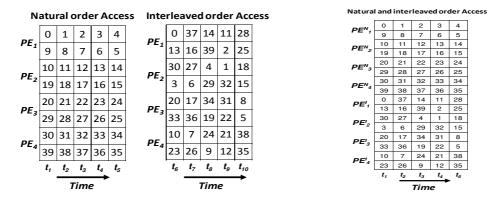

| Figure 5. 7. Arrangement of $K = 44$ data into 5*10 matrix                                      | 109 |

| Figure 5. 8. Matrix after Intra-row Permutation                                                 | 110 |

| Figure 5. 9. Matrix after Inter-row Permutation                                                 | 110 |

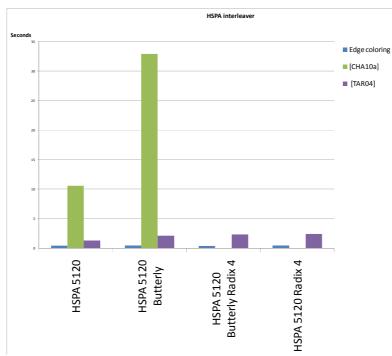

| Figure 5. 10. Comparison of CPU time for various Mapping Approaches                             | 111 |

| Figure 5. 11. $H_{Base}$ Matrix for WiMAX Standard of code word size = 576, Z = 24 and r = 1/2  | 113 |

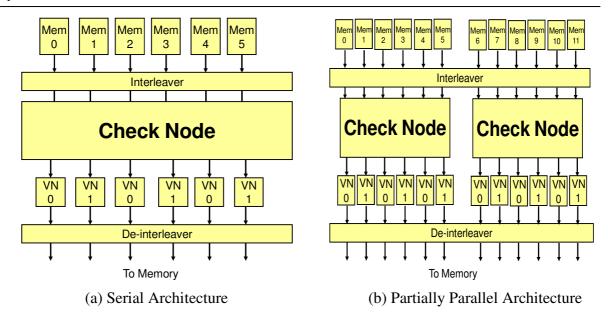

| Figure 5. 12. Partially parallel architecture for ½ Rate WiMAX standard                         | 113 |

| Figure 5. 13. Data Access Matrix for ½ Rate WiMAX standard                                      | 114 |

| Figure 5. 14. Resultant Mapping for data access matrix of Figure 5. 12                          | 114 |

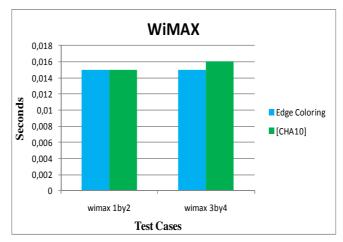

| Figure 5. 15. Comparison of CPU time for various Mapping Approaches                             | 115 |

| Figure 5. 16. Architecture for NB-LDPC                                                          | 117 |

|                                                                                                 |     |

| Figure 5. 18.Data Access Matrix for $D = 192$ and $d_c = 6$ using Partially Parallel Architecture | . 118 |

|---------------------------------------------------------------------------------------------------|-------|

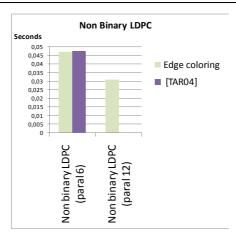

| Figure 5. 19. Comparison of CPU time for various Mapping Approaches                               | . 119 |

| Figure 5. 20. Decoding Architecture for Turbo Decoders                                            | . 120 |

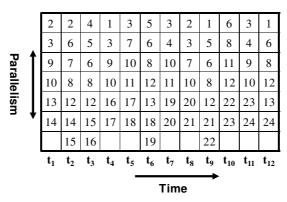

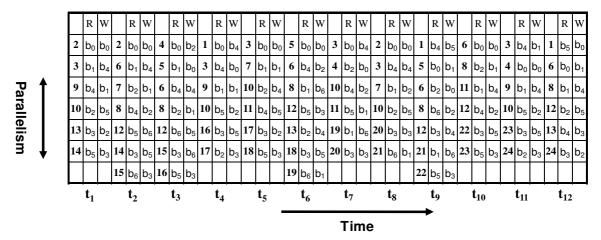

| Figure 5. 21. Scheduling for Turbo Decoding                                                       | . 121 |

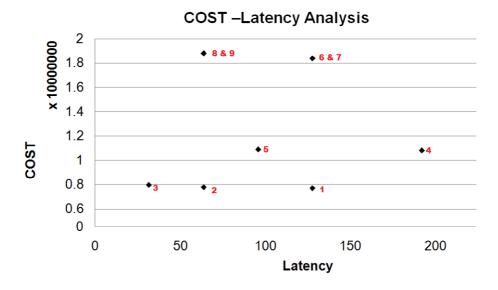

| Figure 5. 22. Latency and cost Analysis for all configurations                                    | . 123 |

## **List of Tables**

| Table 1. 1: State Transition Table                                                                | 8   |

|---------------------------------------------------------------------------------------------------|-----|

| Table 1. 2: Linear block code with $x = 4$ and $c = 7$ .                                          | 16  |

| Table 4. 1: Edge Coloring Algorithm                                                               | 91  |

| Table 4. 2: Perfect Matching Algorithm from [SCH98]                                               | 91  |

| Table 4. 3: Euler Partitioning Algorithm from [GAB76]                                             | 92  |

| Table 4. 4: Complexity Comparison of approaches used in this thesis                               | 96  |

| Table 5. 1. CPU time (second) for various Memory Mapping Approaches                               | 106 |

| Table 5. 2. Resultant area of different components for parallel implementation of bit interleaver | 106 |

| Table 5. 3. List of prime number $p$ and associated primitive root $v$                            | 108 |

| Table 5. 4. CPU time (seconds) for various Memory Mapping Approaches                              | 111 |

| Table 5. 5. Resultant area (in number of Nand-gates) of different components for different types  | 112 |

| Table 5. 6. CPU time (seconds) for various Memory Mapping Approaches                              | 114 |

| Table 5. 7. Resultant area of different components for structured LDPC Decoder Architecture       | 115 |

| Table 5. 8. CPU time for various Memory Mapping Approaches                                        | 118 |

| Table 5. 9. Resultant area of different components for NB-LDPC Decoder Architecture               | 119 |

| Table 5. 10. Different configuration to explore the design space for turbo decoding               | 121 |

| Table 5. 11. Comparison of Configuration 1 and 4 for latency                                      | 122 |

| Table 5. 12. Comparison of all the configurations for hardware cost and latency                   | 122 |

| Table 5. 13. Resultant area for different configurations used in case study                       | 123 |

### **INTRODUCTION**

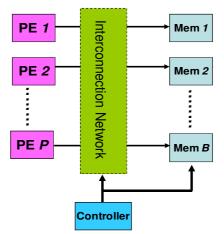

Nowadays, Turbo and LDPC codes are two families of codes that are extensively used in current communication standards due to their excellent error correction capabilities. However, hardware design of coders and decoders for high data rate applications is not a straightforward process. For high data rates, decoders are implemented on parallel architectures in which more than one processing elements decode the received data. To achieve high memory bandwidth, the main memory is divided into smaller memory banks so that multiple data values can be fetched from or stored to memory concurrently. However, due to scrambling caused by interleaving law, this parallelization results in communication or memory access conflicts which occur when multiple data values are fetched from or stored in the same memory bank at the same time. This problem is called *Memory conflict Problem*. It increases latency of memory accesses due to the presence of conflict management mechanisms in communication network and unfortunately decreases system throughput while augmenting system cost.

To tackle the memory conflict problems, three different types of approaches are used in literature. In first type of approaches, different algorithms to construct conflict free interleaving law are proposed. The main reason to develop these techniques is to construct "architecture friendly" codes with good error correction capabilities in order to reduce hardware cost. However, architectural constraints applied during code design may impede error correction performance of the codes. In a second type of approaches, different design innovations are introduced to tackle memory conflict problem. Flexible and scalable interconnection network with sufficient path diversity and additional storing elements are introduced to handle memory conflicts. However, flexible networks require large silicon area and cost. In addition, delay introduced due to conflict management mechanisms degrades the maximum throughput and makes these approaches inefficient for high data rate and low power applications. In third type of approaches deals with algorithms that assign data in memory in such a manner that all the processing elements can access memory banks concurrently without any conflict. The benefit of this technique is that decoder implementation does not need any specific network and extra storage elements to support particular interleaving law. However, till now no algorithm exists that can solve memory mapping problem for both turbo and LDPC codes in polynomial time.

The work presented in this thesis belongs to the last type of approaches. We propose several methods based on graph theory to solve memory mapping problem for both turbo and LDPC codes. Different formal models based on bipartite and tripartite graphs along with different algorithms to color the edges of these graphs are detailed. The complete path we followed before it is possible to solve mapping problem in polynomial time is hence presented. For the first two approaches, mapping problem is modeled as bipartite graph and then each graph is divided into different sub-graphs in order to facilitate the coloring of the edges. First approach deals with Turbo codes and uses transportation problem algorithms to divide and color the bipartite graph. It can find memory mapping that supports particular interconnection network if the interleaving rule of the application allows it. Second approach solves memory mapping problem for LDPC codes using two different complex algorithms to partition and color each partition. In the third algorithm, each time instance and edge is divided into two parts to model our problem as tripartite graph. Tripartite

graph is partitioned into different sub-graphs by using an algorithm based on divide and conquer strategy. Then each subgraph is colored individually by using a simple algorithm to find a conflict free memory mapping for both Turbo and LDPC codes. Finally, in the last approach tripartite graph is transformed into bipartite graph on which coloring algorithm based on Euler partitioning principle is applied to find memory mapping in polynomial time.

Several experiments have been performed using interleaving laws coming from different communication standards to show the interest of the proposed mapping methods. All the experiments have been done by using a software tool we developed. This tool first finds conflict free memory mapping and then generates VHDL files that can be synthesized to design complete architecture i.e. network, memory banks and associated controllers. In first experiment, bit interleaver used in Ultra Wide Band (UWB) interleaver is considered and a barrel shifter is used as constraint to design the interconnection network. Results are compared regarding area and runtime with state of the art solutions. In second experiments, a turbo interleaving law defined in High Speed Packet Access (HSPA) standard is used as test case. Memory mapping problems have been solved and associated architectures have been generated for this interleaving law which is not conflict free for any type of parallelism used in turbo decoding. Results are compared with techniques used in state of the art in terms of runtime and area. Third experiment focuses on LDPC. First, last algorithm we proposed is used to find conflict free memory mapping for non-binary LDPC codes defined in the DaVinci Codes FP7 ICT European project. Then, conflict free memory mapping have also been found for partially parallel architecture of LDPC codes used in WiMAX and WiFi for different level of parallelism. It is shown that the proposed algorithm can be used to map data in memory banks for any structured codes used in current and future standards for partially parallel architecture. In last experiment, thanks to the proposed approach we explored the design space of Quadratic Permutation Polynomial (QPP) interleaver that is used in 3GPP-LTE standard. The QPP interleaver is maximum contention-free i.e., for every window size W which is a factor of the interleaver length N, the interleaver is contention free. However, when trellis and recursive units parallelism are also included in each SISO, QPP interleaver is no more contention-free. Results highlight tradeoffs between area and performances based on for different radixes, parallelisms, scheduling (replica versus butterfly)...

# **Chapter 1**

### **PROBLEMATIC**

### **Table of Contents**

| 1. Forward Error Correction (FEC) Coding          |    |

|---------------------------------------------------|----|

| 2. Convolutional Codes                            | 5  |

| 2.1. Convolutional Encoder                        | 6  |

| 2.2. Convolutional Code state and Trellis Diagram | 7  |

| 2.3. Decoding Convolutional Codes                 |    |

| 2.4. Turbo Codes                                  | 10 |

| 2.4.1. Turbo Encoder                              | 10 |

| 2.4.2. Interleaver                                |    |

| 2.4.3. Turbo Decoder                              |    |

| 2.4.4. Parallelism in Turbo Codes Decoding        | 12 |

| 2.4.4.1 Recursive Unit Parallelism                | _  |

| 2.4.4.2Trellis Level Parallelism                  | 13 |

| 2.4.4.3 SISO Decoder Level Parallelism            |    |

| 2.4.4.4 Conclusion                                | 15 |

| 3. Block Codes                                    | 15 |

| 3.1. Encoding of Linear Block Codes               | 16 |

| 3.2. Low Density Parity Check (LDPC) Codes        | 17 |

| 3.3. Tanner Graph Representation                  |    |

| 3.4. Decoding                                     |    |

| 3.5. Implementation of LDPC Decoder               |    |

| 3.5.1. Fully Parallel Implementation              |    |

| 3.5.2. Fully Serial Implementation                |    |

| 3.5.3. Partially Parallel Implementation          | 22 |

| 4. Memory conflict problem                        | 22 |

| 4.1. Memory conflict problem for Turbo Codes      | 23 |

| 4.2. Memory conflict problem for LDPC Codes       | 24 |

| 5. Conclusion                                     | 26 |

In this chapter, error correction coding techniques with particular emphasis on Turbo and LDPC codes are discussed. Error correction coding can be classified into two broad categories: convolutional codes and block codes. Chapter starts by presenting encoding and decoding related to convolution codes. Afterwards, brief description of turbo codes that are a subclass of convolutional codes are presented. In the later part of this chapter, block codes with particular emphasis on LDPC codes are explained. Finally, problems in implementing these algorithms on parallel architecture are introduced to highlight the importance of the work presented in this thesis.

### 1. Forward Error Correction (FEC) Coding

Early developers of digital communication systems assumed that information could be transmitted through noisy channel with high reliability by increasing the signal to noise ratio. This can only be achieved at that time by increasing transmitted signal power enough to ensure that signal can reliably be transmitted to source. The revolutionary work of Shannon [SHA48] changed this view by proofing that it is possible to send digital data to receiver through noisy channel with high reliability by first encoding digital message with error correction code at transmitter and then subsequently decode it at receiver to generate original message. The function of the encoder is to map X digits message into C digits codeword where C > X. The code rate r = X/C defines the redundancy introduced by corresponding error correction code. Encoded message passes through channel which corrupts the message by adding some noise into it. At receiver, error correction decoder uses this added redundancy to determine the original message despite the noise introduced by channel. Typical communication system is shown in Figure 1. 1.

Figure 1. 1. Communication System

Different error correction codes are introduced in literature. They can be classified into two broad categories: *Block codes* and *Convolutional codes*. In block codes, original information sequence is divided into different message blocks and each message is independently encoded to generate codeword bits whereas in convolutional codes, encoder takes information sequence as a continuous stream and generates a continuous stream of codeword bits. Therefore in block codes, encoder must wait for the entire message block before it starts encoding whereas convolutional encoder can start encoding and transmitting codeword before it obtains the entire message.

In current telecommunication standards, two error correcting codes, one from block codes (called Low Density Parity Check (LDPC) codes) and the other from convolutional codes (called Turbo codes) are extensively used due to their excellent error correcting capabilities. However, implementation of decoder for these two codes for high data rate applications is not straightforward. In this thesis, we restrict our attention to the implementation of both of these codes on parallel architecture.

#### 2. Convolutional Codes

Convolutional codes perform like a finite state machine which converts continuous stream of X message bits into continuous stream of C coded bits (where X > C). Due to their simple structure and efficiently implementable iterative decoding algorithm, convolutional codes are increasingly used in different telecommunication standards. Currently, convolutional codes are part of standards for mobile communication (HSPA [HSP04], LTE [LTE08]) and digital broadcasting (DVB-SH [DVBS08]).

#### 2.1. Convolutional Encoder

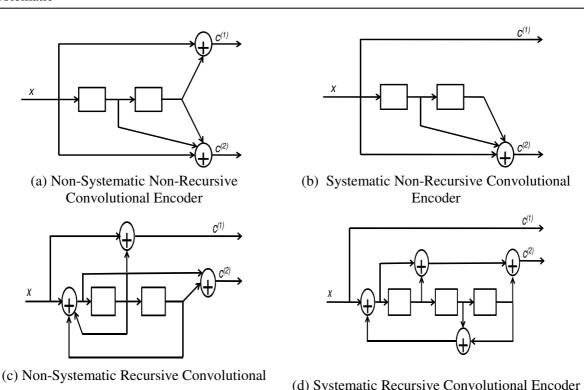

Convolutional encoder consists on modulo-2 adders and shift registers which acts as a memory for past inputs and acts as encoder state. Each shift register contains one or more register element and each register element introduces a delay of one time unit. Due to the presence of these shift registers, output coded bits depend not only on the present message bits but also on the states of encoder i.e., on the already coded message bits.

#### **Definition** Systematic Encoder

A convolutional encoder is called *systematic* if it maps all its input bits directly to the output bits, otherwise it is called *non-systematic*.

In Figure 1. 2.b & d, input bit x is directly map to output bit  $c^{(1)}$ . So, these encoders are example of a systematic encoder.

#### **Definition** Recursive Encoder

A convolutional encoder is called *recursive* if it's state depends on its output, otherwise it is called *non-recursive*.

Recursive Encoder are shown in Figure 1. 2.c & d.

Depending on these definitions, there are four types of convolutional encoders exit:

- 1. Non-systematic non-recursive convolutional encoder (Figure 1. 2.a)

- **2.** Systematic non-recursive convolutional encoder (Figure 1. 2.b)

- **3.** Non-systematic recursive convolutional encoder (Figure 1. 2.c)

- **4.** Systematic recursive convolutional encoder (Figure 1. 2.d)

All these encoders are shown in Figure 1. 2.

Figure 1. 2. Convolutional Encoder

In all of these figures, shift register elements and modulo-2 adders are represented by square blocks and circles respectively. To explain the terminologies used in convolutional codes, we consider the encoder shown in Figure 1. 2.d. This encoder is a part of current 3GPP LTE standard to encode message bits. At time instance t, encoder takes one message bit  $x_t$  and generates two coded bits  $c_t^{(1)}$  &  $c_t^{(2)}$  results into the code rate of ½. Interleaving of coded bits results into the codeword  $\mathbf{c} = [c_I^{(1)} c_I^{(2)}, c_2^{(1)} c_2^{(2)}, c_3^{(1)} c_3^{(2)}, \dots, c_t^{(I)} c_t^{(2)}]$ .

For systematic codes, coded bits are further differentiated into *systematic* and *parity bits*. Input message bits are called systematic bits whereas extra output bits which are not systematic are called parity bits. So for the encoder of Figure 1. 2.d, coded bits  $c_t^{(I)}$  are replaced by message bits  $x^{(I)}$  and coded bits  $c_t^{(2)}$  by parity bits  $p^{(I)}$  to generate the codeword c.

$$\mathbf{c} = [x_1^{(1)} p_1^{(1)}, x_2^{(1)} p_2^{(1)}, x_3^{(1)} p_3^{(1)}, \dots, x_t^{(1)} p_t^{(1)}]$$

#### 2.2. Convolutional Code state and Trellis Diagram

Encoder

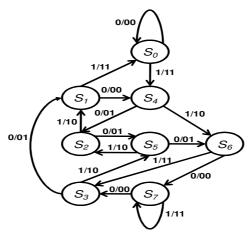

Convolutional encoder can be represented as finite-state machine in which the relationship between input, state and output can be explained through state transition table and state diagram. Encoder discussed in previous section consists of three register elements. So the state of encoder, represented by  $S = (s^{(1)}, s^{(2)}, s^{(3)})$  where  $s^{(1)}, s^{(2)}, s^{(3)} \in \{0,1\}$ , is the contents of three register elements from left to right. If v is the number of elements then there are  $2^v$  possible states in which encoder can be at any time instance. So, the eight possible states for encoder with three register elements are,  $S_0 = (000), S_1 = (001), S_2 = (010), S_3 = (011), S_4 = (100), S_5 = (101), S_6 = (110), S_7 = (111)$ .

For the encoder in discussion, state transition table is shown in Table 1. 1. In this table,  $S_c$  and  $S_n$  are the current and next states respectively and x represents the input message bit which causes this transition. Also the output coded bits generated as a result of transition from  $S_c$  and  $S_n$  are labeled as  $c_{c,n}^{(1)}$  (systematic bit) and  $c_{c,n}^{(2)}$  (parity bit).

| Current state $S_c$                            |                                 | Input x <sub>c,n</sub> | Next State $S_n$                      |                                 | Output $c_{c,n}$                                      |                 |

|------------------------------------------------|---------------------------------|------------------------|---------------------------------------|---------------------------------|-------------------------------------------------------|-----------------|

| $S_c$                                          | $(s_c^{(1)}s_c^{(2)}s_c^{(3)})$ | Х                      | $S_n$                                 | $(S_n^{(1)}S_n^{(2)}S_n^{(3)})$ | $c_{\scriptscriptstyle c,n}^{\scriptscriptstyle (1)}$ | $C_{c,n}^{(2)}$ |

| $S_o$                                          | 000                             | 0                      | $S_o$                                 | 000                             | 0                                                     | 0               |

| $S_o$                                          | 000                             | 1                      | $S_4$                                 | 100                             | 1                                                     | 1               |

| $S_1$                                          | 001                             | 0                      | $S_4$                                 | 100                             | 0                                                     | 0               |

| $S_1$                                          | 001                             | 1                      | $\mathcal{S}_{o}$                     | 000                             | 1                                                     | 1               |

| $S_2$                                          | 010                             | 0                      | $\mathcal{S}_{\scriptscriptstyle{5}}$ | 101                             | 0                                                     | 1               |

| $S_2$                                          | 010                             | 1                      | $S_{\scriptscriptstyle 1}$            | 001                             | 1                                                     | 0               |

| $S_3$                                          | 011                             | 0                      | $S_{\scriptscriptstyle 1}$            | 001                             | 0                                                     | 1               |

| $\mathcal{S}_{\scriptscriptstyle \mathcal{S}}$ | 011                             | 1                      | $\mathcal{S}_{\scriptscriptstyle{5}}$ | 101                             | 1                                                     | 0               |

| $\mathcal{S}_{\scriptscriptstyle{4}}$          | 100                             | 0                      | $S_2$                                 | 010                             | 0                                                     | 1               |

| $\mathcal{S}_{\scriptscriptstyle{4}}$          | 100                             | 1                      | $\mathcal{S}_{6}$                     | 110                             | 1                                                     | 0               |

| $\mathcal{S}_{\scriptscriptstyle{5}}$          | 101                             | 0                      | $\mathcal{S}_{6}$                     | 110                             | 0                                                     | 1               |

| $\mathcal{S}_{\scriptscriptstyle{5}}$          | 101                             | 1                      | $S_2$                                 | 010                             | 1                                                     | 0               |

| $\mathcal{S}_{6}$                              | 110                             | 0                      | $S_7$                                 | 111                             | 0                                                     | 0               |

| $\mathcal{S}_{6}$                              | 110                             | 1                      | $\mathcal{S}_{\scriptscriptstyle 3}$  | 011                             | 1                                                     | 1               |

| $S_7$                                          | 111                             | 0                      | $\mathcal{S}_{\scriptscriptstyle 3}$  | 011                             | 0                                                     | 0               |

| $S_{7}$                                        | 111                             | 1                      | $S_{7}$                               | 111                             | 1                                                     | 1               |

Table 1. 1: State Transition Table

State transition table is represented graphically as a *state diagram* in which node represents one of the eight states and directed edge represent the state transition between nodes as shown in Figure 1. 3. Label on each edge mentions the input bit that generates the state transition and output bits as input/output.

The state diagram completely explains the relationship between state transitions and input/output bits but it does not provide any information about how this relationship evolved with time. *Trellis diagram* gives the required information by expanding state diagram at each time instance as shown in

Figure 1. 4. Two copies of states are represented at time t and t+1 and directed edges are drawn from states at t to states at t+1 to show the state transitions. Due to trellis diagram, convolutional codes are decoded very efficiently by algorithms which operate on code trellis to find most likely codewor

Figure 1. 3. State Diagram

Figure 1. 4. Trellis Diagram

#### 2.3. Decoding Convolutional Codes

As explained in previous section, each state transition from  $S_c$  to  $S_n$  or trellis edge corresponds to a particular input. So, decoder computes the probability of each state transition to find the maximum probability input bit. An efficient decoding algorithm based on trellis was first presented by Bahl, Cocke, Jelenik and Raviv [BAH74] and is called the *BCJR algorithm*.

Algorithm is based on the concept that codeword bits  $c_t$  sent at time t are influenced by the codeword bit  $c_t^+$  sent before it. Thus, they may also affects the codeword bits  $c_t^-$  sent after it. So in order to estimate the message bits, the algorithm makes two passes through the trellis: forward pass and backward pass. Forward Pass estimates the message bit  $x_t$  at t based on  $c_t^+$  whereas backward Pass uses  $c_t^-$  to estimate  $x_t$ . Suppose

$y_t$  represents the symbols received for the codeword bits  $c_t$  sent at time t.

$y_t^+$  represents the symbols received for the codeword bits  $c_t^+$  sent after time t and

$y_t$  represents the symbols received for the codeword bits  $c_t$  sent before t.

Then, the probability of the state transition from state  $S_c$  at time t-1 to state  $S_n$  at time t is given by the following equation,

$$\Gamma_t(S_c, S_n) = A_{t-1}(S_c) \Lambda_t(S_c, S_n) B_t(S_n)$$

1. 1

The probability is a function of following three terms:

- (I)  $A_{t-1}$  represents the probability that the encoder is in state  $S_c$  at t-1 based on the information about symbols received before t i.e.,  $y_t$ ;

- (II)  $B_t(S_n)$  represents the probability that the encoder is in state  $S_n$  at t based on the information about symbols received before after t i.e.,  $y_t^+$ ;

- (III)  $\Lambda_t(S_c, S_n)$  represents the probability of the state transition from  $S_c$  to  $S_n$  based on the information about symbols received at t i.e.,  $y_t$ ;

The calculation of A and B values are respectively called the *forward* and *backward recursion* of the BCJR decoder and are calculated through following equations:

$$A_{t-I}(S_c) = \sum_{i=0}^{2^{\nu}-1} A_{t-2}(S_i) \Lambda_{t-I}(S_i, S_n)$$

1. 2

$$B_{t}(S_{n}) = \sum_{i=0}^{2^{\nu}-1} B_{t+1}(S_{i}) \Lambda_{t+1}(S_{c}, S_{i})$$

1. 3

From this equations it is clear that values of both A and B or *path metrics* can be calculated recursively and each step requires multiplication operations over real numbers which increases the decoder complexity in terms of area and cost when implementing in hardware. This problem is overcome by re-formation of original algorithm in the logarithmic domain. The benefit of representing path metrics as log metrics is that now we can replace multiplication with addition. If  $\alpha,\beta$  and  $\gamma$  represents the log metrics of A, B and  $\gamma$  then previous equations transform into the log domain as follows:

$$\Gamma_t(S_c, S_n) = \alpha_{t-1}(S_c) + \gamma_t(S_c, S_n) + \beta_t(S_n)$$

1. 4

$$\alpha_{t-I}(S_c) = \log \sum_{i} e^{\alpha_{t-2}(S_i) + \gamma_{t-I}(S_i, S_n)}$$

1. 5

$$\beta_{t}(S_{n}) = \log \sum_{i} e^{\beta_{t+1}(Si) + \gamma_{t-1}(Sn, Si)}$$

1. 6

The derivation of these equations is out of the scope of this thesis. Interested reader can consult [JOH10] to understand the derivation and respected terms.

#### 2.4. Turbo Codes

Excellent error correction capabilities of Turbo codes [BER93] make it integral part of current telecommunication standards such as [LTE08] [HSP04] [DVBS08]. Turbo code completely changes the way we perform error correction to reach near Shannon limit of channels capacity. Turbo codes are constructed through the parallel concatenation of two convolutional codes which during decoding share their information to achieve good error correction performance. This outstanding performance is also possible due to the presence of pseudo-random interleaver that scrambles data to break up neighborhood relations. Moreover, low-complexity iterative decoding algorithm makes its implementation feasible at the hardware level to be included in the current standards.

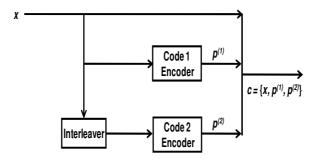

#### 2.4.1. Turbo Encoder

Turbo encoder consists of two convolution encoder in which first component encodes the message x in natural (original) order to produce parity bits  $p^{(1)}$  whereas second one encodes the message in interleaved order (after passing the original message through interleaver) to generate parity bits  $p^{(2)}$  as shown in Figure 1. 5. Since Turbo codes are systematic codes, so at the output, message and parallel concatenation of parity bits are all transmitted to construct turbo codeword. Normally, two component encoders used in Turbo codes are identical but it is also possible to use different components encoders. However, due to presence of interleaver, the parity bits output by two encoders are always different even if identical encoders are used in turbo codes.

Figure 1. 5. Turbo Encoder

#### 2.4.2. Interleaver

An interleaver is expressed through a permutation sequence  $\Pi = \{\pi_1, \pi_2, \pi_3, \dots, \pi_n \}$ , where the sequence  $\{\pi_1, \pi_2, \pi_3, \dots, \pi_n \}$  represents the permutation of the integers from 1 to n.

The function of the interleaver is to generate two completely different set of parity bits after passing through two constituent encoders in order to obtain capacity-approaching performance of turbo codes. This performance is normally achieved by using interleaver with a length of several thousand bits and that performs random permutation on the required length.

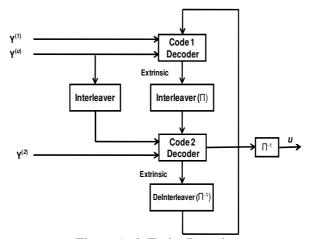

#### 2.4.3. Turbo Decoder

In turbo decoding, the decoding of each individual convolutional code is carried out using BCJR algorithm with the following two modifications [BER93]: First of all, in turbo decoding, the two component codes share information about the message bits. This extra information is called *extrinsic information*. Each decoder fed this extrinsic information to other decoder in order to estimate the message bits. Secondly, in turbo decoding, extrinsic information is updated and shared between the decoders over many iterations. As a result, BCJR decoding algorithm is used by each decoder more than once to decode the message bits. The block diagram for turbo decoder is shown in Figure 1. 6.

The decoder receives input values  $Y^{(u)}$ ,  $Y^{(1)}$ ,  $Y^{(2)}$  from the channel for x,  $p^{(1)}$ ,  $p^{(2)}$  respectively. One complete iteration of turbo decoder is carried out through two half iterations. In the first half iteration, Decoder 1 receives channel values for message bit  $Y^{(u)}$ , first parity bit  $Y^{(1)}$  and deinterleaved extrinsic value from Decoder 2 to generate extrinsic value. However, for initial iteration, Decoder 1 has no extrinsic value from Decoder 2, so it uses only  $Y^{(u)}$ ,  $Y^{(1)}$  to produce extrinsic value. During second half iteration, Decoder 2 creates extrinsic value from interleaved message bits, second parity bit  $Y^{(2)}$  and interleaved extrinsic value from Decoder 1. After the fixed number of iterations, a final decision about the message bits is made based on the extrinsic values from two decoders and channel values for message bits. It is important to note that only extrinsic values are updated at each iteration, channel values for message bits always remain unchanged.

Figure 1. 6. Turbo Decoder

#### 2.4.4. Parallelism in Turbo Codes Decoding

As explained in previous sections 2.3, to decode each component code, turbo decoder first calculates  $\alpha$ -values (using forward recursion) and  $\beta$ -values (through backward recursion) in order to generate extrinsic values. This approach is called serial implementation of turbo decoder. Serial implementation can be represented through *Forward Backward Scheme* as shown in Figure 1. 7.a. Implementation of this scheme can best be explained through data access order shown in Figure 1. 7.b. for D = number of data elements used in a code = 8, T = time to decode a code = 2D = 16 and PE = number of processing elements = 1. For first T/2 = 8 time instances, decoder accesses data elements from extrinsic memory from D = 0 to D = 7, calculate  $\alpha$ -values and store them into decoder inside decoder memory. For next T/2 time instances from 9 to 16, decoder calculates  $\beta$  and extrinsic values and writes updated extrinsic values into extrinsic memory to complete the decoding of component code. It is important to note that decoder can process only one data elements at each time instance in serial implementation.

Serial implementation has following two drawbacks.

- 1. The calculation of *path metrics* ( $\alpha$  and  $\beta$ -values) requires that the whole transmitted data has to be received and stored which increases the decoder memory.

- 2. The approach significantly increases the latency (i.e., time to compute extrinsic values) and make it unsuitable for high data rate application.

To tackle these drawbacks, different parallelism approaches are proposed which are explained below.

(a) Forward Backward Scheme

(b) Data access order in Serial Implementation

Figure 1. 7. Serial Implementation of Turbo Decoder

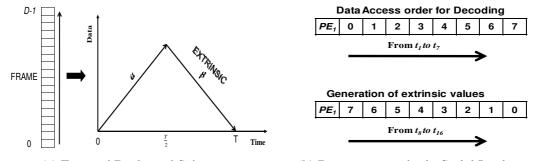

#### 2.4.4.1 Recursive Unit Parallelism

The first type of parallelism [ZHA04] can be directly extracted from decoding algorithm by calculating in parallel  $\alpha$ ,  $\beta$  and extrinsic values used in BCJR algorithms. This approach can be best explained through *Butterfly Scheme* as shown in Figure 1. 8.a. In this scheme, decoder calculates *path metrics* ( $\alpha$  and  $\beta$ -values) at the same time. As a result, butterfly scheme increases the parallelism level by treating two data elements at the same time and requires half the time to decode the component code. Data access order for D = 8, PE = 1 is shown in Figure 1. 8.b.

This scheme parallelizes the forward and backward recursive units to double the parallelism degree without any increase in decoder memory. Also the increase in decoder throughput motivates the use of butterfly scheme at the cost of duplication of recursive units.

Figure 1. 8. Recursive Unit Parallelism

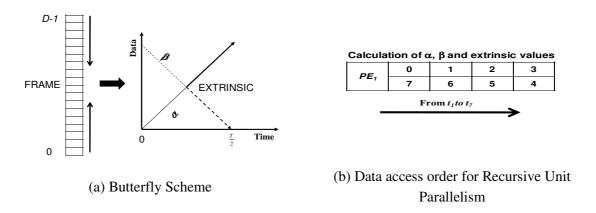

#### 2.4.4.2 Trellis Level Parallelism

In this type of parallelism [WOO00], rather than calculating path matrices ( $\alpha$  and  $\beta$  values) and extrinsic values for each trellis transition, these values are calculated for more than one trellis transition at the same time. Degree of parallelism for calculating these values are bounded by the total number of transitions in a trellis. Trellis parallelism is usually represented as radix-2<sup>S</sup> where S is the number of trellis transitions parallelized in decoder computation. Forward Backward scheme (explained in section 2.4.4) is modified for Trellis level parallelism in Figure 1. 9.a for S = 2. From data access order of this scheme, it is important to note that number of data elements processed by processing element at a given time instant is equal to S. Data access order for D = 8, S = 2, & PE = 1 is shown in Figure 1. 9.b.

This approach has low area overhead [ASG10] since only computational units need to be duplicated, however, decoder memory is reduced which compensates the increase in computation units area cost. The increase in decoder throughput with slight increase in decoder area motivates to implement higher radix implementation for current standards [ASG10].

Figure 1. 9. Trellis Level Parallelism

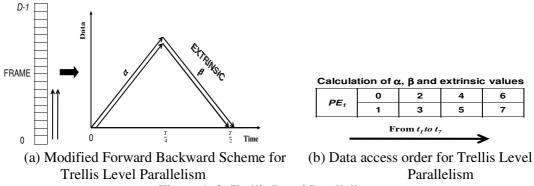

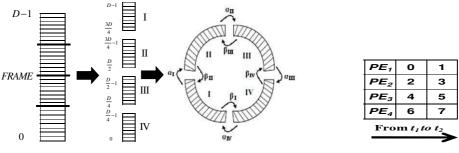

#### 2.4.4.3 SISO Decoder Level Parallelism

As explained at the start of the section 2.4.4, serial implementation of turbo decoder increases the decoder memory and latency for large amount of data. To tackle this problem, *sliding window BCJR algorithm* [BLA05] is proposed in which data block to be decoded is partitioned into number of segments or windows where each window is a subset of original block and has length  $D_w$ . Each window is then treated as separate data block and allocated to separate BCJR-SISO decoder. These SISO decoders then work in parallel so that  $\alpha$ ,  $\beta$ ,  $\gamma$  and extrinsic values for one window are calculated at the same time as these values are calculated for other windows. Since the window can start or end in the middle of overall data block, the BCJR decoding algorithm approximated the initial values needed to start the calculation of  $\alpha$  and  $\beta$  values. To make sufficiently accurate estimates, on either side of the window, forward and backward recursion have been run on some extra bits of the adjacent windows. This is called *acquisition*. Alternately, *message passing method* is used to initialize path metrics by the values generated in the previous iteration by adjacent windows. Sliding window method with message passing technique is shown in Figure 1. 10.a. Number of data processed at a given time instance depends on the number of partitions and window. If one processing element process one window then data access order for D = 8, PE = 4,  $D_w = D/P = 2$  is shown in Figure 1. 10.b.

Approximated initial values for path metrics, calculated in sliding window technique, causes negligible loss in error correction performance of turbo decoder. In contrast, sliding window technique significantly increases throughput and reduces memory of turbo decoder.

(a) Sliding Window Method with Message

Passing Technique

(b) data access order for SISO Decoder Level Parallelism

Figure 1. 10. SISO Decoder Level Parallelism

#### 2.4.4.4 Conclusion

To increase the throughput, any combinations of above described parallelisms can be used to implement turbo decoder. For example, we can use both trellis level parallelism and SISO level parallelism to implement turbo decoder. This technique will increase the throughput at the cost of increase in hardware cost. However, implementation of all these parallelisms causes memory access conflict problem (discussed in Section 4.1). With the increase of parallelism, this conflict problem also increases. In this thesis, we present algorithms that can resolve memory conflict problem for any combination of parallelism in polynomial time.

#### 3. Block Codes

Block codes are second class of error correction codes that are used to transmit digital data reliably through unreliable communication channels in the presence of noise. Many types of block codes are used in different applications but among the classical block codes, Reed-Solomon [AHA] is the most popular due it widespread use in CD, DVD and hard disk drives. Other examples of classical block codes are Golay codes [GOL61] and Hamming codes [HAM50].

In block coding, long data stream is segmented into pieces of fixed length called a message block. Each message block, denoted by X, consist of x information bits that results in  $2^x$  possible distinct messages. The function of the encoder is to transform each input message X into a binary c-tuple C where c > x. This binary c-tuple C is called codeword of the message X. In block coding, there are  $2^x$  codewords corresponds to the  $2^x$  possible messages and this set of  $2^x$  codewords is called *block code*. In order to use this block code for practical purposes, it is necessary that these  $2^x$  codewords must be distinct and have one-to-one correspondence with  $2^x$  messages.

Encoding of block code with  $2^x$  codewords with each codeword has length x is prohibitively complex since encoder has to store these  $2^x$  codewords into memory. To reduce encoding complexity, linear block codes are used in practical application and can be defined as follows:

#### **Definition** Linear Block Codes

A *linear block code* is a class of block codes in which modulo-2 sum of two codewords is also a codeword.

A generator matrix G is used to generate codewords in linear block codes. Generator matrix contains x linearly independent codewords with each codeword length c. Each message is multiplied by G to generate codeword corresponding to this message. Construction of (7, 4) linear code in which c = 7 and c = 4 is explained through an example. This example and the other information related to linear block codes are taken from [LIN04]. G for this example is shown below.

$$G = \begin{pmatrix} 1 & 1 & 0 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 1 \end{pmatrix}$$

If  $X = (1 \ 1 \ 0 \ 1)$  is the message to be encoded then its corresponding codeword is obtained as follows:

C = X.G

$C = 1(1\ 1\ 0\ 1\ 0\ 0\ 0) + 1(0\ 1\ 1\ 0\ 1\ 0\ 0) + 0(1\ 1\ 1\ 0\ 0\ 1\ 0) + 1(1\ 0\ 1\ 0\ 0\ 0\ 1)$

$C = (1\ 1\ 0\ 1\ 0\ 0\ 0) + (0\ 1\ 1\ 0\ 1\ 0\ 0) + (1\ 0\ 1\ 0\ 0\ 0\ 1)$

$C = (0\ 0\ 0\ 1\ 1\ 0\ 1)$

From this example, it is clear that (c, x) linear block code is completely specified by G and encoder has to store x rows of G to generate codeword of length c for any input message. All the codeword for this (7, 4) code is shown in Table 1. 2. From this table, it is clear that modulo-2 sum of any two codewords is also a codeword.

| Message | Codewords |

|---------|-----------|

| (0000)  | (0000000) |

| (1000)  | (1101000) |

| (0100)  | (0110100) |

| (1100)  | (1011100) |

| (0010)  | (1110010) |

| (1010)  | (0011010) |

| (0110)  | (1000110) |

| (1110)  | (0101110) |

| (0001)  | (1010001) |

| (1001)  | (0111001) |

| (0101   | (1100101) |

| (1101)  | (0001101) |

| (0011)  | (0100011) |

| (1011)  | (1001011) |

| (0111)  | (0010111) |

(1111111)

(1111)

**Table 1. 2**: Linear block code with x = 4 and c = 7.

#### 3.1. Encoding of Linear Block Codes

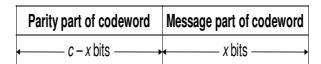

As explained previously, encoder needs to store x rows of length c to encode any message in (c, x) linear block code. Another simplification in the implementation of encoder is carried out by introducing systematic structure during the construction of linear block codes. In this structure, codeword is divided into two parts namely message part and parity part as shown in Figure 1. 11. The message part contains x information (message) bits and the parity part contains c - k parity bits that are linear sum of message bits. A linear block with systematic structure is called *linear systematic block code*.

Figure 1. 11. Systematic format of a codeword

The (7, 4) code, shown in

Table 1. 2, is a linear systematic block code in which rightmost x bits of codeword are identical to the message. A liner systematic code is completely specified by its generator matrix G that can be divided in two matrices of order x \* x and x \* p where p = c - x and x \* x is an identity matrix. Generator matrix for (7, 4) linear systematic block code is expressed as follows.

$$G = \begin{pmatrix} p \text{ matrix} & x * x \text{ identity matrix} \\ 1 & 1 & 0 & \vdots & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & \vdots & 0 & 1 & 0 & 0 \\ 1 & 1 & 1 & \vdots & 0 & 0 & 1 & 0 \\ 1 & 0 & 1 & \vdots & 0 & 0 & 0 & 1 \end{pmatrix}$$

To explain the simplicity introduced by linear systematic codes, let  $X = (x_0, x_1, x_2, x_3)$  is the message to be encoded and  $C = (c_0, c_1, c_2, c_3, c_4, c_5, c_6)$  is the resultant codeword then,

$$C = X. \begin{pmatrix} 1 & 1 & 0 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 1 \end{pmatrix}$$

Using matrix multiplication,

$$C_{6} = X_{3}$$

$$C_{5} = X_{2}$$

$$C_{4} = X_{1}$$

$$C_{2} = X_{1} + X_{2} + X_{3}$$

$$C_{1} = X_{0} + X_{1} + X_{2}$$

$$C_{0} = X_{0} + X_{2} + X_{3}$$

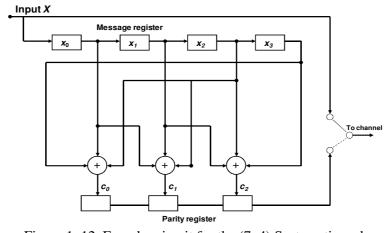

From these equations, it is possible to generate encoding circuit rather that storing rows of G [LIN04]. Encoding circuit for (7, 4) systematic linear code discussed in this section is shown in Figure 1. 12.

Figure 1. 12. Encoder circuit for the (7, 4) Systematic code

#### 3.2. Low Density Parity Check (LDPC) Codes

Low density parity check Codes (LDPC) are a class of linear block codes with error correction capabilities very close to the channel capacity. Due to their excellent error correction performance, it has already included in several wireless communication standards such as DVB-S2 and DVB-T2 [DVB08], WiFi (IEEE 802.11n) [WIF08] or WiMAX (IEEE 802.16e) [WIM06].

But first we explain how we represent code with parity check equations. Consider a codeword  $C = [c_1 \ c_2 \ c_3 \ c_4 \ c_5 \ c_6]$  which satisfies the following three parity check equations.

$$c_2 \oplus c_3 \oplus c_4 = 0,$$

$c_1 \oplus c_2 \oplus c_4 = 0,$

$c_1 \oplus c_3 \oplus c_4 = 0$

Codeword constraints or parity check equations are often expressed in matrix form as follows:

$$\begin{pmatrix} 0 & 1 & 1 & 1 \\ 1 & 1 & 0 & 1 \\ 1 & 0 & 1 & 1 \end{pmatrix} \begin{pmatrix} c_1 \\ c_2 \\ c_3 \\ c_4 \end{pmatrix} = \begin{pmatrix} 0 \\ 0 \\ 0 \end{pmatrix}$$

The above H matrix is an M \* N binary matrix where each row  $M_i$  of H corresponds to a parity check equation whereas each column  $N_j$  associated with codeword bit. A nonzero entry at (i, j)th location means that the jth codeword bit is included in the ith parity check equation.

For a codeword  $x \in \mathbb{C}$  to be valid, it must satisfy the equation:

$$xH^{t} = 0, \forall x \in C$$

As the name explains, LDPC codes are block codes that contains only a small number of 1's in comparison to the number of 0's in parity check matrix *H*. This sparseness in H keeps the complexity of iterative decoding at reason limit and increases linearly with the code length.

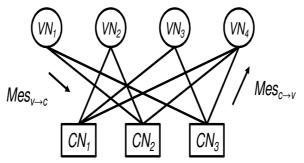

#### 3.3. Tanner Graph Representation

Due to the sparseness of H-matrix, LDPC codes can be graphically represented as a bipartite graph called T-anner G-raph which depicts the association between code bit and parity check equation. The Tanner graph consists of two sets of vertices: variable node set (VNs) and check node set (CNs). A data  $v_i \in VN$  represents one bit in the codeword (i.e. data to be processed) whereas  $c_j \in CN$  represents a check equation used in generating parity check bits (i.e. operation to be done on the data). An edge  $e_{ij}$  connects the i-th check node with j-th variable node if j-th variable node (VN) is checked by or included in i-th check node (CN) which means that number of edges in the Tanner graph is the same as the number of 1s in the H matrix. Tanner graph is helpful in understanding the decoding process which functions by exchanging messages between CN and VN along the edges of these graphs. Tanner graph for the H-matrix in the previous section is shown in Figure 1. 13. In this figure, a message passed from CN to VN is called M-es $_{v \to v}$  whereas a message going from VN to CN is represented by M-es $_{v \to c}$ .

Figure 1. 13. Tanner Graph representation of H

#### 3.4. Decoding

As explained in the previous sections, the algorithms to decode LDPC codes functions by exchanging messages along the edges of a Tanner graph. These algorithms are collectively called message-passing algorithms. Message passing algorithms are a type of iterative decoding algorithm in which CN and VN iteratively exchange massages forward and backward until decoding is completed (or stopping criteria is reached). These algorithms are named for the type of operations executed at the nodes such as belief-propagation or sum-product decoding [PEA88], min-sum decoding [FOS99] or normalized Min-Sum decoding [CHE02].

Sum-Product algorithm is a message passing algorithm which accepts the probability for each received bit as input. These probabilities represent a level of belief regarding the value of codeword bits. Due to simplicity in computation, the probabilities are converted in logarithmic domains that are called Log likelihood Ratio (LLR). The LLRs are defined by the following equation:

$$LLR = \log\left(\frac{P(v=0)}{P(v=1)}\right)$$

where P(v = i) is the probability that bit v is equal to i.

The input LLRs are also called *a-priori* values because they are know in advance even before the decoding of LDPC codes is started.

The decoding is carried out in four steps which are presented below.

#### **I- Initialization**

In this step, a-priori LLR values are assigned to all the outgoing edges of every VNs. The sign of LLR provides a hard decision on the transmitted bit whereas it magnitude |LLR| gives an indication on the reliability of this decision.

#### II- Check node Update

In this step, *jth* CN estimates the value of *ith* VN based on the values received from other VNs connected to this CN which means that the decision about the *ith* VN value is made completely

independently from the value just received from it. The CN supposed to create extra, *extrinsic*, information about *ith* VN value. In check node Update, each CN updates all connected VNs through the extrinsic information calculated for each VN. Bayes law in the logarithmic domain is used to calculate the sign (Equation 1.7) and the absolute value (Equation 1.8) of the extrinsic message for each VN.

$$sign(Mes_{c \to v}) = \prod_{v \in v_c/v} sign(Mes_{v' \to c})$$

1.7

$$|Mes_{c \to v}| = g \left( \sum_{v \in v_c/v} g\left( |Mes_{v' \to c}| \right) \right)$$

1.8

where  $v_c$  represents the set of all the VNs connected with current CN and  $v_c/v$  means all the VNs in  $v_c$  except v. The function g(x) is represented through Equation 1.9 as below.

$$g(x) = -\ln \tanh\left(\frac{x}{2}\right) = \ln \frac{\exp x + 1}{\exp x - 1}$$

#### III- Variable node Update

In this step, each VN updates its value based on the extrinsic information received from all the connected CNs. The soft output (SO) value also called A-Posteriori Probability (APP) is calculated using Equation 1.10, where *LLR* is the initial soft input or a-priori value. The *SO* value is used to calculate new VN to CN message  $Mes_{v\rightarrow c}$  and is give by Equation 1.11.

$$SO_v = LLR + \sum_{c \in c_v} Mes_{c \to v}$$

1.10

$$Mes_{v \to c} = SO_v - Mes_{c \to v}$$

1.11

#### **IV- Iterative Process**

The forth step is to repeat the check and variable node update processes for new APP values until all the parity-check equations are satisfied or until a maximum number of iterations has reached and the decoder halts. At the end of iterative process or decoding, a hard decision is made based on the signs of values of VNs to output the codeword.

#### 3.5. Implementation of LDPC Decoder

Analyzing the equations presented in LDPC decoding, it is clear that implementation of variable node update is quite simple and straight forward whereas the implementation of check node update is complex. The g(x) function used in check node update is highly non-linear and Look-Up Tables (LUTs) are required to directly map g(x) into hardware. However, to cope with finite precision issues, significantly large number of bits is required which results in large LUTs and significant increase in hardware cost. To reduce the computational complexity and hardware cost, different suboptimal algorithms are proposed [FOS99] [CHE02] to avoid the evaluation of the g(x) function.

The Min-Sum algorithm approximates and hence simplifies the sum-product algorithm by replacing g(x) function with the most minimum incoming message. The approach eliminates the complexity of check node update and can be expressed as:

$$Mes_{c \to v}^{new} \approx \min_{v \in v_{c}/v} |Mes_{v' \to c}|$$

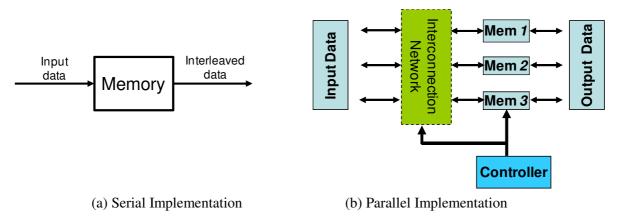

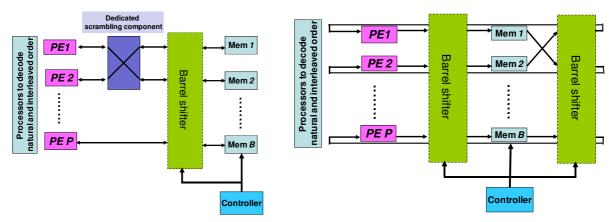

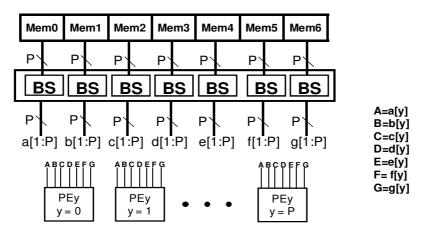

1.12