# Parameter Extraction of MOSFETs Operated at Low Temperature

E. Simoen, C. Claeys, J. Martino

# ▶ To cite this version:

E. Simoen, C. Claeys, J. Martino. Parameter Extraction of MOSFETs Operated at Low Temperature. Journal de Physique IV Proceedings, 1996, 06 (C3), pp.C3-29-C3-42. 10.1051/jp4:1996305. jpa-00254223

HAL Id: jpa-00254223

https://hal.science/jpa-00254223

Submitted on 4 Feb 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Parameter Extraction of MOSFETs Operated at Low Temperature

E. Simoen, C. Claeys and J.A. Martino\*

IMEC, Kapeldreef 75, 3001 Leuven, Belgium \* LSI/PEE/USP, São Paulo, Brazil

Abstract. In this paper, an overview is given of the methods for practical parameter extraction for MOSFETs operated at cryogenic temperatures. The methods considered are based on the input characteristics of the device, from which the charge threshold voltage, the subthreshold slope, the effective mobility, the series resistance and the effective gate length is derived. Whenever possible, the physical basis of the mostly semi-empirical methods will be outlined. Finally, pitfalls and problems, related to low temperature MOSFET characterisation, like transient and freeze-out effects, self-heating, etc, are briefly discussed.

### 1. INTRODUCTION

Today, MOSFET simulation and modelling has left its infancy and has reached a level whereby high agreement is reached with experimental characteristics. At the same time, by building in temperature dependent physical models, it is possible to predict the low temperature operation in an accurate way [1]-[4]. In principle, one could thus restrict the actual low-temperature device characterisation to the absolute minimum and rely on numerical parameter calculations. In practice, however, the situation is more complex. For instance, for MOSFETs operating in the freeze-out regime, which typically occurs below 50 K or so, some new physical phenomena start to play a role, which are generally less well understood and require a detailed study of the underlying mechanisms (for a recent overview see e.g. [5]). Furthermore, upon down-scaling the device dimensions to the submicron and the nanoscale, the device parasitics become prominent and start to affect the I-V characteristics. This is the more true for low temperature operation, which can increase the mobility degradation and the series resistance [5]. At the same time, high transverse and high lateral field effects become important [6] and carrier velocity saturation starts to limit the drive current [7]-[8]. At cryogenic temperatures and/or for sub 100 nm devices, even velocity overshoot has been demonstrated experimentally [9]-[11]. So from a practical and a more fundamental viewpoint there is still a need for detailed MOSFET studies at cryogenic temperatures and hence for parameter extraction methods, in order to unravel the temperature dependence of physically relevant properties like the charge threshold voltage VT, the subthreshold swing S, the effective mobility (µeff), the source-drain series resistance RSD and the effective device length Leff.

In the next sections, the low-temperature extraction of the parameters listed above will be discussed separately. As will be seen, most methods rely on an input curve (ID versus VGS) registered in linear operation, i.e. for low drain voltage VDS. It will become clear that traditional room temperature parameter extraction may no longer work at low T and therefore, dedicated and more sophisticated techniques have been developed, which require, however, a good insight into the underlying physics. In the final paragraph, some experimental difficulties which are typical for low temperature operation will be highlighted and their relevance discussed. Additionally, practical ways to circumvent these anomalies will be pointed out.

## 2. CHARGE THRESHOLD VOLTAGE EXTRACTION

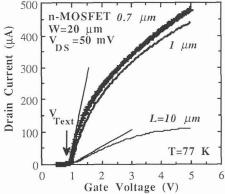

A number of fairly simple, semi-empirical methods have been proposed to derive the threshold voltage VT, some of which have become quite popular. The most widespread is probably the linear extrapolation method, which is illustrated in Fig. 1, whereby a straight line is fitted to the linear drain current ID measured at low VDS (typically 50 mV) to the point of maximum transconductance g<sub>m</sub>. VT is then defined as the gate voltage corresponding to the crossing point minus VDS/2. This technique has been successfully applied to low temperature operation as well [12]-[15], although the corresponding value VText is larger than the true VT at cryogenic T [14].

Another straightforward method is to determine the gate voltage which is necessary to establish a certain drain current level per unit of width (ID/W) at VDS=50 mV. Although very simple, this method has only limited applicability and is for instance useless for so-called accumulation-mode (AM) Silicon-on-Insulator (SOI) transistors [15], which can operate in different conduction modes, both at room [16] and at cryogenic T [17].

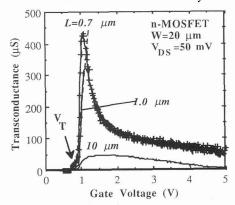

The Fowler and Hartstein (FH) method [18] determines the point of maximum slope in the transconductance (g<sub>m</sub>) characteristic and linearly extrapolates this point to zero transconductance (Fig. 2). Another technique, introduced by Balestra and Ghibaudo [14] is well-suited for cryogenic MOSFETs and will be discussed in the next section, since it is related to the extraction of the effective mobility.

Fig. 1. Definition of the extrapolated threshold voltage, for three n-MOSFETs at 77 K.

Fig. 2. Fowler-Hartstein method for the n-MOSFETs of Fig. 1.

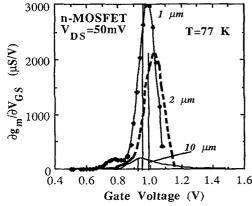

Probably the most powerful (and fairly simple) method for V<sub>T</sub> extraction is the so-called Transconductance peak [19],[20] (TC) or double-derivative method [21]. It is illustrated in Fig. 3 for three

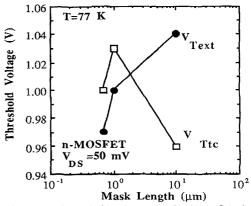

Transconductance peak [19],[20] (TC) or double-derivative method [21]. It is illustrated in Fig. 3 for three bulk n-MOSFETs at 77 K: VT is defined here as the gate voltage corresponding to the peak maximum in the ∂gm/∂VGS curve. From a comparison of different techniques, it can be concluded that the TC method is closest to the 'correct' physical VT, which can be determined by the so-called 'split' C-V method [19],[20]. Furthermore, it is rather insensitive to interface states, normal field mobility degradation [19],[20] and series resistance [19],[20],[22] which are highly desirable features for low-temperature extraction. Fig. 4 compares the extrapolated with the TC threshold voltage for three 0.7 μm bulk CMOS n-MOSFETs at 77 K, as a function of the device length. No systematic difference is found in this particular case.

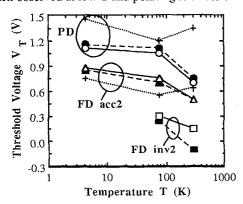

Another benefit of the TC method is that it enables to determine the onset of other conduction modes. For instance, in the case of the AM SOI p-MOSFETs, it has been demonstrated that for each mode (backchannel; body; front-channel) a corresponding peak in the  $\partial g_m/\partial V_{GS}$  is obtained, and this both at room temperature [21] and at low T [15]. The same applies for e.g. parasitic edge conductance, as illustrated in Fig. 3, where the first small peak for the L=0.7  $\mu$ m n-MOSFET corresponds to premature conduction along the LOCOS field regions. Similar observations have been reported for irradiated SOI MOSFETs at low T [22], or for the edge-conduction in dual-gate SOI MOSFETs [23]. A final example of the power of the technique is given in Fig. 5, showing the VT as a function of temperature for a 0.5  $\mu$ mx20  $\mu$ m SOI n-MOSFET, both fully depleted (FD) and partially depleted (PD). In general, a better agreement between the theoretically expected value and the measured data is obtained for the TC technique. Futhermore, for the

case that the back-interface of the FD device is in inversion, only this method yields an acceptable V<sub>T</sub> [15].

Fig. 3. TC threshold voltage for three n-MOSFETs at 77 K. The first maximum for the L=0.7  $\mu m$  transistor corresponds to the onset of parasitic edge conduction, which is not seen at room temperature.

Fig. 4. Extracted threshold voltage as a function of device length, corresponding to T=77 K, for the n-MOSFETs of Fig. 1.

A phenomenon which has been frequently observed in the past for cooled room temperature CMOS technologies which were not optimised for cryogenic operation is the so-called drain-voltage threshold [24]. This occurs typically for deep cryogenic temperatures, where freeze-out becomes important and indicates an insufficient overlap of the gate with the source. As a result, there exists a potential barrier, which inhibits the injection of carriers in the channel. This type of behaviour aggravates for cooled submicron CMOS transistors with Lowly Doped Drain (LDD) regions [25]. Careful analysis of the phenomenon has pointed out that this drain threshold voltage phenomenon is connected to the negative  $\Delta L$  often observed at low T and pointing to a loss of control of the gate electrode over the channel [26].

Fig. 5. Threshold voltage as a function of T for a PD and a FD 0.5  $\mu$ mx20  $\mu$ m SOI n-MOSFET. Full lines represent theoretical estimates; dashed lines TC extracted data and dotted lines extrapolated VTs. FD acc2 corresponds to the case with the back-gate in accumulation; FD inv2 to the case with the back-gate inverted [15].

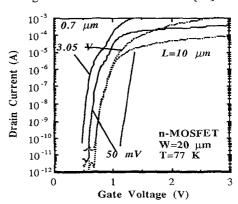

Fig. 6. DIBL effect at 77 K for a L=0.7 and 10  $\mu m$  nMOSFET fabricated in a 0.7  $\mu m$  CMOS technology: no effect is seen for the longer device at  $V_{DS}$ =3.05 V, while a shift of the input curve to the left is found for the 0.7  $\mu m$  device.

For submicron MOSFETs several kinds of short-channel effects can reduce the threshold voltage. One such mechanism is Drain Induced Barrier Lowering (DIBL), which is illustrated in Fig. 6 for bulk 0.7 µm CMOS n-channel transistors. Only the shortest device suffers clearly from the DIBL effect. However, as demonstrated previously, low-temperature DIBL occurs already for long transistors (L=10 µm) in the case of a 3 µm CMOS technology on high-resistivity (HR) substrates [27]. In general, it is found that the

reduction of the threshold voltage, occurring for larger lateral fields (larger VDS) diminishes upon cooling to 77 K, both for n-MOSFETs [28],[29] and p-MOSFETs [30],[31].

## 3. SUBTHRESHOLD SWING

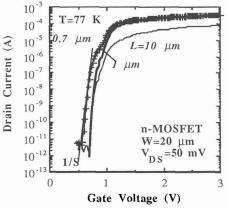

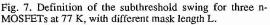

The subthreshold swing, shown in Fig. 7 is defined as the inverse subthreshold slope and corresponds to:

$$S = \frac{\partial V_{GS}}{\partial log I_{D}} \qquad (mV/decade current) \qquad (1)$$

for the device in linear operation. For standard MOSFETs this parameter is tightly connected to the interface and the fixed oxide charge through the equation:

$$S^{-1} \approx \frac{q}{kT} \frac{C_{\text{ox}}}{C_{\text{ox}} + C_{\text{d}} + C_{\text{it}}}$$

(2)

$S^{-1} \approx \frac{q}{kT} \frac{C_{ox}}{C_{ox} + C_d + C_{it}} \tag{2} \label{eq:2}$  where  $C_{ox}$  is the gate oxide capacitance per cm<sup>2</sup>,  $C_d$  the depletion capacitance and  $C_{it} \approx q^2 N_{it}$  the interface state capacitance per unit of area, respectively, with Nit the surface density of interface traps (/eVcm<sup>2</sup>) and kT/q the thermal voltage. Early studies indicated that the subthreshold swing at 4.2 K was higher than expected from eq. (2). In fact, no unique value for S could be extracted [32]. It has been recently demonstrated that eq. (2) is still valid in good approximation and that the observed variation of S with ID at 4.2 K is due to the variation of Nit when approaching the band edge [33]. This is supported by the density of interface traps extracted from the dynamic conductance technique, which is in close agreement. The subthreshold swing has also been applied to analyse the density of interface traps in MOSFETs irradiated at 77 K [34].

In some cases, discrete steps or peaks are observed in the weak inversion drain-current of both bulk [35] and SOI MOSFETs [36] at 4.2 K. This is even more pronounced for devices which have been hotcarrier stressed either at room temperature or at cryogenic T [35],[37], or for small area devices. The physical explanation of this phenomenon is most likely interface-trap assisted resonant tunneling in the ≈0.1 μm degraded region near the drain of the device, although other models are currently being explored. In principle, such observations allow to study single interface traps, occurring close to the band-edges.

For thin-film fully-depleted, or AM SOI MOSFETs coupling between the front and the back interface will affect the subthreshold slope. For the back-gate in depletion, 1/S will reduce and depends on both the front- and the back-gate bias [38]. Consequently, eq. (2) is no longer a good approximation and can therefore not be used to extract Nit. Generally, S becomes a rather complex function for FD or AM SOI MOSFETs, but in some cases, a simplification is possible [39]. It has for instance been demonstrated that for AM MOSFETs the minimum S can be approximated by [39]:

$$S_{\min} \approx \frac{kT}{q} \ln(10) \left[ \left( 1 + \frac{C_{itf}}{C_{oxf}} + \frac{C_{si}}{C_{oxf}} \right) - \frac{\frac{C_{si}}{C_{oxb}} \frac{C_{si}}{C_{oxf}}}{1 + \frac{C_{itb}}{C_{oxb}} \frac{C_{si}}{C_{oxb}}} \right]$$

(3)

with  $C_{itf}$  and  $C_{itb}$  the front and back interface trap capacitance, respectively;  $C_{oxf}$  and  $C_{oxb}$  the corresponding front and back gate capacitance and Csi the Si film capacitance per cm<sup>2</sup>, given by esie0/tsi  $(\varepsilon_{Si})$  the dielectric constant of Si;  $\varepsilon_0$  the permittivity of vacuum and  $t_{Si}$  the thickness of the Si film). At the same time, it has been demonstrated that for negligible Nitf at 300 K, the front interface trap density at 77 K can be extracted from the increase in flatband voltage (or for an AM device, in VT) upon cooling [40], yielding the expression:

$$N_{itf}(77 \text{ K}) \approx \frac{C_{oxf}}{q} \frac{\Delta V_T}{q\Phi_{f77K}}$$

(4)

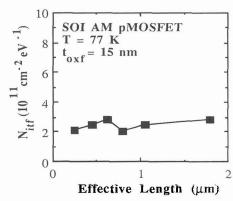

with  $\Delta V_T$  the absolute value of the front threshold voltage increase, which is derived from the TC method as outlined above and  $\Phi_{f77K}$  is the calculated Fermi level potential with respect of the intrinsic level [40]. Using eq. (4), typical Nitfs in the range  $2x10^{11}$  eV<sup>-1</sup>cm<sup>-2</sup> have been derived at 77 K for the AM p-MOSFETs shown in Fig. 8. Combining eqs. (3) and (4) and substituting the experimental S, the back interface trap density at 77 K can be extracted as well [41]. Typical values for Nitb are in the range 1012 eV-1cm-2. These should be considered as effective values for the respective interface trap densities. This analysis can be extended to any cryogenic temperature, provided that the threshold voltage difference with the room temperature value is sufficiently large to be accurately determined.

Fig. 8. Effective front interface trap density derived at 77 K for an array of 0.5  $\mu m$  CMOS AM SOI p-MOSFETs. N<sub>itf</sub>(300 K) is taken 0 in the calculation [40]. The device width is 20  $\mu m$ .

## 4. MOBILITY

# 4.1 Effective mobility at moderate transverse electric field

The extraction and physical modelling of the inversion layer mobility has attracted a lot of attention in the past two decades, both at room temperature [42] and at cryogenic T [43]-[51]. At room temperature, the effective mobility  $\mu_{eff}$ , which is defined as:

$$\mu_{eff} = \frac{L_{eff}}{W_{eff}} \frac{gd(V_{GS})}{qN_{S}(V_{GS})} \approx \frac{L_{eff}}{W_{eff}} \frac{I_{D}}{C_{ox} (V_{GS} - V_{T})V_{DS}}$$

(5)

takes the form:

$$\mu_{eff} = \frac{\mu_0}{1 + \theta^* \; (V_{GS} - V_T)} \eqno(6)$$

in strong inversion. Hereby is gd the channel conductance (\$\partial I\_D / \partial V\_{DS}\$), NS the inversion layer carrier

in strong inversion. Hereby is  $g_d$  the channel conductance ( $\partial I_D/\partial V_{DS}$ ),  $N_S$  the inversion layer carrier surface density and  $\mu_0$  is the zero-field mobility. The generalised mobility attenuation factor  $\theta^*$  is given by [52]:

$$\theta^* = \theta + \frac{C_{ox} R_{SD} W_{eff} \mu_0}{L_{eff}}$$

(7)

and is a measure of the reduction of the effective mobility with increasing normal field. The latter is physically due to the increasing contribution of surface roughness scattering to the carrier mobility. In writing eqs. (6) and (7) it is assumed that the source-drain series resistance is constant with VGS-VT (non-LDD type of MOSFETs) and that the gate overdrive voltage VGS-VT >>IDRSD/2.

As pointed out earlier [53]-[54], the extraction of  $\mu_{eff}$  from a linear input curve at cryogenic temperatures requires in fact already an accurate modelling of the device characteristics, in case of the  $\mu_{eff}$  dependence on the normal field, on T, etc. This implies that most of the extraction methods which have been proposed recently [55]-[57] are rather complex and require numerical treatment of the measurement data. In many cases, they are applicable only in a restricted temperature regime (generally from 77 K on), or to a particular class of devices. An attractive empirical method, applicable in the whole range between 4.2 K and 300 K has been proposed by Emrani et al. [53]-[54] and has been successfully applied for the extraction of the electron mobility in inversion and accumulation layers [58], to SOI MOSFETs [59] and to n- and p-MOSFETs with nitrided oxide gates [60]. The principle of the extraction method is based on the empirical relationship between the function  $I_D^2/g_m$  and the gate overdrive voltage VGS-VT. For instance,

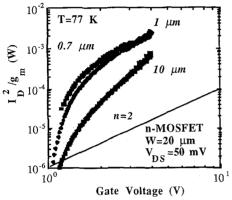

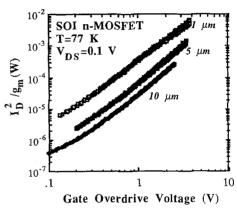

as shown in Fig. 9 for bulk n-MOSFETs at 77 K and in Fig. 10 for PD SOI n-MOSFETs at 77 K, for sufficiently large V<sub>GS</sub>-V<sub>T</sub>, the following applies:

$$\frac{I_D^2}{g_m} = \beta (V_{GS} - V_T)^n$$

(8)

whereby the coefficient  $\beta$  depends on  $\theta^*$ . Physically acceptable values for the empirical exponent n are in the range 2 (300 K) to 3 (4.2 K) [61]. The effective mobility is shown to be [53]:

$$\mu_{\text{eff}} = \mu_{\text{g}} \frac{X^{n-2}}{1 + X^{n-1}} \tag{9a}$$

with  $X=\theta(VGS-VT)$  and  $\mu_g$  proportional to the maximum effective mobility through the relationship:

$$\mu_{\text{max}} = \mu_{\text{g}} \frac{(n-2)(n-2)/(n-1)}{(n-1)}$$

(9b)

$\mu_{max} = \mu_g \frac{(n-2)(n-2)/(n-1)}{(n-1)}$  (9b)

At the same time, the charge threshold voltage V<sub>T</sub> at any temperature in the range 4.2 to 300 K can be derived from:

$$V_{\text{Text}}^* = V_T + \frac{1}{\theta^*} \left[ \frac{(n-2)}{n} \right]^{n/(n-1)}$$

(10)

whereby  $\theta^*$  is obtained from:

$$\theta^* = (\frac{n-2}{n})^{1/(n-1)} \frac{1}{V_{GSmax} - V_T}$$

(11)

$V_{GSmax}$  is the gate voltage which corresponds to the maximum transconductance  $g_{mmax}$ . Since  $\theta^*$  is a positive number and n becomes larger than 2 upon cooling, from eqs (10) and (11) follows that the linear extrapolated threshold voltage V<sub>Text</sub> is slightly larger than the actual V<sub>T</sub> at low T. In practice, it turns out that the exponent n starts to increase in the range between roughly 100 K and 200 K for n-channel devices, depending on the technology, while for p-MOSFETs, the change from 2 to 3 occurs between 20 K and 4.2 K. Physically speaking, the change of n from 2 to 3 points to a change in the dominant scattering mechanism upon cooling. Likewise, the bell-shaped µeff behaviour typically found at low T can be explained by assuming that  $\mu_{eff}$  is an explicit function of the inversion charge  $Q_i$ , which in its most general form is represented by [54]:

$$\frac{1}{\mu \text{eff}} = \frac{A}{O_i^{n-2}} + BQ_i \tag{12}$$

whereby the coefficient A is a Coulomb scattering parameter and B a surface roughness scattering

Although this method is quite general and powerful, there exists a number of limitations which are for example illustrated in Fig. 9. The curves are obtained on bulk CMOS transistors with LDD. While for the L=10  $\mu$ m device an n≈2.5 is obtained, n reduces to ≈2 (L=1  $\mu$ m) and to physically unrealistic values for smaller lengths (1.7 for L=0.7 µm). This implies that the technique is not applicable to short-channel LDD devices at low T, probably because of the series resistance. Of course, it has been demonstrated that the function represented by eq. (8) is independent of RSD and therefore also the determination of n and VT [53], [61], which is, however, only valid if RSD is indeed independent of VGS-VT. This fact has to be taken into account if the above extraction method is to be used for short-channel LDD MOSFETs.

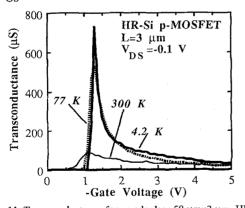

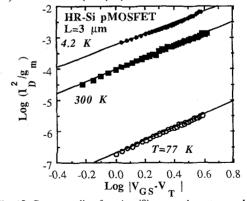

As illustrated by Figs 11 and 12, the same analysis can in principle be applied to the case of p-MOSFETs fabricated on high-resistivity Si substrates (HR-CMOS) [27]. From the transconductance characteristics shown in Fig. 11, it is clear that at cryogenic temperatures this corresponds to a bell-shaped μeff. However, again only physical reasonable values of n are obtained in a limited range (n=2.08 for T=77 K), while n's lower than 2 are found for the other temperatures [27].

Another important point related to the mobility extraction at cryogenic T is the so-called universal electric field dependence of the effective mobility previously reported at room temperature for n- [62] and pchannel devices [63]. It turns out that if  $\mu_{eff}$  is represented versus the effective normal electric field, given by:

$$E_{eff} = \frac{\eta Q_i + Q_d}{\varepsilon_{si}\varepsilon_0}$$

(13)

a universal curve is obtained, which is independent of substrate doping density, or substrate bias. Hereby is the empirical factor  $\eta = 1/2$  for electrons and 1/3 for holes. The resulting effective mobility then reads:

$$\mu_{\text{eff}} = \frac{\mu_{00}}{1 + E_{\text{eff}}/E_{\text{c}}} \tag{14}$$

with  $\mu 00$  the zero field maximum mobility and Ec is a critical electric field.

Early low-temperature studies revealed already that the parameter  $\eta$  is not a constant with T [46],[50],[51], but lies somewhere between 1/3 and 1, which points towards a change in dominant scattering mechanism upon cooling. More recently, detailed studies have been reported on the substrate and doping density dependence of the low temperature  $\mu_{eff}$  [64]-[66], both for n- and for p-channel devices. Emrani et al. conclude from these studies that the universal field dependence approach represented by eqs. (13) and (14) has no physical meaning at cryogenic T and should therefore not be used [54],[64]. The same conclusion followed from the effect of Fowler-Nordheim carrier injection on the low temperature  $\mu_{eff}$  [54],[65].

Fig. 9. Function defined by eq. (8) for an array of 0.7  $\mu m$  CMOS n-MOSFETs at 77 K. A reference line proportional to  $V_{GS}^2$  is drawn as a guide.

Fig. 11. Transconductance for an edgeless 58  $\mu$ mx3  $\mu$ m HRSi p-MOSFET at 300 K (full line); 77 K (dotted line) and 4.2 K (bold line) [27].

Fig. 10. Function defined by eq. (8) for an array of 1  $\mu$ m CMOS PD SOI n-MOSFETs at 77 K. The corresponding exponents are : n=2.33±0.1 (L=10  $\mu$ m); n=2.33±0.1 (L=5  $\mu$ m) and n=2.1±0.1 (L=1  $\mu$ m).

Fig. 12. Corresponding function (8) versus the gate overdrive voltage.  $n=1.92\ (300\ K);\ 1.78\ (4.2\ K)$  and  $2.08\ (77\ K).$

# 4.2 Effective mobility at high transverse electric field

Already in the mid sixties, it was found that the transconductance at large gate overdrive voltages (i.e. large normal fields) can become negative at 77 K [67]. This has more recently been confirmed for both n- and p-channel devices [68]-[70] and for MOSFETs with nitrided oxides [71]-[72]. It turns out that the critical field for zero g<sub>m</sub> is in the range 2.2-2.6 MV/cm for n-MOSFETs at 77 K and increases up to 7 to 8 MV/cm

for p-MOSFETs, depending on e.g. the gate oxide thickness [68]. In physical terms, this means that at low T, a change in scattering mechanism occurs at high normal fields. Empirically, this is modelled by introducing a second attenuation factor  $\theta_2$ , as follows [68]-[70]:

$$\mu_{\text{eff}} = \frac{\mu_0}{1 + \theta (V_{\text{GS-VT}}) + \theta_2 (V_{\text{GS-VT}})^2}$$

(15)

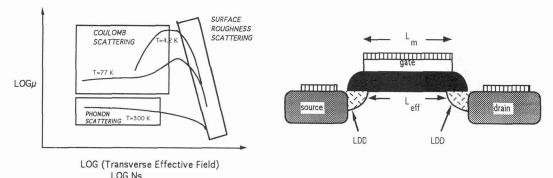

The extraction of this second attenuation factor at low temperatures is in detailed discussed in [69]. Globally speaking, the effective mobility behaviour with T can be represented schematically by Fig. 13 [49],[65]. At 300 K, the inversion layer mobility is dominated by phonon scattering for low effective fields and by surface roughness scattering at high fields. At 77 K and 4.2 K, Coulomb scattering dominates the phonon scattering at low fields, while a much stronger Eeff dependence is observed at higher fields than at 300 K. Detailed expressions can be found in the cited literature for the different scattering mechanisms, but are out of the scope of this paper. It should finally be noted that for high effective fields around 1 MV/cm nitrided oxides yield a higher  $\mu_{eff}$  than conventional oxides, both at 300 K and at liquid nitrogen temperatures, which provides a benefit [71]-[72]. The opposite is, however, true at lower effective fields.

Fig. 13. Schematical representation of the temperature and gate voltage dependence of the inversion layer effective mobility of a MOSFET.

Fig. 14. Schematical representation of a LDD MOSFET.

# 4.3 Velocity saturation and overshoot

For deep submicron MOSFETs velocity saturation at sufficiently large lateral fields creates a serious limitation of the device performance [6],[7]. In that case, the saturation drain current becomes linearly dependent on the gate overdrive voltage, instead of quadratic and can be approximated by [6]:

dependent on the gate overdrive voltage, instead of quadratic and can be approximated by [6]:

$$I_{Dsat} = \frac{1}{2} \mu_0 C_{ox} \frac{W_{eff}}{L_{eff}} \frac{(V_{GS}-V_T)^2}{[1 + \mu_0(V_{GS}-V_T)/2v_{sat}L_{eff}]}$$

(16)

which for very small device lenghts Leff-->0 reduces to the fully velocity saturated current:

$$ID_{Sat} = C_{OX} W_{eff} v_{Sat} (VGS-VT)$$

(17)

The saturation velocity  $v_{sat}$  is thus an important parameter in view of the continuous downscaling of the device dimensions and ultimately can limit the performance. In many cases,  $v_{sat}$  is derived from the drift velocity  $v_{ds}$  of the carriers in the lateral electric field  $E_s$  [73], which is given by the empirical model [6],[7],[73]:

$$v_{ds} = \frac{\mu_0 E_s}{[1 + (E_s/E_C)^{\alpha}]^{1/\alpha}}$$

(18)

The saturation velocity is next obtained from the critical drift field EC, since  $v_{sat}$ = $\mu_0$ EC. The exponent  $\alpha$  is a fitting parameter, generally ranging from 2 to 5. Recently, several alternative techniques have been

proposed to extract vsat, both at 300 K [74] and at cryogenic T [7],[8],[75]. However, due to experimental difficulties (establishing an as homogeneous as possible drift field; source-drain resistance in short-channel devices,...) a large spread is generally found, giving rise to values between  $4.2 \times 10^6$  cm/s up to  $9.2 \times 10^6$  cm/s for electrons at room temperature [75] and  $7 \times 10^6$  cm/s for holes [7]. Upon cooling  $v_{sat}$  is found to increase to values approaching 10<sup>7</sup> cm/s (electrons) or higher [7],[8]. This implies that for short-channel devices, the benefit of cooling is only a mere 20 % increase in drive current or so, which is much smaller than the factor 2 to 4 increase observed for long-channel MOSFETs. It should finally be remarked that for ultra-short channel devices, however, velocity overshoot (and hence ballistic transport) has been reported at cryogenic temperatures [9]-[11] and even at room temperature for L≈0.1 µm MOSFETs [76],[77].

## 5. EFFECTIVE LENGTH AND SERIES RESISTANCE

Present-day CMOS technologies have an architecture schematically represented by Fig. 14, containing an LDD region close to the source and drain, covered by spacer oxides. The LDD serves to reduce the maximum lateral field next to the drain junction in order to reduce hot-carrier degradation effects. As a consequence, however, the series resistance of the devices increases and furthermore is no longer independent of the gate voltage. At the same time, the electrical effective device length Leff=Lm-ΔL becomes also a function of VGS-VT.  $L_m$  is the drawn gate length and  $\Delta L$  is the channel length reduction (generally positive) which is related to source-drain lateral underdiffusion. The electrical effective length is now determined by the positions where the inversion charge density equals the LDD concentration. As both RSD and Leff are critical parameters in the MOSFET device modelling, in the past decade, extensive effort has been spent in developping extraction techniques [78]-[83].

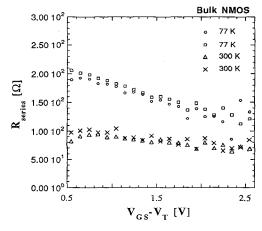

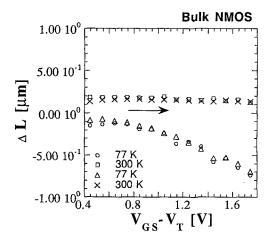

Classically,  $\Delta L$  and RSD are determined simultaneously by plotting the total measured resistance (RT=RSD+R<sub>Channel</sub>) at different VGS-VT (or inverse conductance) in linear operation versus the mask length L<sub>m</sub> [78]. The crossing point of the different lines corresponds with ΔL (horizontal axis) and with RSD (vertical axis). Applying these methods to cryogenic temperatures, negative and thus unrealistic ΔL values are found generally [26],[52],[84]-[87]. An example is given in Figs 15 and 16 for bulk n-MOSFETs: while acceptable RSD are obtained at 77 K, the negative  $\Delta L$  in Fig. 16 indicates that the proposed method is not useful for low-temperature extraction.

In order to overcome these problems, some dedicated techniques have been proposed recently, which take into account the gate voltage dependence of RDS and ΔL [84]-[86]. In that case, the total resistance as a function of the mask length is no longer considered a straight line for constant VGS-VT, but some function, where the best fit is to be determined. For instance, Ortiz-Conde et al. [84], assume that GT =1/RT is given by:

$$G_{T} = \frac{1}{2RSD} + C1 L_{eff}^{1/3} + C2 L_{eff}^{-2/3}$$

(19)

with C1 and C2 fitting parameters. In practice, it turns out that the gate voltage dependence both at 300 K and at 77 K can be described empirically by [86],[88]:

$$R_{SD} = R_{SD0} + \frac{1}{V_{GS} + a}$$

$$\Delta L = \Delta L_0 + \frac{1}{V_{GS} + b}$$

(20a)

(20b)

$$\Delta L = \Delta L_0 + \frac{1}{VGS + b} \tag{20b}$$

An alternative approach for determining the parasitic series resistance of for instance an LDD region is based on a measurement of the channel conductance gd=2ID/2VDS in the linear region [81]. If I/gd is plotted vs 1/gm at constant VGS (>VT), for different device lengths L, a straight line is obtained, which is given by:

$$\frac{1}{gd} = \frac{1}{gm} \left( \frac{1}{VGS - VT} + \theta \right) + R_{SD}$$

(21)

The Y-axis intercept should then correspond to RSD. This technique has been used to study the series resistance of the LDD region as a function of the lateral electric field [25]. At cryogenic temperatures (< 100 K), RLDD shows a pronounced reduction with the field, whereby it is believed that shallow level impact ionisation is the responsible mechanism for this reduction for an LDD lateral field E >3k V/cm.

Fig. 15. Extracted R<sub>SD</sub> as a function of the gate overdrive voltage for 0.7μm CMOS nMOSFETs at 300K and 77K.

Fig. 16. Corresponding  $\Delta L$ . The extractions were performed on two different L-arrays, with W=20  $\mu$ m [87].

## 6. POTENTIAL PITFALLS AND MEASUREMENT PROBLEMS

Upon reducing the effective device length and/or the operation temperature in the linear region, one may be concerned with the fact that for some  $V_{DS}$ , the gradual channel approximation no longer holds and for instance a non-homogeneous charge density and hence a drain voltage dependent mobility results [66]. This is for instance the case in ohmic operation for MOSFETs in the liquid helium temperature region [61], for sufficiently large lateral fields (>1 V/cm). In the literature, different empirical expressions have been proposed to model the  $V_{DS}$  dependence of  $\mu_{eff}$  [61],[89]. On the other hand, too small a  $V_{DS}$  is also impractical in general, so that a compromise has to be sought. At 77 K a  $V_{DS}$ =25 to 50 mV seems to be a reasonable value. For 4.2 K characterisation, even lower values can be considered, e.g. 10 mV.

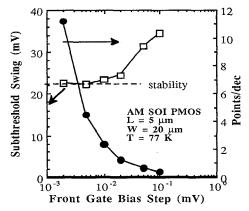

Another issue related to the recording of a low temperature input curve is the step resolution in the gate voltage. As discussed recently [41], this is particularly important for an accurate determination of the subthreshold swing. Fig. 17 illustrates the value of S obtained for different VGS steps at 77 K, for an AM SOI p-MOSFET. For too large a step, an erroneous value is obtained due to the slow response of the device on a relatively fast change in front gate voltage (so-called transient effect). For too small steps, on the other hand, the noise in the measurement becomes too large to allow a stable reading. The lower the temperature is, the lower optimal step height for a stable reading is necessary.

In deriving the effective mobility given by eq. (5), in many cases the inversion layer charge density qNS is approximated by  $qC_{OX}(VGS-VT)$ . This first of all requires an accurate determination of the charge threshold voltage VT and furthermore assumes the validity of the gradual channel approximation [66]. A more precise determination of qNS is by the split C-V technique [50],[65]. At cryogenic T, some special features are observed in this type of measurements, which are related to the slow charging/discharging of interface traps, as described recently [90],[91]. Generally, rather large-area transistors are required for this type of analysis.

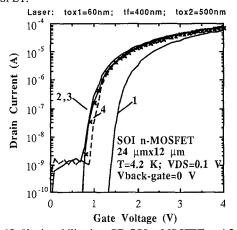

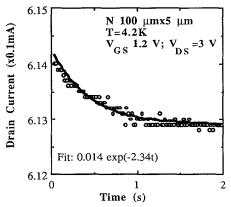

On several occasions, it has been noted that the MOSFET I-V characteristics suffer from transient and hysteresis effects. This is particularly true in the liquid helium temperature range for bulk MOSFETs [92]-[94], although for SOI devices, transients have been observed up to room temperature, whereby the typical time constants increase upon cooling [95]-[97]. For SOI MOSFETs time constants of minutes at 77 K up to hours and days at 4.2 K have been observed [98] when either the front or the back-gate bias was abruptly changed at low T. As a result, the threshold voltage can be switched to any desirable value within a certain operation margin and with a stability determined by the transient time constants. It has been suggested to utilise this so-called multistable charge-controlled memory effects at cryogenic T for one and two-transistor memory cells [98]. From a parameter-extraction viewpoint, this type of transient behaviour is highly undesirable. In many cases, it is related to the freeze-out of carriers on the dopant atoms in the substrate [94] and thus inherently related to low-temperature operation. Ways to circumvent, or at least minimise the effects is to measure the characteristics from high to low temperatures, with the bias applied

at higher temperatures [50]. Biasing at higher temperatures allows to build up the equilibrium depletion region in the substrate with much lower time constants. However, it should be remarked that upon changing the device bias at deep cryogenic T generally provokes new transient and memory effects, which are not easy to 'erase' [94]-[96].

A final concern for low temperature operation of devices is the so-called self-heating problem [99]-[103]. In brief, this phenomenon is related to the fact that the local device (lattice) temperature can be higher than the ambient temperature due to the dissipiation of the power IDVDS in the channel. This can have serious consequences for the extracted carrier mobilities in n- and p-channel devices [100]-[101]. Typical for devices suffering from selfheating is the negative differential resistance in saturation, which can be particularly pronounced for short-channel SOI MOSFETs [103]. Self-heating effects are in first order caused by an insufficient thermal contact with the cooling ambient. In case of SOI devices, the floating substrate on top of a buried oxide does not allow an efficient heat removal. However, as illustrated in Fig. 20, these effects are only thought to become important at higher VDSs in saturation.

Fig. 17. Subthreshold swing as a function of the front gate voltage step at 77 K for a 20  $\mu$ mx5  $\mu$ m SOI AM p-MOSFET.

Fig. 19. V<sub>T</sub> instability in a PD SOI n-MOSFET at 4.2 K. Curve 1 is the original measurement. Curves 2 and 3 are registered after that the drain has been swept to +3 V and +5 V respectively and curve 4 is after 24 h unbiased relaxation at 4.2 K.

Fig. 18. Transient response of a 100  $\mu$ mx5  $\mu$ m bulk n-MOSFET at 4.2 K, upon pulsing both the gate and the drain voltage from 0 V to respectively 1.2 V and 3 V. Also shown is the exponential fit to the data points.

Fig. 20. Estimation of the self-heating effect in a 100  $\mu$ mx5  $\mu$ m bulk n-MOSFET at 4.2 K. The calculated hyperbolic lines correspond to a local temperature rise in the channel of respectively 1 K and 5 K.

## 7. CONCLUSIONS

From the above overview, it is clear that there exists still a necessity for adequate parameter extraction of Si MOSFETs operated at cryogenic temperatures. The state-of-the-art has been summarised and from this follows that there are still some problem areas, related to the device parasitics which gain importance upon down-scaling the device dimensions.

## Acknowledgements

The authors would like to express their appreciation for the collaboration, the stimulating discussions and the use of (co-)authored results to: J.-P. Colinge, B. Dierickx, L. Deferm, U. Magnusson, A.L.P. Rotondaro, R. Schreutelkamp, E. Vandamme and G. Vanstraelen.

#### References

- [1] Selberherr S., IEEE Trans. Electron Devices 36 (1989) 1464-1473.

- [2] Kalonia K.S., Jain F.C., Solid-State Electron. 33 (1990) 947-951.

- [3] Selberherr S., Hänsch W., Seavey M., Slotboom J., Solid-State Electron. 33 (1990) 1425-1436.

- [4] Ghazavi P, Ho F.D., IEEE Trans. Electron Devices 42 (1995) 123-134.

- [5] Balestra F., Ghibaudo G., Solid-State Electron. 37 (1994) 1967-1975.

- [6] Sodini C.G., Ko P.-K., Moll J.L., IEEE Trans. Electron Devices 31 (1984) 1386-1393.

- [7] Taur Y., Hsu C.H., Wu B., Kiehl L., Davari B., Shahidi G., Solid-State Electron. 36 (1993) 1085-1087.

- [8] Rais K., Ghibaudo G., Balestra F., Dutoit M., Journ. de Physique IV, Colloque C6 (1994) C6/19-C6/24.

- [9] Robertson P.J., Dumin D.J., IEEE Trans. Electron Devices 33 (1986) 494-497.

- [10] Chou S.Y., Antoniadis D.A., Smith H.I., IEEE Electron Device Lett. 6 (1985) 665-667.

- [11] Sai-Halasz G.A., Wordeman M.R., Kern D.P., Rishton S., Ganin E., IÈEE Électron Devive Lett. 9 (1988) 464-466.

- [12] Gaensslen F.H., Rideout V.L., Walker E.J., Walker, J.J., IEEE Trans. Electron Devices 24 (1977) 218-229.

- [13] Gaensslen F.H., Jaeger R.C., Solid-State Electron. 22 (1979) 423-430.

- [14] Ghibaudo G., Balestra F., Solid-State Electron. 32 (1989) 221-223.

- [15] Rotondaro A.L.P., Magnusson U., Simoen, E., Claeys C., Solid-State Electron. 36 (1993) 1465-1468.

- [16] Colinge J.-P., IEEE Trans. Electron Devices 37 (1990) 718-723.

- [17] Rotondaro A.L.P., Magnusson U., Claeys C., Flandre D., Terao A., Colinge J.-P., *IEEE Trans. Electron Devices* (1994) 727-732.

- [18] Fowler A.B., Hartstein A.M., Surface Sci. 98 (1980) 169-215.

- [19] Wong H.-S., White M.-H., Krutsick T.J., Booth R.V., Solid-State Electron. 30 (1987) 953-968.

- [20] Booth R.V., White M.H., Wong H.-S., Krutsick T.J., IEEE Trans. Electron Devices 34 (1987) 2501-2508.

- [21] Terao A., Flandre D., Lora-Tamayo E., Van de Wiele F., IEEE Electron Device Lett. 12 (1991) 682-684.

- [22] Simoen E., Vandamme E., Rotondaro A.L.P., Claeys C., "The potential and restrictions of the double derivative method for threshold voltage extraction in SOI MOSFETs", Proc. of the sixth Int. Symposium on Silicon-on-Insulator Technology and Devices, S. Cristoloveanu, K. Izumi, P.L.F. Hemment and H. Hosack, The Electrochem. Society Proc. Vol. 94-11 (The Electrochem. Soc., Pennington, NJ, 1994) pp. 318-323.

- [23] Simoen E., Claeys C., Phys. Stat. Sol. (a) 148 (1995) 635-642.

- [24] Tewksbury S.K., IEEE Trans. Electron Devices 28 (1981) 1519-1529.

- [25] Hafez I.M., Ghibaudo G., Balestra F., Haond M., Solid-State Electron. 38 (1995) 419-424.

- [26] Gutiérrez E.A., IEEE Electron Device Lett. 16 (1995) 85-87.

- [27] Simoen E., Vanstraelen G., Claeys C., Semicond. Sci. Technol. 9 (1994) 1679-1685.

- [28] Woo J.C.S., Plummer J.D., IEEE Trans. Electron Devices 33 (1986) 1012-1019.

- [29] Deen M.J., Yan Z.X., IEEE Trans. Electron Devices 39 (1992) 908-914.

- [30] Yan Z.X., Deen M.J., Solid-State Electron. 33 (1990) 1265-1273.

- [31] Yan Z.X., Deen M.J., Solid-State Electron. 34 (1991) 1065-1070.

- [32] Kamgar A., Solid-State Electron. 25 (1982) 537-539.

- [33] Hafez I.M., Ghibaudo G., Balestra F., J. Appl. Phys. 67 (1990) 1950-1952.

- [34] Saks N.S., Ancona M.G., IEEE Trans. Nucl Sci. 34 (1987) 1348-1354.

- [35] Siegert R., Vitanov P., Eisele I, Solid-State Electron. 37 (1994) 1799-1808.

- [36] Ouisse T, Cristoloveanu S., Maude D.K., J. Appl. Phys. 74 (1993) 408-415.

- [37] Simoen E., Claeys C., Solid-State Electron. 36 (1993) 527-532.

- [38] Mayer D.C., IEEE Trans. Electron Devices 37 (1990) 1280-1288.

- [39] Colinge J.-P., Flandre D., Van de Wiele F., Solid-State Electron. 37 (1994) 289-294.

- [40] Martino J.A., Simoen E., Magnusson U., Rotondaro A.L.P., Claeys C., Solid-State Electron. 36 (1993) 827-832.

- [41] Martino J.A., Simoen E., Claeys C., Solid-State Electron. 38 (1995) 1799-1803.

- [42] Sun S.C., Plummer J.D., IEEE Trans. Electron Devices 27 (1980) 1497-1508.

- [43] Schwarz S.A., Russek S.E., IEEE Trans. Electron Devices 30 (1983) 1634-1639.

- [44] Kaneko M., Narita I, Matsumoto S., IEEE Electron Device Lett. 6 (1985) 575-577.

- [45] Arora N.D., Gildenblat G. Sh., IEEE Trans. Electron Devices 34 (1987) 89-93.

- [46] Takagi S., Iwase M., Toriumi A., IEDM Tech. Dig. (1988) 398-401.

- [47] De Los Santos H., Gray J.L., IEEE Trans. Electron Devices 35 (1988) 1972-1975.

- [48] Watt J.T., Fishbein B.J., Plummer J.D., IEEE Trans. Electron Devices 36 (1989) 96-100.

- [49] Jeon D.S., Burk D.E., IEEE Trans. Electron Devices 36 (1989) 1456-1463.

- [50] Hairapetian A., Gitlin D., Viswanathan C.R., IEEE Trans. Electron Devices 36 (1989) 1448-1455.

- [51] Huang C.-L., Gildenblat G. Sh., IEEE Trans. Electron Devices 37 (1990) 1289-1300.

- [52] Nguyen-Duc Ch., Cristoloveanu S., Ghibaudo G., Solid-State Electron. 29 (1986) 1271-1277.

- [53] Emrani A., Balestra F., Ghibaudo G., IEEE Trans. Electron Devices 40 (1993) 564-569.

- [54] Emrani A., Balestra F., Ghibaudo G., Solid-State Electron. 37 (1994) 1723-1730.

- [55] Gildenblat G.Sh., Huang C.-L., *Electron. Lett.* **25** (1989) 634-636. [56] Huang C.-L., Gildenblat G. Sh., *Solid-State Electron.* **33** (1990) 1309-1318.

- [57] Lee J.I., Lee M.B., Kang K.N., Electron. Lett. 26 (1990) 852-854.

- [58] Hafez I.M., Emrani A., Ghibaudo G., Balestra F., Electron. Lett. 26 (1990) 1633-1635.

- [59] Elewa T., Balestra F., Cristoloveanu S., Hafez I. M., Colinge J.-P., Auberton-Herve A.-J., Davis J.R., *IEEE Trans. Electron Devices* 37 (1990) 1007-1019.

- [60] Emrani A., Ghibaudo G., Balestra F., Piot B., Thirion V., Straboni F., J. Appl. Phys. 73 (1993) 5241-5253.

- [61] Hafez I.M., Balestra F., Ghibaudo G., J. Appl. Phys. 68 (1990) 3694-3700.

- [62] Sabnis A.G., Clemens J.T., IEDM Tech. Dig. (1979) 18-21.

- [63] Watt J.T., Plummer J.D., Proc. Symp. VLSI Technol . (1981) 81-85.

- [64] Emrani A., Ghibaudo G., Balestra F., Solid-State Electron. 37 (1994) 111-113.

- [65] Takagi S., Toriumi A., Iwase M., Tango H., IEEE Trans. Electron Devices 41 (1994) 2357-2362.

- [66] Lu W.-L., Guo J.-C., Kao C.-H., Hsu C.C.-H., Lu L.S., Jpn. J. Appl. Phys. 34 (1995) 3413-

- [67] Fang F.T., Howard W.E., Phys. Rev. Lett. 16 (1966) 797-799.

- [68] Ong T.C., Ko P.K., Hu C., IEEE Trans. Electron Devices 34 (1987) 2129-2135.

- [69] Rais K., Balestra F., Ghibaudo G., Phys. Stat. Sol. (a) 145 (1994) 217-221.

- [70] Wildau H.-J., Bernt H., Friedrich D., Seifert W., Wagemann H.G., Windbracke W., IEEE Trans. Electron Devices 40 (1993) 2318-2325.

- [71] Hori T., Iwasaki H., IEEE Electron Device Lett. 10 (1989) 195-197.

- [72] Wu A.T., Lee S.W., Chan T.Y., Murali V., Solid-State Electron. 35 (1992) 27-32.

- [73] Takagi S.T., Toriumi A., IEDM Tech Dig. (1992) 711-714.

- [74] Fikry W., Ghibaudo G., Haddara H., Cristoloveanu S., Dutoit M., Electron. Lett. 31 (1995) 762-

- [75] Chan T.-Y., Lee S.-W., Gaw H., IEEE Electron Device Lett. 11 (1990) 466-468.

- [76] Shahidi G.G., Antoniadis D.A., Smith H.I., IEEE Electron Device Lett. 9 (1988) 94-96.

- [77] Assaderaghi F., Ko P.K., Hu C., IEEE Electron Device Lett. 14 (1993) 484-486.

- [78] Chern J.G.J., Change P., Motta R.F., Godinho N., IEEE Electron Device Lett. 1 (1980) 170-172.

- [79] Suciu P.I., Johnston R.L., IEEE Trans. Electron Devices 27 (1980) 1846-1848.

- [80] Seavey M.H., IEEE Electron Device Lett. 5 (1984) 479-481.

- [81] Hao C., Cabon-Till B., Cristoloveanu S., Ghibaudo G., Solid-State Electron. 28 (1985) 1025-1030.

- [82] Hu G.J., Chang C., Chia Y.T., IEEE Trans. Electron Devices 34 (1987) 2469-2474.

- [83] Taur Y., Zicherman D.S., Lombardi D.R., Restle P.J., Hsu C.H., Hanafi H.I., Wordeman M.R.,

- Davari B., Shahidi G.G., IEEE Electron Device Lett. 13 (1992) 267-269.

- [84] Ortiz-Conde A., Liou J.J., García Sánchez M., García Nunez M., Anderson R.L., Electron. Lett. 30 (1994) 670-672.

- [85] García Sánchez F.J., Ortiz-Conde A., García Nunez M., Anderson R.L., Solid-State Electron. 37 (1994) 1943-1948.

- [86] Hwang C.Y., Kuo T.-C., Woo J.C.S., IEEE Trans. Electron Devices 42 (1995) 1863-1865.

- [87] Schreutelkamp R., Martino J.A., Simoen E., Deferm L., Claeys C., "Combined ΔL and series resistance extraction of LDD MOSFETs at 77 K", C.L. Claeys, S.I. Raider, R. Kirschman and W.D. Brown, Proc. of the Symposium on Low Temperature Electronics and High Temperature Superconductivity, The Electrochemical Society Proc. Vol. 95-9 (The Electrochem. Soc., Pennington, NJ, 1995), pp. 290-296.

- [88] Sheu B.J., Hu C., Ko P.K., Hsu F.C., IEEE Electron Device Lett. 5 (1984) 365-367.

- [89] Li J., Ma T.-P., J. Appl. Phys. 61 (1987) 1664-1666.

- [90] Viswanathan C.R., Divakaruni R., Kizziar J., IEEE Electron Device Lett. 12 (1991) 503-505.

- [91] Divakaruni R., Viswanathan C.R., IEEE Trans. Electron Devices 42 (1995) 87-93.

- [92] Rocofyllou E., Nassiopoulos A.G., Tsamakis D., Balestra F., Solid-State Electron. 32 (1989) 603-610.

- [93] Nassiopoulos A.G., Tsamakis D., Rocofyllou E., J. Appl. Phys. 68 (1990) 1896-1901.

- [94] Simoen E., Claeys C., J. Appl. Phys. 73 (1993) 3068-3081.

- [95] Wang J., Woo J., Viswanathan C.R., IEEE Electron Device Lett. 12 (1991) 300-302.

- [96] Simoen E., Gao M.-H., Colinge J.-P., Claeys C., Semicond. Sci. Technol. 8 (1993) 423-428.

- [97] Martino J.A., Rotondaro A.L.P., Simoen E., Magnusson U., Claeys C., *IEEE Trans. Electron Devices* 41 (1994) 519-523.

- [98] Tack M.R., Gao M.-H., Claeys C.L., Declerck G.J., *IEEE Trans. Electron Devices* 37 (1990) 1373-1382.

- [99] Sesnic S.S., Craig C.R., IEEE Trans. Electron Devices 19 (1972) 933-942.

- [100] Foty D., Titcomb L., IEEE Trans. Electron Devices **34** (1987) 107-113.

- [101] Foty D., IEEE Trans. Electron Devices 36 (1989) 1542-1544.

- [102] Gutiérrez E.A., Deferm L., Declerck G., Solid-State Electron. 36 (1993) 41-52.

- [103] Jomaah J., Ghibaudo G., Balestra F., Solid-State Electron. 38 (1995) 615-618.