# SPICE MODEL FOR TRANSIENT ANALYSIS OF EEPROM CELLS

R. Bez, D. Cantarelli, P. Cappelletti, F. Maggioni

### ▶ To cite this version:

R. Bez, D. Cantarelli, P. Cappelletti, F. Maggioni. SPICE MODEL FOR TRANSIENT ANAL-YSIS OF EEPROM CELLS. Journal de Physique Colloques, 1988, 49 (C4), pp.C4-677-C4-680. 10.1051/jphyscol:19884142. jpa-00227880

## HAL Id: jpa-00227880 https://hal.science/jpa-00227880

Submitted on 4 Feb 2008

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. SPICE MODEL FOR TRANSIENT ANALYSIS OF EEPROM CELLS

R. BEZ, D. CANTARELLI, P. CAPPELLETTI and F. MAGGIONI

SGS-Thomson Microelectronics, Via C. Olivetti 2, Agrate Brianza (MI), Italy

Abstract. An equivalent model for the EEPROM cell, described on a SPICE circuit analyzer, is used for the transient analysis of erase(E)/write(W) characteristics with ramp waveform programming pulses. The results of the simulation are compared with the experimental data obtained by an innovative method for measuring E/W curves. The validation of the model is made over different variations of the cell lay-out, different programming voltages and different rise times for the ramp of the programming pulse.

#### 1 Introduction

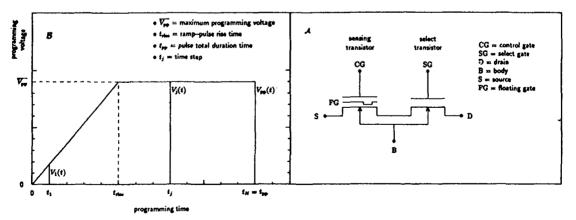

The two transistors FLOTOX cell (Fig. 1.A) is the most widely used among the memory devices proposed for Electrically Erasable Read Only Memories (EEPROM). The first analytical model for this type of EEPROM cell has been proposed by Bhattacharyya in 1984 [1]. A more detailed circuit model has been implemented by Kolodny et al.[2] in order to simulate the shift of the cell threshold voltage after step programming pulses.

Figure 1. A: two transistors FLOTOX cell scheme. B: a typical ramp waveform programming pulse.  $V_{pp}(t)$  is the complete pulse;  $V_j(t)$  is the  $V_{pp}(t)$  stopped at  $t = t_j$ .

C4-677

In actual device operation the cell is prógrammed with a ramp waveform pulse in order to minimize the tunnel current (the peak value of programming current is known to be proportional to the ramp speed): in this case the threshold shift is a function of both the ramp rise time and the pulse width for a fixed pulse amplitude. Therefore an accurate simulation of the transient behavior (*i.e.* threshold shift *vs.* time) of the cell during the programming cycle is desirable.

In this work an equivalent model for transient analysis of EEPROM cell is proposed. The model is described in term of SPICE [3] components in order to utilize a well proven MOSFET capacitance model. A further advantage in using SPICE is the linkability of the cell model to other circuital blocks for global simulation. An innovative experimental method, able to measure transient E/W characteristics, is used for validating and optimizing the model.

#### 2 Experimental

E/W curves are defined as threshold voltage vs. time, where, for operative reasons, the threshold voltage  $(V_{CG}^{T})$  is defined as the control-gate voltage measured at fixed drain current  $(I_{D} = 10\mu A \text{ with } V_{D} = 2V)$  and  $V_{S} = V_{B} = 0V$ . Erasing (writing) is defined as the programming operation, which sets the negative (positive) charge state on the floating-gate, *i.e.* the high (low) threshold voltage condition.

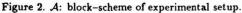

E/W curves are measured for programming pulses  $V_{pp}(t)$  with a ramp waveform (Fig. 1B). A block-scheme of the experimental setup is shown in figure 2A. The programming pulses are generated by an HP 8160A programmable pulse generator. The threshold detector is a current-voltage converter, which forces on the control-gate the voltage needed to sustain a  $10\mu$ A drain current; this *ad hoc* designed circuit allows a faster measurement of the threshold voltage, which is measured by a Keithley 192 DMM voltmeter. All instruments are controlled by an HP 300 computer.

**B**: SPICE equivalent model for the FLOTOX cell. Element description: MSEN=sensing transistor; MSEL, select transistor; CPP=CG-FG capacitance; CX=FG-X capacitance (X=D,S and B); VY=voltage source (Y=CG,SG,D and B); VSI=voltage source simulating voltage drop in silicon; DFN=Fowler-Nordheim diode; TCI=tunnel current integrator. Node description: 1=sensing transistor drain; 2=FG; 3=CG; 4=B; 5=D; 6=SG; 7=S; 8=silicon surface underneath tunnel oxide; 9,10=unreal nodes added for simulation purposes.

In order to clarify how the E/W characteristics are obtained let us refer to the writing curve. The programming pulse timebase is divided into N time steps  $t_1..t_y..t_N = t_{pp}$ . After cycling the cell few tens of times in order to stabilize the threshold shift, N values of the threshold voltage  $(V_{CG_j}^T)$  are measured after stopping the writing pulse at each time step; before each  $V_j(t)$  writing pulse, complete (*i.e.*  $V_{pp}(t)$ ) E/W pulses are applied to reset the cell to the initial erased state. The writing curve is obtained by plotting the N values  $V_{CG_j}^T = V_{CG}^T(t_j)$  vs. the programming time.

#### 3 Simulation

The equivalent circuit shown in figure 2B is described in terms of SPICE components to simulate the EEPROM cell; the description of each component of the circuit is made in the figure caption. The "tunnel diode" (DFN) model can be easily introduced in SPICE using the well known Fowler-Nordheim (FN) equation [4]: external parameters are the pre-exponential and the exponential constants (usually called A and B), the tunnel oxide thickness and the tunnel oxide area. The Ward-Dutton [5] charge model is used for simulating the gate-to-channel capacitance of the sensing transistor. A voltage source (VSI) is introduced to take into account the voltage drop in the  $n^+$  depleted region underneath the tunnel oxide during the writing cycle. A Tunnel Current Integrator *TCI* is added to the circuit to determine at the node 10 a voltage value equivalent to the threshold shift.

The DFN parameters are fixed, using theoretical values for A and B ( $A = 1.67 \times 10^{-6} AV^{-2}$ , B= 224MVcm<sup>-1</sup>) and the measured ones for the tunnel oxide thickness and area. The capacitance values are chosen as fitting parameters of the model, because they can hardly be determined from experimental data. Anyway the fitting values are within a 15% variation from the lay-out capacitances.

In order to compare simulations and experimental data is useful to put an initial condition on node 10 to obtain the threshold voltage instead of the threshold shift. Moreover an initial condition can be put also on node 2 to simulate the charge on the floating-gate due to a programmed state.

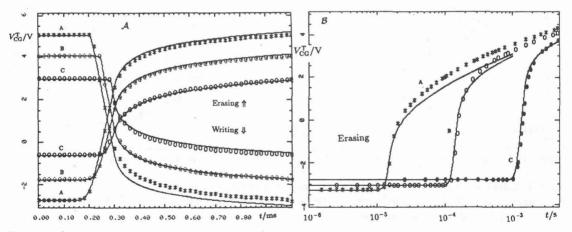

Figure 3. Comparison between simulated (solid line) and measured (symbols) E/W characteristics (*i.e.* threshold voltage,  $V_{CG}^{T}$  vs. time t) of the standard cell (SC). A: the ramp waveform programming pulse  $V_{pp}(t)$  is used with the same  $t_{rise}$  ( $t_{rise} = 300\mu$ s) and the same  $t_{pp}$  ( $t_{pp}=1$ ms) but with different  $V_{pp}$  (A:  $V_{pp}=16V$ ; B:  $V_{pp}=15V$ ; C:  $\overline{V_{pp}}=14V$ ). B: the  $V_{pp}(t)$  is used with the same  $\overline{V_{pp}}$  ( $\overline{V_{pp}}=15V$ ) and the same  $t_{pp}$  ( $t_{pp}=5$ ms) but with different  $t_{rise}$  (A:  $t_{rise} = 15\mu$ s; B:  $t_{rise} = 150\mu$ s; C:  $t_{rise} = 1.5$ ms).

#### 4 Discussion

First the analysis are centralized on a standard cell (SC) operating with  $\overline{V_{pp}}$  at different values with the same  $t_{rise}$  (Fig. 3.4): a good agreement (an error of 3% in the worst case) between simulation and experimental data is found for the complete E/W curve and in particular for the final threshold shift.

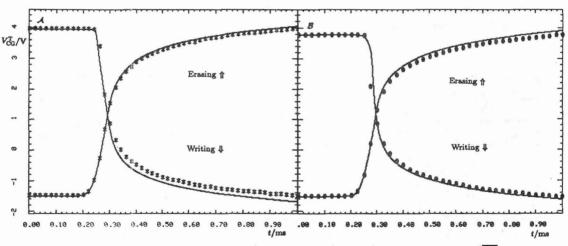

Secondly, the model is validated on different cells, each of one having a single lay-out variation with respect to the SC, *e.g.* the tunnel oxide area or the active area are increased; modifying only those physical parameters in the SPICE EEPROM model that are interested in the lay-out variation, the experimental data are again fitted with a good accuracy (Fig. 4).

Finally different  $t_{rise}$  and different  $t_{pp}$  with the same  $\overline{V_{pp}}$  are considered, operating on the SC. In this case the same fitting parameters are not able to give an acceptable fitting, if  $t_{rise}$  and/or  $t_{pp}$  are changed over wide ranges (Fig. 3B). These discrepancies are attributed to the inaccuracy of the theoretical FN equation to model the actual tunnel current, which is known to deviate from the FN equation at high electric fields [6,7]. In conclusion:

1. the SPICE EEPROM model is able to simulate correctly the transient behavior of the cell (and indeed the physical E/W mechanism), but using fitting parameters;

2. the parameters, found by fitting, are able to take into account cell lay-out variation and/or different  $\overline{V_{pp}}$  values, but they are not for different ramp speed;

3. to obtain a self consistent EEPROM model, able to simulate any programming condition, the exact form of the tunnel current in the high electric field range or, at least, different experimental A and B values for different electric field ranges, should be used in the DFN model.

Figure 4. Comparison between simulated (solid line) and measured (symbols) E/W characteristics ( $\overline{V_{pp}}=15V$ ,  $t_{rise} = 300\mu s$  and  $t_{pp}=1ms$ ) of different cells, having a single lay-out variation with respect to the SC. A: tunnel oxide area increased by 40%; B: active area increased by 7%.

- [1] A.Bhattacharyya, Solid State Electronics, 27,899,1984

- [2] A.Kolodny, IEEE Trans. Electron Devices, 6, 835, 1986

- [3] SGS-Thomson SPICE Version, 1987

- [4] M.Lenzlinger and E.H.Snow, J. Appl. Phys., 4, 278, 1969

- [5] D.E.Ward, Technical Report G201-11, Stanford Electrical Laboratories, 1981

- [6] M.Itsumi, J. Appl. Phys., 52, 3491, 1981

- [7] M.Shatzkes and M.Av-Ron, J. Appl. Phys., 47, 3192, 1976