## Synchronous conditioning circuits for piezo-and triboelectric harvesters in CMOS technologieś

Elie Lefeuvre, Dimitri Galayko

#### ▶ To cite this version:

Elie Lefeuvre, Dimitri Galayko. Synchronous conditioning circuits for piezo-and triboelectric harvesters in CMOS technologieś. 2020 27th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Nov 2020, Glasgow, United Kingdom. pp.1-4, 10.1109/ICECS49266.2020.9294822. hal-03158528

HAL Id: hal-03158528

https://hal.science/hal-03158528

Submitted on 4 Mar 2021

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Synchronous conditioning circuits for piezo- and triboelectric harvesters in CMOS technologies

#### Élie Lefeuvre

Centre for Nanoscience and Nanotechnology, Univ. Paris-Saclay - CNRS, Palaiseau, France elie.lefeuvre@universite-paris-saclay.fr

#### Dimitri Galayko

Sorbonne Université, CNRS, LIP6, UMR7606, Paris, France Centre for Nanoscience and Nanotechnology, Université Paris-Saclay - CNRS, Palaiseau, France dimitri.galayko@lip6.fr

Abstract—This focus paper proposed for the track "Energy Harvesting and Power Efficient Electronics" addresses the new generation of conditioning circuits based on active energy extraction techniques, designed by the term "synchronous conditioning circuits". Initially proposed for enhancing energy yield of piezoelectric transducers having intrinsic poor quality, these techniques are now a part of the established method not only for piezoelectric devices, but also for triboelectric transducers. Their recent success is due to intensive use of integrated CMOS technologies optimized for low-energy power converters, which allowed to build highly efficient systems even in the case when the input energy is of few microwatts.

This paper shortly reviews the synchronous energy extraction technique and their applications, and then discusses recent successful implementations in CMOS technologies.

Index Terms—Energy harvesting, piezoelectric transducer, power converter, conditioning circuits, SSHI, SECE

#### I. INTRODUCTION

Energy harvesting from ambient vibrations has been considered as a promising technique for supplying small autonomous systems in situations where a battery replacement is difficult or undesirable. Implanted/worn biomedical electronics is the most prominent example of such systems.

A kinetic energy harvester (KEH) is composed of an electromechanical device and of a conditioning electronics. A vast majority of efforts of the scientific community have been focused on design and optimisation of electromechanical device, which is responsible for energy conversion from mechanical into electrical domain. However, the importance of the conditioning electronics should not be underestimated, if one wishes to exploit the full potential of electromechanical devices. A conditioning circuit implements a dynamic biasing of the transducer, required for maximization of the energy extraction from the mechanical domain.

Elementary conditioning circuits for piezoelectric, electret and triboelectric transducers include passive charge pumps based on diode-capacitance networks, such as rectifiers and charge pumps. However, in many practical cases more evolved active circuits called "synchronous conditioning circuits" may greatly leverage the energy extraction. Having been considered of complex and difficult implementation for a long time, recently several practical studies have demonstrated working prototypes of such circuits implemented in CMOS technologies, highlighting impressive performances in terms of power overhead, input voltages and conversion efficiency.

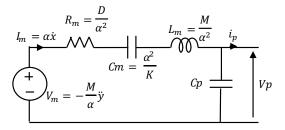

Fig. 1. Equivalent circuit of a single-mode piezoelectric energy harvester.

This paper is devoted to a review of the recent advancement of the circuits in this field.

#### II. SYNCHRONOUS ENERGY EXTRACTION TECHNIQUES

#### A. Motivation for synchronous energy extraction techniques

The development of synchronous conditioning circuits (SCC) was motivated by the willingness to maximize the harvested power whilst minimizing the power lost in the interface [1], [2]. To further explain this topic, let the system composed of a mechanical resonator and a piezoelectric transducer represented by its equivalent circuit of fig. 1 [3]. According to the maximum power transfer theorem, the output power is maximum when the load impedance is optimal. Thus, the extracted power reaches its maximum limit, which can be expressed as (1) considering a harmonic vibration acceleration  $\ddot{y} = \gamma_m \sin(\omega t)$ , with  $\omega_0 = 1/\sqrt{L_m C_m}$  the mechanical resonant angular frequency and Q the mechanical quality factor.

$$P_{lim} = \frac{M\gamma_m^2}{8\omega_0}Q = \frac{\alpha^2 L_m^2 \gamma_m^2}{8R_m} \tag{1}$$

In theory,  $P_{lim}$  can be attained at any frequency if the load impedance is adequately tuned [3]. In practice, the implementation of such interface circuit is jeopardized by its complexity and energy consumption. Therefore, techniques with simpler implementation are preferred in a domain where each microwatt matters. The most commonly used interface circuit is simply composed of a full bridge rectifier and a filter capacitor (FBR+FC). Alternatively, it was shown that the performances can be improved at low energy cost using the so-called Synchronous Conditioning Circuits (SCC) [1], [2]. The key parameters of the piezoelectric resonator for energy harvesting are the mechanical quality factor Q and the expedient electromechanical coupling factor  $k_m$  [3]. These

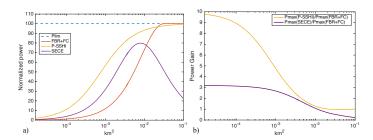

Fig. 2. Comparison between the three circuits : a) Maximum normalized power vs  $k_m^2$  using the FB+CF, P-SSHI and SECE interfaces (Q=100), b) Power gain vs  $k_m^2$  of P-SSHI and SECE interfaces compared to FBR+FC circuit (Q=100).

two parameters define the electromechanical figure of merit, as highlight eq. (2):

$$k_m^2 = \frac{\alpha^2}{KC_p} = \frac{C_m}{C_p} FoM = k_m^2 Q = \frac{\sqrt{L_m C_m}}{R_m C_p} = \frac{1}{R_m C_p \omega_0}$$

(2)

When the FoM is much less than 1, the conventional circuit FBR+FC is unable to approach  $P_{lim}$ . In this case, the use of SCC is fully justified. Here we compare the FBR+FC with two SCC: parallel Synchronous Switching for Harvesting on Inductor (P-SSHI) and Synchronous Electrical Charge Extraction (SECE).

Fig. 2a compares the maximum normalized harvested power as a function of  $k_m^2$  for these tree interfaces connected to the single-mode model of Fig. 1. Note that the only losses of the interface circuits taken into account were those of the inductor of the P-SSHI and the SECE circuits. As shown in Fig. 2a,  $P_{lim}$  is attained for  $k_m^2 \geq \pi \cdot 10^{-2}$  in the case of the FBR+FC circuit, whereas  $P_{lim}$  is approached but never attained in the case of the SECE and the P-SSHI circuits, due to the inductor losses. In counterpart, these two SCC exhibit much better performances than FBR+FC when  $k_m^2 \leq 10^{-2}$ , which corresponds to a  $FoM \leq 1$ . In this case, significant gain in terms of maximum harvested power can be obtained using the SCC (fig. 2b).

#### B. Basic principles of SCC

The basic principle in common to all the SCC is to change the electrical boundary conditions of the piezoelectric resonator in a very short space of time, synchronously with the mechanical motion of the resonator, in a manner that promotes energy conversion. They have also in common the ability to change the boundary conditions using a quasi-adiabatic process, which minimizes energy losses. In addition, their control principle is generally very simple [3].

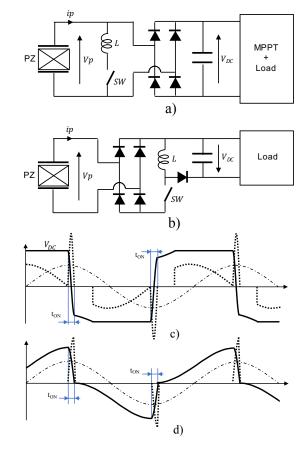

Figure 3 represents the schematic diagrams of the P-SSHI and SECE conditioning circuits. Typical waveforms of the piezoelectric voltage and current obtained using these circuits are shown in Figure 9. In the case of the P-SSHI technique, the polarity of the piezoelectric voltage is inversed each time the mechanical displacement reaches an extremum. This polarity inversion is obtained using a L-C-R energy oscillation: when SW is closed, the inductor L is connected in parallel with the circuit of fig. 1 and the FBR input. The ON time  $t_{ON}$  is set to

Fig. 3. Schematics of the interface circuits (a) P-SSHI, (b) SECE and typical waveforms of x, Vp and ip with the interface circuits (c) P-SSHI, (d) SECE.

reopen SW after a half period of the L-C-R resonant circuit. In order to quickly change the boundary conditions, the inductor L value is chosen so that the L-C-R resonant frequency is much higher than the mechanical vibration frequency. The control of the electronic switch is slightly different in the case of the SECE circuit: the time duration  $t_{ON}$  is set to reopen SW when the piezoelectric voltage is null. In both cases, the piezoelectric voltage amplitude is increased compared to the FRB+FC circuit. This phenomenon must be anticipated for the design of the transducer and the choice of the electronics technology to get compatible maximum voltages.

For the sake of conciseness, the presentation was limited here to the P-SSHI and SECE. These circuits have actually given rise to several other SCC with various features, achieving a trade-off between frequency bandwidth, maximum power output, ability to handle efficiently low or high piezoelectric voltages, and simplicity of implementation.

### III. REVIEW OF RECENT IMPLEMENTATION OF SCC IN INTEGRATED TECHNOLOGIES

Most of successful implementations of SCC have used 0.18  $\mu m$  or 0.35 $\mu m$  technologies, due to requirement of high voltage blocking, of low leakage and of reduced area cost. Use of old an inexpensive technologies allows one to integrate passive components and high dimension analog transistors.

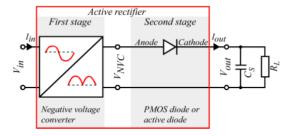

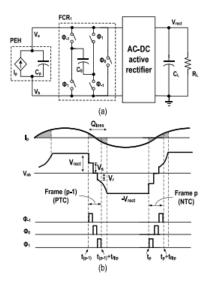

A full-bridge rectifier, used in the majority of conditioning circuits, has recently been implemented with a new circuit

Fig. 4. Circuit implementing a zero threshold full-wave rectifier function [4].

suppressing or minimising the diode threshold effects. Proposed in 2011 [4], this two-stage rectifier is composed of a CMOS-based negative voltage converter and an active diode (see fig. 4). This solution has became a standard in the energy harvesting AC-DC rectifiers [5]–[8].

The on-chip integration imposes some specific constraints on the design. For instance, the inductor required in SSHI and SECE architectures is of few millihenry, which makes impossible its integration. Generally, an inductor is also needed for a BUCK DC-DC converter interfacing the conditioning circuit and the load. A single inductor may be enough if the inductor sharing technique is used, as in [7], [9].

#### A. SSHI implementations

Fundamental and detailed report on a CMOS implementation of SSHI circuits and on associated challenges can be found in [9], [10]. Many recent work consolidated the results and improved the design by introducing a rectifier as in fig. 4 [6], [7], MPPT control, etc.

The most critical point of the SSHI implementation is the detection of the time instant of the bias-flipping switch activation (see sec. II-B). The activation needs to happen at zero motional current  $i_m$  which corresponds to a zero current  $i_n$  (fig. 1). This current cannot be measured directly: the zero current detection requires a voltage measurement on the rectifier circuit. Two techniques has been used. The first one consists in comparing the voltage  $V_{p+}$  and  $V_{p-}$  with a reference voltage setting slightly above  $-V_d$  (diode threshold) [9], [10]. A comparison with a negative voltage requires a use of involved circuitry for generation of negative supply (below  $-V_d$  in order to prevent the direct current in the transistor active areas). When the rectifier uses the negative voltage converter as in fig. 4, the information about the current zero crossing is provided by the second stage diode: either it is possible to compare the "Anode" and "Cathode" voltages [6] or, if an active diode is used, the gate control voltage of the active diode provides directly the information about the zero current event [7]. The switching off of the SSHI switch after the successful Cp voltage flipping requires either a tunable timing circuitry depending on the period of the resonant LCp network [9], [10], or a use of blocking (Schottky) diodes preventing the inversion of the inductor current [6], the latter solution coming at a price of losses in the diodes.

As the SSHI circuit operates properly (see discussion in sec. II-B), the voltage amplitude on the transducer increases. For transducers with low FoM, the optimal voltage is much larger than the optimal voltage of the FBR+FC interface. It might be

Fig. 5. SSHI implemented with a switched capacitor technique [13]

above the maximum voltage allowed by the technology, and then, the regulation is just the maximum voltage allowed by the technology. However, if the transducer and the electronics are well adapted in terms of voltage, an additional MPPT circuit is required to make optimal use of the SSHI interface.

The commonly admitted figure of merit of active conditioning circuit is the improvement with regard to conditioning circuit with an ideal full-bridge rectifier (see fig. 2b). The reported figures are 681% [7], 580% [11], 300% [6]. The "voltage flipping efficiency" is also an important figure, characterizing the losses during the transducer voltage flipping specific to the SSHI. The reported figures are 0.94 [7] and 0.75 [9], [10].

The minimum input power at which the harvester is able to operate is also an interesting figure, especially for use with miniature electromechanical devices providing only few microwatts power. The recently reported figures are 4  $\mu W$  [7] and 2.8  $\mu W$  in [6]. The reported consumption of the control circuitry are below 1  $\mu W$  in works [10], 0.5  $\mu W$  in [6] and 2  $\mu W$  in [9].

Some variants of SSHI circuits have recently been implemented. The Synchronous Switch circuit employs a switch which short circuits the transducer at zero  $I_p$ . No inductor is used. The maximum efficiency gain with regard to an ideal full bridge rectifier is 200%, however, the implementation and integration are much straightforward than for an SSHI [12].

Inductive transfer may be implemented with switched capacitor technique, as demonstrated in [13] (see fig. 5). The circuit uses an active rectifier [14], and flips the transducer voltage with few cycles of switched capactior charge pump. All capacitors are on-chip integrated, with the output power of 50  $\mu$ W and a 480 % of power yield of an ideal full-bridge rectifier. It is remarkable that the circuit is intended to operate at a high frequency (110 kHz) in an ultrasound remote powering application.

#### B. SECE circuits

The SECE circuits are situated between passive (full-bridge based) rectifiers and active SSHI converters. In the SECE

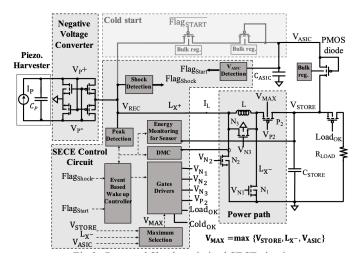

Fig. 6. Architecture of the SECE circuit [15].

mode, the piezoelectric transducer operates nearly always in an open circuit autonomous configuration. As the transducer voltage and the electrostatic energy reaches the maximum, the conditioning circuit transfers the accumulated energy to a storage capacitor, so emptying the transducer. The SECE circuit allows in the best case only a 4x times improvement with regard to a full wave rectifier, but its implementation is much simplier, and the it is widely used with transducers generated high voltage, such as electret and triboelectric transducers. The SECE technique may be efficient from the very first voltage maximum detected by the circuit, while SSHI needs several oscillation periods in order to accumulate the optimal energy on the transducer. As a consequence, the SECE technique is considered to be more suitable for applications where the vibrations are irregular, arriving by shocks and by intermittency.

We first mention one of the most achieved implementation of SECE circuit [15] implemented in 40 nm CMOS technology with 10 V option, and optimized for harvesting energy from sporadic vibrational shocks. The overall architecture is given in fig. 6, with gray blocks being integrated on chip. 'The circuit highlights impressive performance accepting input power starting from 80 nW, highlights 30 nA quiescent current and 94% conversion efficiency.

In order to reduce the peak current in the inductor and the associated losses, a pulsed (multi-shot) transfer is sometimes used. The study [5] highlight a 16% improvement of the efficiency by using a multi-shot technique.

The same group has recently implemented a modified integrated SECE CC allowing a bandwidth extension by adaptive impedance matching [16]. A fully-integrated interface, except the inductor and storage capacitor, allows a positive conversion yield starting from 600 nW input power.

SECE technique has recently became popular for low impedance electrostatic devices generating high voltages, such as triboelectric and electret biased transducers. In triboelectric generators, the energy production is achieved by peak charges generation, and this makes the SECE techniques highly appropriate [17]. A specific problem related to the triboelectric generators is in inequality of positive and negative voltage

peaks, that makes conventional rectifier inefficient. Specific dual-input converters are implemented in order to address this difficulty. The work [18] presents an integrated CC (CMOS 0.18  $\mu$ m BCD) compatible with a 4.5 to 16  $\mu$ W input energy operating till 70 V input voltage.

#### IV. CONCLUSION

Sophisticated conditioning circuits intended to push miniature electromechanical energy converters to its physical limits are highlighting tremendous progresses since 10 years. Advanced analog signal processing and computation implemented in CMOS chips allow one to achieve complex functions such as on-line MMPT, adaptive impedance adaptation and power management. Several recent implementations of optimized conditioning circuits for miniature harvesters highlight a very low power overhead, not exceeding 1  $\mu$ W.

However, among existing approaches of optimized energy extraction, only few techniques have recently been implemented (mainly SSHI and SECE). The full potential of adaptive interfaces for kinetic energy harvester is still to be exploited, offering unique cooperation opportunities between the community of CMOS designers and micro and nano device physicists.

#### REFERENCES

- [1] D. Guyomar, A. Badel, E. Lefeuvre, and C. Richard, *IEEE transactions on ultrasonics, ferroelectrics, and frequency control*, vol. 52, no. 4, pp. 584–595, 2005.

- [2] E. Lefeuvre, A. Badel, C. Richard, and D. Guyomar, Journal of Intelligent Material Systems and Structures, vol. 16, no. 10, pp. 865– 876, 2005.

- [3] A. Badel and E. Lefeuvre, in Nonlinearity in Energy Harvesting Systems. Springer, 2016, pp. 321–359.

- [4] C. Peters, J. Handwerker, D. Maurath, and Y. Manoli, *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 58, no. 7, pp. 1542–1550, 2011.

- [5] T. Hehn, F. Hagedorn, D. Maurath, D. Marinkovic, I. Kuehne, A. Frey, and Y. Manoli, *IEEE Journal of Solid-State Circuits*, vol. 47, no. 9, pp. 2185–2198, 2012.

- [6] E. E. Aktakka and K. Najafi, IEEE Journal of Solid-State Circuits, vol. 49, no. 9, pp. 2017–2029, 2014.

- [7] D. A. Sanchez, J. Leicht, E. Jodka, E. Fazel, and Y. Manoli, in 2016 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 2016, pp. 366–367.

- [8] A. Quelen, A. Morel, P. Gasnier, R. Grézaud, S. Monfray, and G. Pillonnet, in 2018 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2018, pp. 150–152.

- [9] Y. K. Ramadass and A. P. Chandrakasan, *IEEE journal of solid-state circuits*, vol. 45, no. 1, pp. 189–204, 2009.

- [10] S. Du, Y. Jia, C. D. Do, and A. A. Seshia, *IEEE Journal of Solid-State Circuits*, vol. 51, no. 11, pp. 2729–2742, 2016.

- [11] S. Du, Y. Jia, C. Zhao, G. A. Amaratunga, and A. A. Seshia, *IEEE Sensors Journal*, vol. 20, no. 1, pp. 277–285, 2019.

- [12] X.-D. Do, H.-H. Nguyen, S.-K. Han, D. S. Ha, and S.-G. Lee, *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 23, no. 3, pp. 444–453, 2014.

- [13] Z. Chen, M.-K. Law, P.-I. Mak, W.-H. Ki, and R. P. Martins, *IEEE Journal of Solid-State Circuits*, vol. 52, no. 12, pp. 3168–3180, 2017.

- [14] H.-K. Cha, W.-T. Park, and M. Je, *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 59, no. 7, pp. 409–413, 2012.

- [15] A. Morel, A. Quelen, P. Gasnier, R. Grézaud, S. Monfray, A. Badel, and G. Pillonnet, *IEEE Journal of Solid-State Circuits*, vol. 53, no. 12, pp. 3420–3433, 2018.

- [16] A. Morel, A. Quelen, C. A. Berlitz, D. Gibus, P. Gasnier, A. Badel, and G. Pillonnet, in 2020 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2020, pp. 488–490.

- [17] L. Zhou, D. Liu, J. Wang, and Z. L. Wang, Friction, pp. 1–26, 2020.

- [18] I. Park, J. Maeng, D. Lim, M. Shim, J. Jeong, and C. Kim, in 2018 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2018, pp. 146–148.