## SymBIST: Symmetry-based Analog/Mixed-Signal BIST

Antonios Pavlidis, Marie-Minerve Louërat, Eric Faehn, Anand Kumar, Haralampos-G. Stratigopoulos

### ▶ To cite this version:

Antonios Pavlidis, Marie-Minerve Louërat, Eric Faehn, Anand Kumar, Haralampos-G. Stratigopoulos. SymBIST: Symmetry-based Analog/Mixed-Signal BIST. 32. GI / GMM / ITG - Workshop Testmethoden und Zuverlässigkeit von Schaltungen und Systemen, Feb 2020, Ludwigsburg, Germany. hal-02466029

HAL Id: hal-02466029

https://hal.science/hal-02466029

Submitted on 4 Feb 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# SymBIST: Symmetry-based Analog/Mixed-Signal BIST

Antonios Pavlidis\*, Marie-Minerve Louërat\*, Eric Faehn<sup>†</sup>, Anand Kumar<sup>‡</sup>, Haralampos-G. Stratigopoulos\*

\*Sorbonne Université, CNRS, LIP6, Paris, France

<sup>†</sup>ST Microelectronics, Crolles, France

<sup>‡</sup>ST Microelectronics, Greater Noida, India

#### I. INTRODUCTION

The large number of Integrated Circuits (ICs) deployed in modern safety- and mission-critical applications has created an increasing interest to avoid IC malfunctions in the field and reduce the test escapes down to sub-ppm levels. Regarding Analog and Mixed-Signal (A/M-S) ICs, many case studies have shown that the standard specification tests performed on Automated Test Equipment (ATE) offer no guarantee to meet this quality requirement [1]. To this end, performing defect-oriented Built-In Self-Test (BIST) on top of the standard specification tests and proving high defect coverage can address safety concerns. The premise of BIST in this context is that it can detect latent defects and defects that will be triggered in the context of system operation in the field provoked by environmental stress.

In this paper, we present a defect-oriented BIST strategy for A/M-S ICs, called symmetry-based BIST or *SymBIST*. We demonstrate how *SymBIST* can be successfully applied to a 65nm 10-bit Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) IP by ST Microelectronics.

Existing works on ADC BIST focus on functional BIST [2]–[6]. The main reason for the lack of defect-oriented ADC BIST solutions is the long ADC simulation time, typically in the order of hours, which prohibits a defect simulation campaign. Thanks to the fast test time accomplished by *SymBIST*, and by using the recent mixed-signal defect simulator Tessent®DefectSim by Mentor®, A Siemens Business [7], we were able to run very fast in a automated workflow defect simulation for hundreds of defects and compute defect coverage for the entire IP.

#### II. SymBIST PRINCIPLE

The proposed *SymBIST* paradigm exploits existing symmetries into an A/M-S design and builds invariant properties that should hold true only in defect-free operation.

The underlying observation is that symmetries are inherent to virtually all A/M-S designs. Inherent symmetries exist thanks to fully-differential (FD) signal processing, complementary signal processing, and replication of identical blocks. For example, for node pairs carrying FD or complementary signals we can build an invariance in the form of  $V_1 + V_2 = \alpha$ , where  $V_1$  and  $V_2$  are the nodes' voltages and  $\alpha$  is a constant, i.e., in the case of FD signals  $\alpha = 2V$  cm, where V cm is the common mode voltage [8]. Symmetries can also be created artificially with reconfiguration using switches, duplication of blocks, or pseudo-duplication of blocks.

These invariances can be checked with a window comparator circuit implementing a comparison window  $[-\delta, \delta]$ ,  $\delta > 0$ , to account for process, voltage, and temperature variations. If the

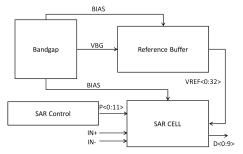

**Fig. 1:** Top-level architecture of SAR ADC.

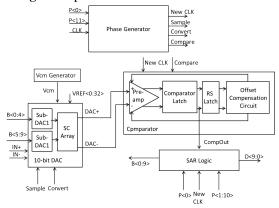

Fig. 2: SARCELL block-level architecture.

invariant signal slides outside the window, then this points to defect detection.

#### III. SymBIST APPLIED TO SAR ADC IP

The top-level of the SAR ADC IP architecture is illustrated in Fig. 1. The circuit accepts a FD analog input  $\Delta IN=IN^+-IN^-$ . The SAR algorithm is implemented into the main SAR CELL block whose block-level architecture is shown in Fig. 2.

Looking into the architecture of the SAR ADC IP, we identified 6 invariances that hold true for any FD input  $\Delta$ IN and at every conversion cycle and cover the entire A/M-S part of the SAR ADC IP. The same test stimulus is used for checking all of these invariances. In particular, the FD input  $\Delta$ IN stays constant at a DC value which can be set arbitrarily and a 5-bit digital counter is used that generates all possible  $2^5$  bit combinations at the inputs B < 0: 4 > and B < 5: 9 > of the two sub-DACs composing the 10-bit DAC. The rationale for this dynamic part of the test stimulus is that it excites all A/M-S sub-blocks. If the 6 invariances are checked sequentially, the test is completed very fast in  $6*2^5\cdot(1/f_{clk})=1.23\mu{\rm sec}$ , where  $f_{clk}=156{\rm MHz}$  is the sampling clock frequency. This time equals about  $16{\rm x}$  the time to convert one analog input sample. A simple window comparator is designed for checking

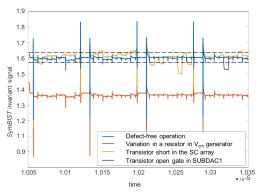

Fig. 3: Defect detection by checking an invariance signal.

| Blocks                            | #<br>defects | # defects<br>simulated | defect<br>simulation<br>time (sec) | L-W defect<br>coverage for<br>k=5 |

|-----------------------------------|--------------|------------------------|------------------------------------|-----------------------------------|

| BandGap                           | 104          | 104                    | 2035                               | 94.22%                            |

| Reference<br>Buffer               | 160          | 55                     | 10620                              | 1%                                |

| SUBDAC1                           | 1260         | 112                    | 2674                               | 80.58%±6.68%                      |

| SUBDAC2                           | 1260         | 112                    | 2474                               | 84.22%±5.89%                      |

| SC Array                          | 44           | 44                     | 1286                               | 97.7%                             |

| Vcm Generator                     | 6            | 6                      | 310                                | 30.88%                            |

| Preamplifier                      | 24           | 24                     | 700                                | 94.12%                            |

| Comparator<br>Latch               | 38           | 38                     | 752                                | 87.79%                            |

| RS Latch                          | 40           | 40                     | 983                                | 68.09%                            |

| Offset<br>Compensation<br>circuit | 20           | 20                     | 1400                               | 15.15%                            |

| Complete A/M-S part of SAR ADC IP | 2956         | 101                    | 6660                               | 86.96%±3.67%                      |

**TABLE I:** L-W defect coverage results.

an invariance composed of voltage followers and an operational amplifier. Overall, the BIST infrastructure is totally transparent to the IP incurring no performance penalties and is estimated to incur a very low and justifiable area overhead below 5%. Furthermore, the BIST can be interfaced with a standard digital test access mechanism based on two external pins which is the minimum.

IV. RESULTS

Defects are assigned a relative likelihood of occurrence as explained in [7]. For this reason, we report the Likelihood-Weighted (L-W) defect coverage computed by the Tessent® DefectSim tool [7]. To reduce defect simulation time, we use the stop-on-detection and Likelihood-Weighted Random Sampling (LWRS) options [7]. When the LWRS option is used, the 95% confidence interval of the L-W defect coverage is also reported [7]. We rely on a standard defect model based on shortand open-circuits and 50% variation in passive components.

Fig. 3 shows in blue the invariant signal that corresponds to the sum of the differential inputs DAC+ and DAC- of the comparator. This signal should be around 1.6V in defectfree operation. In this simulation, the stop-on-detection was disabled. The two dashed horizontal lines correspond to the comparison window which has limits at  $\delta = 5\sigma$  such that yield loss is negligible. The instantaneous glitches are due to the switching operation, either due to changes in the input digital test stimulus or due to the sampling and conversion operations. A clocked comparator is used to check the invariance with the checks performed when the node voltages are settled, thus no defect detection is flagged when the glitches exceed the range. The yellow, red, and purple curves in Fig. 3 show the same invariant signal in the presence of a defect in three different blocks. As it can be seen from Fig. 3, while the defect in  $V_{\rm cm}$  generator is detectable during the entire test duration, the defects within the sub-DAC1 and SC array are detectable during specific conversion periods.

Table I shows for the various individual sub-blocks of the SAR ADC IP and for its complete A/M-S part the total number of defects, the number of defects simulated, the total defect simulation time, and the L-W defect coverage values achieved using SymBIST. For the entire A/M-S part of the IP, the defect coverage is  $86.96\% \pm 3.67\%$ . As a comparison, for two considerably smaller industrial A/M-S IPs, namely a bandgap and a power-on-reset circuit, the reported defect coverage values are 74% and 51%, respectively [7].

The low defect coverage for some sub-blocks can be explained by the non-detection of defects with very high likelihood of occurrence. In fact, the absolute defect coverage is considerably higher.

The defect simulation times are proportional to the number of defects simulated, as well to the detection time stamps since the stop-on-detection option is used. For defects that are not detected the test ends up being exhaustive.

#### ACKNOWLEDGEMENT

The authors would like to acknowledge the financial support in the framework of the ANR EDITSoC project with No ANR-17-CE24-0014-02. The authors would like also to thank Stephen Sunter from Mentor, A Siemens Business, for the technical advice on the defect simulator.

#### REFERENCES

- [1] H. Hashempour et al., "Test time reduction in analogue/mixedsignal devices by defect oriented testing: An industrial example," in Proc. Design, Automation & Test in Europe Conference, 2011.

- [2] B. Dufort and G. W. Roberts, "On-chip analog signal generation for mixed-signal built-in self-test," IEEE Journal of Solid-State Circuits, vol. 34, no. 3, pp. 318-30, 1999.

- [3] M. Barragan et al., "A fully-digital BIST wrapper based on ternary test stimuli for the dynamic test of a 40nm CMOS 18-bit stereo audio  $\Sigma\Delta$  ADC," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 63, no. 11, pp. 1876–1888, 2016.

- [4] F. Azais et al., "Optimizing sinusoidal histogram test for low cost ADC BIST," Journal of Electronic Testing: Theory and Applications, vol. 17, no. 3-4, pp. 255–266, 2001.

- [5] G. Renaud et al., "Fully differential 4-V output range 14.5-ENOB stepwise ramp stimulus generator for on-chip static linearity test of ADCs," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 27, no. 2, pp. 281–293, 2019.

- [6] A. Laraba et al., "Exploiting pipeline ADC properties for a reduced-code linearity test technique," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, no. 10, pp. 2391-2400, 2015.

- [7] S. Sunter et al., "Using mixed-signal defect simulation to close the loop between design and test," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 63, no. 12, pp. 2313-2322,

- [8] H.-G. D. Stratigopoulos and Y. Makris, "An adaptive checker for the fully differential analog code," IEEE Journal of Solid-State Circuits, vol. 41, no. 6, pp. 1421-1429, 2006.