# Low on-resistance and low trapping effects in 1200 V superlattice GaN-on-silicon heterostructures

Riad Kabouche, Idriss Abid, Roland Püsche, Joff Derluyn, Stefan Degroote, Marianne Germain, Alaleh Tajalli, Matteo Meneghini, Gaudenzio Meneghesso, F Medjdoub

# ▶ To cite this version:

Riad Kabouche, Idriss Abid, Roland Püsche, Joff Derluyn, Stefan Degroote, et al.. Low on-resistance and low trapping effects in 1200 V superlattice GaN-on-silicon heterostructures. physica status solidi (a), 2020, Special Issue: Nitride Semiconductors, 217 (7), pp.1900687. 10.1002/pssa.201900687. hal-02363323

HAL Id: hal-02363323

https://hal.science/hal-02363323

Submitted on 8 Dec 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Low on-resistance and low trapping effects in 1200 V superlattice GaN-on-silicon heterostructures

Riad Kabouche<sup>1</sup>\*, Idriss Abid<sup>1</sup>, Roland Püsche<sup>2</sup>, Joff Derluyn<sup>2</sup>, Stefan Degroote<sup>2</sup>, Marianne Germain<sup>2</sup>, Alaleh Tajalli<sup>3</sup>, Matteo. Meneghini<sup>3</sup>, Gaudenzio Meneghesso<sup>3</sup>, Farid. Medjdoub<sup>1</sup>\*\*

<sup>1</sup>IEMN-CNRS, Institute of Electronics, Microelectronics and Nanotechnology, Av. Poincaré, 59650 Villeneuve d'Ascq, France

<sup>2</sup>EpiGaN, Kempische Steenweg 293, 3500 Hasselt, Belgium

<sup>3</sup>Department of Information Engineering, University of Padova, Italy

\*Corresponding author: e-mail riad.kabouche@ed.univ-lille1.fr, Phone: +33 3 20 19 18 06

\*\*e-mail farid.medjdoub@iemn.univ-lille1.fr, Phone: +33 3 20 19 78 40

Keywords: GaN, Silicon, Superlattice, low on-resistance, low trapping effects

We report on the development of GaN-on-silicon heterostructures targeting 1200 V power applications. In particular, it is shown that the insertion of superlattices (SL) into the buffer layers allows pushing the vertical breakdown voltage above 1200 V without generating additional trapping effects as compared to a more standard optimized step-graded AlGaN-based epi-structure using a similar total buffer thickness. DC characterizations of fabricated transistors by means of back-gating measurements reflect both the enhancement of the breakdown voltage and the low trapping effects up to 1200 V. These results show that a proper buffer optimization along with the insertion of SL pave the way to GaN-on-silicon lateral power transistors operating at 1200 V with low on-resistance and low trapping effects.

## 1. Introduction

At the time of global warming, Gallium nitride on silicon (GaN-on-Si) technologies are highly promising to solve energy issues in the future [1-2]. Although the growth of GaN-on-Si represents a real challenge in managing large lattice and thermal mismatch [3-6], this technology remains the best candidate owing to its superior intrinsic properties such as high breakdown voltage (BV), large band-gap, high electron saturation velocity, low on-resistance, suitable for high volume commercialization of low cost substrates [7-22]. However, GaN-on-Silicon is currently limited to a voltage range around 1 kV on large wafer diameter with low

bow and low buffer trapping. That is why significant efforts are now deployed in order to find optimum GaN-on-silicon epitaxial structures enabling outstanding DC performances beyond 1 kV while delivering low trapping effects. This would allow extending the capabilities of these emerging types of devices. In this paper, we present GaN-on-Silicon material using superlattices into a carbon-doped buffer delivering a vertical breakdown well above 1.2 kV together with low buffer trapping for the first time.

## 2. Material description and device fabrication

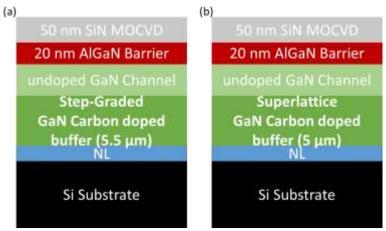

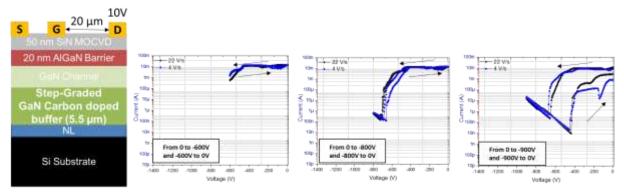

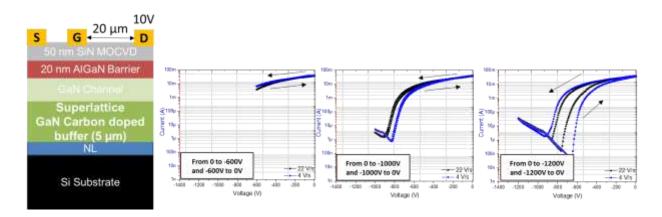

Figure 1 shows a schematic cross section of the AlGaN/GaN-on-silicon heterostructures grown by metal organic chemical vapor deposition (MOCVD) capped with a thick in-situ SiN. Following the nucleation layer, the first structure referred as REF (shown in Figure 1.a) includes a 2.6 µm buffer (AlN nucleation layer and step-graded AlGaN layer), a 2.875 µm carbon-doped GaN layer ( $2 \times 10^{19}$  cm<sup>-3</sup>) resulting in a 5.5  $\mu$ m total buffer thickness, a 0.3  $\mu$ m unintentionallydoped GaN channel, a 20 nm Al<sub>0.29</sub>Ga<sub>0.71</sub>N barrier layer and a 50 nm thick SiN MOCVD passivation. Using a Ti (12 nm)/Al (200 nm)/Ni (50 nm/Au (100 nm) stack with 875°C for 1 min rapid thermal annealing, ohmic contacts have been formed on the top of the barrier by fully etching the thick in-situ SiN cap layer using a Fluorine-based etching, yielding typical contact resistances of 0.4  $\Omega$ .mm. Then, the device isolation was achieved by using nitrogen ion triple implantation using the following energy doses: 20 keV, 50 keV, 100 keV resulting in an isolation depth of about 200 nm. A sheet resistivity of 300 Ω/sq has been measured by Hall Effect measurements revealing an electron mobility of 1800 cm<sup>2</sup>/Vs and an electron concentration of 1.15×10<sup>13</sup> cm<sup>-2</sup>. The second structure (shown in Figure 1.b) consists in the same active layers but with a 1 µm carbon-doped GaN buffer and the insertion of 3.7 µm thick AlN/GaN superlattices (called SL) on top of the AlN nucleation layer. This structure shows with a mobility of 1600 cm<sup>2</sup>/Vs and an electron concentration of 1.3×10<sup>13</sup> cm<sup>-2</sup>. Ni/Au gate metal was deposited within the in-situ SiN by partly dry etching the cap layer with a 20 nm depth using an SF<sub>6</sub> plasma. The transistor gate length and source-gate distance were 2  $\mu$ m and 1  $\mu$ m, respectively with various gate-drain distances.

#### 3. Results and discussion

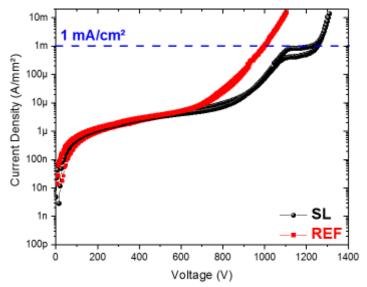

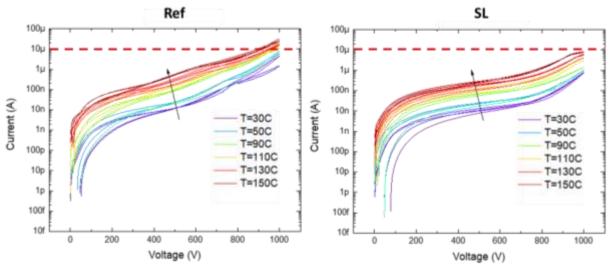

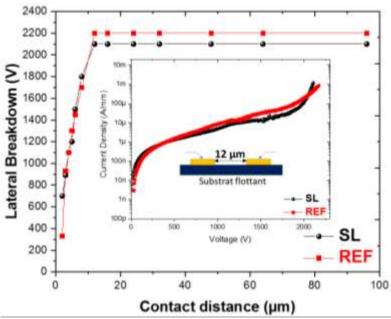

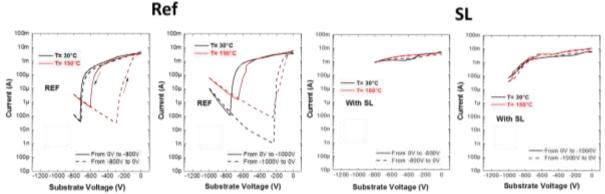

Figure 2 shows the vertical breakdown measurements of both structures, which consist in applying a high voltage on an isolated ohmic contact (100×100 µm) while the substrate is grounded. The SL structure shows a vertical breakdown close to 1.3 kV defined at 1 mA/cm<sup>2</sup> while the REF structure delivers 1 kV under the same conditions despite the slightly thicker buffer layers. The achieved state-of-the-art vertical BV > 1.2 kV reflects the high crystal and growth quality. It can be noticed that from 1.1 kV up to 1.3 kV, the vertical breakdown shows a second plateau observed systematically with a leakage current below 1 mA/cm<sup>2</sup>. Even though the related mechanism is still under investigation, it shows that the superior blocking voltage capabilities of the AlN/GaN superlattice results from a higher effective bandgap than the AlGaN back barriers and a better strain relaxation. Furthermore, the temperature dependence vertical breakdown measurements up to 1 kV (limited by the setup) have been performed as shown in **Figure 3**. A lower vertical leakage current is observed up to 150°C for the SL structure. The leakage current increase with the temperature is much lower than the REF structure, which further confirms the higher voltage insulation resistance nature of the SL structure. In addition, Figure 4 depicts the lateral BV as a function of isolated contact distances while the substrate is floating. The measurements have been performed on-wafer and the samples have been immerged in a Fluorinert solution in order to avoid arcing in air. The lateral BV is well above 2000V and comparable for both structures when using large contact distances. The inset shows specifically the lateral BV characteristics with a 12 µm distance corresponding to the saturated regime. It turns out that the benefit of the superlattice configuration can only be observed when the substrate is grounded (e.g. when the vertical field is significant). On the other hand, from a practical point of view, power devices are generally used with grounded substrate. Electrical

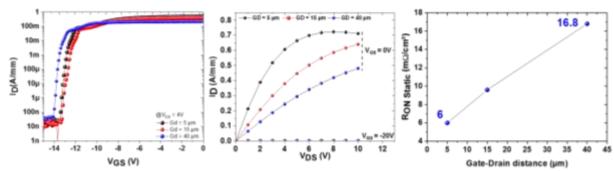

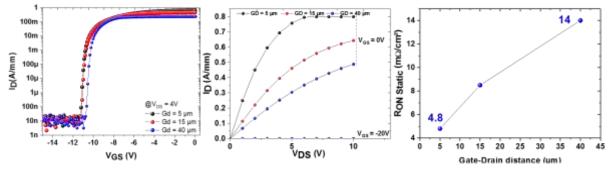

characterizations have been realized on 2×50 µm transistors. The gate length was 2 µm with various gate-drain distances (GD) as shown in Figure 5 (Ref) and Figure 6 (SL). Transfer characteristics I<sub>D</sub>-V<sub>G</sub> reveal a low leakage current and an excellent pinch-off behavior reflecting the absence of parasitic punch-through effects or gate leakage current. The higher threshold voltage for the SL structure than the REF is most likely due to the gate etching depth, which may be higher than expected. High current densities are observed in both cases. The lower current density for the REF structure is in agreement with the lower electron concentration as compared to the SL structure. This is due to the AlGaN back barrier inducing a polarization rather close to the channel that slightly depletes the channel. It can be noticed that low static on-state resistance ( $R_{ON STATIC}$ ) of about 5 m $\Omega$ /cm<sup>2</sup> with a gate-drain distance of 5  $\mu$ m has been obtained. For larger GD, R<sub>ON STATIC</sub> increases as expected but remains still below 15 mΩ/cm<sup>2</sup> for a GD = 40 µm for instance. Figure 7 (Ref) and Figure 8 (SL) show the 3-terminal off-state breakdown for several gate-drain distances with grounded and floating substrate. With grounded substrate, in agreement with the buffer breakdown measurements the 3-terminal BV at  $V_{GS} = -20V$  is about 1 kV and 1.3 kV for the REF and the SL buffer, respectively. Also, with floating substrate both structures shows a 3-terminal BV above 2 kV for large gate-drain distances.

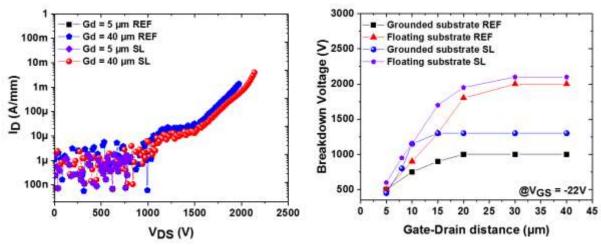

When investigating higher voltage GaN power switch devices, it is critical to assess the related trapping effects. Buffer traps have been studied by means of substrate bias ramp measurements using various sweep rates at room temperature (RT) as described in [23][24]. Indeed, by monitoring the current between two ohmic contacts while ramping down the substrate bias, any charge storage is visible highlighting the presence of trapping effects within the buffer layers. The REF structure optimized for 650 V applications shows low trapping effects up to 800V with fast sweep rates (22 V/s). However, a strong trapping activation can be observed at 800 V when using slow sweep rates (4 V/s). The hysteresis increases significantly at 900 V as expected. On the other hand, the optimized SL structure uniformly delivers state-of-the-art low trapping

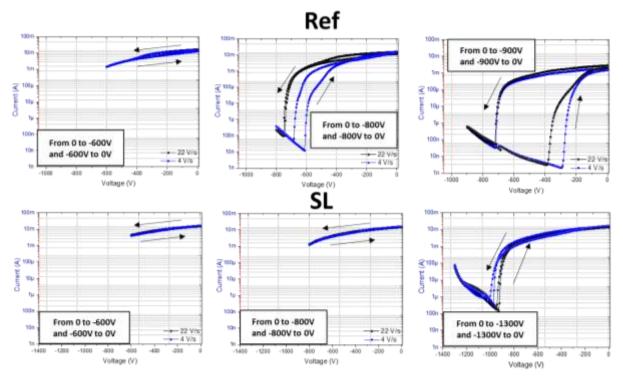

effects all the way to 1300 V regardless of the sweep rates as shown in **Figure 9**. Substrate bias ramp measurements have been also performed at high temperature in order to confirm these data. At 150°C, the REF structure shows trapping activation at 800V, which is in agreement with the measurements at RT using various sweep rates. The SL structure remains unaffected by trapping effects at high temperature (Figure 10). It has been shown that carbon-doping is directly linked to the trapping effects [24][25]. Thus the reduced trapping can be attributed to the lower incorporation of carbon in the case of SL buffer due to the slower growth process as compared to the REF structure. Trapping has been also studied through back-gating measurements on transistors with high vertical drain-to-substrate potential. In this case, tuning the transistor / substrate bias conditions allows in turn to distinguish the surface and bulk traps. Figure 11 reveals the back-gating transistor measurements performed on the REF structure at a drain bias of 10V. We observe a perfect correlation with the substrate ramp measurements illustrated by low trapping effects up to 800V using a slow sweep rate and a strong activation at 800V and above using a fast sweep rate. For the SL structure (Figure 12), back-gating measurements have been applied and confirms the low buffer trapping up to 1200 V despite residual surface traps due to the processing that still needs to be optimized for operation beyond 1 kV.

### 4. Conclusion

This work showed an outstanding vertical breakdown above 1.3 kV using a 5  $\mu$ m thick SL based carbon-doped buffer compared to 1 kV with a more standard AlGaN step-graded thicker buffer. Furthermore, significantly reduced buffer traps up to 1.3 kV have been observed by substrate ramp measurements up to 150°C. Back-gating measurements performed on transistors confirmed the state-of-the-art low trapping up to 1 kV limited by process-induced surface trapping at higher voltage. Finally, a 3-terminal BV above 2 kV associated to a  $R_{on}$ < 15 m $\Omega$ .cm<sup>2</sup>

for GD =  $30 \,\mu m$  have been reached. These results pave the way to GaN-on-silicon lateral power transistors operating at  $1200 \, V$  with low on-resistance and low trapping effects.

# Acknowledgements

This work is supported by the French RENATECH network. It has received partial funding from the European Union's Horizon 2020 research and innovation program under grant agreement No 720527 project Innovative Reliable Nitride based Power Devices and (Inrel-NPower) and the French National grant ANR-16-CE05-0022-01 (DESTINEE).

#### References

- [1] Y. S. Lin, Y. W. Lian, J.M. Yang, H.C. Lu, Y.C. Huang, C.H. Cheng and S. S H. Hsu, Semicond. Sci. Technol., vol. 28, no. 7, 2013.

- [2] J. W. Chung, K. Ryu, B. Lu, and T. Palacios, Proceedings of the European Solid-State Device Research Conference 2010 (ESSDERC). 52–56. © Copyright 2010 IEEE

- [3] A. R. Boyd, S. Degroote, M. Leys, F. Schulte, O. Rockenfeller, M. Luenenbuerger, M.Germain, J. Kaeppeler, and M. Heuken, Phys. Stat. Sol. C, vol. 6, no. S2, pp. S1045–S1048, Jun. 2009.

- [4] E. Dogmus, M. Zegaoui, and F. Medjdoub, "GaN-on-silicon high-electron-mobility transistor technology with ultra-low leakage up to 3000V using local substrate removal and AlN ultra-wide bandgap," *Appl. Phys. Express*, pp. 3–7, 2018.

- [5] G. Pavlidis, S. H. Kim, I. Abid, M. Zegaoui, F. Medjdoub, and S. Graham, "The Effects of AlN and Copper Back Side Deposition on the Performance of Etched Back GaN/Si HEMTs," *IEEE Electron Device Lett.*, vol. 40, no. 7, pp. 1060–1063, 2019.

- [6] Domenica Visalli, Marleen Van Hove, Puneet Srivastava, Denis Marcon, Karen Geens, Xuanwu Kang, Erwin Vandenplas, John Viaene, Maarten Leys, Kai Cheng, Bram Sijmus, Stefaan Decoutere and Gustaaf Borghs, ECS Transactions, 41 (8) 101-112, 2011

- [7] W. K. Wang and M. C. Jiang, "Growth behavior of hexagonal GaN on Si(100) and Si(111) substrates prepared by pulsed laser deposition," Jpn. J. Appl. Phys., vol. 55, no. 9, pp. 1–4, 2016.

- [8] D. Zhao et al. J. Semicond., vol. 36, no. 6, 2015.

- [9] B. J. Baliga, Semicond. Sci. Technol. 28, p. 074011 (2013).

- [10] H. Ishikawa, G.-Y. Zhao, N. Nakada, T. Egawa, T. Jimbo, and M. Umeno, Jpn. J. Appl. Phys., vol. 38, no. 5A, p. L492, May 1999.

- [11] D. Christy, T. Egawa, Y. Yano, H. Tokunaga, H. Shimamura, Y. Yamaoka, A. Ubukata, T. Tabuchi, and K. Matsumoto, K. Appl. Phys. Express 6, p. 026501 (2013).

- [12] M. Zhu et al, IEEE Electron Device Lett., vol. 36, no. 4, pp. 375–377, 2015.

- [13] K. J. Chen et al., IEEE Trans. Electron Devices, vol. 64, no. 3, pp. 779–795, 2017.

- [14] H. C. Chiu, H. L. Kao, K. S. Chin, and F. H. Huang, 2015 IEEE MTT-S Int. Microw. Work. Ser. RF Wirel. Technol. Biomed. Healthc. Appl. IMWS-BIO 2015 Proc., pp. 145–146, 2015.

- [15] Q. Jiang, C. Liu, Y. Lu, and K. J. Chen, IEEE Electron Device Lett., vol. 34, no. 3, pp. 357–359, 2013.

- [16] U. K. Mishra, L. Shen, T. E. Kazior, and Yi-Feng Wu, Proceedings of the IEEE, vol. 96, no.2, pp. 287–305, Feb. 2008.

- [17] M. H. Kwan, et al. in Proc. IEEE Electron Devices Meeting (IEDM), San Francisco, CA, 2014, pp. 17.6.1 17.6.4.

- [18] Y. F. Wu, J. Gritters, L. Shen, R. P. Smith, and B. Swenson, IEEE Trans. Power Electronics, vol.29, no. 6, pp. 2634 2637, June 2014.

- [19] T. Ueda, M. Ishida, T. Tanaka, and D. Ueda, Jpn. J. Appl. Phys., vol. 53, no. 10, p. 100214, 2014

- [20] X. Huang, Z. Liu, Q. Li, and F. C. Lee, IEEE Trans. Power Electronics, vol.29, no. 5, pp. 2453- 2461, May 2014.

- [21] K. S. Boutros, S. Burnham, D. Wong, K. Shinohara, B. Hughes, D. Zehnder, and C. McGuire, in Proc. IEDM, 2009, pp. 1–3.

- [22] Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, and D. Ueda, in Proc. IEDM, Dec. 2006, pp. 907–910.

- [23] P. Moens A. Banerjee, M. J. Uren, M. Meneghini, S.Karboyan, I. Chatterjee, P. Vanmeerbeek, M. Cäsar, C. Liu, A. Salih, E. Zanoni, G. Meneghesso, M. Kuball, M. Tack, in Technical Digest International Electron Devices Meeting, IEDM, 2015, vol. 35.2.1

- [24] M. J. Uren, Serge Karboyan, Indranil Chatterjee, Alexander Pooth, Peter Moens, Abhishek Banerjee, and Martin Kuball, IEEE Trans. Electron Devices, vol. 64, no. 7, pp. 2826–2834, 2017.

[25] M. Meneghini, A. Tajalli, P. Moens, A. Banerjee, E. Zanoni and Gaudenzio Meneghesso, Mater. Sci. Semicond. Process., vol. 78, no. October 2017, pp. 118–126, 2018.

**Figure 1.** Schematic cross section of the structures with a step-graded buffer (REF) (a) and a superlattice buffer (SL) (b).

**Figure 2.** Vertical breakdown for the REF structure (red) and the SL structure (black) at room temperature.

**Figure 3.** Vertical breakdown for the REF structure (left) and the SL structure (right) for various temperatures.

**Figure 4.** Lateral breakdown voltage as a function of the contact distances for the REF structure (red) and the SL structure (black) at room temperature.

Figure 5. Transfer, open channel output characteristics at  $V_{GS}=0V$  and  $R_{ON}$  for the REF structure.

Figure 6. Transfer, open channel output characteristics at  $V_{GS} = 0V$  and  $R_{ON}$  for the SL structure.

Figure 7. 3-terminal breakdown voltage for the REF and SL structures at  $V_{GS} = -22 \text{ V}$

**Figure 8.** Substrate bias ramp measurements for the REF structure (top) and the SL structure (bottom) at room temperature.

**Figure 9.** Substrate bias ramp measurements for the REF structure (left) and the SL structure (right) up to 150°C.

Figure 10. Back-gating measurements up to 900 V for the REF structure with  $V_{DS}=10 V$

Figure 11. Back-gating measurements up to 1200 V for the SL structure with  $V_{DS} = 10V$