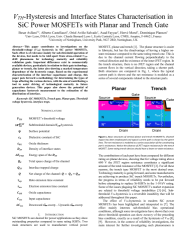

V TH -Hysteresis and Interface States Characterisation in SiC Power MOSFETs with Planar and Trench Gate

Résumé

This paper contributes to investigations on the threshold-voltage (VTH) hysteresis in SiC power MOSFETs. Such effect is of relevance mainly for sub-threshold operation of the devices, but needs to be told apart from stress-related VTH-drift phenomena for technology maturity and reliability validation goals. Important differences exist in commercially available devices, particularly in relation to their gate technology, planar or trench, the latter also showing a marked temperature dependence of the hysteretic range. Based on the experimental characterization of the interface capacitance and charge, this paper puts forward a methodology for determining the types of traps affecting the various devices, with the aim of contributing a tool to assist driving of technological maturity in future generation devices. This paper also shows the potential of capacitance hysteresis measurement to the estimation of the distribution of interface.

Domaines

Energie électrique

Fichier principal

Vth-Hysteresis and Interface States Characterisation in SiC Power MOSFETs with Planar and Trench Gate.pdf (494.04 Ko)

Télécharger le fichier

Vth-Hysteresis and Interface States Characterisation in SiC Power MOSFETs with Planar and Trench Gate.pdf (494.04 Ko)

Télécharger le fichier

Origine : Fichiers produits par l'(les) auteur(s)

Loading...