## Model Checking Real-Time Systems

Patricia Bouyer, Uli Fahrenberg, Kim G. Larsen, Nicolas Markey, Joël Ouaknine, James Worrell

## ▶ To cite this version:

Patricia Bouyer, Uli Fahrenberg, Kim G. Larsen, Nicolas Markey, Joël Ouaknine, et al.. Model Checking Real-Time Systems. Handbook of model checking, Springer-Verlag, pp.1001-1046, 2018, 978-3-319-10574-1. 10.1007/978-3-319-10575-8\_29. hal-01889280

## HAL Id: hal-01889280 https://hal.science/hal-01889280

Submitted on 8 Oct 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Model Checking Real-Time Systems

Patricia Bouyer, Uli Fahrenberg, Kim G. Larsen, Nicolas Markey, Joël Ouaknine, and James Worrell

Abstract This chapter surveys timed automata as a formalism for model checking real-time systems. We begin with introducing the model, as an extension of finite-state automata with real-valued variables for measuring time. We then present the main model-checking results in this framework, and give a hint about some recent extensions (namely weighted timed automata and timed games).

## 1 Introduction

Timed automata were introduced by Rajeev Alur and David Dill in the early 1990s [13] as finite-state automata equipped with real-valued variables for measuring time between transitions in the automaton. These variables all evolve at the same rate; they can be reset along some transitions, and used as *guards* along other transitions or invariants to be preserved while letting time elapse in locations of the automaton.

Patricia Bouyer LSV - CNRS & ENS Cachan, U. Paris-Saclay, France, e-mail: patricia.bouyer@lsv.fr. Uli Fahrenberg IRISA - INRIA & U. Rennes I, France, e-mail: uli.fahrenberg@irisa.fr. Kim G. Larsen Computer Science Department - U. Aalborg, Denmark, e-mail: kgl@cs.aau.dk. Nicolas Markey LSV - CNRS & ENS Cachan, U. Paris-Saclay, France, e-mail: nicolas.markey@lsv.fr. Joël Ouaknine Computer Science Department - U. Oxford, UK, e-mail: joel.ouaknine@cs.ox.ac.uk. James Worrell Computer Science Department - U. Oxford, UK, e-mail: james.worrell@cs.ox.ac.uk. Timed automata have proven very convenient for modeling and reasoning about real-time systems: they combine a powerful formalism with advanced expressiveness and efficient algorithmic and tool support, and have become a model of choice in the framework of verification of embedded systems. The timed-

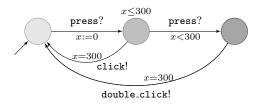

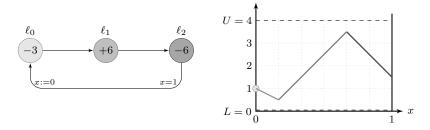

Fig. 1 A timed automaton

automata formalism is now routinely applied to the analysis of real-time control programs [85,127] and timing analysis of software and asynchronous circuits [60, 146, 150]. Similarly, numerous real-time communication protocols have been analysed using timed automata technology, often with inconsistencies being revealed [95, 144]. During the last few years, timedautomata-based schedulability and response-time analysis of multitasking applications running under real-time operating systems have received substantial research effort [61, 78, 80, 109, 156]. Also, for optimal planning and scheduling, (priced) timed automata technology has been shown to provide competitive and complementary performances with respect to classical approaches [1, 2, 32, 86, 97, 108, 119]. Finally, controller synthesis from timed games has been applied to a number of industrial case studies [6, 71, 110].

The handiness of this formalism is exemplified in Fig. 1, modeling a (simplified) computer mouse: this automaton receives **press** events, corresponding to an action of the user on the button of the mouse. When two such events are close enough (less than 300 milliseconds apart), this is translated into a double\_click event.

Because clock variables are real-valued, timed automata are in fact infinitestate models, where a configuration is given by a location of the automaton and a valuation of the clocks. Timed automata have two kinds of transitions: action transitions correspond to firing a transition of the automaton, and delay transitions correspond to letting time elapse in the current location of the automaton. Section 2 provides the definitions of this framework. The main technical ingredient for dealing with this infinity of states is the region abstraction, as we explain in Sect. 3. Roughly, two clock valuations are called region equivalent whenever they satisfy the exact same set of constraints of the form  $x - y \bowtie c$ , where the difference of two clocks x and y is compared to some integer c (no greater than some constant M). This abstraction can be used to develop various algorithms, in particular for deciding bisimilarity (Sect. 4) or model checking some quantitative extensions of the classical temporal logics CTL and LTL (Sect. 6). We also show that some problems are undecidable. most notably language containment (Sect. 5) and model checking the full quantitative extension of LTL. On the practical side, regions are in some sense too fine-grained, and another abstraction, called *zones*, is preferred for implementation purposes. Roughly, zones provide a way of grouping many

regions together, which is often relevant in practical situations. We explain in Sect. 7 how properties of timed automata can be verified in practice.

Finally, we conclude this chapter with two powerful extensions of timed automata: first, *weighted timed automata* allow for modeling quantitative constraints beyond time; since resource (e.g., energy) consumption is usually tightly bound to time elapsing, timed automata provide a convenient framework for modeling such quantitative aspects of systems. Unlike hybrid systems (see Chap. 28hybrid), weighted timed automata still enjoy some nice decidability properties (in restricted settings though), as we explain in Sect. 8. Then in Sect. 9 we present *timed games*, which are very powerful and convenient for dealing with the controller synthesis problem (see Chap. 25gamesynth) in a timed framework. Timed games also provide an interesting way of modeling uncertainty in real-time systems, assuming worst-case resolution of the uncertainty while still trying to benefit from non-worst-case situations.

## 2 Timed Automata

In this chapter, we consider as time domain the set  $\mathbb{R}_{\geq 0}$  of non-negative reals. While discrete time might look reasonable for representing digital systems, it assumes synchronous interactions between the systems. We refer to [17, 27, 67, 102] for more discussions on this point.

Let  $\Sigma$  be a finite set of *actions*. A *time sequence* is a finite or infinite non-decreasing sequence of non-negative reals. A *timed word* is a finite or infinite sequence of pairs  $(a_1, t_1) \dots (a_p, t_p) \dots$  such that  $a_i \in \Sigma$  for every *i*, and  $(t_i)_{i\geq 1}$  is a time sequence. An infinite timed word is *converging* if its time sequence is bounded above (or, equivalently, converges).

We consider a finite set C of variables, called *clocks*. A *(clock) valuation* over C is a mapping  $v: C \to \mathbb{R}_{\geq 0}$  which assigns to each clock a real value. The set of all clock valuations over C is denoted  $\mathbb{R}_{\geq 0}^C$ , and  $\mathbf{0}_C$  denotes the valuation assigning 0 to every clock  $x \in C$ .

Let  $v \in \mathbb{R}_{\geq 0}^{C}$  be a valuation and  $t \in \mathbb{R}_{\geq 0}$ ; the valuation v + t is defined by (v+t)(x) = v(x) + t for every  $x \in C$ . For a subset r of C, we denote by v[r] the valuation obtained from v by resetting clocks in r; formally, for every  $x \in r$ , v[r](x) = 0 and for every  $x \in C \setminus r$ , v[r](x) = v(x).

The set  $\Phi(C)$  of *clock constraints* over C is defined by the grammar

$$\Phi(C) \ni \varphi ::= x \bowtie k \mid \varphi_1 \land \varphi_2 \ (x \in C, \ k \in \mathbb{Z} \text{ and } \bowtie \in \{<, \leq, =, \geq, >\}).$$

We will sometimes make use of diagonal clock constraints, which additionally allow constraints of the form  $x - y \bowtie k$ . We write  $\Phi_d(C)$  for the extension of  $\Phi(C)$  with diagonal constraints. If  $v \in \mathbb{R}_{\geq 0}^C$  is a clock valuation, we write  $v \models \varphi$  when v satisfies the clock constraint  $\varphi$ , and we say that v satisfies  $x \bowtie k$ whenever  $v(x) \bowtie k$  (similarly, v satisfies  $x - y \bowtie k$  when  $v(x) - v(y) \bowtie k$ ). If  $\varphi$  is a clock constraint, we write  $[\![\varphi]\!]_C$  for the set of clock valuations  $\{v \in \mathbb{R}_{\geq 0}^C \mid v \models \varphi\}.$

**Definition 1 ([13]).** A timed automaton is a tuple  $(L, \ell_0, C, \Sigma, I, E)$  consisting of a finite set L of locations with initial location  $\ell_0 \in L$ , a finite set C of clocks, an invariant<sup>1</sup> mapping  $I: L \to \Phi(C)$ , a finite alphabet  $\Sigma$  and a set  $E \subseteq L \times \Phi(C) \times \Sigma \times 2^C \times L$  of edges. We shall write  $\ell \xrightarrow{\varphi, a, r} \ell'$  for an edge  $(\ell, \varphi, a, r, \ell') \in E$ ; formula  $\varphi$  is the guard of the transition (and has to be satisfied when the transition is taken), and r is the set of clocks that are set to zero after taking that transition.

Later for defining languages accepted by timed automata we may add final or repeated (Büchi) locations, and for defining logical satisfaction relations we may add atomic proposition labeling to timed automata. However for readability reasons we omit them here.

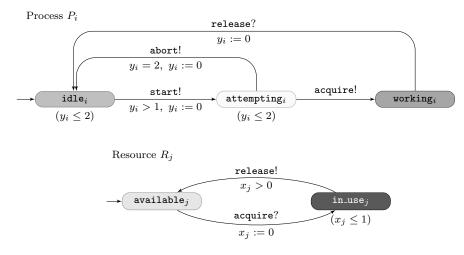

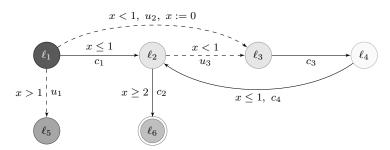

**Fig. 2** Model of a process that acquires and releases two resources. Here and in the rest of this chapter, transitions are decorated with their associated guards (e.g.,  $x_j > 0$ ), letters of the alphabet (e.g., **release**!), and resets (written e.g., as  $x_j := 0$ ); invariants (if any) are written in brackets below their corresponding locations

Example 1. Figure 2 shows timed automata models for processes and resources. Processes can use resources, but mutual exclusion is expected. The model for process  $P_i$  is given in the upper part of the figure, whereas the model for resource  $R_j$  is given in the lower part of the figure. Starting in the idle location, the process should start within one to two time units requesting a

<sup>&</sup>lt;sup>1</sup> The original definition of timed automata [13] did not contain invariants in locations, but had Büchi conditions to enforce liveness. Invariants were added by [103]. Several other convenient extensions have been introduced since then, which we discuss in Sect. 3.2.

resource. After two time units it must abort its request, unless before two time units it acquires the resource and goes to the **working** location. The resource is released when the process is done working with it.

Our model for a resource has two locations, and when the resource is available, it can be acquired and should be released within one time unit.

The operational semantics of a timed automaton  $A = (L, \ell_0, C, \Sigma, I, E)$  is the (infinite-state) timed transition system  $\llbracket A \rrbracket = (S, s_0, \mathbb{R}_{\geq 0} \times \Sigma, T)$  given as follows:

$$S = \left\{ (\ell, v) \in L \times \mathbb{R}_{\geq 0}^C \mid v \models I(\ell) \right\} \qquad \qquad s_0 = (\ell_0, \mathbf{0}_C)$$

$$T = \left\{ (\ell, v) \xrightarrow{d, a} (\ell', v') \mid \forall d' \in [0, d] : v + d' \models I(\ell), \\ \text{and } \exists \ell \xrightarrow{\varphi, a, r} \ell' \in E : v + d \models \varphi, \text{ and } v' = (v + d)[r] \right\}$$

In words, one can jump from one state  $(\ell, v)$  to another one  $(\ell', v')$  by selecting a delay to be elapsed in  $\ell$  (provided that the invariant of location  $\ell$  is fulfilled in the meantime) and an edge of the automaton, which is taken after the delay, provided that its guard is satisfied at that time. In this semantics, a transition combines both a delay and (followed by) the application of an edge of the automaton. A slightly different semantics is sometimes used, which distinguishes pure-delay transitions (denoted  $\xrightarrow{d}$ , for  $d \in \mathbb{R}_{\geq 0}$ ) and pure-action transitions (denoted  $\xrightarrow{a}$  with  $a \in \Sigma$ ).

A (finite or infinite) run of a timed automaton A is a (finite or infinite) path  $\rho = (\ell_0, v_0) \xrightarrow{d_1, a_1} (\ell_1, v_1) \xrightarrow{d_2, a_2} \cdots$  in the transition system  $\llbracket A \rrbracket$ , which starts with  $v_0 = \mathbf{0}_C$ . Given a run  $\rho = (\ell_0, v_0) \xrightarrow{d_1, a_1} (\ell_1, v_1) \xrightarrow{d_2, a_2} (\ell_2, v_2) \ldots$ , we say that it reads the timed word  $w = (a_1, t_1)(a_2, t_2) \ldots$  where for every i,  $t_i = \sum_{j \leq i} d_j$ . A run is *time-divergent* if its time sequence  $(t_i)_i$  diverges. A timed automaton is *non-Zeno* if any finite run can be extended into a time-divergent run.

*Example 2.* The process  $R_1$  given in Fig. 2 has a single clock  $x_1$ , and has as set of states  $S = \{ \texttt{available}_1 \} \times \mathbb{R}_{\geq 0} \cup \{ \texttt{in\_use}_1 \} \times [0, 1]$  where we identify valuations (for the single clock  $x_1$ ) with the value of  $x_1$ . We give below a possible run for the resource  $R_1$ :

$$\begin{array}{c} (\texttt{available}_1, 0) \xrightarrow{5.4, \texttt{acquire}?} (\texttt{in\_use}_1, 0) \xrightarrow{0.8, \texttt{release}!} (\texttt{available}_1, 0.8) \\ & \xrightarrow{1.4, \texttt{acquire}?} (\texttt{in\_use}_1, 0) \rightarrow \dots \end{array}$$

In location in\_use, the invariant is satisfied in this run because the value of  $x_1$  never exceeds 0.8 (hence satisfies the constraint  $x_1 \leq 1$ ).

We now define the parallel composition of timed automata, which allows us to define systems in a compositional way [23, 107]. Let  $(A_i)_{1 \le i \le n}$  be n

timed automata, where  $A_i = (L_i, \ell_0^i, C_i, \Sigma_i, I_i, E_i)$ . Assume that all  $\Sigma_i$ 's are disjoint, and all  $C_i$ 's are disjoint. If  $\Sigma$  is a new alphabet, given a (partial) synchronization function  $f: \prod_{i=1}^{n} (\Sigma_i \cup \{-\}) \to \Sigma$ , the synchronized product (or parallel composition)  $(A_1 \parallel A_2 \parallel \cdots \parallel A_n)_f$  is the timed automaton A =(c) parameter in product (c)  $I = L_1 \times \cdots \times L_n$ ,  $\ell_0 = (\ell_0^1, \dots, \ell_0^n)$ ,  $C = C_1 \cup \cdots \cup C_n$ ,  $I((\ell_1, \dots, \ell_n)) = \bigwedge_{i=1}^n I_i(\ell_i)$  for every  $(\ell_1, \dots, \ell_n) \in L_1 \times \cdots \times L_n$ , and the set E is composed of the transitions  $(\ell_1, \dots, \ell_n) \xrightarrow{\varphi, a, r} (\ell'_1, \dots, \ell'_n)$  whenever

1. there exists  $(\alpha_1, \ldots, \alpha_n) \in \prod_{i=1}^n (\Sigma_i \cup \{-\})$  such that  $f(\alpha_1, \ldots, \alpha_n) = a$ ; 2. if  $\alpha_i = -$ , then  $\ell'_i = \ell_i$ ;

- 3. if  $\alpha_i \neq -$ , then there is a transition  $\ell_i \xrightarrow{\varphi_i, \alpha_i, r_i} \ell'_i$  in  $E_i$ 4.  $\varphi = \bigwedge \{\varphi_i \mid \alpha_i \neq -\}$  and  $r = \bigcup \{r_i \mid \alpha_i \neq -\}$

Example 3. We build on the system given in Fig. 2. The process and the resources are not expected to run independently, but they are part of a global system where the process should synchronize with the resources. Hence for this system we have a natural synchronization function f defined by Table 1.

| $P_1$    | $P_2$    | $R_1$    |               |                      |

|----------|----------|----------|---------------|----------------------|

| start!   | -        | _        | $\rightarrow$ | $\mathtt{start}_1$   |

| _        | start!   | _        | $\rightarrow$ | $\mathtt{start}_2$   |

| abort!   | -        | _        | $\rightarrow$ | $\texttt{abort}_1$   |

| -        | abort!   | _        | $\rightarrow$ | $\mathtt{abort}_2$   |

| acquire! | -        | acquire? | $\rightarrow$ | $\texttt{acquire}_1$ |

| _        | acquire! | acquire? | $\rightarrow$ | $\verb+acquire+_2$   |

| release? | -        | release! | $\rightarrow$ | ${\tt release}_1$    |

| -        | release? | release! | $\rightarrow$ | ${\tt release}_2$    |

**Table 1** The synchronization function f

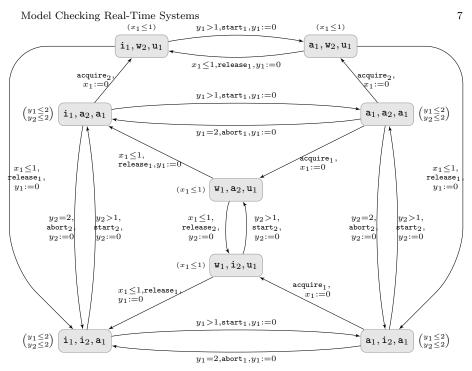

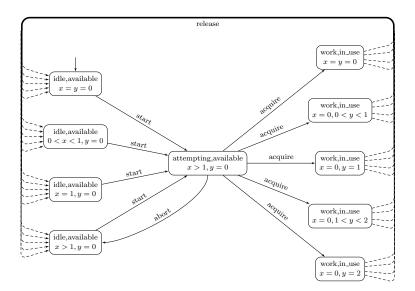

The global system  $(P_1 \parallel P_2 \parallel R_1)_f$  (more precisely the part which is reachable from the initial state) is depicted in Fig. 3. This automaton is rather complex, and the component-based definition as  $(P_1 \parallel P_2 \parallel R_1)_f$  is much easier to understand. Furthermore this allows addition of other processes and other resources to the system without any effort.

### **3** Checking Reachability

In this section we are interested in the most basic problem regarding timed automata, namely reachability. This problem asks, given a timed automaton A, whether a distinguished set of locations F of A is reachable or not.

**Fig. 3** The global system  $(P_1 \parallel P_2 \parallel R_1)_f$ , where " $\mathbf{i}_j$ " (resp. " $\mathbf{a}_j$ ", " $\mathbf{w}_j$ ") stands for location " $\mathbf{idle}_j$ " (resp. " $\mathbf{attempting}_j$ ", " $\mathbf{working}_j$ ") in  $P_j$ , and " $\mathbf{a}_1$ " (resp. " $\mathbf{u}_1$ ") stands for location " $\mathbf{atialbe}_1$ " (resp. " $\mathbf{in\_use}_1$ ") in  $R_1$

## 3.1 Region Equivalence

For the rest of this section we fix a timed automaton  $A = (L, \ell_0, C, \Sigma, I, E)$ and a set of target locations F. For every clock  $x \in C$  we let  $M_x$  be the maximal constant clock x is compared to in A.

Two valuations  $v, v' \colon C \to \mathbb{R}_{\geq 0}$  are said to be region equivalent w.r.t. maximal constants  $M = (M_x)_{x \in C}$ , denoted  $v \cong_M v'$ , if <sup>2</sup>

- for all  $x \in C$ , |v(x)| = |v'(x)| or  $v(x), v'(x) > M_x$ , and

- for all  $x \in C$  with  $v(x) \leq M_x$ ,  $\langle v(x) \rangle = 0$  iff  $\langle v'(x) \rangle = 0$ , and

- for all  $x, y \in C$  with  $v(x) \leq M_x$  and  $v(y) \leq M_y$ ,  $\langle v(x) \rangle \leq \langle v(y) \rangle$  iff  $\langle v'(x) \rangle \leq \langle v'(y) \rangle$ .

The equivalence classes of valuations with respect to  $\cong_M$  are called *regions* (with maximal constants M). The number of regions is finite and is bounded above by  $n! \cdot 2^n \cdot \prod_{x \in C} (2M_x + 2)$ . Region equivalence of valuations is extended to states of A by declaring that  $(\ell, v) \cong_M (\ell', v')$  whenever  $\ell = \ell'$  and  $v \cong_M v'$ . We write  $[\ell, v]_{\cong_M}$  for the equivalence class of  $(\ell, v)$ .

<sup>&</sup>lt;sup>2</sup> For  $d \in \mathbb{R}_{\geq 0}$  we write  $\lfloor d \rfloor$  and  $\langle d \rangle$  for the integral and fractional parts of d, i.e.,  $d = \lfloor d \rfloor + \langle d \rangle$ .

Region equivalence enjoys nice properties, the most important of which is that it is a *time-abstracted bisimulation* in the following sense:

**Definition 2.** A relation R on the states of A is a *time-abstracted bisimulation* if  $(\ell_1, v_1)R(\ell_2, v_2)$  and  $(\ell_1, v_1) \xrightarrow{d_{1,a}} (\ell'_1, v'_1)$  for some  $d_1 \in \mathbb{R}_{\geq 0}$  and  $a \in \Sigma$ imply  $(\ell_2, v_2) \xrightarrow{d_{2,a}} (\ell'_2, v'_2)$  for some  $d_2 \in \mathbb{R}_{\geq 0}$ , with  $(\ell'_1, v'_1)R(\ell'_2, v'_2)$  and vice versa.

In other words, from two equivalent states, the automaton can take the same transitions, except that the values of the delays might have to be changed. This fundamental property has important consequences, like the construction of an interesting finite abstraction for A.

**Definition 3.** The region automaton  $\mathcal{R}_{\cong_M}(A) = (S, s_0, \Sigma, T)$  associated with A has as set of states the quotient  $S = (L \times \mathbb{R}_{\geq 0}^C)_{\cong_M}$ , as initial state  $s_0 = [\ell_0, \mathbf{0}_C]_{\cong_M}$ , and as transitions all the  $[\ell, v]_{\cong_M} \xrightarrow{a} [\ell', v']_{\cong_M}$  for which  $(\ell, v) \xrightarrow{d,a} (\ell', v')$  for some  $d \in \mathbb{R}_{\geq 0}$ . The target set of  $\mathcal{R}_{\cong_M}(A)$  is defined as  $S_F = \{[\ell, v]_{\cong_M} \mid \ell \in F\}$ .

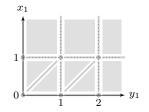

**Fig. 4** Clock regions for the system  $(P_1 \parallel R_1)_{f_1}$

The region automaton  $\mathcal{R}_{\cong_M}(A)$  is a finite automaton whose size is exponential compared with the size of A. It can be used to check, e.g., reachability properties (or equivalently language emptiness):

**Proposition 1.** The set of locations F is reachable in A from  $\ell_0$  iff  $S_F$  is reachable in  $\mathcal{R}_{\cong_M}(A)$  from  $s_0$ .

The region automaton has exponentially larger size, but checking a reachability property can be done on the fly, hence this can be done in polynomial space. One of the most fundamental theorems in the model checking of timed automata can be stated as follows.

**Theorem 1 ([13]).** The reachability problem in timed automata is PSPACEcomplete. Model Checking Real-Time Systems

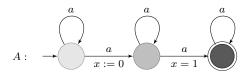

Example 4. Restricting our running example to process  $P_1$  and resource  $R_1$  (we assume  $f_1$  is the synchronization function f restricted to those two processes), the global system has two clocks,  $x_1$  and  $y_1$ . The set of regions is then depicted in Fig. 4. There are 28 regions. The (reachable part of the) corresponding region automaton is depicted in Fig. 5. In this drawing we omit indices over names of locations since they should all be 1; also, the thick "release" transition at the top corresponds to a set of transitions from all the states on the right to all the states on the left.

**Fig. 5** Region automaton for  $(P_1 \parallel R_1)_{f_1}$

## 3.2 Some Extensions of Timed Automata

Timed automata are the most basic model for representing systems with (quantitative) real-time constraints. It is natural to extend the model with features that help in modeling real systems. However decidability of the reachability problem remains the fundamental property one wants to preserve. In this subsection we mention several variants and extensions of timed automata that have been proposed in the literature.

Timed automata as defined in this chapter are the so-called *diagonal-free* timed automata since only constraints of the form  $x \bowtie k$  are used. Timed automata with diagonal constraints (of the form  $x - y \bowtie k$ ) were also originally defined in the seminal paper [13]. They can be analyzed using a slight refinement of the region automaton, but with no extra complexity. Furthermore, diagonal constraints can be removed from the model, at the expense of a (possibly exponential) blowup in the number of locations of the model [40].

Another useful extension of timed automata is obtained by allowing edges to set clocks to arbitrary positive integers (x := k) instead of only 0, or even to synchronize clock values (x := y). In [53] it is shown that any such *updatable* timed automaton can be converted to a usual one, hence this class is no more expressive than timed automata. If one also considers other updates however, like x := x + 1 or x :> k (which non-deterministically sets x to some value larger than k), the situation is much more complex [53] and decidability of reachability is no longer preserved.

One can also extend the timed-automata formalism by allowing richer clock constraints, such as, e.g.,  $x + y \leq 5$  or 2x - 3y > 1. Most such attempted extensions however lead to undecidability of the reachability problem, see for instance [41].

One can extend timed automata with *urgency* requirements [46]. For instance, some locations might be labelled as urgent, which indicates that no time can be spent in this location, it has to be left immediately when entered: an urgent location  $\ell$  can easily be converted into a usual one by introducing an extra clock x which is reset in any edge to  $\ell$  and has invariant x = 0 in  $\ell$ , hence location-urgency does not add expressiveness to the class of timed automata. Some synchronization could be also labelled as urgent: in that case, the corresponding action should be done as soon as it is enabled. In our modeling of Example 1 the synchronization "acquire!/acquire?" could be made urgent since it is natural that a process acquires the resource as soon as it is available.

Another extension of timed automata we should mention is the *stopwatch* automata of [100]. Here timed automata are extended by allowing clocks to be stopped during a delay. Even though reachability is also undecidable for this extension and it has been shown to have the same expressive power as hybrid automata [72], stopwatch automata have found some applications, e.g., in scheduling [3,141] and permit efficient over-approximate analysis [72]. Further extensions of the dynamics of timed automata lead to *rectangular* automata [100] and eventually to general *hybrid* automata [12,98].

Finally, another interesting direction in which timed automata have been extended consists in adding parameters. Parameters can be used in lieu of numerical constants in the timed automaton, with the aim of deciding the existence of (and computing) values for the parameters for which a given property holds true. The use of parameters simplifies the modeling phase, but unfortunately the existence of valid parameters turns out to be undecidable in general [19]. Several decidable classes have been identified, including one-clock parametric timed automata [19, 129] and L/U automata, where each parameter can be used either in lower-bound constraints or in upper-bound constraints [106].

## 4 (Bi)simulation Checking

## 4.1 (Bi)simulations for Timed Automata

As detailed in Sect. 2, the operational semantics of timed automata is given in terms of timed transition systems, which in fact can be viewed as standard labelled transition systems, with labels (d, a) comprising a delay and a letter. Hence any behavioral equivalence and preorder defined on labelled transition systems may be interpreted over timed automata. In particular the classical notions of simulation and bisimulation [130, 138] give rise to the following notion of timed (bi)simulation:

**Definition 4.** Let  $A = (L, \ell_0, C, \Sigma, I, E)$  be a timed automaton. A relation  $R \subseteq L \times \mathbb{R}_{\geq 0}^C \times L \times \mathbb{R}_{\geq 0}^C$  is a *timed simulation* provided that for all  $(\ell_1, v_1) R$   $(\ell_2, v_2)$ , for all  $(\ell_1, v_1) \xrightarrow{d,a} (\ell'_1, v'_1)$  with  $d \in \mathbb{R}_{\geq 0}$  and  $a \in \Sigma$ , there exists some  $(\ell'_2, v'_2)$  such that  $(\ell'_1, v'_1) R$   $(\ell'_2, v'_2)$  and  $(\ell_2, v_2) \xrightarrow{d,a} (\ell'_2, v'_2)$ . A *timed bisimulation* is a timed simulation which is also symmetric, and two

A timed bisimulation is a timed simulation which is also symmetric, and two states  $(\ell_1, v_1), (\ell_2, v_2) \in \llbracket A \rrbracket$  are said to be timed bisimilar, written  $(\ell_1, v_1) \sim (\ell_2, v_2)$ , if there exists a timed bisimulation R for which  $(\ell_1, v_1) R (\ell_2, v_2)$ .

Note that  $\sim$  is itself a timed bisimulation on A (indeed the greatest such), which is easily shown to be an equivalence relation and hence transitive, reflexive, and symmetric. Also—as usual—timed bisimilarity may be lifted to an equivalence between two timed automata A and B by relating their initial states.

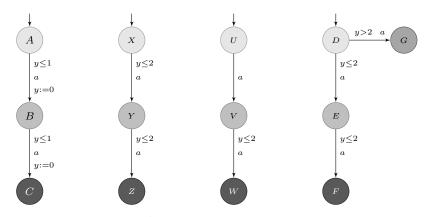

Fig. 6 Four timed automata A, X, U and D

Consider the four automata A, X, U and D in Fig. 6 (identifying the automata with the names of their initial locations). Here (U, v) and (D, v)

are timed bisimilar as any transition  $(U, v) \xrightarrow{d,a} (V, v')$  may be matched by either  $(D, v) \xrightarrow{a} (G, v')$  or  $(D, v) \xrightarrow{a} (E, v')$  depending on whether v(y) > 2 or not after delay d. In fact, it may easily be seen that U and D are the only locations of Fig. 6 that are timed bisimilar (when coupled with the same valuation of y). E.g., A and X are not timed bisimilar since the transition  $(X, 0) \xrightarrow{1.5,a} (Y, 1.5)$  cannot be matched by (A, 0) by a transition with *exactly* the same duration. Instead A and X are related by the weaker notion of *time-abstracted* bisimulation, which does not require equality of the delays (see Definition 2). It may be seen that A and X are both time-abstracted simulated by U and D but *not* time-abstracted bisimilar to U and D. Also, U and D are time-abstracted bisimilar, which follows from the following easy fact:

**Theorem 2.** Any two automata being timed bisimilar are also time-abstracted bisimilar.

## 4.2 Checking (Bi)simulations

As we now explain, timed and time-abstracted (bi)similarity are decidable for timed automata.

**Theorem 3.** Time-abstracted similarity and bisimilarity are decidable for timed automata.

For proving this result, one only needs to see that time-abstracted (bi)simulation in the timed automaton is the same as ordinary (bi)simulation in the associated region automaton; indeed, any state in  $[\![A]\!]$  is untimed bisimilar to its image in  $[\![A]\!]_{\cong}$ . The result follows by finiteness of the region automaton.

For timed bisimilarity, decidability—as we shall see in Sect. 9—is obtained by playing a game on a product construction, yielding an exponential-time algorithm for checking timed bisimilarity.

**Theorem 4 ([73]).** Timed similarity and bisimilarity are decidable for timed automata.

## **5** Language-Theoretic Properties

#### 5.1 Language of a Timed Automaton

This section introduces the notion of (timed) *language* associated with timed automata, and focusses on basic decision problems such as language emptiness and inclusion, as well as standard Boolean operations on languages.

Model Checking Real-Time Systems

Properties of languages associated with various computational models are a classical object of study in computer science; moreover, many model-checking, refinement, and verification problems can often be stated in terms of languages, notably by translating them into language emptiness or language inclusion problems.

In this section we consider timed automata augmented with sets of *accepting locations*. Given a timed automaton  $A = (L, \ell_0, C, \Sigma, I, E, F)$ , where  $F \subseteq L$ is the set of accepting locations, a finite run

$$\rho = (\ell_0, v_0) \stackrel{d_{1,a_1}}{\longrightarrow} (\ell_1, v_1) \stackrel{d_{2,a_2}}{\longrightarrow} \dots \stackrel{d_n, a_n}{\longrightarrow} (\ell_n, v_n)$$

of A is accepting if  $\ell_n \in F$ . The language  $\mathcal{L}(A)$  of A consists of all finite timed words over alphabet  $\Sigma^*$  generated by accepting runs of A.

The language of infinite words accepted by a timed automaton is defined analogously; the relevant acceptance condition is that the underlying infinite run visits locations in F infinitely often. We write  $\mathcal{L}_{\omega}(A)$  to denote the set of infinite timed words accepted by A.

## 5.2 Timed Automata with $\varepsilon$ -Transitions

Silent transitions are transitions of the form  $(q, g, \varepsilon, r, q')$ , where  $\varepsilon$  is the empty word. In other terms, they are transitions carrying no letter. Silent transitions offer a convenient way of modeling, e.g., internal actions. In the setting of finite-state automata, it is well known that such transitions can be removed, by merging them with the possible subsequent actions.

The question whether the above result extends to the timed setting was settled in [42], with a negative answer: to see this, simply consider the automaton in Fig. 7; its language  $\mathcal{L}(A)$  contains precisely those timed words in which all timestamps are even integer numbers. Towards a contradiction, assume that there exists a timed automaton B, without  $\varepsilon$ -transitions, such that

Fig. 7 A timed automaton with  $\varepsilon$ -transitions

$\mathcal{L}(A) = \mathcal{L}(B)$ ; write *m* for the maximal integer constant appearing in the timing constraints of *B*. Then the one-letter word  $(\sigma, 2m)$  is accepted by *B*, since it is accepted by *A*. Since *B* has no silent transition, it must have a  $\sigma$ -transition from an initial state to an accepting one. The guard on this transition can only involve constants less than or equal to *m*, so that *B* must accept  $(\sigma, k)$  for all k > m, which is a contradiction.

**Theorem 5 ([42]).** Silent transitions strictly increase the expressive power of timed automata.

It can be proved that in the case when  $\varepsilon$ -transitions do not reset any clock, they do not add expressiveness. Finally, let us mention that the question whether a timed automaton with silent transitions is equivalent (i.e., accepts the same language) to some timed automaton without such transitions is undecidable [56].

In the sequel, we consider timed automata without  $\varepsilon$ -transitions.

## 5.3 Clock Constraints as Acceptance Conditions

Clock constraints can be used to enable or disable certain conditions along the runs of a timed automaton. As such, they can be used to define acceptance conditions, when added on top of a finite-state automaton.

In this setting, we consider the *untimed language* of timed automata: given a timed automaton A, its untimed language (of infinite words) is the set  $\mathcal{L}_u$ containing exactly those words  $(a_i)_{i \in \mathbb{N}}$  for which there is a *diverging* realvalued sequence  $(d_i)_{i \in \mathbb{N}}$  such that the timed word  $(a_i, d_i)_{i \in \mathbb{N}} \in \mathcal{L}_{\omega}(A)$ . Notice that thanks to the time-abstracted bisimulation between a timed automaton and its region automaton, the untimed language of a timed automaton is easily seen to be  $\omega$ -regular.

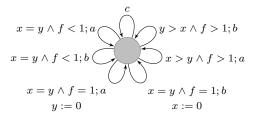

Fig. 8 Automaton accepting words with finitely many a's or finitely many b's

Conversely, any  $\omega$ -regular language is the untimed language of a timed automaton: as an example, consider the language of infinite words over  $\{a, b, c\}$ that have finitely many *a*'s or finitely many *b*'s. The untimed language of the automaton depicted in Fig. 8 precisely corresponds to that language: indeed, the *a*- and *b*-transitions on the left can only be taken finitely many times, since we require time divergence. Hence one of the *a*- and the *b*-transitions at the bottom has to be taken. But after this time, only the corresponding transition on the right is allowed (together with the *c*-transition, which is always allowed). This construction can be generalized, so that:

**Theorem 6 ([101]).** Given an  $\omega$ -regular language L, there exists a (onelocation) timed automaton A such that  $\mathcal{L}_u(A) = L$ . The number of clocks and locations can be shown to define strict hierarchies of (untimed)  $\omega$ -regular languages.

More generally, given a finite-state automaton A and an  $\omega$ -regular language L, one can equip A with clocks and clock constraints in such a way that the untimed language of the resulting timed automaton is the intersection of the language of A with L [101].

## 5.4 Intersection, Union, and Complement

A (finite or infinite) language is said to be *timed regular* if it is accepted by some timed automaton. Timed regular languages (both finite and infinite) are effectively closed under intersection and union. They are however not closed under complement. We reproduce in Fig. 9 an example (taken from [13]) of a timed automaton A, equipped with a single clock, that cannot be complemented: there does not exist a timed automaton A' such that  $\mathcal{L}_{\omega}(A')$  is the set of all timed words not accepted by A. The complement of  $\mathcal{L}_{\omega}(A)$  contains

Fig. 9 A non-complementable timed automaton

all timed traces in which no pair of a's is separated by exactly one time unit. Intuitively, since there is no bound on the number of a's that can occur in any unit-duration time interval, any timed automaton capturing the complement of  $\mathcal{L}_{\omega}(A)$  would require an unbounded number of clocks to keep track of the times of all the a's within the past one time unit. A formal proof that Acannot be complemented is given in [105].

Under some restrictions, timed automata can be made determinizable (hence also complementable). Most notably, event-clock automata [16] enjoy this property. In such timed automata, each letter a of the alphabet is associated with two clocks  $x_a$  and  $y_a$  (and any clock is associated with some letter that way): clock  $x_a$  (called the event-recording clock of a) is used to measure the delay elapsed since the last reset of event a (and is initially set to some special value  $+\infty$ ), while  $y_a$  (the event-predicting clock of a) is used to constrain the delay until the next occurrence of a. One can easily show that event-clock automata can be represented as classical timed automata, though several clocks might be needed to encode each event-recording clock. Figure 10 displays an example of an event-clock automaton accepting those timed words containing two *consecutive* a's separated by exactly one time unit.

Fig. 10 An event-clock automaton

It must be remarked that, at any time during a run of an event-clock automaton on some timed word w, the valuation of the clocks does not depend on the run, but only on w. As a consequence, the classical subset construction for determinising finite-state automata can be adapted to handle event-clock automata, which thus form an (effectively) determinizable and complementable class of timed automata.

## 5.5 Language Emptiness, Inclusion

It follows immediately from Theorem 1 that the language-emptiness problem for timed automata is **PSPACE**-complete [13]. Unfortunately the languageuniversality, language-inclusion and language-equivalence problems for timed automata are all undecidable. By contrast, recall from Theorem 4 that the related branching-time counterparts to language inclusion and equivalence, namely similarity and bisimilarity, are both decidable on timed automata.

**Theorem 7 ([13]).** The language-inclusion problem for timed automata is undecidable, both over finite and infinite words.

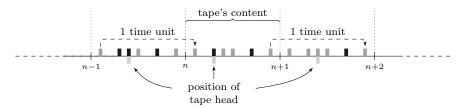

The proof of Theorem 7 is by reduction from the Halting Problem for Turing machines. This reduction involves encoding the valid halting computations of a given Turing machine M as a timed language whose complement is recognized by a timed automaton  $A_M$  which can be effectively computed from M. Intuitively, discrete computation steps of M are simulated over unit-duration time intervals, with timed events used to encode the tape's contents. The integrity of the tape in a valid encoding of a computation is maintained by requiring that any given timed event be preceded and followed at a distance of exactly one time unit by the same timed event, and vice-versa (unless the corresponding character is to be modified by M in the computation step). Figure 11 illustrates this encoding. Note that the density of time enables one to accommodate arbitrarily large tape contents. The key idea is that while no timed automaton can in general accurately capture the encodings of valid computations of a Turing machine,  $A_M$  can be engineered to recognise

Model Checking Real-Time Systems

Fig. 11 Encoding computations of Turing machines as timed words

precisely all the *invalid* computations of M; indeed, a computation is invalid if it fails one of finitely many rules, the most interesting of which is to adequately preserve the tape's contents. The latter is easily detected, either by a timed automaton witnessing a timed event with no predecessor one time unit earlier (corresponding to an *insertion* error on the tape), or conversely by a timed automaton witnessing a timed event with no successor one time unit later (corresponding to a *deletion* error on the tape). Other rule failures can likewise be detected by small timed automata. Automaton  $A_M$  is obtained as the disjunction of those finitely many timed automata. The upshot is that M fails to have a valid halting computation iff  $A_M$  accepts every single timed trace. This shows that universality, and *a fortiori* language inclusion, are indeed undecidable for timed automata.

Theorem 7 places a serious limitation on the algorithmic analysis of timed automata since many verification questions naturally reduce to checking language inclusion. In spite of this hindrance there has been a great deal of research on various aspects of timed language inclusion, including [16,102,134] among many others. Here we describe several approaches, involving syntactic and semantic restrictions on timed automata, to obtaining positive decidability results for language inclusion.

Let us first notice that the classical approach to deciding language inclusion is by testing emptiness of the intersection of the first language with the complement of the second one. Thus whether  $\mathcal{L}_{\omega}(A) \subseteq \mathcal{L}_{\omega}(B)$  is decidable as soon as *B* can be complemented. For instance:

**Theorem 8 ([15]).** Given timed automata A and B, the language-inclusion problem  $\mathcal{L}_{\omega}(A) \subseteq \mathcal{L}_{\omega}(B)$  is decidable if B is an event-clock automaton.

Using more elaborate techniques (based on *well-quasi-orderings* and Higman's Lemma), we can prove:

**Theorem 9** ([124, 134, 135]). Given timed automata A and B, the finiteword language-inclusion problem  $\mathcal{L}(A) \subseteq \mathcal{L}(B)$  is decidable and non-primitive recursive provided B has at most one clock.

In the case of infinite words, the language-inclusion problem  $\mathcal{L}_{\omega}(A) \subseteq \mathcal{L}_{\omega}(B)$ is undecidable even when *B* has only one clock. The proof of undecidability is by reduction from the boundedness problem for lossy channel machines [4]. A natural semantic restriction on timed automata to recover decidability of language inclusion involves adopting a discrete-time model. Given a timed language  $\mathcal{L}$ , let  $\mathbb{Z}(\mathcal{L})$  denote the set of timed words  $(a_1, t_1) \dots (a_p, t_p)$  such that each timestamp  $t_i$  lies in  $\mathbb{Z}$ . Given timed automata A and B, the discrete-time language-inclusion problem is to decide whether  $\mathbb{Z}(\mathcal{L}(A)) \subseteq \mathbb{Z}(\mathcal{L}(B))$ . This problem is EXPSPACE-complete: the exponential blow-up over the complexity of the language-inclusion problem for classical non-deterministic finite automata arises from the succinct binary representation of clock values in timed automata. Hardness in EXPSPACE is proven in [28].

Using a technique called *digitization* [102] the discrete behaviors of timed automata can be used to infer conclusions about their dense-time behavior. For example:

**Theorem 10 ([102]).** Let A be a closed timed automaton (i.e., having only non-strict inequalities as clock constraints) and B an open timed automaton (i.e., having only strict inequalities). Then  $\mathcal{L}(A) \subseteq \mathcal{L}(B)$  if and only if  $\mathbb{Z}(\mathcal{L}(A)) \subseteq \mathbb{Z}(\mathcal{L}(B))$ .

To apply Theorem 10 one can imagine over-approximating a real-time model by a closed timed automaton and under-approximating a specification by an open timed automaton.

Rather than restricting the precision of the semantics we can instead consider a time-bounded semantics in which we consider only finite timed words of total duration at most N. Note that due to the density of time there is no bound on the number of events that can be performed in a fixed time period. In this case, for the whole class of timed automata, we have:

**Theorem 11 ([133]).** Over bounded time (i.e., considering only finite timed words of total duration at most N, for some fixed time bound N), the language-inclusion problem is 2-EXPSPACE-complete.

Theorem 11 was proven as a corollary of the decidability of satisfiability of monadic second-order logic over structures of the form (I, <, +1), with I a bounded interval of reals and +1 denoting the plus-one relation: +1(x, y) iff y = x + 1.

Notwithstanding the positive decidability results Theorem 9 and Theorem 11, neither one-clock timed automata nor automata over bounded time are closed under complement. (The counterexample in Sect. 5.4 can still be used in both cases.) To remedy this deficiency, the strictly more powerful model of *alternating timed automata* has been introduced [124, 135]. Alternating timed automata are a common generalization of timed automata and alternating finite automata; they are closed under all Boolean operations, but language inclusion remains decidable for alternating timed automata with one clock or over bounded time. Unlike in the untimed setting, alternating timed automata. This extra expressiveness is crucially utilised in [135] where it is shown how to translate formulas of Metric Temporal Logic (see Sect. 6) into equivalent one-clock alternating timed automata.

#### 6 Timed Temporal Logics

The whole theory of temporal-logic model checking has been extended to the setting of timed automata, in order to express and check richer properties beyond emptiness/reachability. We present the most significant results below.

## 6.1 Linear-Time Temporal Logics

The most natural way of extending LTL (see Chap. 2temp) with quantitative requirements is by decorating modalities with timing constraints. We present the resulting logic, called *Metric Temporal Logic* (MTL), below. Another extension consists in using clocks in formulas, with a way of resetting them when some property is fulfilled and checking their values at a later moment. The resulting logic is called *Timed Propositional Temporal Logic* (TPTL). Due to lack of space, we don't detail the latter logic, and rather refer to [17, 18, 52] for more details about TPTL.

Given a set P of atomic propositions, the formulas of MTL are built from P using Boolean connectives and time-constrained versions of the *until* operator **U** as follows:

$$\varphi ::= p \mid \neg \varphi \mid \varphi \land \varphi \mid \varphi \mathbf{U}_I \varphi,$$

where  $I \subseteq (0, \infty)$  is an interval of reals with endpoints in  $\mathbb{N} \cup \{\infty\}$ . We sometimes abbreviate  $\mathbf{U}_{(0,\infty)}$  to  $\mathbf{U}$ , calling this the *unconstrained* until operator.

Further connectives can be defined following standard conventions. In addition to propositions  $\top$  (true) and  $\perp$  (false) and disjunction  $\lor$ , we have the constrained eventually operator  $\Diamond_I \varphi \equiv \top \mathbf{U}_I \varphi$ , and the constrained always operator  $\Box_I \varphi \equiv \neg \Diamond_I \neg \varphi$ .

Sometimes MTL is presented with past connectives (e.g., constrained versions of the "since" connective from LTL) as well as future connectives [17]. However we do not consider past connectives in this chapter.

Next we describe two commonly adopted semantics for MTL.

#### Continuous Semantics.

Given a set of propositions P, a signal is a function  $f: \mathbb{R}_{\geq 0} \to 2^P$  mapping  $t \in \mathbb{R}_{\geq 0}$  to the set f(t) of propositions holding at time t. We say that f has finite variability if its set of discontinuities has no accumulation points (in other words, on any finite interval the value of f can only change a finite number of times). In this chapter, we require that all signals be finitely variable. Given an MTL formula  $\varphi$  over the set of propositional variables P, the satisfaction relation  $f \models \varphi$  is defined inductively, with the classical rules for atomic

propositions and Boolean operators, and with the following rule for the "until" modality, where  $f^t$  denotes the signal  $f^t(s) = f(t+s)$ :

$$f \models \varphi_1 \mathbf{U}_I \varphi_2$$

iff for some  $t \in I$ ,  $f^t \models \varphi_2$  and  $f^u \models \varphi_1$  for all  $u \in (0, t)$ .

Pointwise Semantics.

In the *pointwise semantics* MTL formulas are interpreted over timed words. Given a (finite or infinite) timed word  $w = (a_1, t_1), \ldots, (a_n, t_n)$  over alphabet  $2^P$  and an MTL formula  $\varphi$ , the satisfaction relation  $w, i \models \varphi$  (read "w satisfies  $\varphi$  at position i") is defined inductively, with the classical rules for Boolean operators, and with the following rule for the "until" modality:

$$\begin{split} w,i \models \varphi_1 \, \mathbf{U}_I \, \varphi_2 \ \ \text{iff} \ \ \text{there exists} \ j \ \text{such that} \ i < j < |w|, \ w,j \models \varphi_2, \\ t_j - t_i \in I, \ \text{and} \ w,k \models \varphi_1 \ \text{for all} \ k \ \text{with} \ i < k < j. \end{split}$$

The pointwise semantics is less natural if one thinks of temporal logics as encoding fragments of monadic logic over the reals. On the other hand it seems more suitable when considering MTL formulas as specifications on timed automata. In this vein, when adopting the pointwise semantics it is natural to think of atomic propositions in MTL as referring to events (corresponding to location changes) rather than to locations themselves.

Consider our example of Fig. 2. Using LTL, we can express the property that Process  $P_i$  will try to get the resource infinitely many times, by writing  $\Box \Diamond \texttt{start!}$ . With MTL, we can be more precise and write  $\Box \Diamond_{\leq 4} \texttt{start!}$ , stating that whatever the current state, within four time units Process  $P_1$  will start trying to acquire the resource. MTL can also be used to express bounded-time response properties, such as  $\Box (\texttt{start!} \Rightarrow \Diamond_{\leq 10} \texttt{acquire!})$ .

## 6.2 Verification of Linear-Time Temporal Logics

Model checking timed automata can be carried out under either pointwise or continuous semantics. For the latter, it is necessary to alter our definitions to associate a language of *signals* with a timed automaton rather than a language of timed words. In turn, this requires a notion of timed automata in which locations are labelled by atomic propositions. A full development of this semantics can be found, e.g., in [14].

**Theorem 12 ([13]).** Model checking and satisfiability for LTL, over both the pointwise and continuous semantics, are PSPACE-complete.

The PSPACE upper bound in Theorem 12 can be established in the same manner as in the untimed case, by translating the negated formula to a Büchi automaton, and performing an on-the-fly reachability check on the product of this automaton with the region graph of the model. **Theorem 13** ([135–137]). Model checking and satisfiability for MTL in the pointwise semantics over finite words are decidable but non-primitive recursive. Over infinite words, both problems are undecidable.

As explained in Sect. 5.5, the decidability results are essentially obtained by translating MTL formulas into one-clock alternating timed automata, and rephrasing the model-checking or satisfiability problems as instances of language emptiness in one-clock alternating timed automata.

The undecidability result proceeds by reduction from the recurrent reachability problem for channel machines with insertion errors: the infinite runs of such a machine can be encoded as timed words, which in turn are easily characterized by an MTL formula [136].

#### **Theorem 14** ([14]). Model checking and satisfiability for MTL in the continuous semantics (over both finite and infinite signals) are undecidable.

The extra expressiveness of the continuous semantics enables a more direct proof of undecidability than in Theorem 13. In this case, one can directly encode the computations of a Turing machine as timed signals, which again can be captured by an MTL formula, following a scheme similar to that of Theorem 7.

A key ingredient of the undecidability proof of Theorem 14, as well as the non-primitive recursive complexity in Theorem 13, is the ability of MTL to express *punctuality*, i.e., the requirement that two events be separated by an exact duration. A fragment of MTL that syntactically disallows punctuality, known as *Metric Interval Temporal Logic* (MITL), was proposed by Alur *et al.* in [14]. In MITL, one requires that all instances of the interval *I* appearing in uses of the constrained until operator  $\mathbf{U}_I$  be non-singular. The main result of [14] is as follows:

**Theorem 15** ([14]). For both the pointwise and continuous semantics, model checking and satisfiability for MITL are EXPSPACE-complete, over both finite and infinite behaviors.

This theorem was obtained by translating MITL formulas into equivalent timed automata of potentially exponential size. In contrast, it is easy to write an MTL formula that has no equivalent timed automaton: for example, the formula  $\neg \Diamond (a \land \Diamond_{=1} a)$  captures the complement of the language of automaton A in Fig. 9.

Another decidable fragment of MTL can be obtained by adapting the idea of *event clocks* to temporal logics [140]: here, timing constraints can only refer to the *next* (or *previous*) occurrence of an event. Hence ECTL (standing for *Event-Clock Temporal Logic*) extends LTL with  $\triangleright_I \varphi$  and  $\triangleleft_I \varphi$ . For instance, that there are two *consecutive a*'s separated by one time unit is written in ECTL as  $\Diamond (a \land \triangleright_{=1} a)$ .

**Theorem 16 ([140]).** Satisfiability and model checking are PSPACE-complete for ECTL, in either the pointwise or continuous semantics.

Not surprisingly, deciding ECTL is achieved by a translation to event-clock automata (see Sect. 5.4). However, event-clock automata are not powerful enough to precisely capture ECTL, and require the use of *timed Hintikka* sequences. Intuitively, given a formula  $\varphi$  in ECTL, a timed Hintikka sequence is a timed word on sets of subformulas of  $\varphi$ , required to satisfy local consistency conditions. Compare to a timed word, a timed Hintikka sequence contains more information about the truth value of the subformulas of  $\varphi$ , which will help the event-clock automaton decide whether the underlying timed word is to be accepted. We refer to [140] for more details, and to [104] for an extension of event-clock automata that encompasses ECTL.

Rather than imposing syntactical restrictions, an alternative approach to recovering decidability is to consider a *time-bounded* semantics, i.e., in which either timed words or signals are observed over a fixed, bounded time interval:

**Theorem 17 ([133]).** Model checking and satisfiability for MTL over bounded time, in either the pointwise or continuous semantics, are EXPSPACE-complete.

The main technique used in the proof of Theorem 17 is an exponential transformation from MTL formulas, given a fixed time bound, into equisatisfiable LTL formulas.

#### 6.3 Branching-Time Temporal Logics

Given a set P of atomic propositions,  $\mathsf{TCTL}^*$  formulas are state-formulas obtained as formulas  $\varphi_s$  from the following grammar:

$$\begin{split} \varphi_s &::= p \mid \neg \varphi_s \mid \varphi_s \land \varphi_s \mid \mathbf{E}\varphi_p \mid \mathbf{A}\varphi_p \\ \varphi_p &::= \varphi_s \mid \neg \varphi_p \mid \varphi_p \land \varphi_p \mid \varphi_p \mathbf{U}_I \varphi_p \end{split}$$

Compared to  $\mathsf{CTL}^*$ ,  $\mathsf{TCTL}^*$  has a *time-constrained* until, requiring as for  $\mathsf{MTL}$  that the right-hand side formula should be fulfilled within that time. The same shorthands as for  $\mathsf{MTL}$  can be defined, such as  $\Diamond_I \varphi$  or  $\Box_I \varphi$ .

As for the linear-time temporal logics, the semantics of TCTL<sup>\*</sup> comes in (at least) two flavours: continuous and pointwise. The continuous semantics is defined on *dense trees*, which naturally extend classical discrete trees to the continuous setting [7,89] and represent the set of signals of timed automata; this semantics extends the continuous-time semantics of MTL with path quantifiers.

The pointwise semantics is defined over discrete (but infinite-branching) trees, which can be used to represent the timed words generated by timed automata. This corresponds to evaluating TCTL\* formulas over the operational semantics of timed automata, as defined in Sect. 2.

Finally, as for the untimed case, the fragment of TCTL<sup>\*</sup> where each temporal modality is under the immediate scope of a path quantifier is of particular interest, and will be called TCTL.

Before turning to the algorithmic part, let us show how TCTL can be used to express desirable properties of the timed system modeled in Fig. 2. Mutual exclusion (in a setting with two processes  $P_1$  and  $P_2$  and one resource  $R_1$ ) is expressed as  $\neg \mathbf{E} \Diamond$  (working<sub>1</sub>  $\land$  working<sub>2</sub>): two processes will never be working (i.e., using the resource) at the same time. We can also express timing requirements, such as the fact that Process  $P_i$  will never be working continuously for more than one time unit:  $\mathbf{A} \Box (\mathbf{A} \Diamond_{\leq 1} \neg \operatorname{working}_i)$ .

## 6.4 Verification of Branching-Time Temporal Logics

Since TCTL<sup>\*</sup> embeds MTL, there is no hope that its model checking and satisfiability will be decidable. On the lower side, CTL model checking is clearly decidable over timed automata: CTL is invariant under bisimulation, so that any property to be checked on a timed automaton can equivalently be checked on its corresponding finite-state region automaton.

Concerning TCTL, model checking can be shown to be decidable. Actually, this can easily be shown on the explicit-clock version of TCTL (using formula clocks), which strictly subsumes TCTL. For this logic, the important property is that any two region-equivalent states satisfy the same formulas: this can be proven by induction on the structure of the formula. Consider for instance the formula  $\zeta = \mathbf{E}\varphi \mathbf{U}_I \psi$ , assuming that  $\varphi$  and  $\psi$  are compatible with region (i.e., if they hold true in some state, then they also hold true in any regionequivalent state). Given a timed automaton A, consider the automaton  $A_t$ obtained by adding an extra clock t to A, which does not modify its behavior. Then if  $(\ell, v) \models \zeta$  in A, then  $(\ell, v_t) \models \mathbf{E}\varphi \mathbf{U} (\psi \wedge t \in I)$  where  $v_t$  extends vby mapping clock t to zero and " $t \in I$ " (which is not a TCTL formula but whose meaning is rather clear) is also compatible with regions. In the end, the set of states in  $A_t$  where formula  $\mathbf{E}\varphi \mathbf{U} (\psi \wedge t \in I)$  is a union of regions, so that it is also the case for the set of states of A where  $\zeta$  holds.

Using this result, TCTL model checking can be achieved by labeling states of the region automaton with the subformulas they satisfy. This applies for both semantics, with slight differences. It should be noticed that this extends to the explicit-clock version of TCTL, and even to the fragment of explicit-clock TCTL\* where formula-clocks are only reset at the level of path quantifiers [66].

While labeling the region automaton requires exponential space, the algorithm can be implemented in a space-efficient manner so as to only use polynomial space. Reachability being already PSPACE-hard, we get the following theorem:

**Theorem 18 ([9]).** TCTL model checking is PSPACE-complete.

TCTL (as well as CTL) suffers from not being able to express useful properties, in particular fairness (see Chap. 2temp on temporal logics). One way to solve this problem is by decorating path quantifiers with fairness requirements [7,152]. One can then apply classical algorithms for CTL with fairness [75] or adapt fixpoint characterizations. Another approach is to consider TCTL defined with formula clocks as sketched above, and to have it include CTL<sup>\*</sup>. The resulting logic is very expressive while still enjoying a PSPACE model-checking algorithm [66].

These positive results about model checking do not extend to satisfiability:

### **Theorem 19** ([9]). *TCTL* satisfiability is undecidable.

The proof follows the same ideas as for undecidability of MTL satisfiability, by associating universal path-quantifiers with each temporal modality. As for the linear-time case, it suffices to ban equality constraints to recover decidability [117, 118]. This can be proved by lifting tree-automata techniques to the timed setting.

## 7 Symbolic Algorithms, Data Structures, Tools

## 7.1 Zones and Operations

As shown in the previous sections, the regions introduced in Sect. 3 provide a finite and elegant abstraction of the infinite state space of timed automata, enabling us to prove decidability of a wide range of problems, including (timed and untimed) bisimilarity, untimed language equivalence and language emptiness, as well as TCTL model checking.

Unfortunately, the number of states obtained from the region partitioning is extremely large. Indeed, it is exponential in the number of clocks as well as in (the binary representation of) the maximal constants of the timed automaton [13]. Efforts have been made to develop more efficient representations of the state space [34, 39, 103, 121], using the notion of *zones* introduced below as a coarser and more compact representation of the state space.

For a finite set C of clocks, a subset  $Z \subseteq \mathbb{R}_{\geq 0}^C$  is called a *zone* if there exists  $\varphi \in \Phi_d(C)$  for which  $Z = \llbracket \varphi \rrbracket_C$ . For reachability analysis, we need the following operations on zones: for a zone  $Z \subseteq \mathbb{R}_{\geq 0}^C$  and  $r \subseteq C$ , let us denote

- the delay of Z by  $Z^{\uparrow} = \{v + d \mid v \in Z, d \in \mathbb{R}_{>0}\}$  and

- the reset of Z under r by  $Z[r] = \{v[r] \mid v \in \overline{Z}\}.$

**Lemma 1 ([103, 157]).** Let Z, Z' be zones over C and  $r \subseteq C$ . Then  $Z^{\uparrow}$ , Z[r], and  $Z \cap Z'$  are also zones over C.

Model Checking Real-Time Systems

**Definition 5.** The *zone automaton* associated with a timed automaton  $A = (L, \ell_0, C, \Sigma, I, E)$  is the transition system  $\llbracket A \rrbracket_Z = (S, s_0, \Sigma \cup \{\delta\}, T)$  given as follows:

$$S = \left\{ (\ell, Z) \mid \ell \in L, Z \subseteq \mathbb{R}_{\geq 0}^{C} \text{ is a zone} \right\} \qquad s_{0} = \left( \ell_{0}, \llbracket v_{0} \rrbracket \right)$$

$$T = \left\{ (\ell, Z) \stackrel{\delta}{\rightsquigarrow} \left( \ell, Z^{\uparrow} \cap \llbracket I(\ell) \rrbracket_{C} \right) \right\}$$

$$\cup \left\{ (\ell, Z) \stackrel{a}{\rightsquigarrow} \left( \ell', (Z \cap \llbracket \varphi \rrbracket_{C})[r] \cap \llbracket I(\ell') \rrbracket_{C} \right) \mid \ell \stackrel{\varphi, a, r}{\longrightarrow} \ell' \in E \right\}$$

Analogously to Prop. 1, we have:

**Proposition 2 ([157]).** A location  $\ell$  in a timed automaton  $A = (L, \ell_0, F, C, \Sigma, I, E)$  is reachable if and only if there is a zone  $Z \subseteq \mathbb{R}_{\geq 0}^C$  for which  $(\ell, Z)$  is reachable in  $[\![A]\!]_Z$ .

A priori, however, the zone automaton defined above is infinite, hence another, finite, abstraction is needed. This is provided by *normalization* using region equivalence  $\cong_M$ : for a maximal constant M, the *normalization* of a zone  $Z \subseteq \mathbb{R}_{\geq 0}^C$  is the set  $\{v : C \to \mathbb{R}_{\geq 0} \mid \exists v' \in Z : v \cong_M v'\}$ . The normalization of a zone is not in general a zone, hence in practice other normalization operators are used (see Sect. 7.3).

The normalized zone automaton is defined analogously to the zone automaton defined above, and in case the timed automaton to be verified does not contain diagonal clock constraints of the form  $x - y \bowtie k$ , Prop. 2 also holds for the normalized zone automaton. Hence we can obtain a reachability algorithm by applying any search strategy (depth-first, breadth-first, or another) on the normalized zone automaton.

For timed automata that contain diagonal clock constraints  $x - y \bowtie k$ , however, it can be shown [38, 48] that normalization as defined above does *not* give rise to a sound and complete characterization of forward reachability. Instead, one can apply a refined normalization which depends on the difference constraints used in the timed automaton, see [38].

## 7.2 Symbolic Datastructures

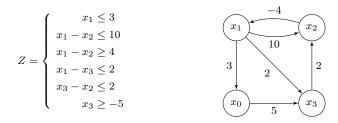

A zone, given by a conjunction of elementary clock constraints, may be represented using a directed weighted graph, where the nodes correspond to the clocks in C together with an extra "zero" clock  $x_0$ , and an edge  $x_i \xrightarrow{k} x_j$ corresponds to a constraint  $x_i - x_j \leq k$  (if there is more than one upper bound on  $x_i - x_j$ , k is the minimum of all these constraints' right-hand sides). The extra clock  $x_0$  is fixed at value 0, so that a constraint  $x_i \leq k$  can be represented as  $x_i - x_0 \leq k$ . Lower bounds on  $x_i - x_j$  are represented as (possibly negative) upper bounds on  $x_j - x_i$ , and strict bounds  $x_i - x_j < k$ are represented by adding a flag to the corresponding edge. The weighted graph in turn may be represented by its adjacency matrix, which in this context is known as a *difference-bound matrix* or DBM. The above technique was introduced in [87] (the main ideas were already present in [43]). Figure 12 gives an illustration of an extended clock constraint together with its representation as a difference-bound matrix. Note that the clock constraint contains superfluous information.

Fig. 12 Graph representation of extended clock constraint

On zones represented using DBMs, efficient (in time cubic in the number of clocks in C) algorithms are available for computing delays, resets and intersections. For reachability checking, other necessary operations inclusion checking whether  $Z \subseteq Z'$ , and emptiness checking,  $Z = \emptyset$ ; these can also be computed efficiently using DBMs.

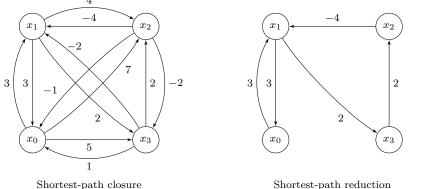

For these computations, a canonical representation obtained as the *shortest-path closure* of the DBM graph is used. Another useful canonical form is the *shortest-path reduction* described in [120]. Whereas the shortest-path closure form gives all derived constraints, the shortest-path reduced form provides a memory-efficient representation, containing only a minimal set of constraints. Figure 13 shows the two canonical forms of the DBM of Fig. 12. Given the shortest-path closure of the DBM graph, the shortest-path reduced form is obtained by partitioning the set of clocks according to zero cycles in the DBM graph; in the DBM of Fig. 13,  $\{x_1, x_2, x_3\}$  constitutes one such class, and  $\{x_0\}$  is another one. The reduced form is now obtained by maintaining a minimal set of constraints for each class, essentially a simple cycle of the clocks of the class, and only keeping constraints between representatives of different classes, here  $x_1$  and  $x_0$ .

To combat state-space explosion in zone graphs, several optimizations are used. One such approach is to detect whether a state  $(\ell, Z)$  reached through the algorithm is contained in another state  $(\ell, Z')$  which has already been explored. In this case, exploration of  $(\ell, Z)$  will be unnecessary.

Another such optimization is to work with unions of zones. If states  $(\ell, Z)$  and  $(\ell, Z')$  are found to reachable during the analysis, then we know that altogether the state  $(\ell, Z \cup Z')$  is reachable. Unfortunately, unions of zones are not generally themselves zones, so cannot be efficiently represented using DBMs.

Model Checking Real-Time Systems

Fig. 13 Canonical representations

For representing unions of zones, or *federations* as they are called in this context, a data structure inspired by decision diagrams called *clock difference diagrams* or CDDs is used [121]. However, no efficient algorithms are known to compute delays or resets of federations using CDDs, so in practice reachability analysis using CDDs is done by extracting the zones from the CDD and performing the operations on them one by one.

Other promising data structures in this context are numerical decision diagrams [24], difference decision diagrams [132], clock-restriction diagrams [154], max-plus polyhedra [5], constraint matrix diagrams [88], and time-darts [111]; generally, the design of efficient data structures for symbolic exploration of timed automata is a field of active research.

## 7.3 Practical Efficiency

Symbolic, zone-based exploration of the (reachable) state-space of timed automata using the DBM data structure is key to their analysis. However, a number of additional algorithmic techniques have been developed for gaining efficiency in practice. In the following we indicate a number of these.

As described in Sect. 7.1, normalization of zones with respect to the maximum constant M appearing in the given timed automata ensures finiteness of the zone graph and hence termination of algorithms searching the zone graph. Here, a practical problem is that the normalization of a zone is in general not a zone itself, but rather a finite union of such. However, given a representation of the zone as a *shortest-path-closed* DBM, a syntactic *extrapolation* operation that removes bounds that are larger than the maximum constant may be easily performed: any upper bound constraint of the form  $x_i - x_j < k$  where k > Mis removed, and any lower bound of the form  $x_i - x_j > k$  where k < -Mis replaced by  $x_i - x_j > -M$ . Clearly, under extrapolation, only a finite number of DBMs will be encountered, ensuring termination. Furthermore, the correctness is based on the fact that extrapolation of a zone (based on its DBM representation) is included in its normalization, as shown in [29, 48].

Coarser, yet complete, notions of extrapolation have been obtained by performing the operation with respect to *clock- and location-dependent* maximum constants [29] and further differentiating the maximum constant used in upper or lower bound comparisons [30,31]. In fact, this last extrapolation yields performance comparable to that of the overapproximate *convex hull* abstraction [81].

Several of the algorithmic problems presented in this chapter—e.g., reachability, model checking, and equivalence checking, as well as notions of optimal reachability and controllability, which will be described in later sections have a fixed-point characterization. Though easy to implement, this leads to backwards iterative algorithms, requiring one to consider and classify states which are possibly not even reachable. Thus, for most problems, so-called *on-the-fly* algorithms have been devised, where the satisfaction of the given property by the initial state is attempted to be concluded in as *local* a fashion as possible, only exploring the state space when needed. For the analysis of timed-automata-based models, such on-the-fly algorithms have been proposed for instance for reachability [120, 157], liveness checking [147, 151], model checking with respect to TCTL [47], time-abstract bisimulation checking [149], and controller synthesis for timed game automata [69].

Despite the above efforts in applying aggressive (yet complete) abstractions, the analysis of timed-automata-based models suffers from the state-space explosion problem. Thus, complementary techniques have been proposed and implemented for reducing space consumption at the expense of time performance [35, 120]. Also, various AI-inspired techniques have been developed for *efficient guidance* of the symbolic exploration of timed automata towards specified error states [114–116]. Similarly, the technique of *symmetry reduction* has been developed and implemented for networks of timed automata with several symmetric components, potentially yielding an exponential gain in performance [96]. Moreover, so-called *time-convexity* analysis provides significant performance improvement [153].

Finally, several attempts have been made to extend the technique of *partial-order reduction* to networks of timed automata. In contrast to the proved effect in the finite-state setting, early attempts [37, 131] did not show any improvement in performance compared with regular symbolic exploration. In fact, being a strong synchronizer in a timed-automata network, time reduces the number of independent transitions, which are key for partial-order reduction to have effect. In later work [36, 125, 126], it was found that the union of all zones reached by different interleavings of the same set of transitions is convex, providing the basis of substantial improvement.

Also, bounded model-checking techniques have been developed for timed automata using *difference logics*, though with a limited performance improvement [76, 77].

## 7.4 Tools and Applications

Timed automata and their extensions have been applied to the modeling, analysis and optimization of numerous real-time applications. In this section we give a few examples, not aiming at being exhaustive but rather to illustrate the wide range of application domains.

A variety of mature tools are available which provide important computeraided support for applications. Well-known tools include UPPAAL [122], KRONOS [158], RED [155] and HyTech [99]. A larger number of other tools related to the analysis of timed automata have emerged over the years including Else [159], Rabbit [44], Verics [84], and TAME [22] as well as tools for analyzing other timed formalisms based on translation to timed automata including Times [21] (task automata), Moby [145] (PLC programs), SART [45] (Safety Critical Java), ART [93] (task graphs), Romeo [91] and TAPALL [68] (Time and Timed-arc Petri Nets), and VeSTA [112] (component integration checking).

The timed-automata formalism is now routinely applied to the modeling and analysis of real-time control programs, including a wide class of Programmable Logic Controller (PLC) control programs [85,127] and timing analysis and code generation of vehicle control software [150]. The timed-automata approach has also demonstrated its viability in the timing analysis of certain classes of asynchronous circuits [60].

Similarly, numerous real-time communication protocols have been analyzed using timed automata technology, often with inconsistencies being revealed: e.g., using real-time model checking, the cause of a ten-year-old bug in the IR-link protocol used by Bang & Olufsen was identified and corrected [95]. Most recently, real-time model checking has been applied to the clock synchronization algorithm currently used in a wireless sensor network that has been developed by the Dutch company CHESS [144]. Here it is shown that in certain cases a static, fully synchronized network may eventually become unsynchronized if the current algorithm is used, even in a setting with infinitesimal clock drifts.

During the last few years, timed automata modeling of multitasking applications running under real-time operating systems has received substantial research effort. Here the goals are multiple: to obtain less-pessimistic worst-case response time analysis compared with classical methods for single-processor systems [156]; to relax the constraints of period task arrival times of classical scheduling theory to task arrival patterns that can be described using timed automata [90]; to allow for schedulability analysis of tasks in terms of concurrent objects executing on multiprocessor or distributed platforms (e.g., MPSoC) [61, 80, 109].

Just as symbolic reachability checking of finite-state models has led to very efficient planning and scheduling algorithms, reachability checking for (priced) timed automata has demonstrated competitive and complementary performance with respect to classical approaches such as MIPL on optimal scheduling problems involving real-time constraints, e.g., job-shop and task-graph scheduling [1,32] and aircraft landing problems [119]. In fact a translation of the variant PDDL3 of PDDL (Planning Domain Definition Language) into priced timed automata has been made [86] allowing optimal planning questions to be answered by cost-optimal reachability checking. Industrial applications include planning a wafer scanner from the semiconductor industry [97] and computation of optimal paper paths for printers [108].

Most recently, computation of winning strategies for timed games has been applied to controller synthesis for embedded systems, including synthesis of most general non-preemptive online schedulers for real-time systems with sporadic tasks [6], synthesis of climate control for pig shed provided by the company Skov [110], and automatic synthesis of robust and near-optimal controllers for industrial hydraulic pumps [71].

## 8 Weighted Timed Automata

Time is not the only quantity one may want to measure when checking an embedded system: one may need to keep track of the battery charge or of the level of oil in a tank. Hybrid automata [98, 100] extend timed automata with extra variables that can help measure such quantities. Unfortunately, reachability is undecidable for these models, even with two-slope hybrid variables. Weighted timed automata [20, 33] is an intermediary model, extending timed automata with hybrid *observer* variables: these variables cannot appear in the guards of the automaton, but they can be used, for example, for optimization purposes. The special case where the observer is a stopwatch (computing the accumulated delay in some locations) was already introduced and solved in [11].

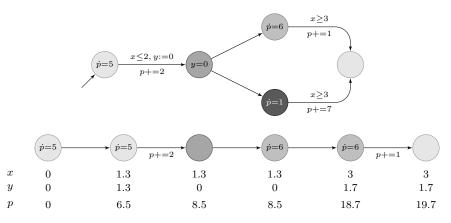

Formally, a weighted timed automaton is a pair (A, w) where A is a timed automaton and w labels the locations and edges of A with an integer (or a vector of integers for automata with multiple observer variables). For a transition t, w(t) is the value by which the value of the observer variable is increased, while for a location  $\ell$ ,  $w(\ell)$  is the rate by which the variable increases w.r.t. time (in other words, the observer variable p follows the differential equation  $dp/dt = w(\ell)$ ).

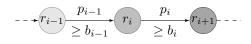

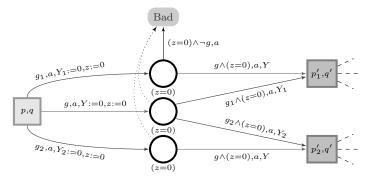

The semantics of a weighted timed automaton (A, w) is that of the underlying timed automaton A. Each run of A is decorated with the value of the observer variable. Figure 14 shows an example of a weighted timed automaton<sup>3</sup>, and a run of this automaton. This run reaches the rightmost location within 3 time units, and with a total weight of 19.7.