# IR Camera Validation of IGBT Junction Temperature Measurement via Peak Gate Current

Nick Baker, Laurent Dupont, Stig Munk-Nielsen, Francesco Iannuzzo, Marco Liserre

# ▶ To cite this version:

Nick Baker, Laurent Dupont, Stig Munk-Nielsen, Francesco Iannuzzo, Marco Liserre. IR Camera Validation of IGBT Junction Temperature Measurement via Peak Gate Current. IEEE Transactions on Power Electronics, 2017, 32 (4), pp.3099 - 3111. 10.1109/TPEL.2016.2573761. hal-01704618

HAL Id: hal-01704618

https://hal.science/hal-01704618

Submitted on 8 Feb 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# IR Camera Validation of IGBT Junction Temperature Measurement via Peak Gate Current

Nick Baker, Laurent Dupont, Stig Munk-Nielsen, Francesco Iannuzzo and Marco Liserre

Abstract—Infra-red measurements are used to assess the measurement accuracy of the Peak Gate Current (IGPeak) method for IGBT junction temperature measurement. Single IGBT chips with the gate pad in both the centre and the edge are investigated, along with paralleled chips, as well as chips suffering partial bond-wire lift-off. Results are also compared with a traditional electrical temperature measurement method: the voltage drop under low current  $(V_{CE(low)})$ . In all cases, the I<sub>GPeak</sub> method is found to provide a temperature slightly overestimating the temperature of the gate pad. Consequently, both the gate pad position and chip temperature distribution influence whether the measurement is representative of the mean junction temperature. These results remain consistent after chips are degraded through bondwire lift-off. In a paralleled IGBT configuration with non-negligible temperature disequilibrium between chips, the  $I_{GPeak}$  method delivers a measurement based on the average temperature of the gate pads.

Index Terms—Power semiconductor devices, insulated-gate bipolar-transistor (IGBT), temperature measurement.

#### I. INTRODUCTION

The junction temperature of a power semiconductor device is a key parameter that influences both performance and reliability. Knowledge of this temperature during operation could improve condition monitoring systems, and allow temperature based control algorithms that enhance module lifetime [1].

Real-time junction temperature measurement is however often difficult. Physical or contact measurement methods such as optical fibres, on-chip sensors, or infra-red cameras are expensive and require substantial modification to standard power module packaging. For these reasons, electrical measurement methods are often preferred. Using a Temperature Sensitive Electrical Parameter (TSEP), such as

Nick Baker, Stig Munk-Nielsen and Francesco Iannuzzo are at the Department of Energy Technology, Aalborg University, Denmark. (emails: <a href="mailto:nba@et.aau.dk">nba@et.aau.dk</a>, <a href="mailto:smm@et.aau.dk">smm@et.aau.dk</a>, <a href="mailto:smm@et.aau.dk">smm@et.aau.dk</a>, <a href="mailto:smm@et.aau.dk">smm@et.aau.dk</a>, <a href="mailto:smm@et.aau.dk">smm@et.aau.dk</a>, <a href="mailto:smm@et.aau.dk">smm@et.aau.dk</a>).

L. Dupont is with the Laboratory of New Technologies, French Institute of Science and Technology for Transport, Development and Networks, 78000 Versailles, France (e-mail: <a href="mailto:laurent.dupont@ifsttar.fr">laurent.dupont@ifsttar.fr</a>).

Marco Liserre is with the Chair of Power Electronics at Christian-Albrechts-University of Kiel, Germany. (email: <a href="mailto:ml@tf.uni-kiel.de">ml@tf.uni-kiel.de</a>).

the on-state voltage drop or threshold voltage, junction temperature measurements can be performed on standard power modules without modification to their structure [2]-[4].

Electrical methods for junction temperature measurement have been used for many decades on transistors, particularly for offline thermal characterisation of devices. Nevertheless, TSEP-based methods face many challenges in online implementation (i.e. during normal transistor operation) [4][5]. Issues regarding online TSEP usage generally involve the need to compensate for operating conditions other than temperature (such as load current), and the need for complex measurement circuitry or alteration to converter structure or control. Calibration procedures can also present substantial problems when self-heating compensation is required for higher current levels [6][7].

In the past two years, a significant number of proposals for online TSEP measurements have been presented [8]-[15]. This paper extends on the work displayed in [11] and [12], by providing a detailed evaluation on the accuracy of IGBT temperature measurement using the Peak Gate Current ( $I_{\rm GPeak}$ ). Although this method claims to resolve some of the TSEP implementation issues highlighted above, no validation is currently available regarding whether the measured temperature suitably represents the junction temperature in an operating IGBT.

Validating the accuracy of a TSEP is of fundamental importance if a TSEP is to be considered for real-world use, since a TSEP may not always provide accurate results. In fact, inconsistencies between different TSEP measurements have been found as far back as 1966 [16]. Since then, there is ample research to back up the assertion that TSEPs can deliver widely varying temperature measurements. A notable example is the  $V_{CE}$  at high current, which can give vastly erroneous temperatures due to the series resistance contribution of the packaging interconnections [7][17]. The discrepancies between different TSEPs may also change depending on the device and dissipation conditions [18]-[20]. Nevertheless, many recent TSEP proposals come with little or no validation (perhaps limited to one single chip) of the temperature provided.

As a result, this paper focuses on evaluating the accuracy of the  $I_{GPeak}$  method for IGBT junction temperature measurement. First of all, infra-red (IR) measurements are used to validate the  $I_{GPeak}$  method on two identically rated IGBTs with

differing geometry (shape and gate pad position). The IGBTs are also investigated in a paralleled configuration – both with and without large temperature disequilibrium between the paralleled IGBTs. Finally, since the electrical parameters of a device are prone to alter throughout its lifetime, a pertinent question is whether the accuracy of a TSEP method is resistant to these effects. To begin a preliminary assessment on this question, an IGBT is investigated both before and after several bondwires are disconnected from the die, which mimics one of the most common degradation mechanisms reported in prior literature.

All results obtained using the  $I_{GPeak}$  method are compared to measurements made using a conventional TSEP method, the voltage drop under low current injection ( $V_{CE(low)}$ ). This TSEP is selected for comparison with  $I_{GPeak}$  due to its widespread use and repeated evidence of correlation with mean junction temperature [7][18][21].

The paper will first provide a short description of the procedure for junction temperature measurement using both  $I_{GPeak}$  and  $V_{CE(low)}$ . Details will then be provided on the IGBT chips studied, and the methodology behind the IR measurements. The electrical test bench will also be described, which allows thermal measurements to be conducted on IGBTs operating under constant current injection. The results of each temperature measurement on the variety of IGBT configurations are then presented.

#### II. TSEP MEASUREMENTS

### A. Peak Gate Current - I<sub>GPeak</sub>

This measurement method relies on the temperature dependence of the internal gate resistance ( $R_{\text{Gint}}$ ), which is located in the IGBT chip itself. If the peak gate current and voltage swing of the gate driver are known, these values can be used to calculate a value for  $R_{\text{Gint}}$ . A detailed explanation of this method is provided in [11]; however the basic measurement principle will be outlined in the following paragraphs.

$I_{GPeak}$  is measured during the normal charging cycle of the gate terminal during turn-on. The time constant for the charging of the gate in a MOS-gated device before the threshold voltage is reached (i.e. during the turn-on delay) can be written as [22]:

$$R_G[C_{GS} + C_{GD}(V_{DS})] \tag{1}$$

where  $R_G$  is the gate resistance,  $C_{GS}$  is the gate-source capacitance (gate-emitter in IGBTs),  $C_{GD}$  is the gate-drain capacitance (gate-collector in IGBTs) and  $V_{DS}$  is the drain-source voltage (collector-emitter in IGBTs).

During the turn-on delay, the capacitance  $C_{GD}$  remains small and constant due to a high and unchanged value of  $V_{DS}$  [23][24]. Thus, if the parasitic gate inductance is kept negligible, the gate current during the turn-on delay can be viewed as a step response of a first order RC circuit where the initial (and peak) charging current into the gate capacitor can be calculated as:

$$I = \frac{V}{R}e^{-t/RC} \tag{2}$$

The peak current can therefore be approximated by using Ohm's Law,  $I \approx V/R$ ; where V is the voltage swing of the gate driver, and R is the total gate resistance.

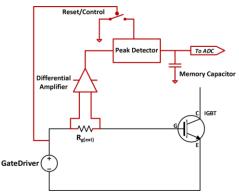

It is possible to monitor  $I_{GPeak}$  by measuring the peak value of the voltage across the external gate resistor, since this voltage is directly proportional to the gate current. A peak detector circuit is integrated into the gate driver and consists of a differential amplifier, a peak detector, a memory capacitor and a reset switch that is controlled by the gate voltage signal, as seen in Fig. 1.

Along with the output of the peak detector circuit  $(V_{Peakdetector})$ , the gate voltage just before turn-on is measured  $(V_{Gneg})$ , as well as the positive supply from the gate driver  $(V_{Gpos})$ . These three values are then used in (3) to calculate a value for  $R_{Gint}$ .

$$R_{Gint} = \frac{V_{Gpos} - V_{Gneg}}{\left(V_{peakdetector}/R_{Gext}\right)} - R_{Gext} \tag{3}$$

This paper uses a prototype measurement circuit previously detailed in [11]. High power verification of the measurement in the form of a double pulse test, along with discussion of several implementation issues can be found in [11]. This paper however focuses on evaluating the fundamental accuracy of the  $I_{\text{GPeak}}$  method; therefore, implementation issues relating to real-world use in commercial converters will not be extensively discussed.

Fig. 1. Peak Detector Schematic to detect peak voltage over the external

# B. Forward Voltage under Low Current Injection – $V_{CE(low)}$

The  $V_{CE(low)}$  has been used for the thermal characterisation of bipolar transistors for many decades [3][16][21][25]. By taking advantage of the temperature dependence of the voltage drop across a PN junction, this parameter generally exhibits a negative temperature dependence of approximately -2mV/°C in silicon devices.

The measurement process is very simple: a constant sensing current generally in the range of 1mA - 100mA is fed into the power device, and the subsequent voltage drop is measured. Typically, the sensing current is injected into the device after a

sufficient delay (up to a few hundred µs) once the load current has been removed in order to be sure that excess carriers are completely swept away or recombined. Since the sense current induces negligible self-heating, the voltage drop can be recorded as the device is cooling and a linear regression vs. the square root of time used to estimate the temperature value at the moment the load current is switched off [3][21].

Although the  $V_{CE(low)}$  has been experimentally validated in numerous studies and shown to provide a temperature close to the mean temperature of the chip [7][18][21], it is problematic to implement in real switching conditions due to requiring a suitable window to inject the sensing current [26][27]. Nevertheless, its traditional use and repeated evidence of correlation with mean junction temperature is why the method is chosen as the current state-of-the-art for comparison with the recently proposed  $I_{GPeak}$  method.

#### III. TSEP MEASUREMENTS

#### A. IGBTs under test

Two Infineon IGBTs are chosen for investigation, both rated at 1200V/200A. Additionally, each IGBT contains an  $R_{\text{Gint}}$  of  $3.5\Omega$ . Although these IGBTs have identical specifications, the geometry of the chips is dissimilar and is the primary reason for their selection.

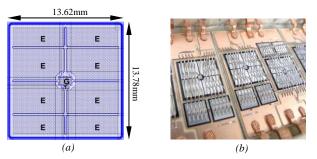

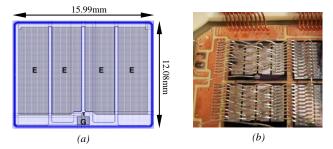

The first IGBT (Die: *IGC189T120T8RL* [28], Module: *FS200R12PT4*) is square in profile with the gate pad in the centre, while the second IGBT (Die: *IGC193T120T8RM* [29], Module: *FF600R12ME4*) has a rectangular profile with the gate pad at the side. The geometry and dimensions of the dies are shown in Fig. 2 and Fig. 3. These IGBTs will subsequently be referred to as Type A and Type B respectively.

Because functional dies complete with bondwires and packaging could not be obtained individually, the experiments are performed on individual dies isolated from inside commercial multi-chip power modules. The module layout for IGBT A (square, gate pad centre) also allowed investigation of two IGBTs in parallel. In addition, IGBT A is investigated both with and without bond-wire removal.

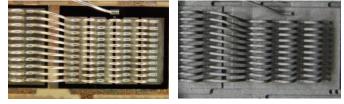

#### B. IR Thermal Measurements

To prepare the power modules for IR measurements, the dielectric gel was first removed by soaking for several hours in Ardrox 2312 at 75°C. The modules were then cleaned with Acetone and deionised water, before being painted with PYROMARK 1200 high temperature paint. Care was taken during the painting process to achieve as consistent emissivity as possible across the chip surface: the paint was filtered to attain a uniform particle size, and micro-spraying equipment was used that allowed tight control over the paint thickness. Before and after painting photos of IGBT B are shown in Fig. 4.

The thickness of the paint was selected as a trade-off between achieving uniform emissivity, while minimising the impact on the thermal behaviour of the IGBTs. The paint thickness in all cases is between  $10\text{-}16\mu\text{m}$ , compared to the  $115\text{-}120\mu\text{m}$  thickness of the IGBT dies.

The IR camera used is a CEDIP-FLIR SC7500. For each measurement, 100 IR frames (100Hz frequency) are acquired while the IGBTs conduct a constant current in a thermal steady-state. To fix identical positioning for each image acquisition, the position of the camera was controlled by a 3-axis positioning system.

Fig. 2. IGBT A:

- (a) Geometry of Infineon IGC189T120T8RL bare die.

- (b) Dies inside FS200R12PT4 module after dielectric gel is removed.

Fig. 3. IGBT B:

- (a) Geometry of Infineon IGC193T120T8RM bare die.

- (b) Dies inside FF600R12ME4 module after dielectric gel is removed.

Fig. 4. IGBT B before painting (left) and after painting (right).

# C. Test Bench Operation

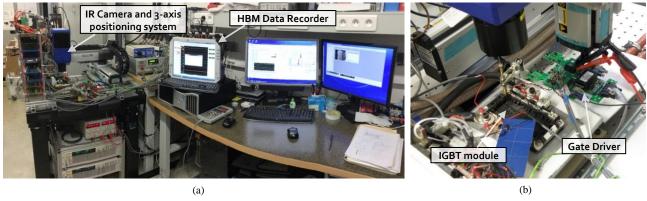

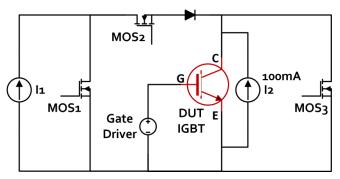

A panoramic view of the test bench, along with a close up of the IR camera, power module and gate driver with the  $I_{GPeak}$  measurement circuit is shown in Fig. 5. A schematic of the test setup is displayed in Fig. 6, which allowed the TSEPs to be evaluated with IGBTs operating under constant current injection. The operating principle is described below, with the basic premise being a two stage operation: a heating phase and a measurement phase.

The first step is the heating step, where a high current is fed into the DUT IGBT from the current source I1. This induces self-heating in the device, which can last for several minutes until a thermal steady-state is reached. The second step is the measurement step. At this point, the IGBT temperature is measured using the three presented measurement methods: IR camera,  $V_{\text{CE(low)}}$  and  $I_{\text{GPeak}}$ .

Fig. 5. (a) Panoramic view of test bench (b) Close up of power module, IR Camera, and gate driver with peak detector measurement circuit [11]

Fig. 6. Test Bench Schematic

All electrical measurements are performed using a HBM Gen3i data recorder. To measure  $I_{GPeak}$ , the peak detector prototype described in [11] is used, and the circuit output along with the gate voltage is sampled at 100MS/s (14-bit resolution). The  $V_{CE}$  of the DUT IGBT is recorded at 2MS/s (16-bit resolution).

It is clear that both  $V_{CE(low)}$  and  $I_{GPeak}$  cannot be performed while conducting the full dissipation current:  $V_{CE(low)}$  requires a low sensing current of 100mA and  $I_{GPeak}$  must be recorded during an IGBT turn-on. Therefore, synchronisation of MOSFETs MOS1, MOS2, MOS3, and current source I2 are used in order to facilitate these measurements.

The current source I2 is fixed at 100mA and provides the sensing current to perform a temperature measurement using  $V_{\rm CE(low)}$ . MOS1 and MOS2 on the other hand are used to control the injection of the high heating current into the IGBT. MOS3 is used to force a zero collector-emitter voltage during measurement of  $I_{\rm GPeak}$ .

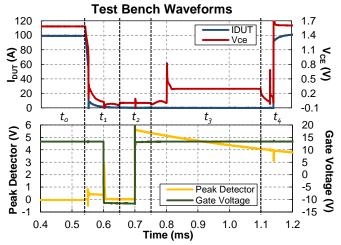

The general procedure is as follows and depicted in Fig. 7. First of all,  $t_0$  depicts the end of the heating phase which may have been ongoing for several minutes previously, with the DUT IGBT conducting a high current. In this phase, the temperature evolution of the IGBT is monitored using the IR camera. Once a thermal steady-state is reached, 100 IR images are sampled at 100Hz. Following this,  $t_1$  commences with  $I_{DUT}$  redirected into MOS1, and the DUT IGBT switched off – a transition that lasts 100 $\mu$ s in total. In  $t_2$ , MOS3 is closed to short the collector and emitter of the DUT IGBT. This fixes the  $V_{CE}$  at 0V and is vital to ensure a stable  $C_G$  for the  $I_{GPeak}$  measurement [11]. The IGBT is turned on again and a measurement of  $I_{GPeak}$  occurs using the peak detector circuit.

In total,  $I_{GPeak}$  is measured 200 $\mu$ s after the heating current is removed. The negative gate voltage and the positive voltage supply of the gate driver are sampled 500ns before turn-on, while the output of the peak detector is recorded  $1\mu$ s after turn-on.

Now that the  $I_{GPeak}$  measurement is completed, MOS3 is opened and a 100mA sensing current (I2) is injected into the DUT IGBT during t3. The  $V_{CE(low)}$  is recorded for a period of 250µs, and a linear regression vs. the square root of time is used to estimate the  $V_{CE(low)}$  at the instant the load current is removed the DUT IGBT [3]. Finally, the original IDUT is returned to the DUT IGBT in t4.

This procedure is repeated 10 times and the mean value of these measurements is used for analysis. For calibration of  $V_{\text{CE(low)}}$  and  $I_{\text{GPeak}}$ , the cooling fluid to the IGBT heatsink is varied from 40°C to 180°C, and the procedure described above is performed with  $I_{\text{DUT}}$  set to 0A. A type-K open thermocouple is placed on the copper base of the power module and used as the reference temperature during the calibration procedure.

Fig. 7. Synchronisation of Electrical Measurements

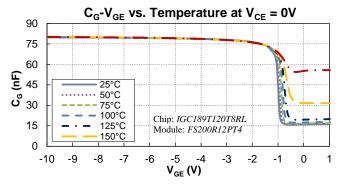

### *D.* Gate Capacitance Stability at $V_{CE} = 0V$

Although the measurement of  $I_{GPeak}$  is conducted at a constant  $V_{CE}$ , previous assumptions have stipulated that a *high*  $V_{CE}$  is also required for  $C_G$  to be stable [11][23]. Since  $I_{GPeak}$  is measured at a  $V_{CE}$  of 0V in these experiments, a short validation of the stability of  $C_G$  in this condition was

conducted. Fig. 8 displays a  $C_{\text{GE}}$ - $V_{\text{GE}}$  profile vs. temperature on IGBT A with the collector-emitter shorted (i.e. the same conditions for  $I_{\text{GPeak}}$  measurement in the test bench).

Fig. 8. C<sub>G</sub>-V<sub>GE</sub> vs. temperature profile for IGBT A (Infineon FS200R12PT4)

The profile shows that  $C_{GE}$  is around 80nF and stable with temperature while  $V_{GE}$  remains below approximately -1V. Given that the Concept2 gate driver used in the peak detector prototype has a negative turn-off voltage of -10V [30],  $I_{GPeak}$  should be detected well before the voltage on the gate capacitor reaches -1V. Therefore, the fluctuation of  $C_{GE}$  with temperature at a  $V_{GE}$  beyond -1V should not impact the measurement of  $I_{GPeak}$ . For the experiments conducted in this paper, a unipolar gate driver with a turn-off voltage of 0V (or within temperature dependent region of Fig. 8) would yield fallacious results.

#### IV. RESULTS

In the following sections, all raw data values for the dissipation results are included in the tables in Appendix A.

# A. Definition of 'Junction Temperature'

The term 'junction temperature' is ambiguous, since the temperature of a power semiconductor cannot be described using a single temperature value. Instead, the junction is made up of a large distribution of temperatures. In prior literature concerning the evaluation of TSEP accuracy, the mean surface temperature and the absolute maximum temperature of the chip are the two most common measurements chosen for comparison with the TSEP measurement. In this work, the 'junction temperature' is assumed to be the mean surface temperature of the emitter metallisation on the IGBT die. These emitter pads can be seen in the die datasheets [28][29] and in Figs. 2 and 3. As a result, the 'junction temperature' does not include the entirety of the die area, or any of the attached bondwires.

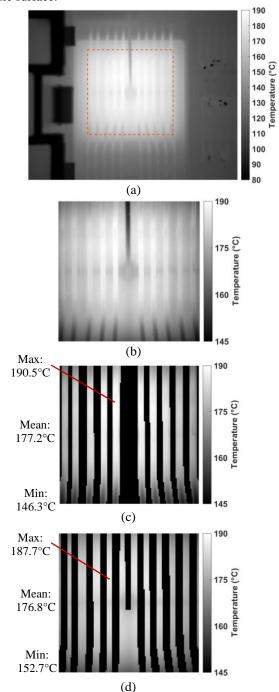

To extract the mean surface temperature of the emitter pads, the IR images are processed using image masks in MATLAB to remove the undesired pixels. This process is depicted in Fig. 9.

A noteworthy observation from this procedure is that the bondwires experience a wider temperature distribution than the die. From Fig. 9, where IGBT A is conducting 140A, it can be seen that the bondwires have both a lesser minimum and a higher maximum temperature. The maximum temperature of the bondwires is close to 3°C higher than the

die, while the minimum is more than  $6^{\circ}$ C lower. Nonetheless, the overall mean temperature of both structures is similar, with the mean temperature of the bondwires just  $0.4^{\circ}$ C higher than the die surface.

Fig. 9. Processing of IR images to extract the junction temperature:

- (a) Unedited IR image of IGBT A during dissipation at 140A

- (b) Cropped IR image to the active area of the die

- (c) IR image of bondwires with die surface removed via a MATLAB image mask

- (d) IR image of die surface with bondwires removed via a MATLAB image mask. This image is used to calculate the mean junction temperature.

#### B. Location of $R_{Gint}$

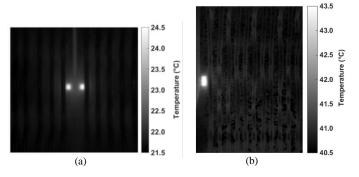

The IR camera was used to perform a preliminary assessment on the location of the internal gate resistor for each

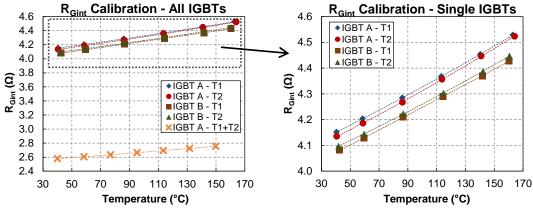

Fig. 11:  $R_{Gint}$  vs. Temperature from calibration data for IGBT A and B ( $I_{GPeak}$  used to calculate  $R_{Gint}$ )

IGBT. To do this, IGBTs were shorted between the collector and emitter, and switched using a gate driver at a frequency of 30kHz. Fig. 10 displays thermal images of the IGBTs during this procedure. Clear heating in the gate pad of around 3°C can be seen on both IGBTs, which is assumed to be the result of the self-heating of R<sub>Gint</sub>.

As a result, image masks were created in MATLAB to extract both the mean surface temperature of the emitter metallisation on the IGBT die ( $IR_{Mean}$ ), as well as the mean temperature of the gate pad ( $IR_{Gate}$ ).

Fig. 10. Self-heating of R<sub>Gint</sub>: (a) IGBT A. (b) IGBT B.

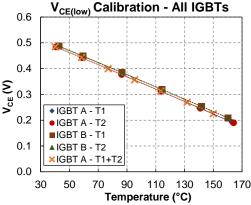

#### C. Calibration

Two IGBTs are characterised from each module. In addition, the layout of the FS200R12PT4 module allowed IGBT A to be calibrated with two IGBTs in parallel. In this case, the sensing current for  $V_{\rm CE(low)}$  was accordingly doubled from 100mA to 200mA, while the gate driver remained unchanged.

Calibration curves for the two TSEP measurement methods are shown in Figs. 11 and 12.  $I_{GPeak}$  is used in conjunction with the gate voltage swing to calculate  $R_{Gint}$ , as specified in (3). Although both  $R_{Gint}$  and  $V_{CE(low)}$  display a near linear relationship with temperature, a 2nd order polynomial fit is in fact used to calculate their respective relationships for when the TSEPs are used during dissipation.

For the traditional  $V_{\text{CE(low)}}$ , the calibration reveals very little variance between the chips. The temperature sensitivity is approximately -2.4mV/°C, with only a small offset between IGBT A and B of around 6mV. Furthermore, the two paralleled chips of IGBT A displayed precisely the same  $V_{\text{CE(low)}}$  as when they were calibrated individually.

On the other hand,  $R_{Gint}$  has significant variation between IGBTs in spite of each chip having a specified datasheet value of  $3.5\Omega.$  Within chips from the same module, sensitivity was fairly uniform:  $3.2m\Omega/^{\circ}C$  for IGBT A and  $2.9m\Omega/^{\circ}C$  for IGBT B. However, an offset of approximately  $20\text{-}30m\Omega$  is present between T1 and T2 for both IGBT types. Furthermore, there is a discrepancy of around  $50m\Omega$  between IGBT A and B. This offset could be due to manufacturing tolerances in the production of  $R_{Gint}.$  For the paralleled chips of IGBT A, the sensitivity was halved to  $1.6m\Omega/^{\circ}C.$

Fig. 12:  $V_{\text{CE(low)}}$  vs. Temperature from calibration data for IGBT A and B

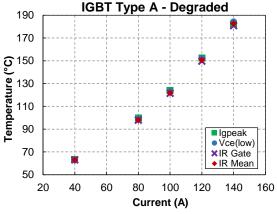

### D. Dissipation Results - Single IGBTs

Temperature measurements during dissipation were conducted at a range of current values from 40-160A. The heating current was limited to below the 200A rating of each IGBT in order to maintain a safe maximum junction temperature of below 200°C. The input fluid to the heatsink was maintained at 40°C during all tests.

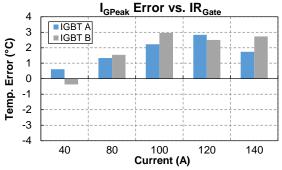

Fig. 13 displays the temperature measurement results during dissipation on a single IGBT of both Type A and B. Temperature measurements via  $I_{GPeak}$  and  $V_{CE(low)}$  are displayed, along with IR measurements regarding the mean surface temperature of the die (IR<sub>Mean</sub>) and gate pad (IR<sub>Gate</sub>).

For IGBT A (square, gate pad centre), all temperature measurements appear to match closely. On the other hand, the 4 temperature measurement methods show clear divergence on IGBT B – particularly at high current levels. In IGBT B,  $I_{\rm GPeak}$  clearly underestimates the mean surface temperature and

provides a temperature that is lower than measured via  $V_{\text{CE(low)}}$ .

Fig. 13: Temperature measurement results during dissipation from 40A to 160A. (a) IGBT A. (b) IGBT B.

To demonstrate these trends more precisely, Fig. 14 compares both TSEP measurements in relation to  $IR_{Mean}$  for each IGBT. It can be observed that in all cases,  $V_{CE(low)}$  provides a temperature that slightly overestimates the mean surface temperature of the die. The difference between the  $V_{CElow}$  and  $IR_{Mean}$  remains strictly lower than +2°C. These results are in accordance with several previous studies [18][21].

The slight overestimation of the mean temperature may be a consequence of the temperature gradient across the chip during dissipation, which is a contrast to the homogenous temperature during calibration. Due to the negative temperature coefficient of  $V_{\text{CE(low)}}$ , the central and hotter parts of the chip experience an increased current density compared to the colder outer parts of the chip. As the entire current in the chip must equal the total sense current of 100mA, these hotter areas subsequently contribute a larger weighting in the composition of  $V_{\text{CE(low)}}$ .

Meanwhile,  $I_{GPeak}$  provided a temperature that differed in comparison to  $IR_{Mean}$  depending on the chip type. For IGBT A, with a centrally located gate pad, Fig. 14 shows that  $I_{GPeak}$  obtained a temperature that was higher than the mean surface temperature by between 1 and 4°C. These results are

comparable to those obtained via  $V_{CE(low)}$ . Conversely, for IGBT B,  $I_{GPeak}$  always delivered a temperature lower than IR<sub>Mean</sub>. At lower current levels, this underestimation was not severe at around -2°C. However, this increased to -7.6°C and -10.9°C at higher current (and temperature) levels.

Fig. 13: Measurement error vs. mean surface temperature for (a)  $I_{\text{GPeak}}$  and (b)  $V_{\text{CE(low)}}.$

These trends could perhaps be anticipated due to the respective locations of the gate pad. In fact, Fig. 15 shows the correlation of temperature measurement via  $I_{GPeak}$  to the temperature of the gate pad measured via IR camera. In almost all cases on both chip types,  $I_{GPeak}$  provided a temperature within  $+1^{\circ}C$  and  $+3^{\circ}C$  of the gate pad.

Fig. 15: Temperature measurement via  $I_{\text{GPeak}}$ : error vs. gate pad temperature.

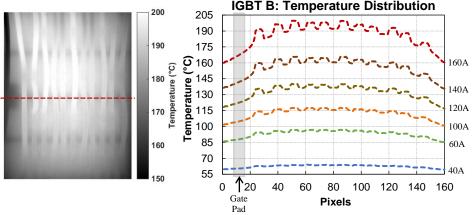

A gate pad at the side experiences a comparatively lower temperature than one in the centre due to the temperature gradient across the chip during dissipation. These temperature gradients generally become more significant at higher mean temperatures. This is shown in Fig. 16, which displays the temperature profile across IGBT B at all investigated current levels. This is therefore an explanation for why  $I_{GPeak}$  still delivered a reasonable approximation of  $IR_{Mean}$  (within -2°C) on IGBT B up to 100A dissipation current, while severely

Fig. 16: Temperature profile across IGBT B from 40A to 160A. Temperature is plotted along the dotted line

underestimating  $IR_{\text{Mean}}$  as the current and temperature increased.

These results infer that use of  $I_{GPeak}$  for junction temperature measurement on single IGBTs would require consideration of the gate pad position, as well as the expected operating temperatures and temperature distribution throughout the chip.

The fact that the I<sub>GPeak</sub> method consistently measures a slight overestimation of the gate pad temperature could indicate a systematic error in the experiment. This may be due to a suboptimal design of the peak detector circuit, or a systematic error in the measurement principle. For example, the gate connection in the IGBTs studied is not a kelvin connection. Therefore, the collector current and the gate current must share the same path (including bondwires), which could produce a discrepancy between the calibration conditions with 0A load current, and the dissipation conditions with a high heating current.

# E. Dissipation Results: Degraded Single IGBT with Partial Bondwire Removal

To begin an assessment on the robustness of the  $I_{GPeak}$  method, temperature measurements were performed on a degraded IGBT suffering bondwire lift-off. The bondwire lift-off mechanism was selected for two reasons. Firstly, it is one of the most common degradation mechanisms written about in academic literature, and secondly it is easy to emulate without requiring removal of the power modules from the test setup. In this manner, the  $I_{GPeak}$  method can be assessed in precisely the same conditions for both the healthy and degraded states.

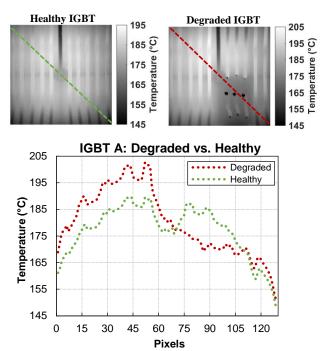

To achieve the degraded condition, 3 bondwires on IGBT A were cut with wire clippers, resulting in the complete disconnection of a central emitter pad on the IGBT. An IR image of this condition at 140A is displayed in Fig. 17, from which, clear distortion of the temperature distribution can be seen in comparison to the healthy IGBT. Mean and maximum temperatures of the IGBT are around 5-10°C higher after bondwire removal.

Temperature measurements on the degraded IGBT A are shown in Fig. 18. The results appear similar to the findings of IGBT A in a healthy condition (Fig. 13) – all temperature measurements match closely.

Fig. 17: Comparison of IGBT A temperature profile at 140A before and after bondwire removal. Temperature is displayed along diagonal lines

Fig. 18: Temperature measurement results during dissipation on IGBT A with bondwires removed.

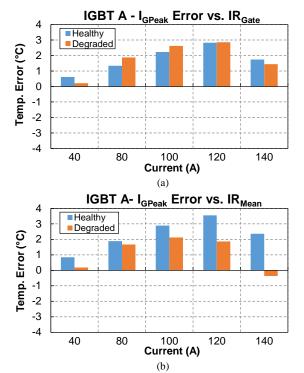

For further analysis, Fig. 19 is presented and displays a comparison of  $I_{GPeak}$  in relation to  $IR_{Mean}$  and  $IR_{Gate}$ , both before and after degradation. The correlation between  $I_{GPeak}$

and  $IR_{Gate}$  remains almost unchanged between healthy and degraded conditions. However, a non-negligible shift can be seen when comparing  $I_{GPeak}$  to  $IR_{Mean}$ . In a healthy state,  $I_{GPeak}$  typically delivered a temperature between 2-3°C larger than the mean junction temperature. After bondwire removal, this overestimation reduced by 1°C to 2°C. In fact, a -0.4°C underestimation of  $IR_{Mean}$  was observed at the highest heating current of 140A. Although this adjustment may seem small, it is in clear contrast to  $V_{CE(low)}$ , whose correlation with  $IR_{Mean}$  altered less than  $\pm 0.2$ °C in all cases, as shown in Fig. 20.

Fig. 19: Temperature measurement via  $I_{\text{GPeak}}$  in degraded and healthy conditions: (a) Error vs. gate pad temperature. (b) Error vs. mean surface temperature.

Fig. 20: Temperature measurement via  $V_{\text{CE(low)}}$ : error vs. mean surface temperature in healthy and degraded condition

These results again infer that  $I_{GPeak}$  is primarily influenced by local conditions in the vicinity of the gate pad, rather than the overall active area of the die as is the case with the traditional  $V_{CE(low)}$ .

It is perhaps logical that  $I_{GPeak}$  was found to be largely unaffected by bondwire lift-off, since the emitter bondwires may contribute a total resistance of just a few m $\Omega$ , as opposed to the 3.5 $\Omega$  of  $R_{Gint}$ . Additionally, since the parasitic gate

inductance is mainly comprised of the terminal leads and packaging, the lift-off of just a few bondwires cannot significantly change the total inductance in the circuit [31].

It must also be noted that merely cutting three bondwires on an IGBT is not a realistic representation of a degraded condition. In practical applications an IGBT can be subject to a wide variety of failure mechanisms, some of which may be far more pertinent in influencing the I<sub>GPeak</sub> method. To provide more thorough assessment on the robustness of I<sub>GPeak</sub>, an investigation on IGBTs with a degraded gate oxide or gate capacitance would be relevant, especially as there is data to suggest that IGBT gate capacitances can vary through aging [101][102].

# F. Dissipation Results: Paralleled IGBTs

The module structure for IGBT A allowed investigation of two IGBTs in parallel. For paralleled IGBTs, the heating current ranged from 120A to 240A, and the sense current for  $V_{\text{CE(low)}}$  was accordingly doubled from 100mA to 200mA. The gate driver and peak detector were unchanged from previous investigations, with a single gate driver being used to drive both IGBTs.

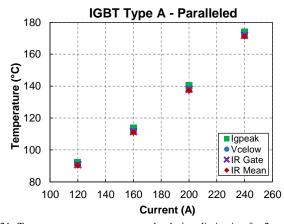

First of all, the paralleled IGBTs were assessed without inducing a temperature imbalance. In this condition, the temperature difference between the mean surface temperatures of each IGBT was a maximum of  $2^{\circ}$ C. Temperature measurements in this paralleled state are displayed in Fig. 21. Since the temperature difference between the two IGBTs is minimal, single IR measurements are displayed which is the cumulative mean of both IGBTs (i.e.  $IR_{Mean-T1}+IR_{Mean-T2}$ ).

Fig. 21: Temperature measurement results during dissipation for 2 paralleled IGBTs (IGBT A) from 120A-240A.

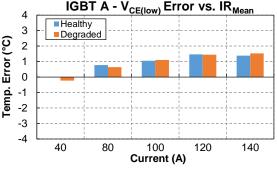

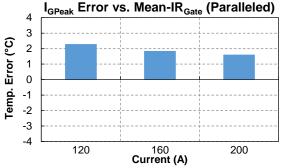

The results on IGBT A in a paralleled configuration follow the same trends as with single IGBTs. Fig. 22 shows that  $I_{GPeak}$  delivers a temperature within +2°C of the gate pad temperature. This leads to an overestimation of  $IR_{Mean}$  by between +1°C and +3°C. Additionally,  $V_{CE(low)}$  again provides a temperature closely correlated with the mean surface temperature, with measurements at all current levels showing a difference of less than +1°C.

Fig. 22: Temperature measurement error for 2 paralleled IGBTs (IGBT A), (a)  $I_{\text{GPeak}}$  error vs. gate pad temperature. (b)  $I_{\text{GPeak}}$  and  $V_{\text{CE(low)}}$  errors vs. mean surface temperature.

# G. Dissipation Results: Paralleled IGBTs with Temperature Disequilibrium

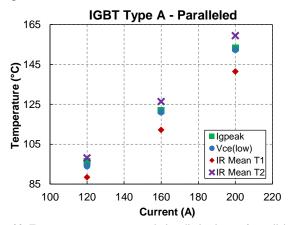

A more interesting scenario is to examine the TSEP methods on paralleled IGBTs that have a large temperature imbalance. To achieve this, the connection from the heatsink to the baseplate was loosened on one side of the power module so that one IGBT suffered a deteriorated thermal contact. The IGBTs were then examined with a heating current of up to 200A, where the temperature disequilibrium between the two IGBTs reached close to 20°C.

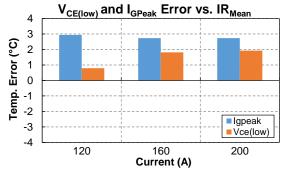

Fig. 23 displays the temperature measurement results with this thermal imbalance. In this figure, the mean surface temperature measured via IR camera is included for both IGBTs. It can be seen that both I $_{\rm GPeak}$  and  $V_{\rm CE(low)}$  provide a temperature in between the IR $_{\rm Mean}$  of IGBT 1 and IGBT 2.

Fig. 23: Temperature measurements during dissipation on 2 paralleled IGBTs (IGBT A) with a temperature disequilibrium.

Fig. 24: I<sub>GPeak</sub> on 2 paralleled IGBTs (IGBT A) with a temperature disequilibrium: error vs. cumulative mean of gate pad temperature.

I<sub>GPeak</sub> delivers a temperature within +2°C of the cumulative mean temperature of the gate pad, as shown in Fig. 24.

The temperature profile of the two IGBTs with a 200A heating current is shown in Fig. 25. Here, the  $I_{GPeak}$  and  $V_{CE(low)}$  measurements are within 1°C of each other and appear to correspond closely with the combined mean temperature profile of the two IGBTs. In fact, both TSEP measurements overestimate the cumulative mean surface temperature by between +1°C and +3°C, as shown in Fig. 26.

Fig. 25: Temperature profile of 2 paralleled IGBTs (IGBT A) with 200A heating current. Temperature is plotted along diagonal lines.

Fig. 26:  $I_{\text{GPeak}}$  and  $V_{\text{CE(low)}}$  on 2 paralleled IGBTs (IGBT A): error vs. cumulative mean surface temperature.

These results suggest that  $I_{GPeak}$  can provide an adequate assessment of the mean temperature of IGBT chips in a paralleled condition, at the least in line with results provided by the traditionally used  $V_{CE(low)}$ . This is providing that the IGBTs contain a centrally located gate pad.

For a more detailed assessment on the performance of  $I_{GPeak}$  with paralleled chips, a number of additional studies could be carried out. Clearly, immediate steps would be to assess  $I_{GPeak}$  on a greater number than two IGBTs in parallel, as well as on paralleled IGBTs with the gate pad at the edge of the die. Other relevant studies would be to investigate the impact different paralleling layout techniques such as grouping IGBTs into 'cells' [32].

#### v. Conclusion

This paper uses infra-red measurements to experimentally evaluate the accuracy of the Peak Gate Current ( $I_{GPeak}$ ) method for IGBT junction temperature measurement. The accuracy of  $I_{GPeak}$  is compared to a traditional electrical temperature measurement method, the voltage drop at low current ( $V_{CE(low)}$ ). The investigation is performed with IGBTs operating under constant current injection and temperature measurements are taken while the IGBT is in a thermal steady-state.

The  $I_{GPeak}$  method is found to correlate closely with the temperature conditions in the vicinity of the gate pad. This is in contrast to the  $V_{CE(low)}$ , which is influenced by the entire area of the die. As a result,  $I_{GPeak}$  provided a slight overestimation of the mean surface temperature of the die in IGBTs with a centrally located gate pad, while underestimating the mean surface temperature in IGBTs with a gate pad located at the side. These trends became more pronounced as the overall temperature of the dies increased, as a result of more pronounced temperature gradients.

The  $I_{GPeak}$  method is found to be largely unaffected by partial bondwire lift-off, which is a common degradation mechanism in IGBTs. In this respect, the  $I_{GPeak}$  method continued to provide a temperature associated with the gate pad temperature when the IGBT was in a degraded condition. However, since the temperature distribution in the die was modified due to this degradation, the correlation with the mean surface temperature was slightly altered.

In paralleled IGBTs where the gate pad is centrally located,  $I_{\rm GPeak}$  was found to have similar averaging properties as the traditional  $V_{\rm CE(low)}$  method, and provided a temperature slightly overestimating the cumulative mean temperature when a large temperature imbalance is present between the IGBTs.

As a general conclusion, using and interpreting measurement results provided by  $I_{GPeak}$  requires a good knowledge of the gate pad position, as well as likely operating temperatures and the temperature gradient in the chip.

Future work should primarily involve extending the validation to real functional conditions that are not experienced during constant current injection, and to a statistically significant number of IGBTs with differing power ratings and manufacturer. An assessment of the  $I_{\text{GPeak}}$  method

tracking fast dynamic changes in temperature should also be a priority. Finally, an evaluation of robustness towards gate oxide degradation introducing non-negligible gate leakage currents should also be carried out.

#### VI. APPENDIX A

Complete table of temperature measurement results from experiments performed.

IGBT A - Healthy

| Current | Current I <sub>GPeak</sub> |       | IR <sub>Gate</sub> | IR <sub>Mean</sub> | IR <sub>Max</sub> |  |  |

|---------|----------------------------|-------|--------------------|--------------------|-------------------|--|--|

| (A)     | (°C)                       | (°C)  | (° <b>C</b> )      | (°C)               | (°C)              |  |  |

| 0       | 42.1                       | 42.0  | 41.7               | 41.8               | 42.1              |  |  |

| 40      | 63.9                       | 63.0  | 63.3               | 63.1               | 65.3              |  |  |

| 80      | 98.7                       | 97.6  | 97.4               | 96.8               | 102.1             |  |  |

| 100     | 122.3                      | 120.5 | 120.1              | 119.4              | 126.7             |  |  |

| 120     | 150.1                      | 148.0 | 147.2              | 146.5              | 156.5             |  |  |

| 140     | 179.2                      | 178.2 | 177.5              | 176.9              | 190.5             |  |  |

IGBT A - Degraded

| Current I <sub>GPeak</sub> |       | V <sub>CE(low)</sub> | IR <sub>Gate</sub> | IR <sub>Mean</sub> | IR <sub>Max</sub> |  |

|----------------------------|-------|----------------------|--------------------|--------------------|-------------------|--|

| (A)                        | (°C)  | (°C)                 | (°C)               | (° <b>C</b> )      | (°C)              |  |

| 0                          | 40.9  | 40.5                 | 40.8               | 40.9               | 41.3              |  |

| 40                         | 63.1  | 62.7                 | 62.9               | 63.0               | 65.8              |  |

| 80                         | 99.6  | 98.6                 | 97.7               | 98.0               | 105.1             |  |

| 100                        | 123.9 | 122.9                | 121.3              | 121.8              | 132.2             |  |

| 120                        | 152.5 | 152.1                | 149.6              | 150.6              | 165.3             |  |

| 140                        | 182.1 | 184.0                | 180.7              | 182.5              | 203.1             |  |

IGBT B

| Current | $I_{GPeak}$ | $V_{CE(low)}$ | IR <sub>Gate</sub> | $IR_{Mean}$ | $IR_{Max}$ |

|---------|-------------|---------------|--------------------|-------------|------------|

| (A)     | (°C)        | (°C)          | (°C)               | (°C)        | (°C)       |

| 0       | 41.8        | 41.6          | 41.5               | 41.6        | 41.8       |

| 40      | 60.6        | 62.4          | 60.9               | 62.2        | 64.3       |

| 80      | 90.8        | 93.5          | 89.2               | 92.7        | 97.6       |

| 100     | 109.5       | 112.7         | 106.6              | 111.7       | 118.4      |

| 120     | 127.4       | 133.2         | 124.9              | 132.1       | 140.7      |

| 140     | 147.6       | 156.4         | 144.9              | 155.3       | 166.5      |

| 160     | 175.0       | 186.5         | 171.3              | 186.0       | 201.5      |

IGBT A - 2x Paralleled without Temperature Disequilibrium

| Current | $I_{GPeak}$   | $V_{CE(low)}$ | $IR_{Gate}$ | $IR_{Gate}$ | IR <sub>Mean</sub> | IR <sub>Mean</sub> |

|---------|---------------|---------------|-------------|-------------|--------------------|--------------------|

| (A)     | (° <b>C</b> ) | (° <b>C</b> ) | T1 (°C)     | T2 (°C)     | T1 (°C)            | T2 (°C)            |

| 120     | 92.2          | 90.6          | 90.7        | 90.8        | 90.3               | 90.4               |

| 160     | 113.7         | 111.6         | 110.5       | 112.6       | 110.0              | 111.9              |

| 200     | 140.3         | 138.1         | 136.7       | 139.5       | 135.7              | 138.6              |

| 240     | 173.9         | 171.7         | 171.0       | 172.6       | 170.1              | 172.2              |

IGBT A - 2x Paralleled with Temperature Disequilibrium

|   | Current | $I_{GPeak}$ | $V_{CE(low)}$ | IR <sub>Gate</sub> | IR <sub>Gate</sub> | $IR_{Mean}$ | IR <sub>Mean</sub> |

|---|---------|-------------|---------------|--------------------|--------------------|-------------|--------------------|

|   | (A)     | (°C)        | (°C)          | T1 (°C)            | T2 (°C)            | T1 (°C)     | T2 (°C)            |

| _ | 120     | 96.2        | 94.1          | 89.2               | 98.6               | 88.4        | 98.1               |

|   | 160     | 122.0       | 121.1         | 113.1              | 127.1              | 112.2       | 126.3              |

|   | 200     | 153.1       | 152.3         | 142.5              | 160.5              | 141.4       | 159.4              |

#### VII. REFERENCES

- [1] H. Wang, M. Liserre, F. Blaabjerg, "Toward Reliable Power Electronics: Challenges, Design Tools, and Opportunities," IEEE Ind. Electron. Mag., vol.7, no.2, pp.17-26, June 2013.

- Mag., vol.7, no.2, pp.17-26, June 2013.

[2] D.-L. Blackburn, "Temperature measurements of semiconductor devices—A review," in Proc. 20th Annu. Semicond. Therm. Meas. Manage. Symp., San Jose, CA, Mar. 11–24, 2004,

- [3] D.L. Blackburn, "A review of thermal characterization of power transistors," in Proc. 4th Annu. IEEE Semicond. Therm. Temp. Meas. Symp., San Diego, CA, Feb. 10–12, 1988.

- [4] Y. Avenas, L. Dupont, Z. Khatir, "Temperature Measurement of Power Semiconductor Devices by Thermo-Sensitive Electrical Parameters—A Review", IEEE Trans. Power Electron., vol.27, no.6, pp.3081-3092, June 2012.

- [5] N. Baker, M. Liserre, L. Dupont, Y. Avenas, "Improved Reliability of Power Modules: A Review of Online Junction Temperature Measurement Methods," IEEE Industrial Electronics Magazine, vol.8, no.3, pp.17-27, Sept. 2014.

- [6] P.Ghimire, A.R. deVega, S. Beczkowski, B. Rannestad, S.Munk-Nielsen, and P. Thogersen, "Improving power converter reliability: Online monitoring of high-power IGBT modules," IEEE Ind. Electron. Mag., vol. 8, no. 3, pp. 40–50, Sep. 2014.

- [7] L. Dupont and Y. Avenas, "Evaluation of thermo-sensitive electrical parameters based on the forward voltage for on-line chip temperature measurements of IGBT devices," in Proc. IEEE Energy Convers. Congr. Expo., Sep. 14–18, 2014, pp. 4028–4035.

- [8] V. Sundaramoorthy, E. Bianda, R. Bloch, and F. Zurfluh, "Simultaneous online estimation of junction temperature and current of IGBTs using emitter-auxiliary emitter parasitic inductance," in Proc. PCIM Eur., May 20–22, 2014, pp. 1–8.

- [9] V. Sundaramoorthy, E. Bianda, R. Bloch, I. Nistor, G. Knapp, and A. Heinemann, "Online estimation of IGBT junction temperature (Tj) using gate-emitter voltage (Vge) at turn-off," in Proc. 15th Eur. Conf. Power Electron. Appl., Sept. 2–6, 2013, pp. 1–10.

- [10] H. Luo, W. Li, and X. He, "Online high-power p-i-n diode chip temperature extraction and prediction method with maximum recovery current di/dt," IEEE Trans. Power Electron., vol. 30, no. 5, pp. 2395– 2404, May 2015.

- [11] N. Baker, S. Munk-Nielsen, F. Iannuzzo, M. Liserre, "IGBT Junction Temperature Measurement via Peak Gate Current," in IEEE Transactions on Power Electronics, vol.31, no.5, pp. 3784-3793, May 2016

- [12] N. Baker, L. Dupont, S. Munk-Nielsen, F. Iannuzzo, M. Liserre, "Experimental evaluation of IGBT junction temperature measurement via peak gate current," in 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Europe), pp. 1-11, 8-10 Sept. 2015.

- [13] C. Butron, J. Alexander, B. Strauss, G. Mitic, and A. Lindemann, "Investigation of temperature sensitive electrical parameters for power semiconductors (IGBT) in real-time applications," in Proc. PCIM Eur., May 20–22, 2014, pp. 1–9.

- [14] Z.Xu, F.Wang, and P.Ning, "Junction temperature measurement of IGBTs using short circuit current," in Proc. Energy Convers. Congr. Expo., Sep. 15–20, 2012, pp. 91–96.

- [15] M. Denk and M. Bakran, "An IGBT driver concept with integrated real time junction temperature measurement," in Proc. PCIM Eur., May 20– 22, 2014, pp. 1–8.

- [16] H.R. Plumlee, D.A. Peterman, "Accuracy of junction temperature measurement in silicon power transistor", International Electron Devices Meeting, vol.12, no., pp.86, 1966.

- [17] X. Perpina, J. F. Serviere, J. Saiz, D. Barlini, M. Mermet-Guyennet, and J. Millan, "Temperature measurement on series resistance and devices in power packs based on on-state voltage drop monitoring at high current," Microelectron. Rel., vol. 46, pp. 1834–1839, Sept.–Nov. 2006.

- [18] L. Dupont, Y. Avenas, and P. O. Jeannin, "Comparison of junction temperature evaluations in a power IGBT module using an IR camera and three thermo-sensitive electrical parameters," IEEE Trans. Ind. Appl., vol. 49, no. 4, pp. 1599–1608, Jul./Aug. 2013.

- [19] Y. Avenas and L. Dupont, "Evaluation of IGBT thermo-sensitive electrical parameters under different dissipation conditions— Comparison with infrared measurements," Microelectron. Rel., vol. 52, pp. 2617–2626, Nov.2012.

- [20] D.L. Blackburn and D.W Berning, "Power MOSFET Temperature Measurements", in Proc. I982 IEEE Power Electron. Specialists Conference, 400-407, 1982.

- [21] R. Schmidt, U. Scheuermann, "Using the chip as a temperature sensor—The influence of steep lateral temperature gradients on the Vce(T)-measurement," 13th European Conference on Power Electronics and Applications 2009, pp.1-9, 8-10 Sept. 2009.

- [22] J. Baliga, "Power Semiconductor Devices", International Thomson Publishing, Boston, 1996

- [23] Y. Lembeye, J. L. Schanen, and J. P. Keradec, "Experimental characterization of insulated gate power components: Capacitive aspects," in Proc. 32nd IAS Annu. Meeting Ind. Appl. Conf., vol. 2, pp. 983–988, Oct. 5–9, 1997.

- [24] Infineon Application Note, "Industrial IGBT modules explanation of technical information," AN 2011-05, V1.1, May 2013.

- [25] F.F. Oettinger, D.L. Blackburn, S. Rubin, "Thermal characterization of power transistors," IEEE Transactions on Electron Devices, vol.23, no.8, pp.831-838, Aug 1976.

- [26] V. Smet, F. Forest, J. Huselstein, A. Rashed, F. Richardeau, "Evaluation of VCE Monitoring as a Real-Time Method to Estimate Aging of Bond Wire-IGBT Modules Stressed by Power Cycling," IEEE Trans. on Industrial Electronics, vol.60, no.7, pp.2760-2770, July 2013.

- [27] F. Forest, A. Rashed, J.-J. Huselstein, T. Martiré, P. Enrici, "Fast power cycling protocols implemented in an automated test bench dedicated to IGBT module ageing", Microelectron. Reliabil., Vol. 55, Issue 1, Pages 81-92, Jan. 2015.

- [28] Infineon Technologies, "IGC189T120T8RL" Edition 1.1, 20th June 2013.

- [29] Infineon Technologies, "IGC193T120T8RM" Edition 1.2, 20th June 2013.

- [30] http://www.igbt-driver.com/products/scale-2-plug-and-playdrivers/2sp0320

- [31] Shengqi Zhou; Luowei Zhou; Pengju Sun, "Monitoring Potential Defects in an IGBT Module Based on Dynamic Changes of the Gate Current," IEEE Transactions on Power Electronics, vol.28, no.3, pp.1479-1487, March 2013.

- [32] Kouichi Mochizuki, Yoshifumi Tomomatsu, "IGBT Module", Patent US 20050194660 A1, Sept 2005

- [33] L. Boyer. Analyse des propri´t´s de l'oxyde de grille des composants semi-conducteurs de puissance soumis à des contraintes électrothermiques cycliques : vers la définition de marqueurs de veillissement. PhD thesis, Thèse de l'Université Montpellier 2, 2010.

- [34] Boyer, L.; Notingher, P.; Agnel, S., "Characterization of a Trench-Gated IGBT using the split C-V Method," in Applied Power Electronics Conference and Exposition, 2009. APEC 2009. Twenty-Fourth Annual IEEE, vol., no., pp.2055-2060, 15-19 Feb. 2009

Award in 2015.

Nick Baker received the M.Eng. degree in Electrical & Electronic Engineering from Loughborough University, UK, in 2011. In 2013 he began a PhD at Aalborg University, Denmark in Temperature Measurements of Power Semiconductor Devices using Electrical Parameters. He was awarded with the European Power Electronics Association Young Member

Laurent Dupont received his electrical engineering degree in 2002 and his Ph.D. degree in electrical engineering from the École Normale Supérieure de Cachan, France, in 2006. After ten years of experience in industry, he works as research scientist in the Systèmes et Applications des Technologies de l'Information et de l'Energie (SATIE)

Laboratory in the Institut français des sciences et technologies des transports, de l'aménagement et des réseaux (IFSTTAR), Versailles, France, since 2007. His research interest is the robustness evaluation of power semiconductor modules. In the French project MEMPHIS, supported by the National Research Agency, his research activities are focused on the evaluation of functional and aging indicators usable to monitor the health status of power components.

Stig Munk-Nielsen (S'92–M'97) received the M.Sc. and Ph.D. degrees from Aalborg University, Aalborg, Denmark, in 1991 and 1997, respectively. He is currently Professor at the Department of Energy Technology, Aalborg University. His research interests include LV and MV inverters, power module packaging,

permanent magnet biased inductors, accelerated lifetime test and power module on-state voltage and temperature monitoring. In the last ten years, he has been involved or has managed 12 research projects.

**Francesco Iannuzzo** (M '04, SM '12) earned his M.Sc. (laurea) degree cum laude in 1997 and his Ph.D. degree in Electronics and Information Engineering from the University of Naples, Italy, in 2001, with a study on the reliability of power MOSFETs during diode operations. He is primarily specialized in the field of

power device modelling. He has been Researcher since 2000 with University of Cassino, Italy, where he became Aggregate professor in 2006 and he is currently Associate professor since 2012.

In 2014 he got a contract as professor in Reliable Power Electronics at the Aalborg University, Denmark, where he is also part of CORPE (Center Of Reliable Power Electronics, http://www.corpe.et.aau.dk). He is author or co-author of more than 90 publications on journals and international conferences, and one pending patent on an innovative inverter topology for very compact, galvanic-isolated auxiliary power supply for heavy trains. His research interests are in the field of reliability of power devices, including against cosmic rays, power device failure modelling and testing of power modules up to MW-scale under extreme conditions, like overvoltage, overcurrent and overtemperature.

Prof. Iannuzzo was the Technical Programme Committee co-Chair in two editions of ESREF, the European Symposium on Reliability and Failure analysis. He is a senior member of the IEEE (Reliability Society, Industrial Electronic Society and recently Industrial Application Society) and of AEIT (Italian Electric, Electronic and Telecommunication Association). He permanently serves as expert and peer reviewer for several conferences and journals in the field, like: APEC, ECCE, ESREF, IECON, Microelectronics Reliability,

IEEE Transactions on Industrial Electronics, Transactions on Industrial Informatics and Transactions on Power Electronics.

Marco Liserre (S'00-M'02-SM'07-F'13) received the MSc and PhD degree in Electrical Engineering from the Bari Polytechnic, respectively in 1998 and 2002. He has been Associate Professor at Bari Polytechnic and Professor in reliable power electronics at Aalborg University (Denmark). He is currently Full Professor

and he holds the Chair of Power Electronics at Christian-Albrechts-University of Kiel (Germany). He has published over 200 technical papers (more than 60 of them in international peer-reviewed journals), 4 chapters of a book and a book (Grid Converters for Photovoltaic and Wind Power Systems, ISBN-10: 0-470-05751-3 – IEEE-Wiley, second reprint, also translated in Chinese). These works have received more than 12000 citations. Marco Liserre is listed in ISI Thomson report "The world's most influential scientific minds", 2014.

He has been recently awarded with an ERC Consolidator Grant for an overall budget of 2 MEuro for the project "The Highly Efficient And Reliable smart Transformer (HEART), a new Heart for the Electric Distribution System".

He is member of IAS, PELS, PES and IES. He is Associate Editor of the IEEE Transactions on Industrial Electronics, IEEE Industrial Electronics Magazine, IEEE Transactions on Industrial Informatics, where he is currently Co-Eic, IEEE Transactions on power electronics and IEEE Journal of Emerging and Selected Topics in Power Electronics. He has been Founder and Editor-in-Chief of the IEEE Industrial Electronics Magazine, Founder and the Chairman of the Technical Committee on Renewable Energy Systems, Co-Chairman of the International Symposium on Industrial Electronics (ISIE 2010), IES Vice-President responsible of the publications. He has received the IES 2009 Early Career Award, the IES 2011 Anthony J. Hornfeck Service Award, the 2014 Dr. Bimal Bose Energy Systems Award, the 2011 Industrial Electronics Magazine best paper award and the Third Prize paper award by the Industrial Power Converter Committee at ECCE 2012, 2012. He is senior member of IES AdCom. In 2013 he has been elevated to the IEEE fellow grade with the following citation "for contributions to grid connection of renewable energy systems and industrial drives".