# Using Variable Width RF Integrated Inductors for Quality Factor Optimization

Pedro Almeida, Pedro Pereira, Helena Fino

# ▶ To cite this version:

Pedro Almeida, Pedro Pereira, Helena Fino. Using Variable Width RF Integrated Inductors for Quality Factor Optimization. 4th Doctoral Conference on Computing, Electrical and Industrial Systems (DoCEIS), Apr 2013, Costa de Caparica, Portugal. pp.619-627,  $10.1007/978-3-642-37291-9\_67$ . hal-01348809

HAL Id: hal-01348809

https://hal.science/hal-01348809

Submitted on 25 Jul 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Using Variable Width RF Integrated Inductors for Quality Factor Optimization

Pedro Almeida<sup>1</sup>, Pedro Pereira<sup>1</sup>, Helena Fino<sup>1</sup>

Departamento de Engenharia Electrotécnica, Faculdade de Ciências e Tecnologia, FCT, Universidade Nova de Lisboa, 2829-516 Caparica, Portugal.

pedrodalmeida77@gmail.com, {pmrp, hfino}@ieee.org

**Abstract.** The advancement of CMOS technology led to the integration of more complex functions. In the particular of wireless transceivers, integrated LC tanks are becoming popular both for VCOs and integrated filters [1]. For RF applications the main challenge is still the design of integrated inductors with the maximum quality factor. For that purpose, tapered, i.e., variable width inductors have been proposed in the literature. In this paper, analytical expressions for the determination the pi-model parameters, for the characterization of variable width integrated inductors are proposed. The expressions rely exclusively on geometrical and technological parameters, thus granting the rapid adaptation of the model to different technologies. The results obtained with the model are compared against simulation with *ASITIC*, showing errors below 10%. The model is then integrated into an optimization procedure where inductors with a quality factor improvement in the order of 20-30% are obtained, when compared with fixed width inductors.

**Keywords:** Inductor layout optimization, variable metal width, integrated RF inductor.

# 1 Introduction

During the last years the worldwide market on communications has experienced an ever-growing demand for integrated systems with scaling down dimensions and increased functionality. In the particular case for RF communication circuits, integrated spiral inductors are widely used, notwithstanding their poor performance and their subsequent negative impact on the circuit efficiency at high frequencies. This poor performance is due to the large effect the technology parasitics have on the small value of inductance usually required. As a result, significant effort has been employed in investigating silicon planar inductors, their associated models and methods of improving their performance [1-3].

Regarding layout optimization, non-uniform metal width is proposed, as a way of increasing the inductor quality factor [4, 5]. The main objective of this methodology is to reduce the influence of magnetically induced losses in the inner turns of the spiral where the magnetic field reaches its maximum. By reducing the line width toward the center of the spiral a minimization of the series resistance of the inductor

coil, taking into account both Ohmic losses due to conduction currents, and magnetically induced losses due to Eddy currents, is obtained. Although several promising results have been reported, a fully analytical characterisation of the inductor, leading to perfect understanding of the device performance limitations, is needed so that optimized designs may be obtained.

In this paper analytical expressions for the evaluation of the inductor model parameters are proposed. These expressions rely exclusively on technological parameters and on the geometrical characterization of each inductor segment. The proposed model is used for the optimization-based design of several inductors, where the advantage of using tapered topologies is well pointed out.

The remaining of the paper is organized as follows. The novelty introduced by this paper, is highlighted in Section 2. In this section the basic inductor model is introduced and then, the adaptation of the model for variable width inductors is carefully described. Section 3 is dedicated to the description of several working examples. Finally, conclusions are offered in Section 4.

#### 2 Relationship to Internet of Things

Internet of things relies on the interconnections of a large number of heterogeneous cooperating devices. The development of these devices has been made possible due to the rapid evolution of electronic technologies, enabling the implementation complex functions, in smaller and more rapid circuits. To cope with the necessity of minimizing the power consumption of such systems, new design methodologies must be adopted. In the particular case of communications services, RF integrated inductors are becoming popular elements. Yet, designing integrated inductors for RF applications is a challenging process where a set of correlated geometrical parameters must be obtained, leading to the need of using optimization-based design methodologies.

The main objective of the work described is the optimization of the spiral inductors quality factor, by using variable width inductors.

The novel contributions of this paper are as follows:

- It proposes a set of analytical expressions for the evaluation of the pi-model parameters, for variable width integrated inductors. The proposed expressions depend exclusively on the technological parameters and on the geometric characterization of each segment of the inductor.

- It proposes an efficient optimization-based design for nano-CMOS planar spiral inductor, based in analytical models, instead of using an electromagnetic simulation based approach;

Since the proposed equations are an extension of the model used for fixed width inductors, next sub-section gives a brief description of this model. In subsection 2.2 the adequacy of the model to variable width inductors is carefully described.

# 2.1 Planar Spiral Inductor Pi-Model

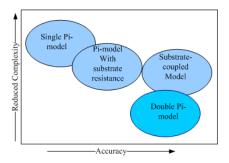

Several integrated inductor models have been introduced in the last years, as illustrated in Fig.1 [6]

Fig. 1. Planar inductor lumped element models complexity versus accuracy trade-off.

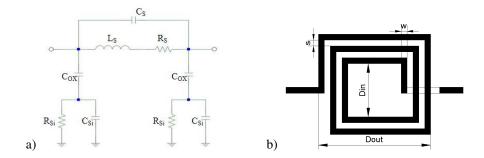

The simplest one is the pi-model, which is widely used for inductors operating in a frequency range up to a few GHz. For the sake of simplicity, the pi-model, illustrated in Fig. 2.a., is adopted, where  $L_s$ , and  $R_s$ . account for the inductance and resistance of the spiral. The overlap between the spiral and the underpass allows direct capacitive coupling between the two terminals of the inductor. The feed-through part is modelled by  $C_s$ . Capacitor  $C_{ox}$  represents the capacitance between the spiral and the substrate. Finally,  $C_{si}$  and  $R_{si}$  account for the silicon substrate capacitance and resistance, respectively.

Fig. 2. a) Planar inductor pi-model; b) Geometric parameters for a square inductor.

For the evaluation of the inductance,  $L_s$ , several approaches have been proposed, based either on fitting processes to experimental values [7] or through physics-based equations [8], where

$$L_{s} = k_{1}\mu_{0}n^{2}d_{avg}/(1 + k_{2}\rho). \tag{1}$$

Given that,

$$\rho = (d_{out} - d_{in})/(d_{out} + d_{in}). \tag{2.a}$$

$$d_{avg} = 0.5(d_{out} + d_{int}). (2.a)$$

$$d_{out} = d_{in} + 2nw + 2(n-1)s. (2.b)$$

Where n is the number of turns, s is the track-to-track distance, and w is the track width. Finally,  $k_1$  and  $k_2$ , are coefficients allowing the model to be adapted to several inductor shapes.

The evaluation of the spiral resistance,  $R_s$ , is obtained by [9]

$$R_s = \sqrt{{R_{dc}}^2 + {R_{ac}}^2}. (3)$$

Where,

$$R_{dc} = l/(\sigma wt). (4.a)$$

$$R_{ac} = kl/[2\sigma\delta(w+t)]. \tag{4.b}$$

And  $\sigma$  and t are the metal conductivity and thickness, respectively. The metal length, l, is obtained with [10]

$$l = N_{sides} d_{ava} n \tan(\pi/N_{sides}). \tag{5}$$

And the skin depth,  $\delta$ , may be determined by [11]

$$\delta = 1/\sqrt{\sigma\mu\pi f}.\tag{6}$$

For the evaluation of the capacitance,  $C_s$ , all overlap capacitances are considered and given by [12].

$$C_s = n_c w^2 \, \varepsilon_{ox} / t_{oxM1-M2}. \tag{7}$$

Where  $\varepsilon_{ox}$  is the oxide permittivity,  $n_c$  is the number of overlaps and  $t_{oxM1-M2}$  is the oxide thickness between the spiral upper and lower metal. The parasitic capacitance,  $C_{ox}$  between the spiral metal and the silicon substrate, is estimated with [12]

$$C_{ox} = 0.5 lw \, \varepsilon_{ox} / t_{ox}. \tag{8}$$

Where  $t_{ox}$  is the thickness of the  $SiO_2$  between the inductor and the substrate and lw defines the area of the spiral. Finally the Substrate resistance,  $R_{si}$ , and capacitance  $C_{si}$ , are obtained with 11

$$R_{si} = 2h_{si}/(l w \sigma_{si}). (9)$$

$$C_{si} = 0.5 lw \, \varepsilon_o \varepsilon_r / h_{si}. \tag{10}$$

Where  $\sigma_{si}$  and  $h_{si}$  are the substrate conductivity and height, respectively.

This model has been extensively used in an optimization-based tool for inductor design [13] yielding solutions with very good accuracy when compared with results obtained with ASITIC .

#### 2.2- Variable Width Inductor Model

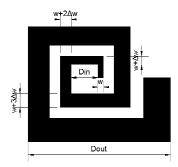

Variable width inductor layout has been proposed as a way of maximizing the quality factor of integrated inductors. In this work, square inductors, where each segment shows a width increment of  $\Delta w$ , as illustrated in Fig.3., are considered.

Fig. 3. Variable width square inductor.

Since each segment will show an increment on both width and length new equations will be proposed, relying on the dimensions of each segment of the inductor. The width of a segment may be evaluated with

$$w_i = w + n_i \Delta w. \tag{11}$$

Where  $n_i$  is the number of the segment, and w is the initial metal width.

In this work, the basic structure for supporting all the inductor segments characterization is a matrix of five columns (one for each segment per turn) and n lines (one per inductor turn). Initially, a matrix containing every segment length,  $l_{ij}$  as

$$l_{ij} = \begin{bmatrix} l_{11} & l_{12} & l_{13} & l_{14} & l_{15} \\ l_{21} & l_{22} & l_{23} & l_{24} & l_{24} \\ ... & ... & ... & ... & ... \\ l_{n1} & l_{n2} & l_{n3} & l_{n4} & l_{n5} \end{bmatrix}$$

(12)

is generated. Then a matrix containing every segment width,  $w_{ij}$

$$w_{ij} = \begin{bmatrix} w_{11} & w_{12} & w_{13} & w_{14} & w_{15} \\ w_{21} & w_{22} & w_{23} & w_{24} & w_{24} \\ \dots & \dots & \dots & \dots & \dots \\ w_{n1} & w_{n2} & w_{n3} & w_{n4} & w_{n5} \end{bmatrix}.$$

(13)

is generated.

Regarding the pi-model inductance,  $L_s$ , a new way for evaluating  $d_{out}$  must be adopted. Considering the basic matrixes in (12), (13),  $d_{out}$  may be obtained by

$$d_{out} = l_{n4} + w_{n5}. (14)$$

For the evaluation of  $R_S$ , (4.a) and (4.b) are replaced by

$$R_{dc} = \frac{1}{\sigma t} \sum_{i=1}^{n} \sum_{j=1}^{5} \frac{l_{ij}}{w_{ij}}.$$

(15.a)

$$R_{ac} = \frac{k}{2\sigma\delta} \sum_{i=1}^{n} \sum_{j=1}^{5} \frac{l_{ij}}{w_{ij} + t} .$$

(15.b)

For this purpose the two new matrix (15.a) and (15.b) are generated containing each segment geometrical information for  $R_{dc}$  and  $R_{ac}$

$$\frac{l_{ij}}{w_{ij}} = \begin{bmatrix}

\frac{l_{11}}{w_{11}} & \frac{l_{12}}{w_{12}} & \frac{l_{13}}{w_{13}} & \frac{l_{14}}{w_{14}} & \frac{l_{15}}{w_{15}} \\

\frac{l_{21}}{l_{21}} & \frac{l_{22}}{l_{22}} & \frac{l_{23}}{l_{23}} & \frac{l_{24}}{l_{25}} & \frac{l_{25}}{w_{25}} \\

\frac{l_{n1}}{w_{n1}} & \frac{l_{n2}}{w_{n2}} & \frac{l_{n3}}{w_{n3}} & \frac{l_{n4}}{w_{n4}} & \frac{l_{n5}}{w_{n5}}

\end{bmatrix}.$$

(16)

$$\frac{l_{ij}}{w_{ij}+t} = \begin{bmatrix}

\frac{l_{11}}{w_{11}+t} & \frac{l_{12}}{w_{12}+t} & \frac{l_{13}}{w_{13}+t} & \frac{l_{14}}{w_{14}+t} & \frac{l_{15}}{w_{15}+t} \\

\frac{l_{21}}{w_{21}+t} & \frac{l_{22}}{w_{22}+t} & \frac{l_{23}}{w_{23}+t} & \frac{l_{24}}{w_{24}+t} & \frac{l_{25}}{w_{25}+t} \\

\vdots & \vdots & \vdots & \vdots & \vdots \\

\frac{l_{n1}}{w_{n1}+t} & \frac{l_{n2}}{w_{n2}+t} & \frac{l_{n3}}{w_{n3}+t} & \frac{l_{n4}}{w_{n4}+t} & \frac{l_{n5}}{w_{n5}+t}

\end{bmatrix}.$$

(17)

Finally (8), (9) and (10) are replaced by

$$C_{ox} = \frac{1}{2} \cdot \frac{\varepsilon_{ox}}{t_{ox}} \sum_{i=1}^{n} \sum_{j=1}^{5} l_{ij} w_{ij} .$$

(18)

$$R_{si} = \frac{2}{G_{sub}} \sum_{i=1}^{n} \sum_{j=1}^{5} \frac{1}{l_{ij} w_{ij}}.$$

(19)

$$C_{si} = \frac{1}{2} \cdot C_{sub} \sum_{i=1}^{n} \sum_{j=1}^{5} l_{ij} w_{ij} .$$

(20)

For which an auxiliary matrix containing the area of each segment is considered.

# 4 Variable Inductor Working Example

In order to confirm the validity of the proposed layout optimization method, a set of square spiral inductors has been designed. Three examples, considering the design of 1nH, 1.5nH and 2nH inductors at a working frequency of 1GHz will be presented. In all examples the technological parameters shown in Table I were used

TABLE I UMC130 – TECHNOLOGICAL PARAMETERS

| Parameter                   | Value     | Parameter                     | Value  |  |  |

|-----------------------------|-----------|-------------------------------|--------|--|--|

| $\mathcal{E}_{o}$           | 8.85e-12  | $t_{ox}(\mu m)$               | 600    |  |  |

| $\mathcal{E}_r$             | 1.0       | $C_{\text{sub}} (F/m^2)$      | 4.0e-6 |  |  |

| $\sigma(\Omega \mathrm{m})$ | 1/2.65e-8 | $G_{sub}$ (S/m <sup>2</sup> ) | 2.43e5 |  |  |

For the model validation a comparison between results obtained with variable width design, against fixed width designs, for an approximately equal area, is

presented. The layout parameters were evaluated according to the constraints in Table II

TABLE III

SPIRAL INDUCTOR DESIGN CONSTRAINTS

| Parameter           | Min  | Step | Max   |

|---------------------|------|------|-------|

| w (µm)              | 5.0  | 0.5  | 100.0 |

| <i>Δw</i> (μm)      | 1    | 0.25 | -     |

| s(µm)               | 1.5  | -    | -     |

| $d_{in}$ ( $\mu$ m) | 20.0 | 0.5  | 200.0 |

| N                   | 1.5  | 1.0  | 15.5  |

| $d_{out}$           | -    | -    | 500   |

#### A. Example 1 – Inductor with 1 nH

In this example a spiral inductor of 1nH was considered. The results obtained for a fixed width layout as well as for  $\Delta w$  of  $1.25\mu m$ ,  $1.5\mu m$  and  $1.75\mu m$  are represented in Table II. Also in the same table, the simulation results obtained with ASITIC for each case are represented.

| Ind | $\Delta w$ | W    | $d_{in}$ | n   | $d_{out}$ | L (nH) |        |                | Q     |        |                      | Q.    |

|-----|------------|------|----------|-----|-----------|--------|--------|----------------|-------|--------|----------------------|-------|

|     | (µm)       | (µm) | (µm)     |     | (µm)      | Model  | Asitic | $\epsilon_{L}$ | Model | Asitic | $\epsilon_{	ext{Q}}$ | Impr. |

| 1   | 0          | 13.8 | 68.8     | 2.5 | 157       | 1      | 1.07   | 6.3%           | 6.94  | 6.28   | 10.5%                |       |

| 2   | 1.25       | 7.5  | 41.3     | 3   | 154       | 0.998  | 1.06   | 5.4%           | 8.07  | 8.24   | 1.7%                 | 16%   |

| 3   | 1.5        | 7.25 | 39.8     | 3   | 161       | 0.999  | 1.04   | 4.3%           | 8.57  | 8.53   | 0.5%                 | 23%   |

| 4   | 1.75       | 5.75 | 40.3     | 3   | 162       | 1.01   | 1.04   | 2.5%           | 8.52  | 8.16   | 4.4%                 | 23%   |

In the last column the relative improvement in the quality factor from using incremental width is given.

#### B. Example 2 – Inductor with 1.5nH

In this example a spiral inductor of 1.5nH was considered. The results obtained for a fixed width layout as well as for  $\Delta w$  of  $2\mu m,\,2.5\mu m$  and 3.0  $\mu m$  are represented in Table II. Also in the same table, the simulation results obtained with ASITIC for each case are represented.

TABLE IVI  $Optimization \ Results \ for \ 1.5 \ nH \ Inductor \ with \ several \ \Delta w$

| Ind | $\Delta w$ | W    | $d_{in}$ | n   | $d_{out}$ | L (nH) |        |                   | Q     |        |                      | Q    |

|-----|------------|------|----------|-----|-----------|--------|--------|-------------------|-------|--------|----------------------|------|

|     | (µm)       | (µm) | (µm)     |     | (µm)      | Model  | Asitic | $\epsilon_{ m L}$ | Model | Asitic | $\epsilon_{	ext{Q}}$ | impr |

| 1   | 0          | 20.3 | 10.3     | 2.5 | 231       | 1.5    | 1.62   | 7.6%              | 10.1  | 9.27   | 9.0%                 |      |

| 2   | 2          | 11.5 | 61.3     | 3   | 233       | 1.5    | 1.58   | 5.2%              | 12.29 | 12.61  | 2.6%                 | 22%  |

| 3   | 2.5        | 6.25 | 64.3     | 3   | 221       | 1.5    | 1.52   | 1.6%              | 11.07 | 10.59  | 4.6%                 | 9%   |

| 4   | 3          | 8.75 | 58       | 3   | 253       | 1.51   | 1.54   | 1.8%              | 13.44 | 12.74  | 5.5%                 | 33%  |

#### C. Example 3 – Inductor with 2nH

In the last example a spiral inductor of 2.0nH was considered. The results obtained for a fixed width layout as well as for  $\Delta w$  of  $2\mu m$ ,  $2.5\mu m$  and  $3.0\mu m$  are represented in Table II. Also in the same table, the simulation results obtained with ASITIC for each case are represented.

TABLE V  $Optimization \ Results \ for \ 1.5 \ nH \ Inductor \ with \ several \ \Delta w$

| Ind | $\Delta w$ | W    | $d_{in}$ | n   | $d_{out}$ | L (nH) |        |                   | Q     |        |                      | Q    |

|-----|------------|------|----------|-----|-----------|--------|--------|-------------------|-------|--------|----------------------|------|

|     | (µm)       | (µm) | (µm)     |     | (µm)      | Model  | Asitic | $\epsilon_{ m L}$ | Model | Asitic | $\epsilon_{	ext{Q}}$ | impr |

| 1   | 0          | 25.8 | 137      | 2.5 | 297       | 2      | 2.16   | 7.6%              | 12.72 | 11.62  | 9.4%                 |      |

| 2   | 2.75       | 12.5 | 85       | 3   | 296       | 2      | 2.1    | 4.8%              | 15.03 | 15.21  | 1.2%                 | 18%  |

| 3   | 3          | 9.75 | 86.3     | 3   | 288       | 2      | 2.05   | 2.6%              | 14.39 | 14.19  | 1.4%                 | 13%  |

| 4   | 3.75       | 10.3 | 80.5     | 3   | 317       | 2      | 2.05   | 2.6%              | 16.14 | 15.34  | 5.2%                 | 27%  |

#### 5 Conclusions

In this paper the analytical expressions for the evaluation of integrated inductor pimodel parameters was proposed. This expressions consider variable width square inductors, were each segment shows a constant increment of width. The validity of the model was shown through three working examples considering the design of 1.0nH, 1.5nH and 2.0nH inductors at a working frequency of 1GHz. From the examples presented a quality factor improvement in the order of 20% to 30% may be obtained, by using variable width.

Should higher frequency of operation be envisaged, a more accurate inductor, such as 2-pi-model should be used. The adaptation of the proposed equations to the 2-pi-model is under test.

#### References

- 1. I Krout, H. Mnif, M. Fakhfakh, and M. Loulou, "Optimizing LC VCO Performances Through a Heuristic", Wseas Transactions on Electronics, vol. 5, pp.274-281, 2008.

- P-W. Lai, L. Dobos, S. Long, "A 2.4GHz SiGe low phase noise VCO using on chip Tapped inductor", Solid-State Circuits Conference - ESSCIRC,pp. 505–508, 2003.

- 3. L. L. K. Leung, and H. C. Luong, "A 1V9.7mW CMOS frequency synthesizer for IEEE 802.11a transceivers", IEEE Trans. Microw. Theory Tech., vol. 56, pp. 39–48, Jan. 2008.

- Wesley A. Gee, "CMOS Integrated LC Q-enhanced RF Filters for wireless Receivers", PhD. Thesis, Georgia Institute of Technology, 2005.

- C. Patrick Yue and S. Simon Wong, "Physical modeling of spiral inductors on silicon", IEEE Transactions on Electron Devices, Vol. 47 560-568, 2000.

- Lai,I., Fujishima, M., "Design and Modeling of Millimeter-Wave CMOS Circuits for Wireless Transceivers - Era of Sub-100nm Technology", Springer, 2008.

- Sunderarajan S. Mohan, Maria del Mar Hershenson, Stephen P. Boyd, and Thomas H. Lee, "Simple Accurate Expressions for Planar Spiral Inductances", IEEE Journal of Solid-State Circuits, Vol. 34, No 10, October 1999.

- 8. S. Jenei, B. K. J. C. Nauwelaers, and S. Decoutere, "Physics-Based Closed-Form Inductance Expression for Compact Modelling of Integrated Spiral Inductors," IEEE J. Solid-State Circuits, vol. 37, no. 1, pp. 77–80, January 2002.

- 9. Y. S. Choi and J. B. Yoon, "Experimental Analysis of the Effect of Metal Thickness on the Quality Factor in Integrated Spiral Inductors for RF ICs," IEEE Electron Device Lett., vol. 25, no. 2, pp. 76–79, February 2004.

- J. Allstot, K. Choi, J. Park, "Parasitic-Aware Optimization of CMOS RF Circuits", Kluwer Academic Publishers, ISBN 1-4020-7399-2, 2003.

- 11.M. Park, C. H. Kim, C. S. Kim, et. al, "Frequency-Dependent Series Resistance of Monolithic Spiral Inductors," IEEEMicrowave Guided Lett., vol. 9, no. 12, pp. 514–516, December 1999.

- 12.Olive H. Murphy, "Advanced Physical Modelling of Multilayer Inductors for CMOS RF Front-End Applications", PhD Thesis, University College Cork National University of Ireland, October, 2005.

- 13. Pereira, P., Fino, M. H., Coito, F. & Ventim-Neves, M. "ADISI- An efficient tool for the automatic design of integrated spiral inductors" The 16th IEEE International Conference on Electronics, Circuits, and Systems (ICECS'09), 799–802, 2009.