# Modelling the ARMv8 Architecture, Operationally: Concurrency and ISA

Shaked Flur, Kathryn E. Gray, Christopher Pulte, Susmit Sarkar, Ali Sezgin, Luc Maranget, Will Deacon, Peter Sewell

# ▶ To cite this version:

Shaked Flur, Kathryn E. Gray, Christopher Pulte, Susmit Sarkar, Ali Sezgin, et al.. Modelling the ARMv8 Architecture, Operationally: Concurrency and ISA. Principles of Programming Languages 2016 (POPL 2016), Jan 2016, Saint Petersburg, United States. hal-01244776

# HAL Id: hal-01244776 https://inria.hal.science/hal-01244776

Submitted on 16 Dec 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Modelling the ARMv8 Architecture, Operationally: Concurrency and ISA

Shaked Flur<sup>1</sup> Kathryn E. Gray<sup>1</sup> Christopher Pulte<sup>1</sup> Susmit Sarkar<sup>2</sup> Ali Sezgin<sup>1</sup>

Luc Maranget<sup>3</sup> Will Deacon<sup>4</sup> Peter Sewell<sup>1</sup>

1 University of Cambridge, UK first.last@cl.cam.ac.uk s

<sup>2</sup> University of St Andrews, UK ss265@st-andrews.ac.uk <sup>3</sup> INRIA, France

<sup>4</sup> ARM Ltd., UK will.deacon@arm.com

#### **Abstract**

In this paper we develop semantics for key aspects of the ARMv8 multiprocessor architecture: the concurrency model and much of the 64-bit application-level instruction set (ISA). Our goal is to clarify what the range of architecturally allowable behaviour is, and thereby to support future work on formal verification, analysis, and testing of concurrent ARM software and hardware.

Establishing such models with high confidence is intrinsically difficult: it involves capturing the vendor's architectural intent, aspects of which (especially for concurrency) have not previously been precisely defined. We therefore first develop a concurrency model with a microarchitectural flavour, abstracting from many hardware implementation concerns but still close to hardware-designer intuition. This means it can be discussed in detail with ARM architects. We then develop a more abstract model, better suited for use as an architectural specification, which we prove sound w.r.t. the first.

The instruction semantics involves further difficulties, handling the mass of detail and the subtle intensional information required to interface to the concurrency model. We have a novel ISA description language, with a lightweight dependent type system, letting us do both with a rather direct representation of the ARM reference manual instruction descriptions.

We build a tool from the combined semantics that lets one explore, either interactively or exhaustively, the full range of architecturally allowed behaviour, for litmus tests and (small) ELF executables. We prove correctness of some optimisations needed for tool performance.

We validate the models by discussion with ARM staff, and by comparison against ARM hardware behaviour, for ISA singleinstruction tests and concurrent litmus tests.

Categories and Subject Descriptors C.0 [General]: Modeling of computer architecture; D.1.3 [Programming Techniques]: Concurrent Programming—Parallel programming; F.3.1 [Logics and Meanings of Programs]: Specifying and Verifying and Reasoning about Programs

Keywords Relaxed Memory Models, semantics, ISA

#### 1. Introduction

The ARM architecture is the specification of a wide range of processors: cores designed by ARM that are integrated into devices produced by many other vendors, and cores designed ab initio by ARM architecture partners, such as Nvidia and Qualcomm. The architecture defines the properties on which software can rely on, identifying an envelope of behaviour that all these processors are supposed to conform to. It is thus a central interface in the industry, between those hardware vendors and software developers. It is also a desirable target for software verification and analysis: software that is verified w.r.t. the architecture should run correctly on any of those processors (modulo any hardware errata, of course).

However, exactly what behaviour is and is not allowed by the architecture is not always clear, especially when it comes to the concurrency behaviour of ARM multiprocessors. The architecture aims to be rather loose, to not over-constrain the hardware microarchitectural design choices of all those different vendors, and to permit optimised implementations with high performance and low power consumption. To this end, it adopts a *relaxed memory model*, allowing some effects of out-of-order and non-multi-copy-atomic implementations to be programmer-visible. But it describes that in prose, which, as one might expect, leaves many open questions.

Our goal in this paper is to clarify this situation, developing mathematically rigorous models that capture the ARM architectural intent. But establishing such models with high confidence is intrinsically difficult, as the vendor intent has not previously been made this precise, either in public documents or internally. Blackbox testing of processor implementations is useful here, comparing their behaviour against that allowed by models for a variety of concurrent test programs [3, 4, 8, 21, 22, 24], but it can only go so far; one really needs to discuss the model in detail with the architects (those with the authority to define what the architecture allows). This means it must be accessible to them, and that suggests our strategy: we first develop a concurrency model with a microarchitectural flavour, abstracting from many hardware implementation concerns but still close to hardware-designer intuition, so that it can be clearly (albeit necessarily informally) related to the processor designs they have in mind, and be tested against their extensional behaviour. In this Flowing model read requests, writes, and barriers flow explicitly through a hierarchical storage subsystem. We then develop a more abstract model, better suited for use as an architectural specification and programmer's model, which we prove sound w.r.t. that. This partial-order propagation (or POP) model abstracts from the storage-subsystem hierarchy to give a model in which all hardware threads are symmetrical. Both models have been discussed in detail with senior ARM staff, resolving many subtle questions about the architecture.

1

The concurrency semantics alone is not enough to understand or reason about concurrent code; one also needs semantics for the instruction set architecture (the ISA). The ARM architecture describes the sequential behaviour of the ISA reasonably precisely, in a proprietary pseudocode language; the problems here are (1) dealing with the mass of detail involved, and (2) integrating these sequential descriptions into the concurrent semantics. One cannot simply treat each instruction as an atomic transaction, or interleave their pseudocode. Previous work on relaxed-memory semantics has not really addressed this issue, either avoiding it entirely or defining semantics for a small ad hoc fragment of the ISA. Here we use a novel ISA description language, with a lightweight dependent type system, that lets us use a rather direct representation of the ARM architecture reference manual (the ARM ARM) instruction descriptions [7]. We model all the application-level ISA except for floating-point and vector instructions, and we validate this part of the semantics against hardware for a suite of automatically generated single-instruction tests.

Our models are defined in executable higher-order logic, in Lem [19], and we use Lem to generate executable OCaml code to make a tool allowing one to explore, either interactively or exhaustively, the behaviour of concurrent litmus tests or (small) conventional ELF binaries. For performance the tool relies on the fact that certain transitions commute, to reduce the combinatorial blow-up; we prove that those properties hold.

Our focus throughout is on the ARMv8 version of the architecture, which introduced support for 64-bit execution. Example ARMv8 cores and processors include the ARM-designed Cortex-A53 and A57 cores, in the AMD Opteron A1100, the Qualcomm Snapdragon 810, and the Samsung Exynos Octa 5433 SoCs; together with architecture-partner-designed processors such as Nvidia Denver core, used in the Tegra K1. The Apple A7 and A8 (in iPhones and iPads since the iPhone 5S) also appear to be ARMv8-compatible.

ARMv8 also added several new concurrency primitives, including the ARM load-acquire and store-release instructions, and weaker barrier instructions than the ARMv7 dmb full barrier. It includes both a 64-bit and 32-bit instruction set; we deal with the former, the A64 of AArch64, and all those concurrency primitives.

To summarise our contribution, we:

- give an abstract-microarchitectural model, the Flowing model, for ARMv8 concurrency, validated both by black-box testing and discussions with ARM staff (§3,4,7,13);

- give a more abstract model, the POP model (§5,8);

- integrate the above with an ISA semantics for all the application-level non-FP/SIMD ARMv8 instruction set (§6);

- prove that POP does indeed abstract Flowing (§9);

- prove that various model transitions commute (§10);

- develop a tool that allows one to explore, either interactively or exhaustively, the behaviour of concurrent litmus tests or (small) conventional ELF binaries (§11); and

- demonstrate this on an example of the Linux ARMv8 spinlock code (§12).

We begin with an informal description of the main ideas underlying the Flowing model, and the concurrency phenomena it has to deal with (§3,4). The web interface and other online material can be accessed from http://www.cl.cam.ac.uk/~pes20/popl16-armv8.

We envisage a stack as below, where the black-labelled edges, in this paper, enable a range of semantics and verification activities above this solid foundation, such as the gray-labelled edges showing a possible C/C++11 concurrency implementation result above ARM. Looking downwards, the Flowing model can also be used for testing and verification of aspects of real hardware, taking us closer towards a production top-to-bottom verified stack.

by multiple vendors

## 2. Related Work

There has been extensive recent work on hardware memory models, e.g. for x86 [20], IBM Power [22, 23], and ARMv7 [4]. The Power and ARM concurrency architectures are broadly similar, both being relaxed non-multi-copy atomic models that respect only certain program-order relations, and which have cumulative memory barrier instructions. But they differ in many important aspects: they have different memory barrier and synchronisation instructions<sup>1</sup>, and the associated microarchitectures are quite different. That is important for us here: that Power model [22, 23] does not correspond well to ARM implementations, and so cannot serve as a basis for the discussion with ARM architects that is needed for solid validation that it matches their intent.

For example, in typical Power microarchitectures (as we understand them) memory writes and read-requests propagate via separate structures, and the Power sync memory barrier implementation involves an acknowledgement being sent back to the originating hardware thread when the barrier has been processed by each other thread. That Power model, largely based on discussions with an IBM architect as it was, explicitly modelled those syncacknowledgements. But ARM microarchitectures may keep memory writes and read-requests in the same structures, with the ARM dmb memory barrier achieving similar extensional effects to sync quite differently, by keeping pairs of barrier-separated accesses ordered within those, rather than with global acknowledgements. It is this ordering that our Flowing model captures. We shall see other more subtle differences below, all of which are important for intensional discussion with the vendors, and some of which give rise to programmer-observable effects.

The other closely related work is the ARMv7 model of Alglave et al. [4], which differs in other important aspects from what we do here. Most importantly, it is aiming to be considerably more abstract than either of the two models we present, without the microarchitectural flavour that enables us to establish a clear relationship between them and the architects' intent. That level of abstraction is thus good for simplicity but bad for validation, and the validation of that model relies heavily on black-box testing. In an ideal world (but one which we leave for future work) we would have both the low-level microarchitectural Flowing model as we describe here, validated both by discussion and testing, and a proof (via our POP model) that such an abstract model is indeed sound

<sup>&</sup>lt;sup>1</sup> The Power sync and ARM dmb are broadly similar, but there is no ARM counterpart of the Power lwsync, and there is no Power counterpart of the ARMv8 dmb st and dmb |d barriers or of the ARMv8 load-acquire and store-release instructions.

w.r.t. the architectural intent. The models differ also in their mathematical style: following Sarkar et al. [22, 23], we adopt an operational style, which again is good for the correspondence with architect intuition, while [4] is axiomatic. The latter is faster for exhaustively checking the results of small litmus tests, while the former allows one to incrementally explore single executions of larger programs. Finally, we cover ARMv8 rather than ARMv7, and integrate with semantics for a large part of the instruction set.

There has been a great deal of previous work using domain-specific IDLs and proof assistants to describe instruction behaviour, for many different purposes. On the formal and semantics side, this includes the ARMv7 model by Fox [10] in his L3 language, that by Goel et al. [11] for x86 in ACL2, work on automatically generating compiler components, e.g. [9], and the assembly language and machine-code models used by verified compilation work, e.g. [5, 13–15, 18, 26] With the exception of CompCertTSO [26], which was w.r.t. the much simpler x86-TSO model, none of these address concurrency. A few, notably those of Fox and Goel, are rather complete in their coverage of the sequential ISA, but many include just enough for the purpose at hand (simplifying the problems of scale), and are not concerned with engineer-accessibility.

# 3. Introduction to the Flowing Model

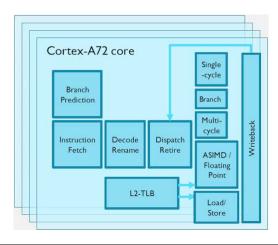

Modern high-end processors are astonishingly complex. The pipeline of an ARM Cortex-A57 core can have up to 128 instructions in flight simultaneously [6], with each instruction broken down into micro-operations that are dispatched to multiple arithmetic, branch, floating-point, and load/store execution units. Shadow registers and register renaming are used to prevent the number of architected registers being a bottleneck. A very high-level view of a Cortex-A72 core showing some of this is in Fig. 1, and there are multiple levels of cache and interconnect in addition to that, some shared between cores or clusters thereof.

A detailed microarchitectural description does not make a good programmers model, or a usable basis for semantics and reasoning about concurrent software. Indeed, much microarchitectural detail is, by design, not observable to programmers (except via performance properties); there are only some aspects that give rise to behaviour that concurrent contexts can observe, notably the out-oforder execution that the pipeline permits (including shadow registers), and the lack of multi-copy-atomicity that the cache protocol, cache hierarachy and interconnect might exhibit. Our task here is to invent a new abstraction, just concrete enough to model those aspects, and just concrete enough to let hardware designers and architects relate it to the range of actual microarchitectures they have in mind, but otherwise as simple as possible. This model can be validated by discussion and by testing against hardware. Note that we are not defining a *specific* microarchitecture, but rather a model with a microarchitectural flavour that is architecturally complete, allowing the full envelope of behaviour that the architects intend. Then we can build higher-level models, proving them sound with respect to that abstract-microarchitectural one, to use for reasoning.

We build this new abstraction, the *Flowing model*, in three parts. The *instruction semantics* defines the behaviour of each instruction in isolation, giving, for each, a clause of an AST type denoting the machine-code instructions, a decode function that maps 32-bit opcode bitvectors into that type, and a clause of an execute function that gives imperative pseudocode for the instruction. Fig. 2 shows these for the ADD instruction (eliding the body of its decode function). We elaborate on this ISA model and the language used for it in §6. We interpret the bodies of the decode and execute functions with an operational semantics for our ISA description language; the steps of that semantics are essentially abstract micro-operations, abstracting from the actual hardware micro-operations performed by the arithmetic units etc. Even what one might think is a simple

Figure 1. ARM Cortex-A72 Core Block Diagram (source: ARM)

```

typedef ast =

forall Int 'R, 'R IN {32, 64}, (*register size*)

Int 'D, 'D IN {8,16,32,64}. (*data size*)

| AddSubImmediate of

(reg_idx, reg_idx, [:'R:], boolean, boolean, bit['R])

function forall Int 'R, 'R IN {32,64},

Int 'D, 'D IN {8,16,32,64}.

decodeAddSubtractImmediate

([sf]:[op]:[S]:0b10001:shift:(bit[12]) imm12:Rn:Rd)

: ast<'R,'D> effect pure =

function clause execute (AddSubImmediate(d,n,

datasize,sub_op,setflags,imm)) = {

(bit['R]) operand1 :=

if n == 31 then rSP() else rX(n);

(bit['R]) operand2 := imm;

(bit) carry_in := 0; (*ARM:uninitialized*)

if sub_op then {

operand2 := NOT(operand2);

carry_in := 1;

else

carry_in := 0;

let (result,nzcv) =

(AddWithCarry(operand1,operand2,carry_in)) in {

if setflags then

wPSTATE_NZCV() := nzcv;

if (d == 31 \& \sim (setflags)) then

wSP() := result

else

wX(d) := result;

}

```

Figure 2. Instruction semantics for add/adds/sub/subs

instruction like add is surprisingly intricate when one handles all the details; one execution involves 80 instruction-semantics steps.

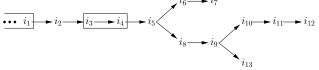

The *thread subsystem*, analogous but different in detail to that of the IBM Power model of Sarkar et al. [22], models the execution of instructions in a single core (or hardware thread) by allowing out-of-order execution, respecting various inter-instruction dependencies as necessary. This abstracts from the out-of-order dispatch and control logic, the register renaming, the load/store queues, and the local (L1) cache of the core, modelling all that with a simple tree of instruction instances:

Some of these (boxed) may be finished, while others may be executing out-of-order or speculatively, after a conditional branch (the forks) which is not yet resolved. The ISA model generates *events*, principally: *register-read*, *register-write*, *memory-read*, *memory-write* and *barrier*, which are used by the thread-subsystem (§7.7 Sail interpreter step); some involve instruction-state continuations, e.g. to record an instruction state which is awaiting the result of a memory read.

The last part of the model is the *storage subsystem*, which receives memory read, write and barrier *requests* from the thread and replies to read-requests with *read-responses* containing the write to be read from. The storage subsystem abstracts from the interconnect and shared cache levels in the microarchitecture. The Flowing-model instruction semantics and thread subsystem will be reused in our more abstract POP model, while the storage subsystem will be replaced by a more abstract model.

Given all the complexity of real microarchitectures it is interesting to note that the ARM architects have a much simpler abstraction in mind when they discuss the validity of different behaviour: they can often reason about the architecture and the hypothetical behaviour of hardware without needing to unpack details of cache protocols and suchlike. The basic idea of our Flowing model is to try to formalize this abstraction, keeping it as familiar to them as much as possible. In the rest of this section we introduce it, via two motivating examples.

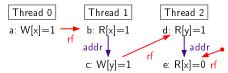

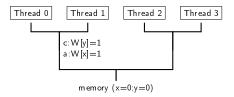

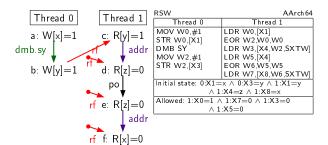

Lack of multi-copy atomicity The ARM architecture is not multi-copy atomic [8]: a write by one hardware thread can become visible to some other threads before becoming visible to all of them. This is observable to the programmer in concurrent litmus tests such as WRC+addrs (write-to-read causality):

Test WRC+addrs: Allowed

Here a message x=1 is written by Thread 0 and read by a Thread 1 which then raises a flag y=1. That in turn is read by Thread 2 which then tries to read the message. To prevent local reordering in the second two threads, both of their second accesses are made address-dependent on the results of their first reads. This is not enough to prevent the unwanted behavior shown, in which Thread 2 reads from the initial state of x, not the value 1 of the message (a).

The diagram shows a particular execution, not a program: a graph over memory read and memory write events. A read event b:R[x]=1 represents a memory read from the address of x of value 1. Similarly a:W[x]=1 represents a memory write. All variables are disjoint and initialized to 0. The rf edges indicate *reads-from*

relations between writes and reads (the rf edge from a red dot indicates a read from the initial memory value).

Microarchitecturally, this behaviour can arise from multi-level cache and core clustering. Two cores that share a cache level that is not shared with a third core can observe each other's memory accesses before the third core does. ARM architects reason about the behaviour of this by abstracting it to a tree-shaped topology of queues in which requests "flow", starting from the entry point of the issuing thread through join points until they reach main memory. On their way to main memory some requests might bypass others subject to reordering conditions. In this abstraction, read requests do not need to travel all the way to main memory to get satisfied: if a read request encounters a write to the same address, a read response can be immediately sent to the issuing thread of the read request. This abstraction is the inspiration behind the Flowing storage subsystem.

For example, a particular processor might have a topology as below, with the pairs of threads 0,1, and 2,3, each sharing a queue which is not shared with the rest (many other topologies are possible, especially with more cores). At a certain point in the computation, the write (a) might have propagated down past one join point, with the read request (b) still above that point.

Later the read request (b) can flow down another step, and then perhaps be satisfied directly from (a). That will resolve the address dependency to write (c), which could be committed and flow to the same point:

Then, as (c) and (a) are to different addresses (and not separated by a barrier), they can be *reordered*, and (c) could flow past the next point where it can satisfy Thread 2's first read. In turn that resolves the Thread 2 address dependency to its read of x, and that can flow down and be satisfied from the initial x=0 value in main memory before (a) passes the bottom join point.

The abstraction used in this description has pros and cons. It is reasonably simple and easy to understand, and to relate to hierarchical microarchitectures. But the asymmetry between hardware threads is uncomfortable from an architectural point of view (programmers will typically not know the assignment of software threads to particular hardware threads, and should not write code where the correctness depends on that assignment); it is exactly that asymmetry that our POP model will abstract from.

It is interesting to note also that the testing of ARM implementations that we have done to date has not exhibited observable non-multi-copy-atomic behaviour, even though the architecture intentionally and unambiguously permits it (to allow freedom for future implementations). This limits the extent to which a model can be validated by black-box testing alone; it also means, as usual for a loose specification, that it is important to reason about software w.r.t. the architecture rather than w.r.t. current implementations, at least if it is intended to be portable to future implementations.

Contrasting again with Power, there such non-multi-copyatomic behaviour can be understood in a different way, from the cache protocol alone acting in a symmetric topology [16, §12]. In this sense the Flowing model is not a good intensional representation of Power microarchitectures, and there are litmus tests that are observable on Power implementations that Flowing does not allow. But the POP model permits those, and it is a plausible basis for a good common model.

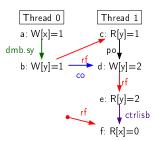

**Out-of-order execution** Turning to the thread model that we use for both Flowing and POP, ARM and Power implementations differ in just how much out-of-order execution they exhibit. The MP+dmb.sy+fri-rfi-ctrlisb (message-passing) litmus test below is a message-passing test where the writes of Thread 0 are maintained in order by a dmb sy barrier and the reads c and f of Thread 1 are separated by another write to y (which is coherence<sup>2</sup> after the write to y in Thread 0, indicated by co edge), a read of y, a branch, and an isb barrier (indicated by a ctrlisb edge); the question is whether the instructions in Thread 1 create enough order to prevent the read of x reading from the initial state 0.

| MP+dmb.sy+fri-rfi-ctrlisb AArch                   |              |  |  |

|---------------------------------------------------|--------------|--|--|

| Thread 0                                          | Thread 1     |  |  |

| MOV W0,#1                                         | LDR W0,[X1]  |  |  |

| STR W0,[X1]                                       | MOV W2, #2   |  |  |

| DMB SY                                            | STR W2,[X1]  |  |  |

| MOV W2,#1                                         | LDR W3,[X1]  |  |  |

| STR W2,[X3]                                       | CBNZ W3,LC00 |  |  |

|                                                   | LC00:        |  |  |

|                                                   | ISB          |  |  |

|                                                   | LDR W4,[X5]  |  |  |

| Initial state: $0:X1=x \land 0:X3=y \land 1:X1=y$ |              |  |  |

| ∧ 1:X5=x                                          |              |  |  |

| Allowed: x=1 ∧ y=2 ∧ 1:X0=1                       |              |  |  |

| ∧ 1:X3=2 ∧ 1:X4=0                                 |              |  |  |

|                                                   |              |  |  |

$Test\ MP+dmb.sy+fri\text{-rfi-ctrlisb}\colon Allowed$

The PLDI11 Power model [22] forbids this behaviour as the read c, the write d, the read e, the isync (the Power analogous to isb) and the read f all have to commit in program order. The read c can be committed only after it has been satisfied (by the write b) which means the write b has propagated to Thread 1. Write b can propagate to Thread 1 only after the |wsync (the Power lightweight memory barrier, weaker than dmb sy) and the write a have propagated to Thread 1. Therefore, when the read f is satisfied it can only be from the write a (or coherence-after write).

In testing, the above is observed on some ARM machines ([4, Table VI] and [16, §10.6]). To allow this behaviour read e has to be able to commit before read c gets its value back. ARM architects give two distinct explanations for this behaviour. In the first explanation the microarchitecture handles reads in two distinct steps, with a read request being issued and then satisfied. In this example, after the read c has been issued the microarchitecture can guarantee its coherence order even though it has not been satisfied yet, by keeping read requests and writes to the same address ordered in the Flowing hierarchy, and continue by committing the program-order–following write to the same address d. This enables e to be committed, which resolves the control dependency and allows f to be issued and satisfied with the initial value (0), before c was satisfied.

The second explanation is that the write d is independent of the read c in every respect except coherence. This prevents d from being committed but it does not prevent the thread from forwarding d to the po-following read e which in turn can be committed before d (as the address and value of d are fixed).

Our Flowing model incorporates both of these mechanisms.

# 4. Flowing Model Design

We now discuss a selection of further aspects of the Flowing design.

#### 4.1 Coherence

Relaxed-memory processors exhibit much programmer-observable reordering of memory actions, but they typically do aim to guarantee some *coherence* property: with loads and stores to a single location appearing to execute in a global linear order.

The PLDI11 Power model guaranteed this in the storage subsystem by fiat, by maintaining a partial order of the coherence commitments between writes made so far, and in the thread semantics by allowing writes (to the same address) to be committed, and reads (to the same address) to be satisfied, only in program order.

Here the Flowing storage subsystem can easily maintain writes and read requests to the same address in-order as they flow down the hierarchy, but the thread semantics has to be more liberal to match the architects' intent, and this is further complicated by the need to restart reads. In the following paragraphs we explain how the thread subsystem guarantees the coherence order of two writes will match their program order (write-write coherence), and the coherence of two writes that were read by two reads will match the program order of the reads (read-read coherence).

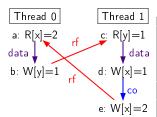

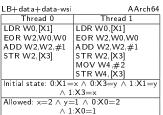

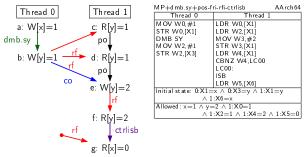

*Write-write coherence* Simply committing writes to the same address in program order would exclude the LB+data+data-wsi (load-buffering) litmus test below, which the ARM architects intend to be allowed (to date, we have not observed this behaviour in testing). We resolve this in the model by allowing writes to be committed out of order, and only passing a write to the storage when no other poafter write to the same address has been committed. This means we can commit and pass to the storage subsystem the write e: W[x]=2 before the data dependency in Thread 1 is resolved, and only later commit d: W[x]=1, without ever passing it to the storage subsystem. In hardware, the two writes might be merged together.

Test LB+data+data-wsi: Allowed

If the dependency from the read c to the write d was an address dependency the behaviour would be forbidden by the architecture, as resolving the address of the write d might raise an exception, in which case the write e must not be visible to other threads. The models therefore distinguish between the two cases by allowing a write to be committed only after all po-previous addresses have been fully determined.

**Read-read coherence** The RSW (read-from-same-write) litmus test below challenges the coherence order of reads. The model allows it in the same way as hardware, by allowing read e to be issued before the address dependency from c to d is resolved, and therefore before the read d to the same address is issued. After e is satisfied by the storage subsystem with the initial value, read request f can be issued and satisfied with the initial value as well. Only at that point can the instructions of Thread 0 commit in order and the writes and the barrier flow all the way into memory. In turn, Thread 1 issues read c and the storage satisfies it with the write b that just flowed into memory. This resolves the address dependency and allows read d to be issued and satisfied from the initial state.

<sup>&</sup>lt;sup>2</sup> Coherence is the per-location order over writes to that location that conventional multiprocessor architectures all provide.

Test RSW: Allowed

Notice that there is no coherence violation between the reads d and e as both of them read from the same write. If read d was to read from a different write than e, then e would have had to be restarted as the write e reads from might be co-before the write d reads from.

It is thus because the model allows issuing reads out of order that the model must also perform read restarts. In fact the model also allows reads to be issued out of order with write commitments. Coherence is then maintained by restarting uncommitted reads in two situations. When a read r is satisfied by a write w, if exists a po-previous read that was issued after r (i.e. the reads were issued out of order), and has already been satisfied by a write that is different than w, and w was not forwarded to r then r is restarted; otherwise all po-following reads to the same address that have been issued before r and have already been satisfied are restarted, except for reads that have been satisfied by w and reads that have been satisfied by forwarding a write that is po-after r. When a write w is committed we restart all po-following reads to the same address that have been satisfied by a different write that is not po-after w, together with all po-following reads to the same address that have been issued and not satisfied yet.

When a read is restarted all its dataflow dependents are also restarted, and the storage subsystem removes any read request issued for the read.

The restart of reads on write commitment guarantees write-read coherence. Finally read-write coherence is maintained by requiring that when a write w is committed all po-previous reads to the same address have been issued and can not be restarted.

The MP+dmb.sy+pos-fri-rfi-ctrlisb litmus test, which is observed on ARM hardware, is explained by ARM architects by allowing the write e to be committed before the reads c and d are satisfied.

Test MP+dmb.sy+pos-fri-rfi-ctrlisb: Allowed

But to do so the model must guarantee read d will not be restarted when c is satisfied. To do so and maintain read-read coherence, the model allows write e to be committed only if the reads have been issued in order, and refrains from restarting reads that are satisfied out of order if they were issued in program order. Hence the model keeps track of the order in which reads are issued (again, following hardware).

#### 4.2 New ARMv8 Memory Barriers

ARMv8 introduces a new variant of the dmb barrier, dmb |d. The regular dmb barrier orders arbitrary memory actions that occur before and after it, and also has cumulativity properties. Among other things, it orders stores that the barrier thread reads from before the dmb w.r.t. stores that it performs after, and orders stores (from the barrier thread) that occur before the barrier w.r.t. stores (from any thread) that appear logically after the barrier.

The new dmb |d orders loads that occur before the barrier with load and stores that occur after the barrier, and dmb st (also in ARMv7) orders stores that occur before the barrier with stores that occur after the barrier.

Ongoing discussions with ARM architects reveals that they intend these barriers to have weaker cumulative properties than the dmb sy, but their exact strength is still subject to debate. Our current understanding is that dmb st only has a cumulativity property with respect to stores that occur after the barrier; the situation for dmb |d is less clear and is currently under discussion in ARM.

#### 4.3 Load-Acquire/Store-Release

Another addition in AArch64 is the load-acquire and store-release instructions. According to the ARM ARM, store-release is multicopy-atomic when observed by load-acquires, a strong property that conventional release-acquire semantics does not imply. Furthermore, despite their names, these instructions are intended to be used to implement the C11 sequentially consistent load and store.

From their description in the ARM ARM, these two instructions behave somewhat like two halves of a dmb sy, where the store-release enforces cumulative order with po-previous instructions and load-acquire enforces order with po-later instructions. One might expect this will be enough to guarantee the multi-copy atomicity of store-release, but this is not the case. In the Flowing model one can imagine a read request from a load-acquire being satisfied by a write from a store-release when the two requests are adjacent in some (non root) queue. Before the read satisfaction, the load/store pair behaves like a dmb sy, preventing instructions from being reordered with them. But after the read is satisfied, half of the implicit dmb sy disappears, and instructions can be reordered with the write, breaking its multi-copy atomicity.

To guarantee the multi-copy atomicity of store-release, the Flowing model does not allow a read from load-acquire to be satisfied from a store-release write until the write has reached the memory. In addition, when such a read is satisfied from a regular write, the read does not disappear from the storage subsystem as regular reads do, instead it is marked as satisfied and reordered with the write that satisfied it. This semantics has some surprising effects the ARM architects did not expect, in particular, the litmus test in [7, §J10.2.4] (IRIW+poaas+LL) can be weakened by changing the second load in P3 and P4 to regular loads (IRIW+poaps+LL) and the behaviour will still be forbidden. The implications of these are currently being discussed with ARM.

#### 4.4 Dependencies

We say there is a load-store dependency between a load and a following store instructions, if there is a data flow from the register holding the value loaded by the load and the registers used by the store, and similarly for load-load dependency. The architecture guarantees some ordering for instructions that have load-load and load-store dependencies. Currently, ARM ARM [7, §B2.7.4] makes a distinction between 'true' and 'false' load-store data dependencies, with the intuition being that for a 'false' dependency the value read does not extensionally affect the value stored. Making this precise in a satisfactory way is problematic, as too liberal a notion of 'false' dependency (allowing more hardware optimisation) can also make it impractical to compute whether a trace is

admitted by the architecture or not. This question is currently under discussion with ARM, after we drew it to their attention, and it is possible the semantics will be strengthened to not distinguish between the two kinds of dependency; our model follows that proposal at present.

#### 4.5 Branch Prediction

Control dependencies from a load to another load are not in general respected, as hardware can speculatively reach and satisfy the second load early. For a computed branch, in principle the branch prediction hardware might guess an arbitrary address (or at least an arbitrary executable-code-page address); there seems to be no reasonable way to limit this behaviour, and one can construct litmus tests that observe it. Mathematically that is no problem, but to make the tool based on our model usable in practice, we have to approximate here, otherwise the nondeterminism (picking addresses that turn out to be incorrect) would be prohibitive.

A detailed prose description of the Flowing thread and storage subsystem is given in §7.

#### 5. Introduction to the POP Model

We now show how the POP model abstracts from the hierarchical storage subsystem structure of the Flowing model, to give a better programming model (and to combine the best of both worlds from the pros and cons of the Flowing abstraction listed in §3).

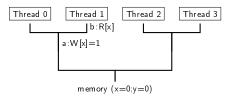

The purpose of the queues in the Flowing storage subsystem is to maintain order between requests, relaxing it subject to the reordering condition. The topology, on the other hand, determines the order in which a request becomes visible to the threads. Consider for example the write a:W[x]=1 in the first storage subsystem state diagram of §3 for WRC+addrs. It is visible to threads 0 and 1, as a read request from each of these threads can potentially flow and encounter a, but it is not visible to threads 2 and 3, as a read request issued by those would flow all the way to memory without encountering a. In the POP model we make these two notions explicit. Instead of the queues enforcing an implicit order we record an order (as a graph) over all requests, and instead of letting a fixed topology determine the order in which a request becomes visible, we record for each thread a set of requests that have become visible to it, and we allow requests to be added to these sets (subject to conditions over its place in the order).

Notice that unlike the PLDI11 storage coherence order, which is only over writes, and only relates writes to the same address, the POP storage model records an order over all requests (writes, reads and barriers) and it relates requests with different addresses. In addition, POP records propagation sets (which do not add ordering) as opposed to the PLDI11 propagation queues (which play a significant role in ordering). Moreover, in the PLDI11 model, when an event is propagated to a new thread, it takes its place in the head of the propagation queue, while in the POP model, requests that propagated to a new thread can do so from the middle of the order. Further, in the PLDI11 model the storage subsystem receives a read request from a thread and replies to it with a read response in an atomic transition, while in POP the storage subsystem receives the request and replies to it in two distinct transitions. Finally, as mentioned in the introduction, the Power sync memory barrier requires an acknowledgement to be passed from the storage subsystem to the issuing thread, while the POP model maintain memory-barrierinduced ordering without such acknowledgements.

# 5.1 Example: POP Simulating Flowing

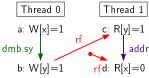

In the following we will demonstrate an execution of the MP+dmb.sy+addr litmus test below. On the thread subsystems side we will do our best to make the second load read 0. On the storage

subsystem side we will first show how the Flowing model behaves and then an analogous behaviour of the POP model.

Since there is an address dependency between the first load and the second load in Thread 1, the thread has to start by issuing the first load, c. In the Flowing storage subsystem, read c is received from Thread 1 and placed at the top of the queue associated with that thread. Similarly, in the POP storage subsystem, read c is recorded as propagated to Thread 1.

In Thread 0 now, the presence of a dmb sy between the two stores forces them (and the dmb sy) to be committed in program order. The Flowing storage model places these requests in the queue associated with Thread 0, one on top of the other, in the order they were received (i.e. program order). The POP storage model records each of these instructions as propagated to Thread 0 when it is received. In addition, when the dmb sy request is received it is recorded as being ordered after the previously received write a and when the write b is received it is recorded as being ordered after the dmb sy.

| IVIP + amb.sy+adar                              | AArch04             |  |

|-------------------------------------------------|---------------------|--|

| Thread 0                                        | Thread 1            |  |

| MOV W0,#1                                       | LDR W0,[X1]         |  |

| STR W0,[X1]                                     | EOR W2 W0 W0        |  |

| DMB SY                                          | LDR W3,[X4,W2,SXTW] |  |

| MOV W2,#1                                       |                     |  |

| STR W2,[X3]                                     |                     |  |

| Initial state: 0:X1=x \land 0:X3=y \land 1:X1=y |                     |  |

| ∧ 1:X4=x                                        |                     |  |

| Forbidden: 1:X0=1 ∧ 1:X3=0                      |                     |  |

|                                                 |                     |  |

Test MP+dmb.sy+addr: Forbidden

The Flowing storage model must flow the write b to the root queue before the read c gets there in order for c to be satisfied by b. But before it can do that it must flow the dmb sy and write a to the root, as none of these can be reordered with the others. Similarly, the POP storage subsystem must propagate the write b to Thread 1 before propagating the read c to Thread 0 in order for c to be satisfied by b. But before it can do that it must propagate the dmb sy and write a, as they are ordered before b. When the dmb sy and write b are propagated to Thread 1 they are recorded as being ordered before c.

Back in the Flowing storage subsystem, read c can flow to the root queue and get satisfied by b. In the POP storage subsystem, read c can propagate to Thread 0 and get satisfied by b.

After c was satisfied the address dependency is resolved and Thread 1 can issue read d. In the Flowing storage model, d is placed at the top of the queue associated with Thread 1 and it is clear it will not be able to read the initial value of x as the write a is in the root queue. Similarly in the POP storage model, d is recorded as propagated to Thread 1 and ordered after the dmb sy and write a, and therefore d will not be able to read the initial value of x.

A detailed prose description of the POP storage subsystem is given in §8. In the next section we describe the ISA model.

## 6. ISA Model

Handling the instruction semantics raises two problems, as noted in the introduction: the mass of detail involved, and its semantic integration with the concurrent semantics. We address both with a domain-specific language for ISA description, Sail.

The ARM ARM has 224 application-level non-FP/SIMD instructions, counting subsections of Chapter C6 *A64 Base Instruction Descriptions* (each of which defines one instruction, sometimes with several variants). Of these 224, we support all except 21 (and aspects of 4 more), relating to exceptions, debug, systemmode, and load-non-temporal-pair.

Fig. 2 shows excerpts of this. At the top is a clause of an instruction AST datatype (ast), with constructor AddSubImmediate, covering four ADD and SUB instructions. Then there is

a decoding function decodeAddSubtractImmediate that pattern-matches a 32-bit vector and constructs an element of that ast type (the body of this function is elided). For example, the ARM assembly instruction ADD X1, X2, #1 would be assembled to 0x91000441, which is decoded to AddSubImmediate(1,2,64,0,0,ExtendType\_UXTB,1). Finally there is a clause of the execute function that defines the behaviour of these instructions.

Hardware vendors differ widely in the level of detail and rigor of their instruction descriptions. The ARM ARM is relatively good in these respects: the pseudocode used is reasonably complete and close to something that could be executed, at least for sequential code (Shi et al. build a simulator based on pseudocode extracted from an ARMv7 pdf [25]). We therefore want to follow it closely, both to avoid introducing errors and to keep our definitions readable by engineers who are already familiar with the ARM ARM. Sail is designed with this in mind, and our instruction descriptions can often be line-for-line identical to those of the ARM ARM. Looking again at Fig. 2, the body of the Sail execute clause differs from the ARM ARM text [7, §C6.6.4, ADD (immediate)] only in minor details: the type annotations and concrete syntax for let. Both languages are imperative, with mutable local variables and primitives for register and memory reads and writes, and typed bit vectors.

For Sail, we developed a type system expressive enough to typecheck such code without requiring excessive type annotation or partiality. The ISA description manipulates bitvectors of differing sizes and start-indices, which we support with dependent types over Int. For example, Fig. 2 includes a variable 'R of kind Int, bounded to be either 32 or 64, to accommodate those two flavours of instructions; the code involves bitvector types bit['R] of that length and also a singleton type [:'R:] (really, an integer range type from 'R to 'R). This instruction happens not to index into a vector; in those that do, the indices use such range types (not necessarily singletons). Type inference and checking involve polynomial equations and inequalities, undecidable in general but not a problem in practice, as the constraints that actually arise here are relatively simple. Sail also provides implicit type coercions between numbers, vectors, individual bits, and registers, again keeping the specification readable. A simple effect system tracks the presence of memory and register operations, identifying pure code. The language has first-order functions and pattern-matching, including vector concatenation patterns (as used in decodeAddSubtractImmediate). We have also used Sail for related work on IBM Power ISA semantics [12] (Power uses a broadly similar but different and less rigorous pseudocode); it is expressive enough for both.

The dynamic semantics of Sail is where we see the integration with the concurrency thread-subsystem semantics: unlike a sequential or sequentially consistent system, we cannot simply use a state-monad semantics that updates a global register and memory state. Instead, the Sail semantics (expressed as an interpreter in Lem) makes register and memory requests to the thread semantics, providing a continuation of the instruction state. It also has to announce to the thread semantics the point at which the address of a memory write becomes available – an example where we differ from the ARM ARM pseudocode as written there, adding extra information. The thread semantics further needs to know the register footprint of an instruction and intra-instruction register dataflow information (e.g. the register reads that may feed into a memory address); the Sail interpreter calculates these with an exhaustive symbolic taint-tracking execution.

# 7. The Flowing Model in Detail

#### 7.1 The Storage Subsystem/Thread Interface

The model is expressed in terms of read, write, and barrier requests. Read and write requests include the kind of the memory access (e.g. exclusive, release, acquire), the ID of the issuing thread and the memory access address. Write requests also include a value. Barrier requests include the issuing thread ID.

When we refer to a write or read request without mentioning the kind of request we mean the request can be of any kind.

The storage subsystem and a thread subsystem can exchange messages through synchronous transitions:

- a write request can be passed to the storage subsystem by a thread Commit store instruction transition coupled with a storage subsystem Accept request transition;

- a (memory) barrier request can be passed to the storage subsystem by a thread Commit barrier instruction transition coupled with a storage subsystem Accept request transition;

- a read request can be passed to the storage subsystem by a thread Issue read request transition coupled with a storage subsystem Accept request transition; and

- a read response can be returned from the storage subsystem to a thread by a storage subsystem Satisfy read from segment or Satisfy read from memory transition coupled with a thread Satisfy memory read from storage response transition.

# 7.2 Storage Subsystem States

The Flowing storage subsystem state includes:

- thread\_ids, the set of thread IDs that exist in the system;

- topology, a data structure describing how the segments are connected to each other;

- thread\_to\_segment, a map from thread IDs to segments, associating each thread with its leaf segment;

- buffers, a map from segments to list of requests associating each segment with the requests queued in that segment;

- reordered, a set of request pairs that have been reordered w.r.t. each other; and

- memory, a map from memory addresses to the most recent write request to that address to reach memory.

#### 7.3 Storage Subsystem Transitions

**Accept request** A request r from thread r.tid can be accepted if:

- 1. r has not been accepted before (i.e. r is not in buffers); and

- 2. r.tid is in thread\_ids.

Action: add r to the top of  $buffers(thread\_to\_segment(r.tid))$ .

**Flow request** A request r can flow from segment s1 to s2 if:

- 1. r is at the bottom of buffers(s1); and

- 2. s1 is a child of s2 in topology.

#### Action:

- 1. remove *r* from *buffers(s1)*;

- 2. add r to the top of buffers(s2); and

- 3. remove from *reordered* any pair that contains *r*.

**Reorder requests** Two requests  $r_new$ ,  $r_nold$  that appear consecutively in *buffers(s)* ( $r_new$  nearer the top) can be reordered if:

- 1. (*r\_new*, *r\_old*) does not appear in *reordered* (i.e. they have not been reordered (in segment *s*) with each other before (preventing live lock); and

- 2.  $r_new$  and  $r_nold$  satisfy the reorder condition (§7.4).

#### Action:

- 1. switch the positions of  $r\_new$  and  $r\_old$  in buffers(s); and

- 2. record the reordering of *r\_new* and *r\_old* (by adding the pair (*r\_new*, *r\_old*) to *reordered*).

Satisfy read from segment Two requests, r\_read, r\_write, can generate a read response to thread r\_read.tid if:

- 1. r read is a read request;

- 2. *r\_write* is a write request;

- 3. r\_read, r\_write appear consecutively in buffers(s) for some segment s, with r\_read closer to the top (newer); and

- 4. *r\_read* and *r\_write* are to the same address.

#### Action:

- send a read response for request r\_read to thread r\_read.tid, containing r\_write; and

- 2. remove *r\_read*.

**Satisfy read from memory** A read request  $r\_read$  from thread  $r\_read.tid$  can generate a read response to thread  $r\_read.tid$  if  $r\_read$  is at the bottom of buffers(s), where s is the root segment in topology. Action:

- send a read response for request r\_read to thread r\_read.tid, containing the write stored in memory for the address r\_read.addr; and

- 2. remove *r\_read*.

**Flow write to memory** The write request  $r\_write$  can be stored into memory if:  $r\_write$  is at the bottom of *buffers*(s), where s is the root segment in *topology*. Action:

- 1. update *memory* to map the address *r\_write.addr* to *r\_write*; and

- 2. remove  $r\_write$  from buffers(s) and reordered.

**Flow barrier to memory** A barrier request  $r\_barr$  can be discarded if:  $r\_barr$  is at the bottom of *buffers(s)*, where s is the root segment in *topology*. Action: remove  $r\_barr$ .

#### 7.4 Auxiliary Definitions for Storage Subsystem

**Reorder condition** Two requests  $r_new$  and  $r_nold$  are said to meet the *reorder condition* if:

- 1. neither one of *r\_new*, *r\_old* is a dmb sy; and

- if both r\_new and r\_old are memory access requests, they are to different addresses.

#### 7.5 Thread States

The state of a single hardware thread includes:

- thread\_id, a unique identifier of the thread;

- register\_data, general information about the available registers, including name, bit width, initial bit index and direction;

- initial\_register\_state, the initial values for each register;

- initial\_fetch\_address, the initial fetch address for this thread;

- *instruction\_tree*, a data structure holding the instructions that have been fetched in program order; and

- read\_issuing\_order, a list of read requests in the order they

were issued to the storage subsystem.

# 7.6 Instruction State

Each instruction in the instruction\_tree has a state including:

- program\_loc, the memory address where the instruction's opcode resides:

- instruction\_kind, the kind of the instruction (e.g. load-acquire);

- regs\_in, the input registers, for dependency calculation;

- regs\_out, the output registers, for dependency calculation;

- reg\_reads, accumulated register reads;

- reg\_writes, accumulated register writes;

- mem\_read, one of none, pending a, requested a, write\_read\_from w, where a is a memory address and w is a memory write;

- mem\_write, one of none, potential\_address a, pending w, committed w, where a is a memory address and w is a memory write;

- *committed*, set to *true* when the instruction can no longer affect the memory model (the Sail interpreter might still need to complete the execution of the ISA definition);

- finished, set to true only after committed is set to true and the Sail interpreter has finished executing the ISA definition; and

- micro\_op\_state, the meta-state of the instruction, one of plain interpreter\_state (ready to make a Sail interpreter transition from interpreter\_state), pending\_mem\_read read\_cont (ready to perform a read from memory) or potential\_mem\_write write\_cont (ready to perform a write to memory) where read\_cont is a Sail interpreter continuation that given the value read from memory returns the next interpreter state, and write\_cont is a Sail interpreter continuation that given a boolean value (that indicates if the store was successful) returns the next interpreter state.

Instructions that have been fetched (i.e. in <code>instruction\_tree</code>) and have a <code>finished</code> value of <code>false</code> are said to be <code>in-flight</code>. Instructions that have a <code>committed</code> value of <code>true</code> are said to be <code>committed</code>. Load instructions with the value <code>requested</code> for <code>mem\_read</code> are said to have an <code>outstanding read request</code>, and if they have the value <code>write\_read\_from</code> they are said to be <code>satisfied</code>. Store instructions with <code>mem\_write = pending w</code> are said to have a <code>pending write</code>. We say instruction <code>i</code> has <code>fully determined address</code> if all instructions that write to input registers of <code>i</code> that affect memory address calculation in the ISA definition of <code>i</code> are committed. We say <code>i</code> is <code>fully determined</code> if all instructions that write to input registers of <code>i</code> are committed.

#### 7.7 Thread Transitions

*Sail interpreter step* An instruction *i* in meta-state *plain inter-preter\_state* can perform an interpreter step as follows:

- if <a href="interpreter\_state">interpreter\_state</a> indicates a memory-read event: set <a href="interpreter\_state.read\_addr">interpreter\_state.read\_addr</a> and update the instruction meta-state to <a href="pending\_mem\_read">pending\_mem\_read</a> interpreter\_state.read\_cont;

- if interpreter\_state indicates a memory-write-address event: set mem\_write to potential\_address interpreter\_state.write\_addr and update the instruction meta-state to plain interpreter\_state.next;

- if interpreter\_state indicates a memory-write-value event: set mem\_write to pending w (where w is a write request with the value interpreter\_state.write\_value and the address that was in mem\_write before) and update the instruction meta-state to potential\_mem\_write interpreter\_state.write\_cont;

- if interpreter\_state indicates a register-read event: look in instruction\_tree for the most recent po-previous instruction, i' that has interpreter\_state.reg in i'.regs\_out. If interpreter\_state.reg is not in i'.reg\_writes the transition is disabled. Otherwise, add interpreter\_state.reg to i.reg\_reads and update the meta-state of i to plain (interpreter\_state.reg\_count val) (where val is the value written to the register by i');

- if interpreter\_state indicates a register-write event: add interpreter\_state.reg to i.reg\_writes and update the meta-state of i to plain interpreter\_state.next; and

- if *interpreter\_state* indicates an internal step: update the metastate of *i* to *plain interpreter\_state.next*.

**Fetch instruction** An instruction *i*, from address *loc*, can be fetched, following its program-order predecessor *i*' if:

- 1. *i*' is in *instruction\_tree*;

- loc is a possible next fetch address for i' according to the ISA model;

- 3. none of the successors of i' in instruction\_tree are from loc; and

- 4. *i* is the instruction of the program at *loc*.

The possible next fetch addresses allow speculation past calculated jumps and conditional branches; they are defined as:

- for a non-branch/jump instruction, the successor instruction address;

- 2. for a jump to constant address, that address;

- for a conditional branch, the possible addresses for a jump<sup>3</sup> together with the successor; and

- 4. for a jump to an address which is not yet fully determined (i.e., where there is an uncommitted instruction with a dataflow path to the address), any address. This is (necessarily) approximated in our implementation, c.f. §4.5.

Action: construct an initialized instruction instance, including static information available from the ISA model such as *instruction\_kind*, *regs\_in*, *regs\_out*, and add it to *instruction\_tree* as a successor of *i*'.

This is an internal action of the thread, not involving the storage subsystem, as we assume a fixed program rather than modelling fetches with memory reads; we do not model self-modifying code.

**Issue read request** An in-flight instruction i in meta-state *pending\_mem\_read read\_cont* can issue a read request of address a to the storage subsystem if:

- i.mem\_read has the value pending a, i.e., any other reads with dataflow path to the address have been satisfied, though not necessarily committed, and any arithmetic on such a path completed; and

- 2. all po-previous dmb sy and isb instructions are committed.

#### Action:

- 1. send a read-request to the storage subsystem;

- 2. change i.mem read to requested a; and

- 3. update read\_issuing\_order to note that the read was issued last.

Satisfy memory read from storage response A read response with write w, for read request from instruction i in meta-state pending\_mem\_read read\_cont can always be received. Action:

- 1. if *i.mem\_read* does not have the value *requested* the response is ignored (this can happen when the read is satisfied by write forwarding while waiting for the response); else

- 2. if there exists a po-previous load instruction to the same address that was issued after *i* (i.e., issued out of order) and was satisfied by a write that is not *w*, set *i.mem\_read* to *pending*; else

- 3. for every in-flight instruction *i*' that is po-after *i* and has read from a write to the same address as *i* that is not *w* and not posuccessor of *i*, restart *i*' and its data flow dependents;

- 4. change i.mem\_read to write\_read\_from w; and

- 5. update the meta-state of *i* to *plain* (*read\_cont w.value*).

Satisfy memory read by forwarding an in-flight write A pending memory write w from an in-flight store instruction i' can be forwarded directly to a load instruction i in meta-state pending\_mem\_read read\_cont if:

- 1. *i.mem\_read* has the value *pending w.address* or *requested w.address*; and

- i' is po-before i, there is no other store instruction to the same address in between them, and there is no other load instruction in between them that has read from a different store instruction to the same address.

#### Action:

- 1. for every in-flight instruction *i*" that is po-after *i* and has read from a write to the same address as *i* that is not *w* and not posuccessor of *i*, restart *i*" and its data flow dependents;

- 2. change i.mem\_read to write\_read\_from w; and

- 3. update the meta-state of *i* to *plain* (*read\_cont w.value*).

**Commit store instruction** A store instruction i in meta-state potential\_mem\_write write\_cont and with pending write w can be committed if:

- 1. *i* is fully determined;

- 2. all po-previous conditional branches are committed;

- 3. all po-previous dmb sy and isb instructions are committed;

- all po-previous memory access instructions have a fully determined address; and

- 5. all po-previous instructions that read from the same address have either an outstanding read request or are satisfied, and cannot be restarted (see §7.8).

#### Action:

- 1. restart any in-flight loads (and their dataflow dependants) that:

- (a) are po-after *i* and have read from the same address, but from a different write and where the read could not have been by forwarding an in-flight write that is po-after *i*; or

- (b) have issued a read request that has not been satisfied yet.

- 2. if there is no committed po-following store to the same address, send a write request to the storage subsystem;

- 3. record the store as committed (i.e. set *i.mem\_write* to *committed* w and *committed* to *true*); and

- 4. update the meta-state of *i* to *plain* (*write\_cont true*).

**Commit barrier instruction** A barrier instruction *i* in meta-state plain interpreter\_state can be committed if:

- 1. interpreter\_state indicates a barrier event is pending;

- 2. all po-previous conditional branches are committed;

- 3. all po-previous barriers (of any kind) are committed;

- 4. if *i* is isb, all po-previous memory access instructions have a fully determined address; and

- 5. if *i* is dmb sy, all po-previous memory access instructions are committed.

#### Action:

- 1. record the barrier as committed (i.e. set committed to true); and

- 2. update the meta-state of *i* to *plain interpreter\_state.next*.

*Finish instruction* An in-flight instruction i in meta-state *plain interpreter\_state* can be finished if:

- 1. *interpreter\_state* indicates the execution of the ISA definition has finished:

- 2. if *i* is a load instruction:

- (a) all po-previous dmb sy and isb instructions are committed;

- (b) let i' be the store instruction to the same address as i that appears last in program order before i:

- i. if i' was forwarded to i, i' is fully determined, otherwise

i' is committed;

- ii. all memory access instructions, po-between *i'* and *i*, have a fully determined address; and

- iii. all load instructions to the same address as i, that are po-between i' and i, are committed.

- 3. *i* is fully determined; and

- 4. all po-previous conditional branches are committed.

#### Action:

- 1. if *i* is a branch instruction, abort any untaken path of execution, i.e., any in-flight instruction that are not reachable by the branch taken in *instruction\_tree*; and

- 2. record the instruction as finished, i.e., set *finished* (and *committed*) to *true*.

# 7.8 Auxiliary Definitions for Thread Subsystem

**Restart condition** To determine if instruction i might be restarted we use the following recursive condition: i is an in-flight instruction and at least one of the following holds,

$<sup>^3</sup>$  In AArch64, all the conditional branch instructions have a constant address.

- there exists an in-flight store instruction s such that applying the action of the Commit store instruction transition to s will result in the restart of i;

- 2. there exists an in-flight load instruction *l* such that applying the action of the Satisfy memory read from storage response transition to *l* will result in the restart of *i* (even if *l* is already satisfied);

- 3. *i* has an outstanding read request that has not been satisfied yet, and there exists a load instruction po-before *i* that has an outstanding read request to the same address (maybe already satisfied) after *i*; or

- 4. there exists an in-flight instruction *i'* that might be restarted and an output register of *i'* feeds an input register of *i*.

# 8. The POP Model

#### 8.1 The Storage Subsystem/Thread Interface

The storage subsystem and a thread subsystem can exchange messages through synchronous transitions:

- a write request can be passed to the storage subsystem by a thread Commit store instruction transition coupled with a storage subsystem Accept request transition;

- a (memory) barrier request can be passed to the storage subsystem by a thread Commit barrier instruction transition coupled with a storage subsystem Accept request transition;

- a read request can be passed to the storage subsystem by a thread Issue read request transition coupled with a storage subsystem Accept request transition; and

- a read response can be passed from the storage subsystem to a thread by a storage subsystem

Send read-response to thread transition coupled with a thread Satisfy memory read from storage response transition.

In addition to the above, when a load instruction is restarted in the thread subsystem, all its read-requests are removed from the storage subsystem.

#### 8.2 Storage Subsystem State

The POP storage subsystem state includes:

- thread ids, the set of thread IDs that exist in the system;

- requests\_seen, the set of requests (memory read/write requests and barrier requests) that have been seen by the subsystem;

- order\_constraints, the set of pairs of requests from requests\_seen. The pair (r\_old,r\_new) indicates that r\_old is before r\_new (r\_old and r\_new might be to different addresses and might even be of different kinds); and

- requests\_propagated\_to, a map from thread IDs to subsets of requests\_seen, associating with each thread the set of requests that has propagated (potentially visible) to it.

# 8.3 Storage Subsystem Transitions

**Accept request** A request  $r_new$  from thread  $r_new.tid$  can be accepted if:

- r\_new has not been accepted before (i.e., r\_new is not in requests\_seen); and

- 2. *r\_new.tid* is in *thread\_ids*.

#### Action:

- 1. add  $r_new$  to  $requests_seen$ ;

- 2. add  $r_new$  to  $requests\_propagated\_to(r_new.tid)$ ; and

- 3. update *order\_constraints* to note that *r\_new* is after every request *r\_old* that has propagated to thread *r\_new.tid*, and *r\_new* and *r\_old* do not meet the Flowing *reorder condition* (see Reorder condition).

**Propagate request to another thread** The storage subsystem can propagate request *r* (by thread *tid*) to another thread *tid*' if:

- 1. r has been seen before (i.e., r is in requests\_seen);

- 2. r has not yet been propagated to thread tid'; and

- 3. every request that is before *r* in *order\_constraints* has already been propagated to thread *tid*'.

#### Action:

- 1. add *r* to *requests\_propagated\_to(tid')*; and

- 2. update *order\_constraints* to note that *r* is before every request *r\_new* that has propagated to thread *tid'* but not to thread *tid*, where *r\_new* and *r* do not meet the Flowing *reorder condition* (see Reorder condition).

**Send read-response to thread** The storage subsystem can send a read-response for read request  $r\_read$  to thread  $r\_read.tid$  containing the write request  $r\_write$  if:

- 1. *r write* and *r read* are to the same address;

- r\_write and r\_read have been propagated to (exactly) the same threads:

- 3. r\_write is order\_constraints-before r\_read; and

- 4. any request that is *order\_constraints*-between *r\_write* and *r\_read* has be *fully-propagated* (§8.4) and is to a different address.

#### Action:

- send thread r\_read.tid a read-response for r\_read containing r\_write; and

- 2. remove *r\_read*.

#### 8.4 Auxiliary Definitions for Storage Subsystem

*Fully propagated* Request *r* is said to be fully-propagated if it has been propagated to all threads and so has every request that is *order constraints*-before it.

**Removing read request** When a read request is removed from the storage subsystem, due to restart of the instruction in the thread subsystem or satisfaction, first *order\_constraints* is restricted to exclude the request; it is then further restricted by applying the *reorder condition* to each pair of ordered requests and removing pairs that can be reordered; finally the transitive closure of the result is calculated.

#### 9. POP Abstracts Flowing

We now show that the POP model does indeed abstract the Flowing model, as intended. The detailed proof is available online; here we outline the statement of the theorem and the overall structure of the proof. A Flowing *trace* is a sequence

$$(tss_0, flo_0), a_1, (tss_1, flo_1), \ldots, a_n, (tss_n, flo_n)$$

where each  $tss_i$  denotes a thread subsystem state,  $flo_i$  denotes a Flowing storage subsystem state and for each  $i \in [1,n]$  the transition  $a_i$  is enabled at the Flowing system state  $f = (tss_{i-1}, flo_{i-1})$  and when taken leads to  $f' = (tss_i, flo_i)$ , written as  $f \stackrel{a_i}{\longrightarrow}_{\mathcal{F}} f'$ . We define the dual notion for POP traces with a POP system state (tss, pop), where pop is a POP storage subsystem state. We say that a Flowing trace  $tr_{\mathcal{F}}$  is equivalent to a POP trace  $tr_{\mathcal{P}}$  if the last system state in each trace has identical thread subsystem states.

We prove that POP soundly relaxes Flowing by establishing a simulation relation from Flowing to POP which for a given Flowing trace generates an equivalent POP trace. Since the thread subsystem state has full information about the execution of the instructions, equivalence of traces implies identical program behaviour.

**Theorem 1** (POP relaxes Flowing). Let  $tr_{\mathcal{F}}$  be a Flowing trace ending at Flowing system state (tss, flo). Then there exists a POP

trace  $tr_{\mathcal{P}}$  which ends at POP system state (tss', pop) such that tss = tss'.

#### 10. Commutativities

Exploring all architecturally allowed outcomes of concurrent test programs is computationally expensive. In any state of the model multiple transitions might be enabled, and any possible trace of these transitions might produce a new outcome. From the definition of the model, however, it is clear that the order in which the abstract machine takes certain transitions does not matter: certain thread-internal transitions can be reordered and the outcome will be the same. We proved this for particular kinds of transitions and implemented an optimisation of the tool we describe below that uses this result to improve the performance of exhaustively exploring the possible behaviours of concurrent programs.

The property we proved is the following: assume transition t takes the abstract machine from state  $s_0$  to s, and transition t' from  $s_0$  to s'. Then for particular types of transitions t the model only needs to explore the traces starting with t, because in s transition t' is enabled again and either

- in s', transition t is enabled and taking t in s' produces the same state as taking t' in s; or

- taking transition t' in state s results in s'.

**Theorem 2.** Let  $t, t' \in enumerate$ -transitions-of-system  $s_0$  and assume t is a thread-internal transition, an instruction-finish transition, a register read or write transition, a potential-memory-write transition, or a fetch transition, and neither t nor t' are fetch transitions directly po-after a branch. Then

$$(t \in enumerate-transitions-of-system \ s' \land \qquad (1)$$

$$t' \in enumerate-transitions-of-system \ s \land \qquad \qquad state-after-transition \ s' \ t = state-after-transition \ s \ t') \lor \qquad (t' \in enumerate-transitions-of-system \ s \land \qquad \qquad (2)$$

$$system-state-after-transition \ s \ t' = s')$$

The proof (available online) is by case analysis on the transition kinds of t and t'. The reason the second clause in the statement above is needed is that t might be enabled by an instruction i that can be subject to restart, for example by a storage read response transition t', or part of a speculatively executed branch that might be aborted when the branch is resolved. In these cases, when taking transition t the instruction t makes progress which is "overwritten" when taking transition t'.

#### 11. Exploration Tool

We have built a tool that lets one explore, interactively or exhaustively, all the executions admitted by the model for small test programs, either litmus tests or conventional ARMv8 ELF executables. The core of the tool is OCaml code automatically generated by the Lem compiler from the model definition (giving reasonable confidence that it is executing the model as specified), to which we add a driver and user interface code.

The exhaustive mode of the tool takes a litmus test as an input and produces a list of all the observable final states (using a memoised search), together with an example trace for each one; it also evaluates the litmus test final-state assertion. We use this on a cluster and a large server machine for bulk litmus test and ISA test validation.