# Transport property study of MgO-GaAs(001) contacts for spin injection devices

Jean-Christophe Le Breton, S. Le Gall, Guy Jézéquel, Bruno Lépine, Philippe Schieffer, Pascal Turban

#### ▶ To cite this version:

Jean-Christophe Le Breton, S. Le Gall, Guy Jézéquel, Bruno Lépine, Philippe Schieffer, et al.. Transport property study of MgO-GaAs(001) contacts for spin injection devices. Applied Physics Letters, 2007, 91 (17), pp.172112. 10.1063/1.2802727. hal-00908143

HAL Id: hal-00908143

https://hal.science/hal-00908143

Submitted on 22 Nov 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Transport property study of MgO-GaAs(001) contacts for spin injection devices

J. C. Le Breton, S. Le Gall, G. Jézéquel, B. Lépine, P. Schieffer, and P. Turban

Citation: Applied Physics Letters 91, 172112 (2007); doi: 10.1063/1.2802727

View online: http://dx.doi.org/10.1063/1.2802727

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/91/17?ver=pdfcov

Published by the AIP Publishing

### Re-register for Table of Content Alerts

Create a profile.

Sign up today!

## Transport property study of MgO–GaAs(001) contacts for spin injection devices

J. C. Le Breton, S. Le Gall, G. Jézéquel, B. Lépine, P. Schieffer, a) and P. Turban Equipe de Physique des Surfaces et Interfaces, UMR 6627, CNRS-Université de Rennes 1, Campus de Beaulieu, Bât 11C, 35042 Rennes Cedex, France

(Received 4 September 2007; accepted 5 October 2007; published online 25 October 2007)

The electrical properties of Au/MgO/n-GaAs(001) tunnel structures have been investigated with capacitance-voltage and current-voltage measurements at room temperature with various MgO thicknesses between 0.5 and 6.0 nm. For an oxide thickness higher than 2 nm and for low bias voltages, the voltage essentially drops across the oxide and the structure progressively enters the high-current mode of operation with increasing reverse bias voltage, the property sought in spin injection devices. In this mode, we demonstrate that a large amount of charge accumulates at the MgO/GaAs interface in interface traps located in the semiconductor band gap. © 2007 American Institute of Physics. [DOI: 10.1063/1.2802727]

Electrical spin injection from a ferromagnetic metal into semiconductor structures is essential to realize functional devices based on spins in semiconductors. In conventional ferromagnetic metal/semiconductor contacts, the large conductivity mismatch between the two materials prevents efficient spin injection.<sup>2-4</sup> However, spin injection can be achieved by a tunnel effect through a thin insulating barrier inserted between the ferromagnetic metal spin source and the semiconductor, as soon as the condition for efficient spin injection established by Fert and Jaffrès<sup>4</sup> is fulfilled. Although it was shown in recent studies that a CoFe/MgO tunnel spin injector can provide a high polarization of electrons in a GaAs based structure,<sup>5</sup> the fundamental mechanisms governing the current injection in this structure are not clearly understood so far. The purpose of this paper is to investigate the mode of operation and the electrical properties of Au/MgO/n-GaAs(001) tunnel structures. In particular, we show that these structures can enter the high-current mode of operation under applied reverse bias voltage (the spin injection condition) because it is possible to modify the charge accumulated in the trap states at the MgO/GaAs interface with the reverse bias.

Au/MgO/GaAs(001) structures were grown by molecular beam epitaxy (MBE). Some details about the preparation of the MgO/GaAs(001) samples can be found elsewhere. In brief, 1.5  $\mu$ m thick Si *n*-doped (4×10<sup>16</sup> cm<sup>-3</sup>) GaAs buffer layers were first grown on  $n^+$ -GaAs(001) substrate using standard MBE conditions. The MgO layers between 0.5 and 6 nm were then deposited at room temperature (RT) by the evaporation of high purity MgO powder at approximately 0.06 nm/min under an  $O_2$  atmosphere of  $5 \times 10^{-7}$  Torr on an As-rich GaAs(001)- $(2 \times 4)$  surface. Finally, the 30 nm thick Au metal contacts of 250, 350, or 500 µm in diameter were deposited in situ at RT from an effusion cell using a shadow mask. The capacitance-voltage (C-V) measurements were carried out using a HP4284 LCR meter with a sinusoidal voltage amplitude of 30 mV and a frequency between 20 and 1 MHz, and the current-voltage (I-V) measurements were obtained using a Keithley K617 electrometer. All C-V and

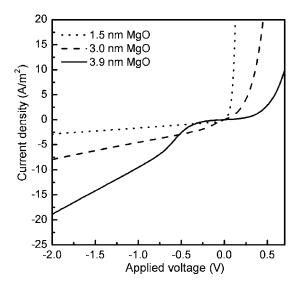

Figure 1 shows measured current density–voltage (J-V)characteristics for various MgO thicknesses. As can be seen in Fig. 1, for an oxide thickness of 1.5 nm, the structure shows a rectifying behavior. This indicates that the voltage drop takes place mainly across the semiconductor depletion layer, as in intimate metal/semiconductor contacts, and that the barrier height under bias  $\Phi_R$  ( $\Phi_R$  is defined as the energy difference between the GaAs conduction band minimum at the MgO/GaAs interface and the Fermi level in the metal under bias) weakly evolves with the applied voltage  $(V_a)$ . From an analysis of the J-V characteristic in the forward direction using thermionic model, we obtain a zero-bias barrier height of 0.65 eV and an ideality factor of 1.12. The ideal factor near unity indicates that thermionic emission is the dominant mechanism in this structure. Upon increasing the oxide thickness, we observe that the rectifying characteristic progressively disappears. For instance, for an oxide thickness of 3.9 nm, the structure progressively enters a high-current mode of operation with increasing reverse bias voltage (under -1 V, a high reverse current density of about

FIG. 1. *J-V* curves measured at RT for MgO thicknesses of 1.5, 3.0, and 3.9 nm.

I-V characterizations were made in the dark and at RT.

a) Author to whom correspondence should be addressed; electronic mail: philippe.schieffer@univ-rennes1.fr

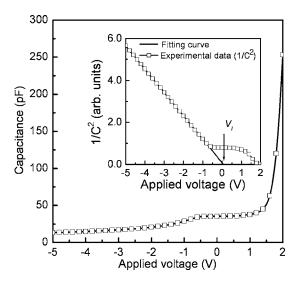

FIG. 2. High-frequency (1 MHz) C-V curve measured at RT with a voltage sweep rate of  $\sim$ 0.1 V/s for an MgO thickness of 3.9 nm and a Au contact of 250  $\mu$ m in diameter. The inset shows the corresponding  $1/C^2$  curve compared to the linear fitting curve in the deep depletion regime ( $V_a$ <-0.7 V).  $V_I$  is the voltage intercept of the extrapolated  $1/C^2$  curve with the voltage axis

10 A/m² is obtained). This result suggests that the presence of the MgO layer causes a reduction in barrier height  $\Phi_B$  with the increasing reverse bias voltage. It is interesting to note that due to the reduction of  $\Phi_B$ , the reverse current density of the structure with 3.9 nm MgO thickness may actually be greater than that of the structure with 1.5 nm MgO thickness. For reverse bias voltages higher than 0.7 V, the *J-V* curve is linear indicating that the structure operates in the Ohmic mode with a differential resistance of 0.1  $\Omega/\text{m}^2$ . Although the reverse current density strongly increases in reverse bias due to the reduction of the barrier height, the condition for efficient spin injection as calculated by Fert and Jaffrès for a metal/semiconductor/metal structure is still not fulfilled. The interface contact resistance is indeed too large by five orders of magnitude.

To obtain further information on the mode of operation of the metal/oxide/semiconductor (MOS) structure, we have performed capacitance measurements. Figure 2 shows the C-V characteristic at 1 MHz for MgO thickness of 3.9 nm. No detectable hysteresis effects were observed in the C-V loops taken with voltage sweep rate going up to 2 V/s, which means that the structure operates in the steady-state mode. Considering that the interface traps do not respond to the alternative excitation at 1 MHz, the total capacitance is a series combination of the oxide capacitance  $(C_{OX})$  and the semiconductor capacitance  $(C_{SC})$ . As long as the structure does not enter the accumulation mode, the  $C_{\rm OX}$  value is much larger than the  $C_{\rm SC}$  value and, consequently, the measured capacitance is essentially that of the depletion layer in GaAs. To calculate the  $C_{\rm OX}$  value, we have considered the geometric capacitance of the MgO layer with a relative dielectric constant of 8.0.

The C-V curve in Fig. 2 exhibits an almost flat step between -0.7 and 1.0 V, which indicates that the depletion width is only weakly changed in this voltage range. At  $V_a$ =0 V, the estimated band bending, using depletion approximation, is 0.7 eV. In fact, the large plateau in the C-V curve can be interpreted as being caused by trap states located at the MgO/GaAs interface in the band gap of GaAs.

This interpretation was proposed to explain the presence of similar plateau in C-V curves of MOS capacitors. 10 Let us assume that the interface trapped charges are in equilibrium with the semiconductor, where the quasi-Fermi level is flat and are located in the semiconductor band gap at the interface. As the bias voltage decreases, the quasi-Fermi level at the MgO/GaAs interface moves toward the valence band maximum. When interface states cross the quasi-Fermi level, they become empty (by emission and/or recombination processes), and, consequently, the interface charge is changed. Thus, if the interface trap distribution is continuous in the band gap of the semiconductor and presents a high density, a slight change in semiconductor band bending causes a large modification of the charge density at the interface. Such a plateau region can also be observed for MOS structures operating under strong-inversion conditions. However, in this case, we expect a capacitance value (at high frequency) per unit area of  $5.3 \times 10^{-4}$  F/m<sup>2</sup>. The measured value (per unit area) at zero-bias voltage is larger  $(7.1 \times 10^{-4} \text{ F/m}^2)$ , excluding the formation of an inversion layer at the interface, in our case in the voltage range of the plateau.

Since the current density injected in the semiconductor through the MgO barrier is high in the forward direction and as the oxide capacitance is only known with a large error, it is then difficult to obtain an accurate estimate of the distribution of the interface traps density ( $D_{\rm it}$ ) using the conductance or capacitance methods. However, using the conductance method we have obtained between 0.1 and 0.3 eV above the GaAs midgap a  $D_{\rm it}$  value of about 4  $\times$  10<sup>13</sup> states/cm²/eV, which is a rather large value.

Let us now discuss the C-V characteristic for the large negative bias voltages ( $V_a < -0.7 \text{ V}$ ). The capacitance increases with the applied voltage and the corresponding  $1/C^2$ vs  $V_a$  curve (inset of Fig. 2) is a straight line. The value of the doping concentration deduced from the slope of the curve agrees well with that of the GaAs buffer layer, and the intercept of the straight line with the voltage axis gives a  $\Phi_R$ value of 0.1 eV. 12 From these observations, it is clear that for large negative bias voltages, a nonequilibrium deep depletion mode occurs. Indeed, at thermal equilibrium, in the stronginversion mode, the capacitance should be constant. The absence of the inversion charge in the valence band of the GaAs can be related here to the long response time of the minority carriers in GaAs and the high reverse current density in the structure.<sup>13</sup> These results also show that in this regime, the barrier  $\Phi_B$  does not evolve significantly with the applied voltage, and the voltage drop across the MgO layer remains mainly constant: the further decrease of the bias voltage falls entirely over the GaAs depletion layer.

The fact that  $\Phi_B$  remains constant for applied voltage below -0.7 V can be explained as follows: <sup>14</sup> for  $V_a < -0.7 \text{ V}$ , the tunnel current becomes high enough so that the electron injection from the metal to the interface trap states compensates any increase of positive charge in these states. As a result, it is not possible to accumulate more positive charge in the interface states for higher reverse bias voltages.

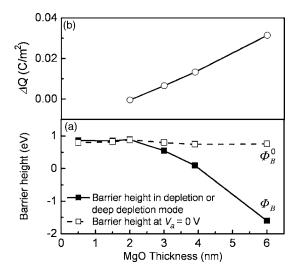

Under (sufficiently large) reverse bias voltages, the linear dependence of the  $1/C^2$  vs  $V_a$  curves has been observed for the whole range of oxide thicknesses, showing that the MOS structures operate under depletion or deep depletion mode. In Fig. 3(a), we show the evolution of the  $\Phi_B$  value extracted from these curves as a function of the MgO thick-

FIG. 3. (a) Evolution of  $\Phi_B$  and  $\Phi_B^0$  as a function of the MgO thickness.  $\Phi_B$  ( $\Phi_B^0$ ) corresponds to the barrier height under depletion or deep depletion mode (for the nonpolarized structure). (b) Evolution of the additional positive charge per unit area  $\Delta Q$  accumulated in the interface traps  $[\Delta Q = C_{\text{OX},A}(\Phi_B^0 - \Phi_B)/e$ , where  $C_{\text{OX},A}$  is the oxide capacitance per unit area and e is the elementary charge].

ness. The barrier height value for the nonpolarized structure  $\Phi_B^0$  is also presented in Fig. 3(a). As can be seen, no significant difference between  $\Phi_B$  and  $\Phi_B^0$  for MgO thicknesses lower than 2 nm appears. This means that the voltage drops almost entirely across the semiconductor, as already deduced from the analysis of the J-V characteristics. Here, the interface states are probably in equilibrium with the metal and no significant charge can be accumulated at the MgO/GaAs interface under reverse bias voltage. For oxide thicknesses higher than 2 nm, the difference between  $\Phi_B^0$  and  $\Phi_B$  increases with the oxide thickness, which demonstrates that the maximum voltage drop across the MgO layer also increases. Figure 3(b) shows the corresponding evolution of the additional positive charge per unit area  $\Delta Q$  accumulated in the interface traps. In fact, as observed in Fig. 3(b), the probability of charge exchange between the metal and interface traps diminishes with increasing MgO thickness and, consequently, the  $\Delta Q$  quantity increases.

In summary, we have studied the electrical properties of the Au/MgO/GaAs(001) (n type) structure using C-V and

*I-V* measurements at RT. For oxide thickness higher than 2 nm, our results show a clear evidence of the presence of a large density of trap states at the MgO/GaAs interface (~4.10<sup>13</sup> states/cm<sup>2</sup>/eV). Although the structure does not operate under strong-inversion or accumulation conditions, we observe a large voltage drop across the MgO layer with the change of the applied voltage. We demonstrate that this behavior is caused by the charge accumulation in the interface traps. As a result of this voltage drop across the MgO layer, a strong increase of the current injection into the semiconductor structure can be observed with increasing reverse bias.

The authors warmly acknowledge L. Frein and C. Lallaizon for technical support. This work was supported by the French Agence Nationale pour la Recherche (MOMES) and French Program Action Concertée Nanosciences-Nanotechnologies (NANOOPTOSPIN).

<sup>1</sup>I. Žutić, J. Fabian, and S. Das Sarma, Rev. Mod. Phys. **76**, 323 (2004). <sup>2</sup>G. Schmidt, D. Ferrand, L. W. Molenkamp, A. T. Filip, and B. J. van Wees, Phys. Rev. B **62**, R4790 (2000).

<sup>3</sup>E. I. Rashba, Phys. Rev. B **62**, R16267 (2000).

<sup>4</sup>A. Fert and H. Jaffrès, Phys. Rev. B **64**, 184420 (2001).

<sup>5</sup>X. Jiang, R. Wang, R. M. Shelby, R. M. Macfarlane, S. R. Bank, J. S. Harris, and S. S. P. Parkin, Phys. Rev. Lett. **94**, 056601 (2005).

<sup>6</sup>Y. Lu, J. C. Le Breton, P. Turban, B. Lépine, P. Schieffer, and G. Jézéquel, Appl. Phys. Lett. 88, 042108 (2006).

<sup>7</sup>S. M. Sze, *Physics of Semiconductor Devices* (Wiley, New York, 1981), p. 245.

<sup>8</sup>L. S. Wei and J. G. Simmons, Solid-State Electron. 17, 1021 (1974).

<sup>9</sup>L. Yan, C. M. Lopez, R. P. Shrestha, E. A. Irene, A. A. Suvorova, and M. Saunders, Appl. Phys. Lett. 88, 142901 (2006).

<sup>10</sup>J. G. Simmons and L. S. Wei, Solid-State Electron. **16**, 40 (1973).

<sup>11</sup>E. H. Nicollian and J. R. Brews, MOS Physics and Technology (Wiley, New York, 1982), pp.176 and 319.

<sup>12</sup>The barrier height  $\Phi_B$  under depletion or deep depletion mode of operation of the MOS structure is calculated from the  $1/C^2$  vs  $V_a$  curve under reverse bias voltage using  $\Phi_B = eV_I + kT + \xi$ , where  $V_I$  is the voltage intercept of the extrapolated  $1/C^2$  curve with the voltage axis, e is the elementary charge, k is the Boltzmann constant, and  $\xi$  is the difference between the energies of bottom of conduction band and the Fermi level in bulk GaAs (Ref. 7).

<sup>13</sup>M. Passlack, M. Hong, E. F. Schubert, G. J. Zydzik, J. P. Mannaerts, W. S. Hobson, and T. D. Harris, J. Appl. Phys. 81, 7647 (1997).

<sup>14</sup>H. C. Card and E. H. Rhoderick, J. Phys. D **4**, 1602 (1971).