# Modular Multilevel Converters for HVDC power stations

Nicola Serbia

### ► To cite this version:

Nicola Serbia. Modular Multilevel Converters for HVDC power stations. Engineering Sciences [physics]. Institut National Polytechnique de Toulouse - INPT, 2014. English. NNT: . tel-04229839v1

## HAL Id: tel-04229839 https://theses.hal.science/tel-04229839v1

Submitted on 12 Feb 2014 (v1), last revised 5 Oct 2023 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par :

Institut National Polytechnique de Toulouse (INP Toulouse)

Cotutelle internationale avec "Seconda Università degli Studi di Napoli"

### Présentée et soutenue par : SERBIA, Nicola

le mercredi 29 janvier 2014

Titre :

Modular Multilevel Converters for HVDC power stations

École doctorale et discipline ou spécialité : ED GEET : Génie Electrique

**Unité de recherche :** LABORATOIRE PLASMA ET CONVERSION D'ENERGIE (LAPLACE)- UMR5213

Directeur(s) de Thèse :

M. LADOUX, Philippe M. MARINO, Pompeo

Jury :

LADOUX, Philippe (Directeur de Thèse) MARINO, Pompeo (Directeur de Thèse) DEL PIZZO, Andrea (Rapporteur) MACHMOUM, Mohamed (Rapporteur) EGROT, Philippe (Examinateur) IMPROTA, Vinvenzo (Examinateur)

### Acknowledgements

The Phd thesis is not just an intensive work period of three years. This is an experience of life where I had the opportunity to increase my personal and professional experience. In these three years through the interfacing with persons that assisted me and with which I had the honor to share this period. With them (directly and un-directly), I had the opportunity to grow up my professional knowledge and to improve my personality.

Firstly I would like to thanks the members of the jury:

**Mr. Mohamed MACHMOUM**, Professor at the Polytech Nantes and **Mr. Andrea DEL PIZZO**, Professor at the Università degli Studi di Napoli Federico II, for having read in details this dissertation and for having wrote a very detailed and exhaustive report about the manuscript as examiners of my thesis by contributing to the improvement of the work.

**Mr. Philippe EGROT,** engineer at EDF in the HVDC frame for having accepted to review my thesis and having been part of the jury.

**Mr. Vincenzo IMPROTA**, Engineer at Ansaldobreda SpA for having accepted to review my thesis and having been part of the jury.

Then I would like to thanks **Mr. Paolo BORDIGNON**, executive vice president of Rongxin Power Electronic Co., Ltd for his economic (by means the company) and professional support to the development of the work

Then I like to say thank you to my two supervisors. Peoples that I'll never stop thanking. I can consider these two persons the only guys who attended to my professional development and they principally contributed to my professional and recently personal maturation. I know that is very difficult to meet persons like them. These two persons are alphabetically sorted below.

Thank you to **Mr. Philippe LADOUX**, Professor at the Institut National Polytechnique of Toulouse and director of my thesis. Firstly for having accepted me as Ph.D. student and to have believed that for me was possible facing this much hard and tricky subject. Thank for giving me his support and his methods, and for best having supervised my studies. He taught me how the complex world of engineering can become very easy and pleasurable. For me was an honor working with him and I hope that a new working adventure is going to start. Besides the professional aspect I found a person with a great humanity and friendship. It was able to make easy all the difficulties that I had at my arriving in France. Thank you, Philippe his family, because they spent a lot of time with me giving me the honor to meet me at their home. With their help I never had any difficulties. Thank you for their precious friendship.

Thank you to **Mr. Pompeo MARINO**, Professor at the Seconda Università degli Studi di Napoli, supervisor of my final project of the "Laurea" degree in 2007, supervisor of my final project of the "Laurea Magistrale" degree in 2010 and finally my PhD thesis director. Thank you for trusting in me. Thank you having gave me the opportunity. Thank for your very precious suggestions and your intuitions. He taught me that everything is possible by working hard and fine. Under the human aspect I think that there are many things to learn by him. He made my Ph.D. period a superlative experience. He shared with me his passion for the sailing which for me was a very formative and fantastic experience. So, of course I'm sure that a very great friendship has been consolidated. It is always an honor spending time with him, thank you Prof.!

Thanks to the LAPLACE, I have met a lot of people, and I have to say thanks to someone of them:

All the members of the group *Convertisseur Statique*, expecially the responsible **Mr**. **Frédéric RICHARDEAU**.

Thank you "Les Super Filles"! **Carine BASTIE, Lea BOULANGER, Cécile DAGUILLANES, Catherine MOLL-MAZELLA** and **Valérie SCHWARZ.** Besides their impeccable professionalism they made the time at the laboratory more pleasant and cheerful (particularly the Valerie' sneezes).

**Mr Jean-Marc BLAQUIERE** for his great technical experience and for having helped me in the realization of the prototype.

**Mr Jeaques BENAIOUN** for his great technical informatics experience. He was very efficient to solve my informatics problem.

All the PhD students, Post-Doc and others that shared all the good times, especially:

**Andre DE ANDRADE** (dedé), he helped me especially at the beginning. Thank for your friendship. He never left me alone

and Julio BRANDELERO, Clement NADAL and Damien BIDART, les "colocataires plus emportants ».

François PIGACHE, a very good friend always helpful and friendly.

Then **Johannes SCHELLER** and **Samer YAMMINE**, I found very good friends; they are principally responsible of my "intensive week-ends".

Alberto ROSSI, Etienne FOURNIER (thank you for your help for the language), Julie EGALON, Sebastien SANCHEZ (mon "professeur de toulousian"), Maud TAUZIA (ma prof de Français) Amanda VELAZQUEZ SALAZAR ("*la nina*"), Mustapha DEBBOU, Bernardo COUGO, Eduard Hernando SOLANO SAENZ, Julian Andres SUAREZ, Benedikt BYRNE sorry if I've forgotten someone.

Then I say thank you to **Giuliano RAIMONDO**, thank to his help especially at the beginning. It was principal responsible of my integration. Thank you for your friendship too.

I have also to say thanks to the people of DITEN from the University of Genova, especially to **Gianluca PARODI**, Luis VACCARO and Prof. Mario MARCHESONI.

I have also to say thanks to the people of the Dipartimento di Ingegneria Industriale e dell'Informazione of the Seconda Università degli Studi di Napoli, especially to:

**Nicola GRELLA** and **Angela BRUNITTO** for their efficiency in all the bulky administrative procedures.

My Italians colleagues:

Michele FIORETTO for his friendship and for his time spent together

**Luigi** and **Guido RUBINO**, for their technical experience and their very precious help. Especially lately.

#### Felice Andreozzi, Marco BALATO and Luigi FEOLA.

Professors **Roberto LANGELLA** and **Alfredo TESTA** for having shared several time of his research with me, and all the others PhD students I've met in Aversa.

At the end I'd like to say thank you to my **FAMILY**, they supported always my choices. They are responsible of my ambition. Thank you for having always believed in me and for me is an honor being your son. I hope and I know that this my new goal helps your happiness.

Then at the end there is **ROSSELLA**, despite the distance she is able to make me a happy man again. Moreover she makes me want be a better man.

# **SUMMARY**

This work was performed in the frame of collaboration between the Laboratory on Plasma and Energy Conversion (LAPLACE), University of Toulouse, and the Second University of Naples (SUN). This work was supported by Rongxin Power Electronic Company (China) and concerns the use of multilevel converters in High Voltage Direct Current (HVDC) transmission.

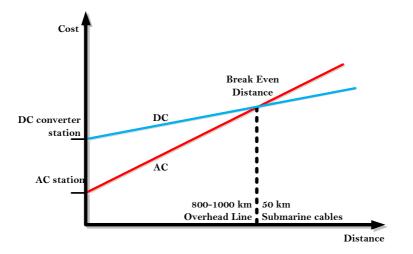

For more than one hundred years, the generation, the transmission, distribution and uses of electrical energy were principally based on AC systems. HVDC systems were considered some 50 years ago for technical and economic reasons. Nowadays, it is well known that HVDC is more convenient than AC for overhead transmission lines from 800 - 1000 km long. This break-even distance decreases up to 50 km for underground or submarine cables.

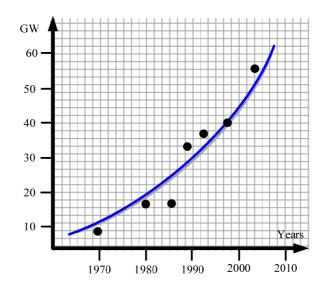

Over the twenty-first century, HVDC transmissions will be a key point in green electric energy development. Due to the limitation in current capability of semiconductors and electrical cables, high power applications require high voltage converters. Thanks to the development of high voltage semiconductor devices, it is now possible to achieve high power converters for AC/DC conversion in the GW power range.

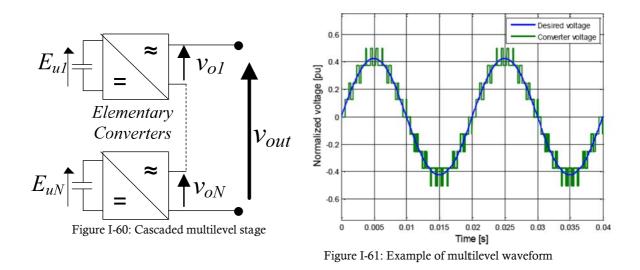

For several years, multilevel voltage source converters allow working at high voltage level and draw a quasi-sinusoidal voltage waveform. Classical multilevel topologies such as NPC and Flying Capacitor VSIs were introduced twenty years ago and are nowadays widely used in Medium Power applications such as traction drives. In the scope of High Voltage AC/DC converters, the Modular Multilevel Converter (MMC), proposed ten years ago by Professor R. Marquardt from the University of Munich (Germany), appeared particularly interesting for HVDC transmissions.

On the base of the MMC principle, this thesis considers different topologies of elementary cells which make the High Voltage AC/DC converter more flexible and easy suitable respect to different voltage and current levels. The document is organized as follow.

Firstly, HVDC power systems are introduced. Conventional configurations of Current Source Converters (CSCs) and Voltage Source Converters (VSCs) are shown. The most attractive topologies for VSC-HVDC systems are analyzed.

The operating principle of the MMC is presented and the sizing of reactive devices is developed by considering an open loop and a closed loop control. Different topologies of elementary cells offer various properties in current or voltage reversibility on the DC side. To compare the different topologies, an analytical approach on the power losses evaluation is achieved which made the calculation very fast and direct.

A HVDC link to connect an off-shore wind farm platform is considered as a case study. The nominal power level is 100 MW with a DC voltage of 160 kV. The MMC is rated considering press-packed IGBT and IGCT devices. Simulations validate the calculations and also allow analyzing fault conditions. The study is carried out by considering a classical PWM control with an interleaving of the cells.

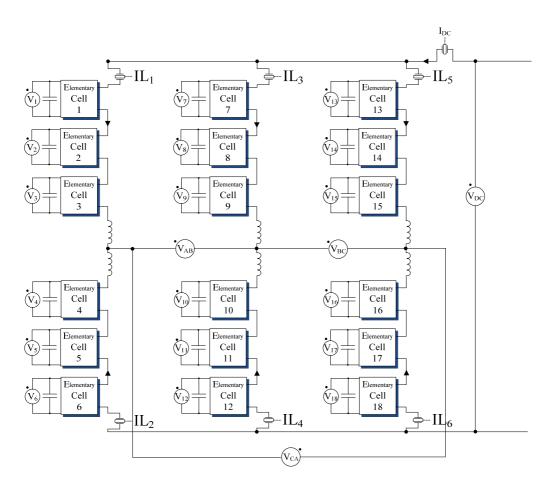

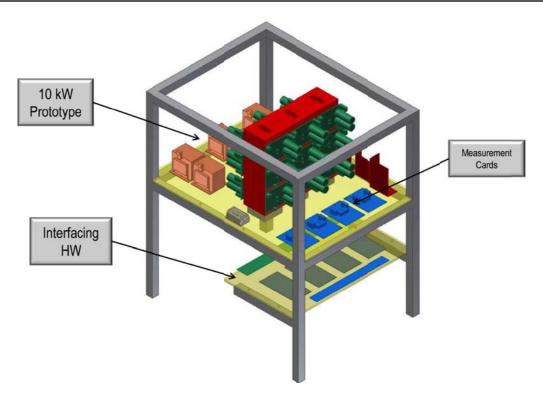

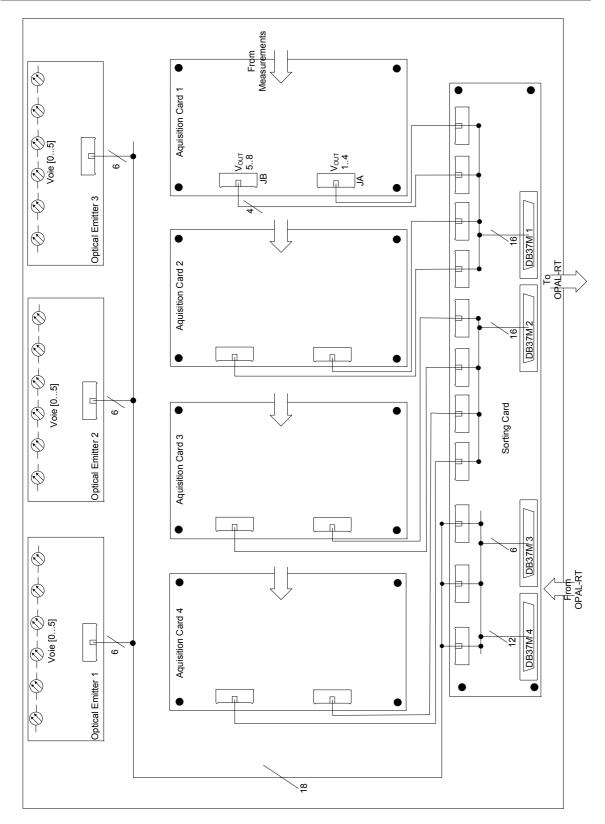

In order to validate calculation and the simulation results, a 10kW three-phase prototype was built. It includes 18 commutation cells and its control system is based on a DSP-FGPA platform.

## RESUME

Les travaux présentés dans ce mémoire ont été réalisés dans le cadre d'une collaboration entre le LAboratoire PLAsma et Conversion d'Énergie (LAPLACE), Université de Toulouse, et la Seconde Université de Naples (SUN). Ce travail a reçu le soutien de la société Rongxin Power Electronics (Chine) et traite de l'utilisation des convertisseurs multi-niveaux pour le transport d'énergie électrique en courant continu Haute Tension (HVDC).

Depuis plus d'un siècle, la génération, la transmission, la distribution et l'utilisation de l'énergie électrique sont principalement basées sur des systèmes alternatifs. Les systèmes HVDC ont été envisagés pour des raisons techniques et économiques dès les années 60. Aujourd'hui il est unanimement reconnu que ces systèmes de transport d'électricité sont plus appropriés pour les lignes aériennes au-delà de 800 km de long. Cette distance limite de rentabilité diminue à 50 km pour les liaisons enterrées ou sous-marines.

Les liaisons HVDC constituent un élément clé du développement de l'énergie électrique verte pour le XXIème siècle. En raison des limitations en courant des semi-conducteurs et des câbles électriques, les applications à forte puissance nécessitent l'utilisation de convertisseurs haute tension (jusqu'à 500 kV). Grâce au développement de composants semi-conducteurs haute tension et aux architectures multicellulaires, il est désormais possible de réaliser des convertisseurs AC/DC d'une puissance allant jusqu'au GW.

Les convertisseurs multi-niveaux permettent de travailler en haute tension tout en délivrant une tension quasi-sinusoïdale. Les topologies multi-niveaux classiques de type NPC ou « Flying Capacitor » ont été introduites dans les années 1990 et sont aujourd'hui couramment utilisées dans les applications de moyenne puissance comme les systèmes de traction. Dans le domaine des convertisseurs AC/DC haute tension, la topologie MMC (Modular Multilevel Converter), proposée par le professeur R. Marquardt (Université de Munich, Allemagne) il y a dix ans, semble particulièrement intéressante pour les liaisons HVDC.

Sur le principe d'une architecture de type MMC, le travail de cette thèse propose différentes topologies de blocs élémentaires permettant de rendre le convertisseur AC/DC haute tension plus flexible du point de vue des réversibilités en courant et en tension. Ce document est organisé de la manière suivante.

Les systèmes HVDC actuellement utilisés sont tout d'abord présentés. Les configurations conventionnelles des convertisseurs de type onduleur de tension (VSCs) ou de type onduleur de courant (CSCs) sont introduites et les topologies pour les systèmes VSC sont ensuite plus particulièrement analysées.

Le principe de fonctionnement de la topologie MMC est ensuite présenté et le dimensionnement des éléments réactifs est développé en considérant une commande en boucle ouverte puis une commande en boucle fermée. Plusieurs topologies de cellules élémentaires sont proposées afin d'offrir différentes possibilités de réversibilité du courant ou de la tension du côté continu. Afin de comparer ces structures, une approche analytique de

l'estimation des pertes est développée. Elle permet de réaliser un calcul rapide et direct du rendement du système.

Une étude de cas est réalisée en considérant la connexion HVDC d'une plateforme éolienne off-shore. La puissance nominale du système étudié est de 100 MW avec une tension de bus continu égale à 160 kV. Les différentes topologies MMC sont évaluées en utilisant des IGBT ou des IGCT en boitier pressé. Les simulations réalisées valident l'approche analytique faite précédemment et permettent également d'analyser les modes de défaillance. L'étude est menée dans le cas d'une commande MLI classique avec entrelacement des porteuses.

Enfin, un prototype triphasé de 10kW est mis en place afin de valider les résultats obtenus par simulation. Le système expérimental comporte 18 cellules de commutations et utilise une plate-forme DSP-FPGA pour l'implantation des algorithmes de commande.

# RIASSUNTO

Durante i tre anni del corso di Dottorato di Ricerca in Conversione dell'Energia, l'attività si è sviluppata nel quadro di una collaborazione tra la Seconda Università degli Studi di Napoli, il laboratorio LAPLACE (Laboratoire Plasma et Conversion d'Energie) dell'Università di Toulouse. Il lavoro di tesi è stato inoltre supportato dalla Rongxin Power Electronic (Cina) e concerne l'impiego del convertitore multilivello per le trasmissioni in corrente continua ad alta tensione comunemente conosciute in letteratura come High Voltage Direct Currents (HVDC).

Nell'ultimo secolo, la generazione, la trasmissione, la distribuzione ed il consumo di energia è stato principalmente basato su sistemi in corrente alternata (AC). I sistemi di tipo HVDC si sono resi attrattivi negli ultimi 50 anni per una serie di ragioni di natura tecnica ed economica. Oggi, è ben noto che le connessioni HVDC sono più convenienti rispetto a quelle AC per distanze superiori a linee comprese tra 800 – 1000 km. Questa distanza di soglia si riduce quando si parla di trasmissioni sottomarine.

Nel ventunesimo secolo, le trasmissioni HVDC saranno un punto chiave anche per lo sviluppo e l'integrazione con il preesistente sistema elettrico delle energie rinnovabili. A causa della limitazione in corrente dei dispositivi semiconduttori e dei cavi di trasmissione, l'impiego di alte potenze si traduce nell'impiego di convertitori ad alte tensioni. Grazie alo sviluppo di dispositivi semiconduttori, è oggi possibile ottenere conversioni AC/DC per alte potenze dell'ordine dei GW.

Per diversi anni, i convertitori Multilivello di tipo sorgente di tensione, in letteratura noti come voltage source converters (VSC), consentono di lavorare ad alti livelli di tensione e di imporre una forma d'onda di tensione al lato AC pressoché sinusoidale. Le classiche topologie come NPC e Flying Capacitors ti tipo VSI sono state introdotte circa venti anni addietro ed oggi sono generalmente utilizzate in applicazioni di media potenza come gli azionamenti delle macchine elettriche. Per la conversione AC/DC ad alta tensione, il convertitore modulare multilivello (MMC), proposto circa dieci anni fa dal professore R. Marquardt della Università di Monaco (Germania), è sembrato particolarmente attrattivo ed interessante per le trasmissioni HVDC.

Partendo dalla struttura HVDC, si sono considerate all'interno del lavoro di differenti topologie di celle elementari che rendono il convertitore più flessibile e più facilmente adattabile rispetto ai differenti livelli di tensione e corrente.

Il lavoro di tesi si è svolto secondo il seguente ordine:

in primis, i sistemi HVDC sono stati introdotti. Le configurazioni convenzionali basate sui convertitori a sorgente di corrente (CSC) e quelle basate sui convertitori a sorgente di tensione (VSC) sono state descritte. In entrambi i casi il principio di funzionamento sul quale si basa il trasferimento di potenza è stato descritto. Parallelamente è stato effettuato uno studio sullo stato dell'arte dei semiconduttori impiegati nella elettronica di potenza e sono state tratte

valutazioni sui meglio adattabili alle connessioni HVDC. Si è evinto dedotto che l'orientamento delle trasmissioni HVDC è basato sulla conversione VSC. Per tale motivo ha analizzato le topologie multilivello più attrattive.

I principi di funzionamento dell'MMC sono stati studiati e il dimensionamento dei componenti reattivi è stato proposto considerando due differenti approcci a seconda del controllo ipotizzato per il sistema. Nel corso del suo studio si è inoltre evinto che differenti topologie di celle elementari offrono varie proprietà reversibilità di corrente o di tensione sul lato DC. Al fine di comparare le differenti topologie, si è proposto un nuovo approccio analitico per lo studio delle perdite ha reso il calcolo veloce e diretto.

In tale ambito una nuova struttura multilivello è stata introdotta. Tale topologia è stata pensata per sistemi AC/DC basata su raddrizzatori a ponte di diodi. Tali sistemi infatti sono composti da trasformatori di rete di tipo ZigZag configurati in tal modo da compensare le componenti continue della corrente introdotte dal raddrizzatore a ponte lato AC. La topologia proposta nel lavoro di tesi è pensata per rimpiazzare i vecchi raddrizzatori obsoleti e poco versatili con una struttura multilivello capace di avere un impatto armonico ridotto ed un funzionamento a quattro quadranti in termini di potenza.

In una fase successiva gli studi sono stati validati attraverso una campagna di simulazioni. Il caso considerato è quello di un sistema HVDC-VSC multiterminal chiamato ad interfacciare un parco eolico off-shore sito in Cina. La potenza del sistema è di 100 MW con una tensione DC di 160 kV. Il convertitore MMC è stato dimensionato considerando dei dispositivi IGBT di tipo press-Pack e dei dispositivi IGCT. Le simulazioni hanno validato le simulazioni anche in condizioni di fault. Lo studio del controllo per il sistema è stato effettuato in prima battuta considerando la classica modulazione PWM. Tale modulazione è stata implementata sfasando le portanti tra le celle che compongono la struttura.

Al fine di validare lo studio e i risultati di simulazione, un prototipo trifase da 10 kW è stato realizzato. Tale prototipo è formato da 18 celle di commutazione di tipo semplici. Il sistema di controllo è stato implementato grazie una piattaforma basata su logica DSP-FPGA.

#### **RESUME DE LA THESE EN LANGUE FRANÇAISE**

#### Chapitre I : Les systèmes HVDC

Ce chapitre présente les systèmes pour le transport d'énergie électrique en courant continu à haute tension (HVDC) et souligne leur rôle clé dans le développement des énergies renouvelables.

Ces 40 dernières années, les systèmes HVDC ont été développés pour le transport de l'électricité compte tenu des considérations techniques et économiques suivantes :

- Par rapport aux systèmes en courant alternatif, la transmission en courant continu, malgré le coût additionnel des sous-stations de conversion, est économiquement intéressante pour des distances supérieures à 800 km dans le cas des lignes aériennes et 50 km pour les lignes enterrées ou sous-marines (Figure I-1).

- Les systèmes en courant continu permettent les interconnexions entre des réseaux hétérogènes qui peuvent être asynchrones entre eux, et/ou à fréquences différentes.

- L'amélioration constante de la technologie des dispositifs semi-conducteurs a permis d'atteindre des niveaux de puissance de l'ordre du GW.

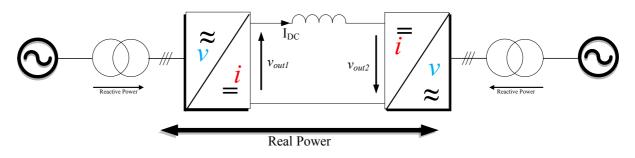

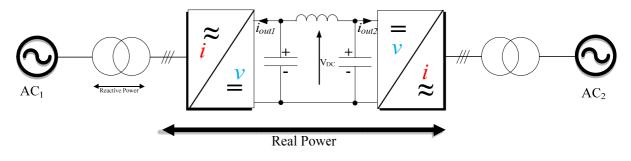

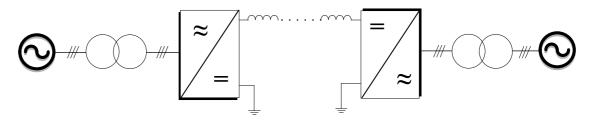

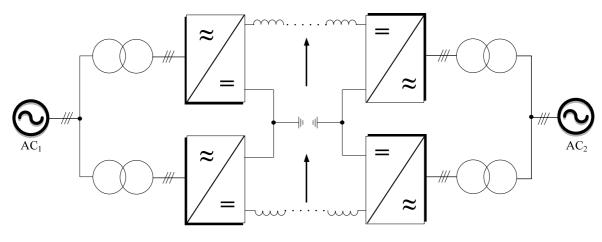

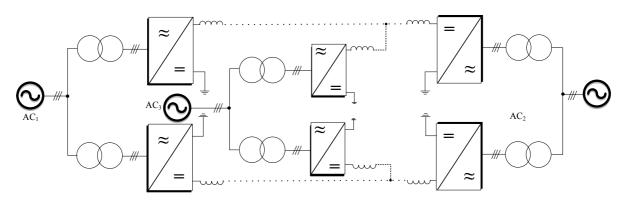

Nous illustrons la description des principes de connexion HVDC en faisant référence aux principales installations actuelles. Deux principaux types de connexion HVDC sont utilisés. Celles basées sur des convertisseurs AC/DC de type onduleur de courant (CSC) et celles basées sur des convertisseurs AC/DC de type onduleur de tension (VSC).

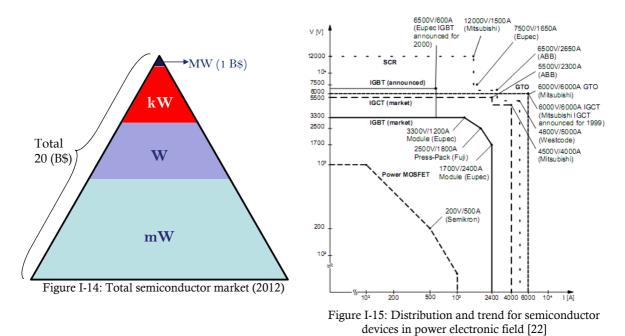

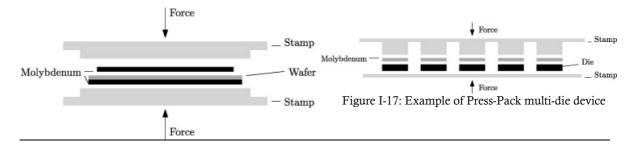

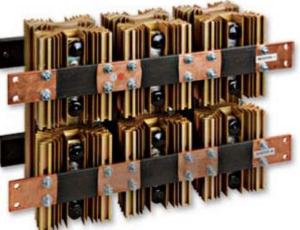

Avant d'entrer dans les détails de fonctionnement de ces liaisons HVDC, nous décrivons les principaux dispositifs semi-conducteurs disponibles sur le marché et employés pour les applications « haute tension ». Nous donnons en particulier une description détaillée des technologies en boitier pressé (*press-pack*), qui peuvent être considérées comme les meilleures candidates pour la mise en œuvre de semi-conducteurs en haute tension et fort courant.

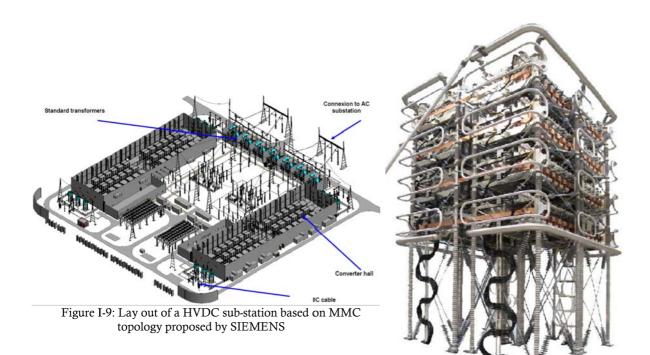

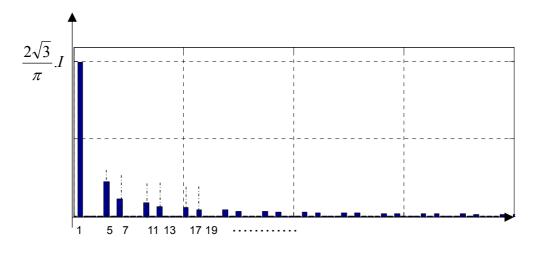

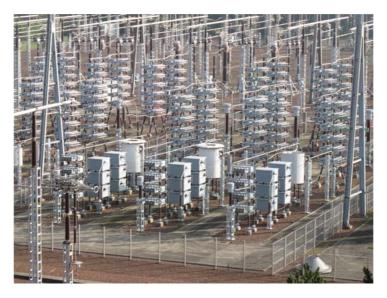

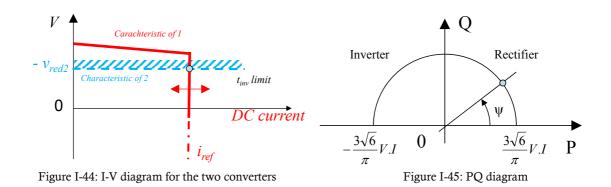

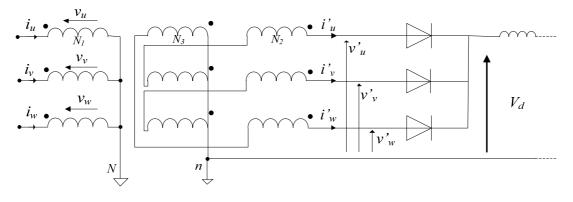

Nous donnons ensuite une description des convertisseurs CSC à base de thyristors et présentons les principes de réglage de la puissance. Du fait que les thyristors ne présentent pas de problèmes de mise en série directe, les convertisseurs peuvent atteindre des tensions de l'ordre de 500 kV. Bien que simple et robuste, la topologie de type CSC ne permet pas un contrôle indépendant des puissances active et réactive et absorbe également des courants non sinusoïdaux qui nécessitent des dispositifs de filtrage occupant 20 à 30% de la superficie totale d'une sous-station (Figure I-42).

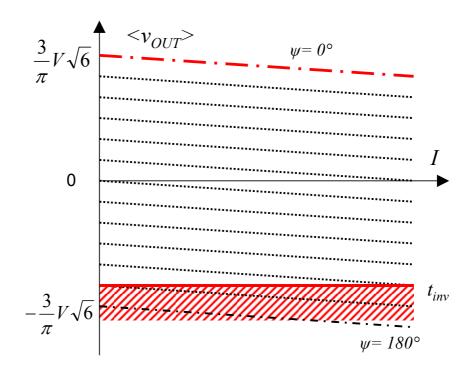

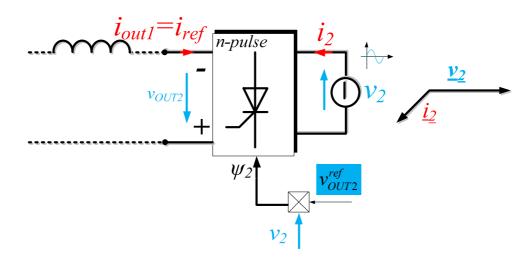

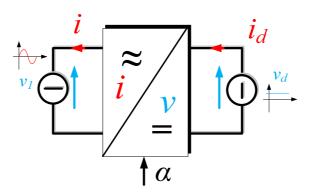

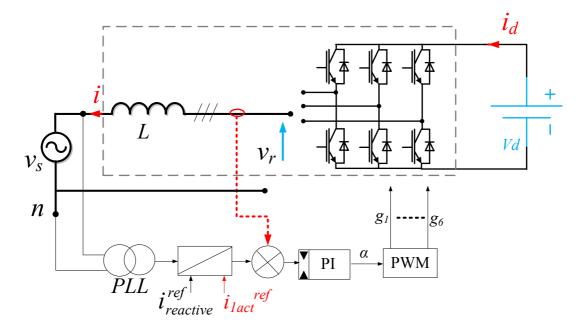

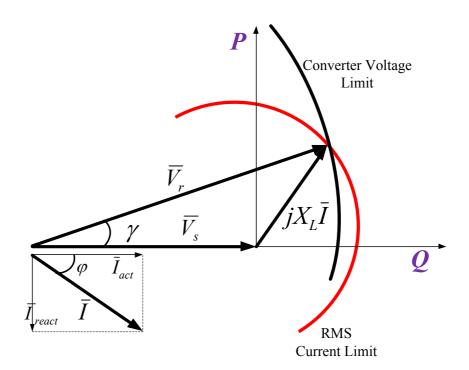

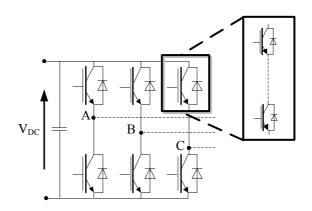

Les convertisseurs de type VSC commandés en modulation de largeur d'impulsion (MLI) sont basés sur des semi-conducteurs à amorçage et blocage commandées (IGBT ou IGCT). Les topologies HVDC-VSC permettent d'effectuer le transport d'énergie en courant continu en offrant, vis-à-vis des réseaux AC, des réglages indépendants des puissances active et réactive . La mise en série directe d'IGBT étant très délicate, la tension reste aujourd'hui limitée à 320 kV pour une topologie classique à trois niveaux de tension par bras.

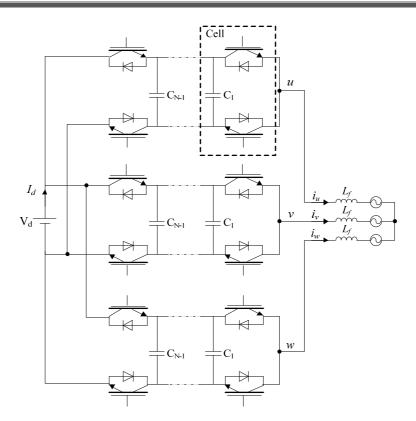

Nous décrivons ensuite des topologies multiniveaux qui sont adaptées à la haute tension. Par rapport aux structures classiques, elles peuvent garantir une forme d'onde quasi sinusoïdale en réduisant les harmoniques et en permettant une réduction des éléments de filtrage. Parmi ces topologies multiniveaux, nous présentons le principe de base du convertisseur modulaire multiniveaux (MMC) qui sera développé dans la suite de la thèse. Cette structure consiste en la mise en série de blocs élémentaires identiques (Figure I-62). Elle est aujourd'hui préférée aux structures traditionnelles car elle garantit une modularité en termes de production industrielle et n'a théoriquement pas de limite supérieure pour la valeur de la tension DC puisqu'il est toujours possible d'ajouter des blocs élémentaires en série.

#### Chapitre II : Le convertisseur modulaire multiniveaux (MMC)

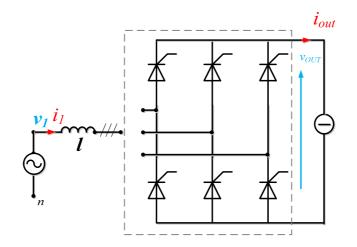

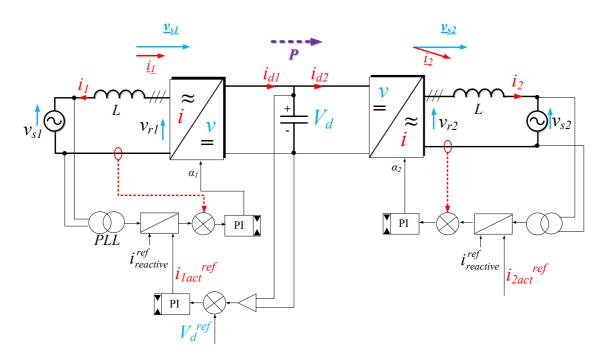

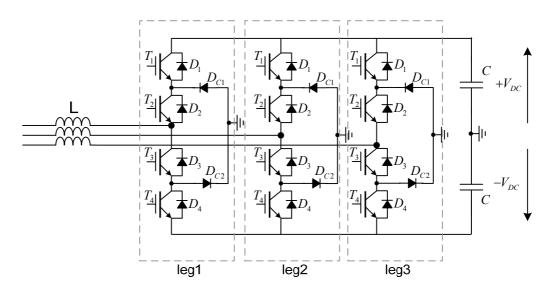

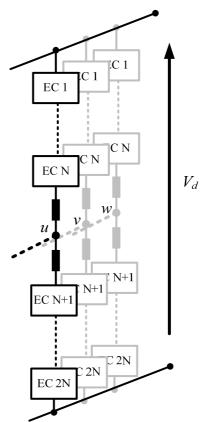

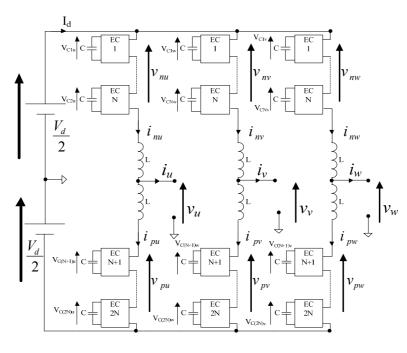

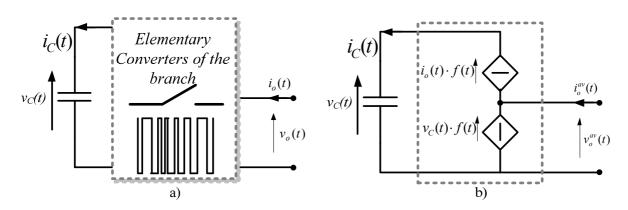

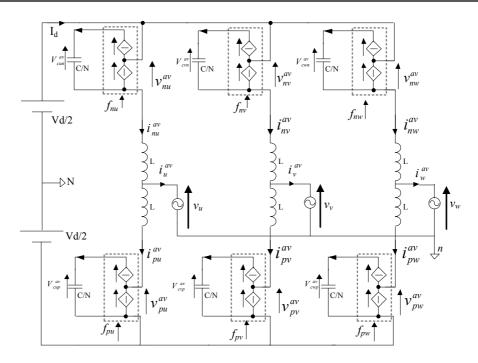

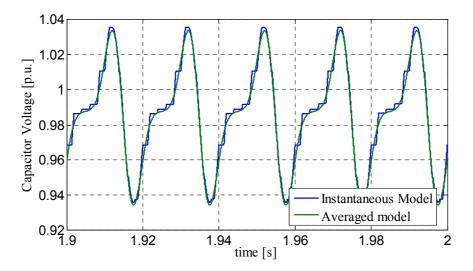

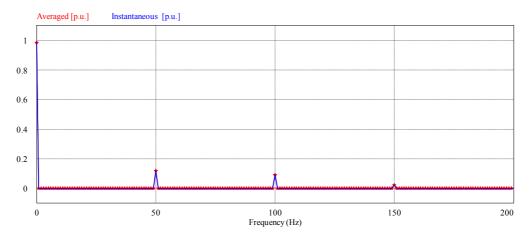

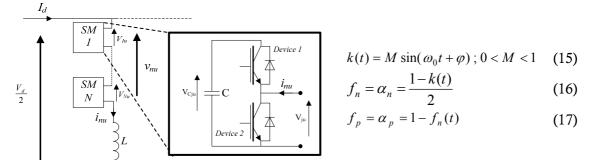

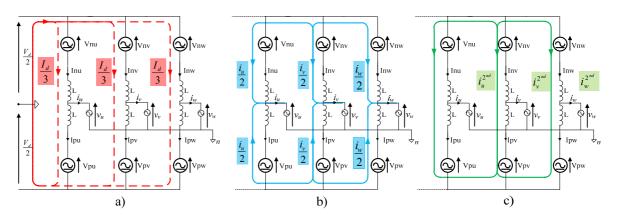

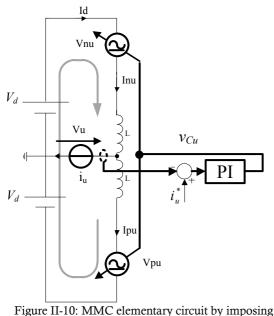

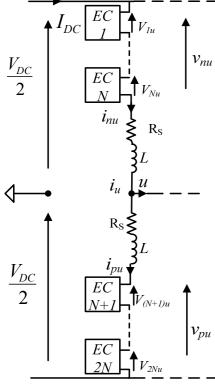

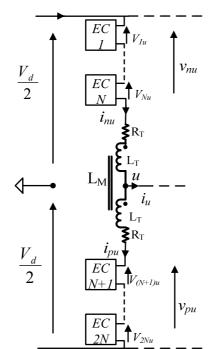

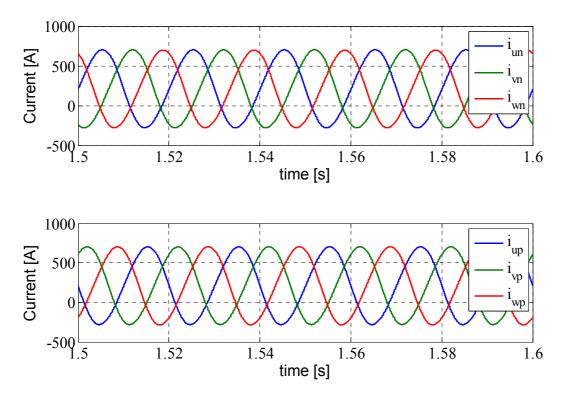

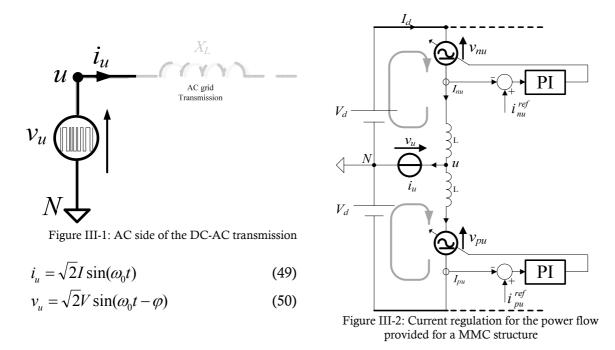

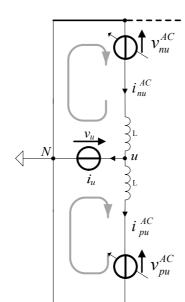

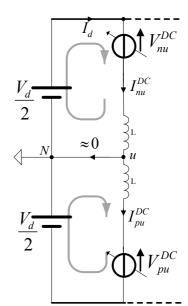

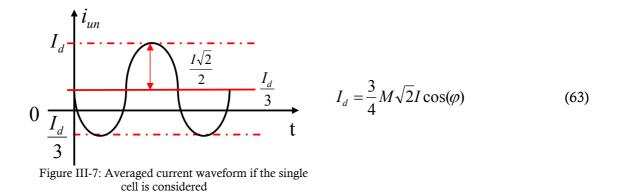

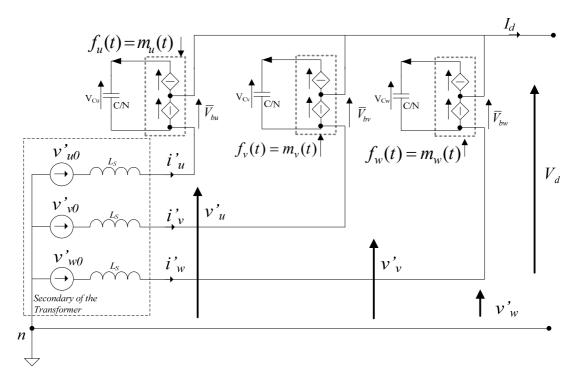

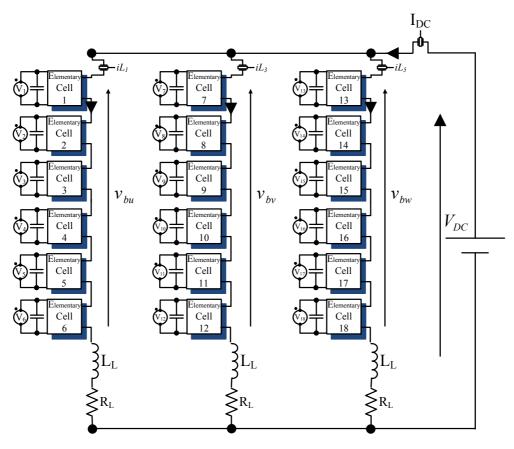

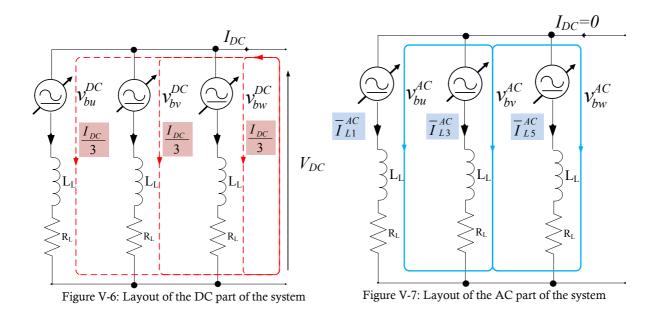

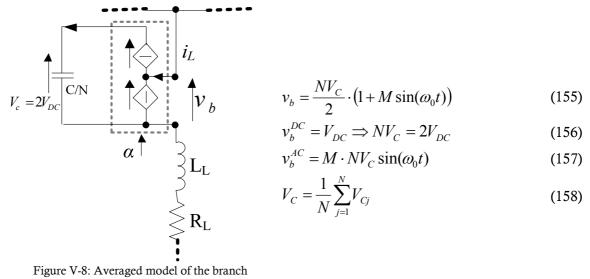

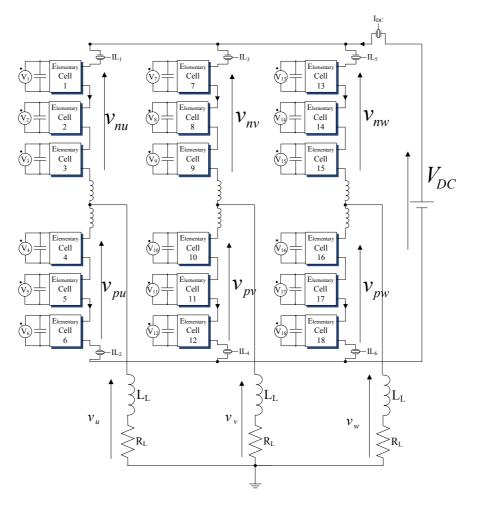

Nous étudions dans ce chapitre le convertisseur AC/DC modulaire multiniveaux. Le circuit triphasé est formé de la connexion de deux bras par phase (Figure II-1). Chaque bras impose la moitié de la tension DC ainsi que la tension AC. Chacun des bras conduit également un tiers du courant DC et la moitié du courant AC. La combinaison des deux bras nous permet d'obtenir les courants et tensions AC et DC nécessaires au transfert de puissance par la liaison DC. Après une première analyse du fonctionnement, nous proposons un modèle moyen de la structure (macro modèle) afin de simplifier l'étude de dimensionnement. Ce modèle ne prend pas en considération les effets des harmoniques dus aux dispositifs de commutation mais garantit une plus grande rapidité dans les simulations, les calculs étant simplifiés. L'étude est en outre valable quelle que soit la topologie des blocs élémentaires et considère une commande MLI classique avec entrelacement des porteuses.

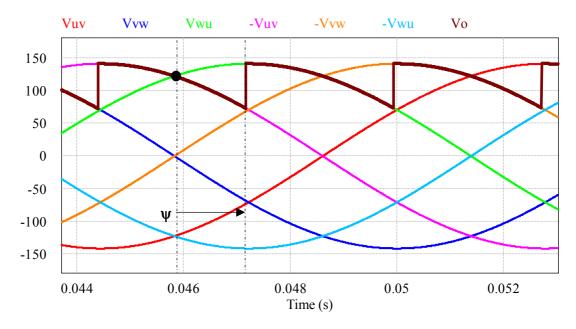

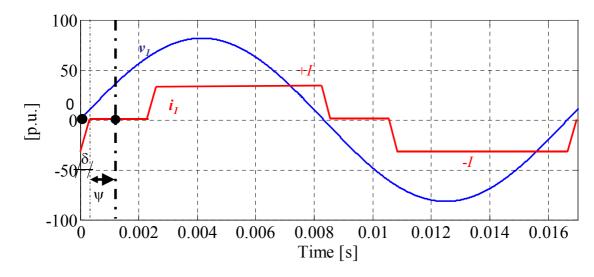

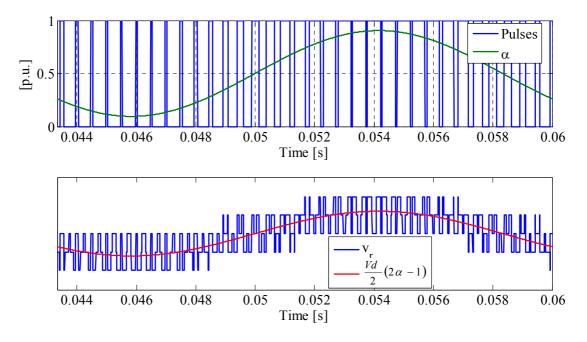

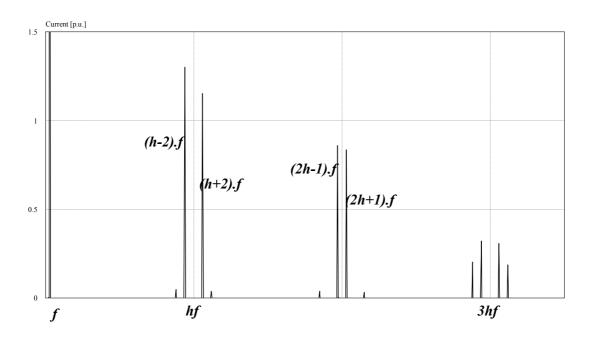

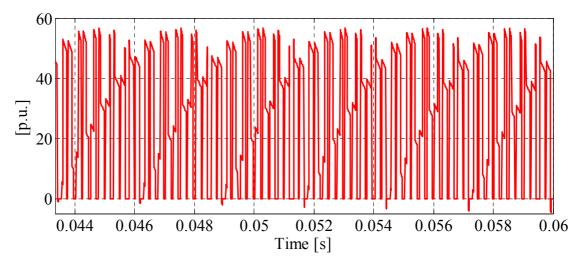

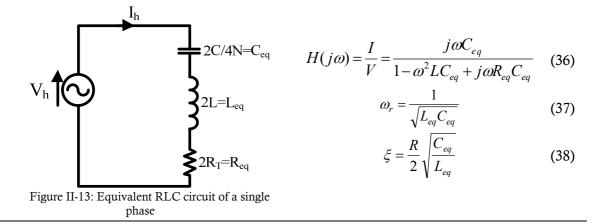

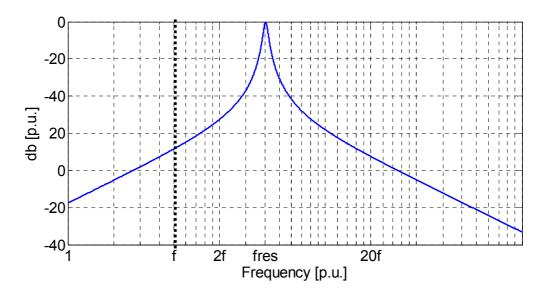

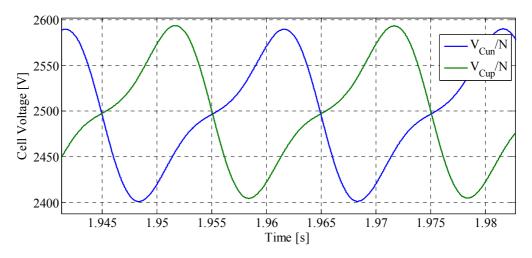

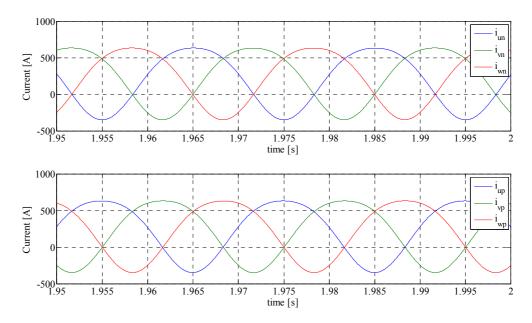

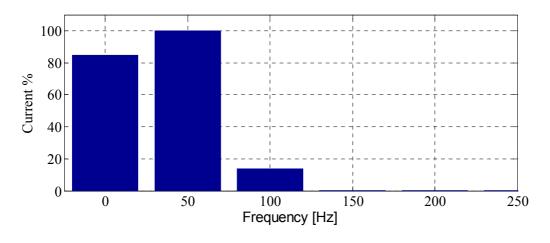

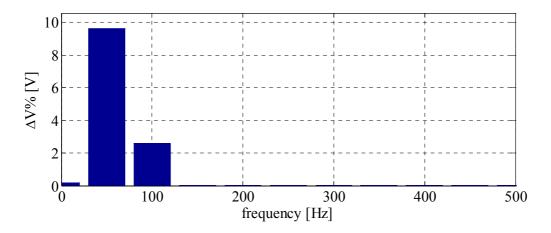

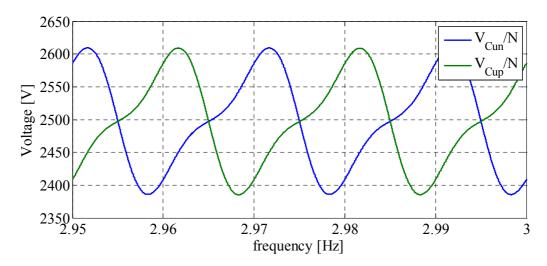

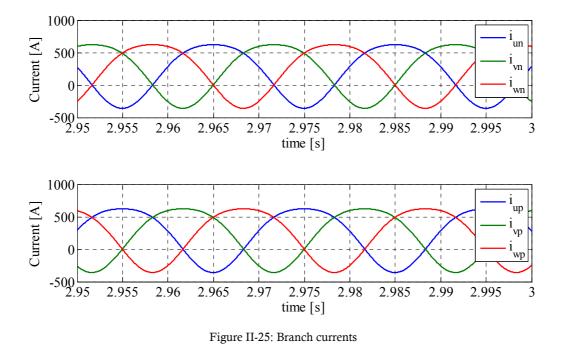

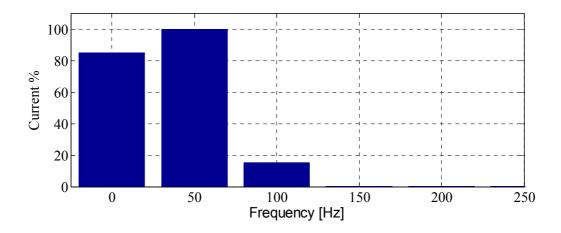

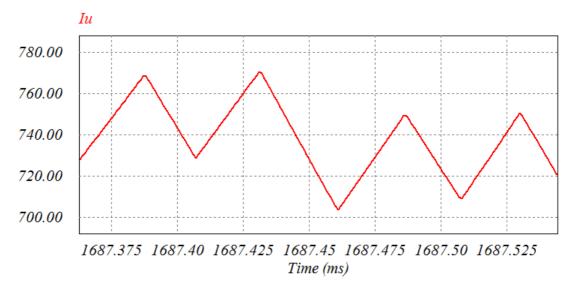

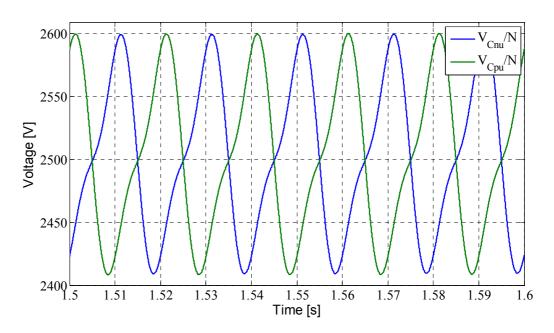

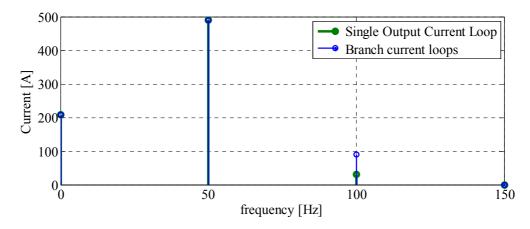

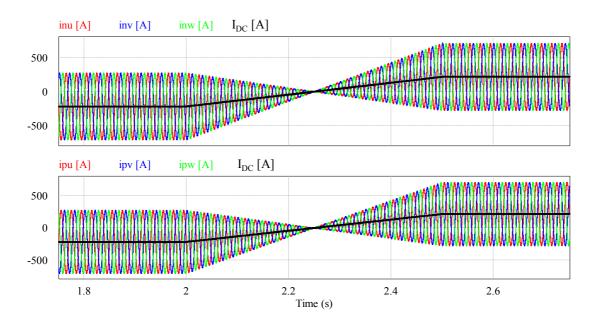

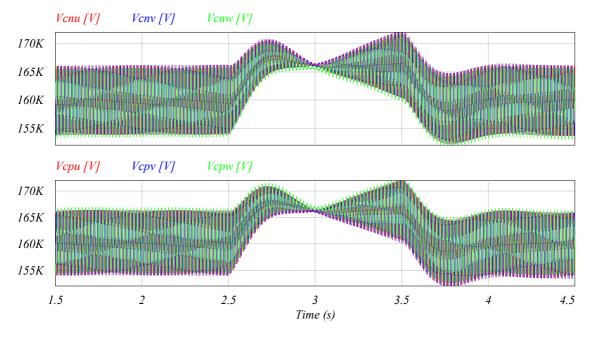

Nous effectuons une analyse préliminaire des courants et tensions du convertisseur. Du point de vue des harmoniques de courant, outre les composantes DC et AC, chacun des bras conduit une composante au double de la fréquence fondamentale (Figure II-9). Cette composante découle de l'équilibrage énergétique entre les deux bras qui composent chaque phase. La minimisation de cette composante jouant un rôle fondamental dans le dimensionnement des éléments de filtrage, nous étudions par la suite deux possibilités liées au pilotage de la structure. Des simulations sur un système de 100 MW composé de 64 convertisseurs élémentaires par bras valident l'étude.

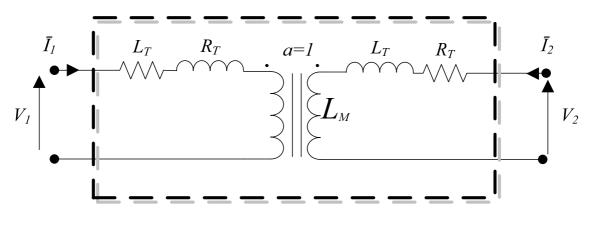

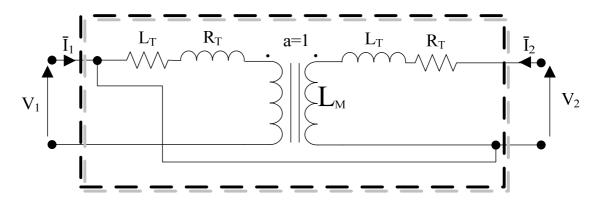

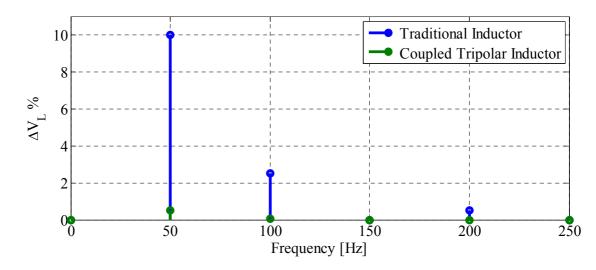

Dans le premier cas, nous adoptons un contrôle de la structure qui ne permet pas de supprimer l'harmonique de second ordre du courant de bras. La limitation de son amplitude est alors effectuée exclusivement par les composants passifs. Ainsi, en augmentant la capacité du condensateur de chaque bloc élémentaire et l'inductance série de chaque bras, l'amplitude de cet harmonique peut être diminuée. Pour ne pas limiter la plage de réglage du convertisseur à cause des valeurs élevées de l'inductance de bras, nous proposons alors d'utiliser deux inductances couplées par phase. Elles sont couplées de manière à présenter une valeur élevée vis-à-vis de l'harmonique de courant d'ordre deux tandis qu'une valeur faible est présentée vis-à-vis de la composante fondamentale de courant. Cette approche requiert bien entendu une structure plus coûteuse mais un circuit de contrôle plus simple.

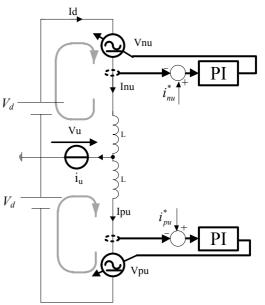

Le second cas considère une commande plus complexe capable de contrôler chaque courant de bras de façon à obtenir la référence désirée à la fréquence fondamentale tout en

#### Nicola Serbia

supprimant la composante de rang deux. Dans ces conditions, le dimensionnement des composants passifs est réduit puisque seul l'harmonique de courant à fréquence fondamentale est considéré. La complication du contrôle n'est pas aujourd'hui un problème grâce au large choix de dispositifs numériques de commande disponibles sur le marché. Ainsi, avons-nous privilégié ce cas dans la suite du travail de thèse.

#### Chapitre III : Nouvelles topologies de convertisseurs modulaires multiniveaux.

Dans ce chapitre, nous proposons et étudions et différentes topologies pour le convertisseur modulaire multiniveaux afin d'obtenir différentes propriétés en termes de réversibilité de tension ou de courant.

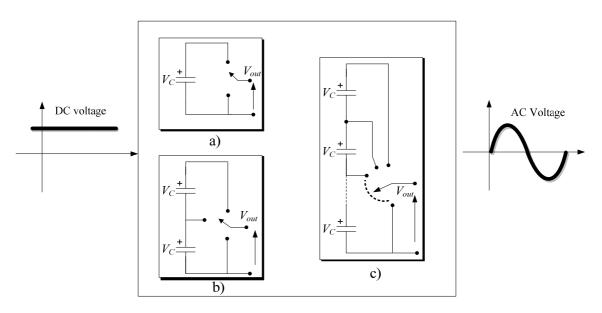

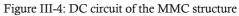

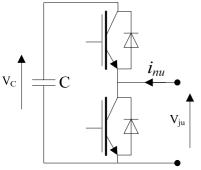

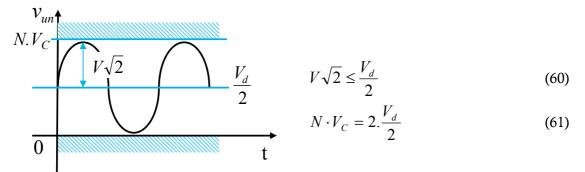

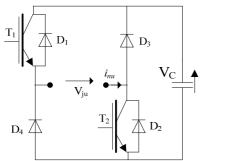

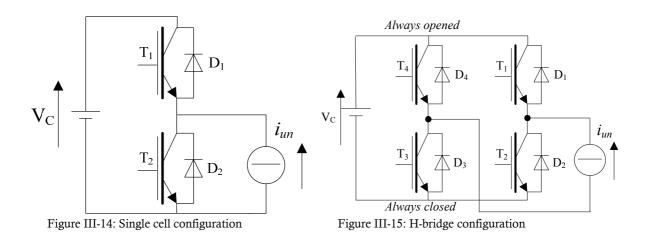

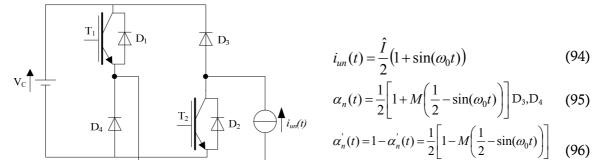

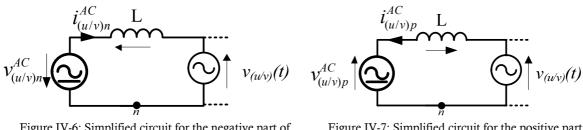

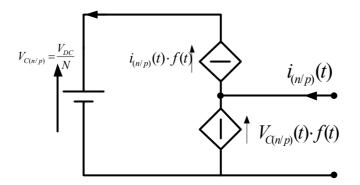

La première topologie considérée pour réaliser un bloc élémentaire est une simple cellule de commutation. C'est celle qui est utilisée dans la version de base du MMC (Figure III-5). Cette topologie est bidirectionnelle en courant et unipolaire en tension. Pour cette raison, en cas de court-circuit sur le côté DC, le système multiniveaux n'est pas en mesure de limiter le courant ce qui risque de détruire les semi-conducteurs. Seules les cellules bipolaires sont en mesure de limiter le courant en cas de court-circuit sur le côté DC. Dans ce but, nous introduisons le pont asymétrique et le pont complet. La première structure (Figure III-8) est bipolaire en tension mais unidirectionnelle en courant. Cette topologie rend le MMC peu adaptée au réglage de la puissance réactive mais dans le cas où le facteur de puissance est unitaire, cette topologie étant unidirectionnelle en courant, le système effectue l'inversion de la puissance en inversant la tension DC, ce qui est typique des CSC à thyristors. Pour cette raison, une telle structure peut être utilisée pour le remplacement immédiat des convertisseurs à thyristors. Par la suite, nous considérons également le pont complet (Figure III-11). Assurément, cette structure est la plus flexible car elle est simultanément bidirectionnelle en courant et en tension, mais par rapport aux deux précédentes elle exige le double de composants semi-conducteurs.

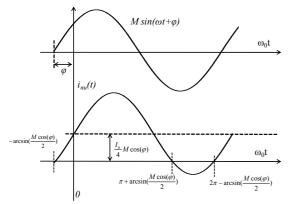

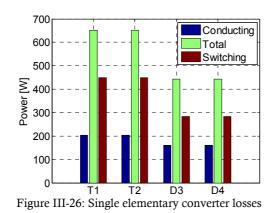

Dans ce chapitre, nous présentons une approche analytique pour le calcul des pertes dans les semi-conducteurs. Elle permet par la suite une évaluation directe et rapide du rendement du convertisseur AC/DC. Jusqu'à présent, dans la littérature, une telle approche n'avait pas été proposée pour le MMC car la forme d'onde du courant dans les semi-conducteurs rend le calcul des pertes très complexe.

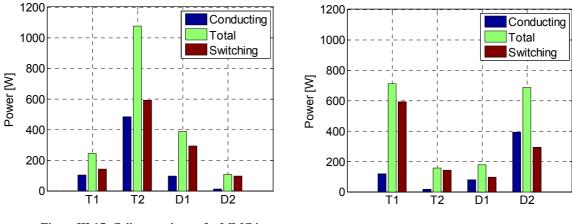

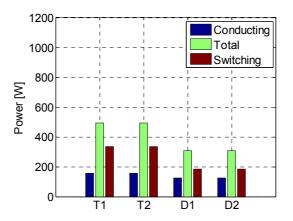

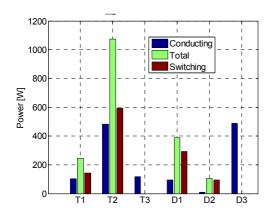

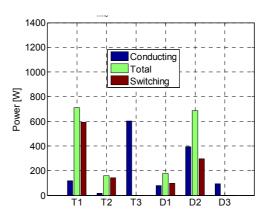

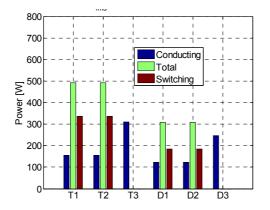

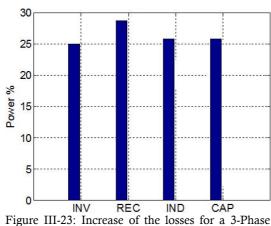

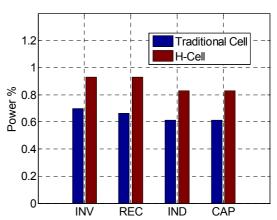

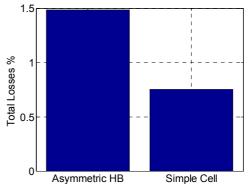

A la suite de la validation des formules analytiques par des simulations avec les modules de calcul de pertes du logiciel PSIM, nous effectuons une comparaison du rendement du système en considérant l'utilisation des trois topologies mise en avant ci-dessus. La comparaison est effectuée pour une puissance de 100 MW et une tension DC de 160 kV. En termes de rendement, la structure à simples cellules est la moins dissipative. Les deux autres à base de cellules bipolaires présentent des pertes plus élevées car elles requièrent au final plus de composants semi-conducteurs. Bien que ces topologies permettent au système de mieux gérer les conditions de court-circuit DC, une baisse même minime au niveau du rendement (de l'ordre 0,5%) est difficilement acceptable compte tenu des niveaux de puissance mis en jeu.

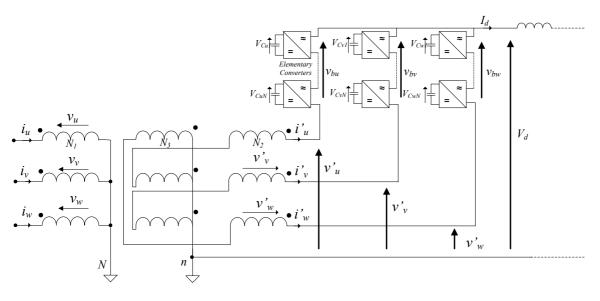

Nous présentons ensuite une nouvelle structure modulaire multiniveaux (Figure III-28) de convertisseur AC/DC. Contrairement à la version traditionnelle, cette topologie adopte pour

chaque phase une seule branche de blocs élémentaires et une seule boucle de contrôle du courant. D'autre part, celle-ci est connectée avec le réseau alternatif triphasé à travers un transformateur zig-zag. Le dimensionnement des composants réactifs et des semi-conducteurs est identique à la version de base. A titre d'exemple, nous proposons cette nouvelle structure pour remplacer les anciens redresseurs à base de diodes ou thyristors (Figure III-30). Nous développons ce remplacement en conservant le même transformateur de ligne et ainsi les mêmes niveaux de courant et tension. Nous effectuons les simulations en considérant un système de 10 MVA.

#### Chapitre IV : Commande MLI pour les convertisseurs modulaires multiniveaux

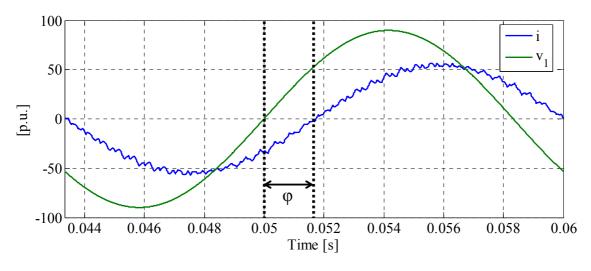

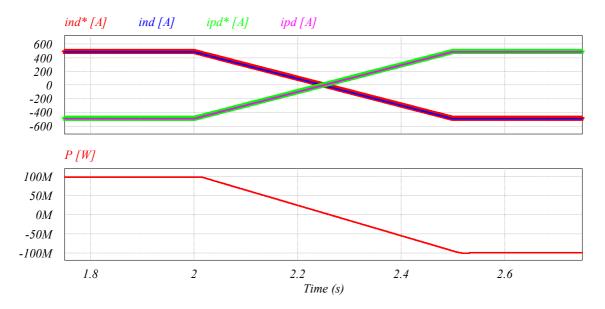

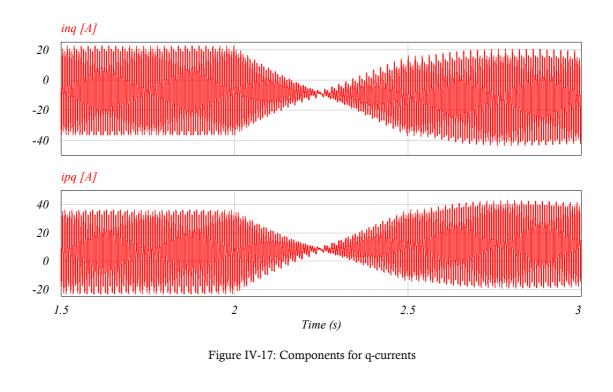

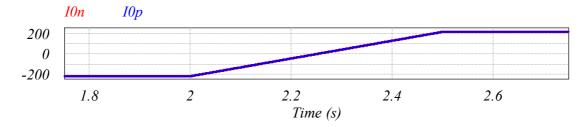

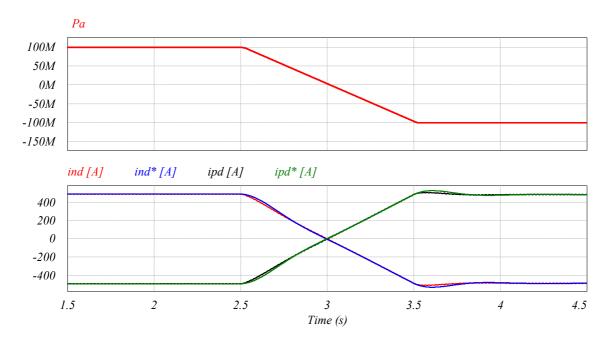

Nous développons dans ce chapitre le contrôle pour les structures MMC en considérant une modulation (commande MLI classique avec entrelacement des porteuses). A chaque fois, les simulations valident l'étude en considérant un système de 100 MW avec une tension de 160 kV sur le côté continu et côté alternatif un fonctionnement à facteur de puissance unitaire en mode onduleur ou redresseur.

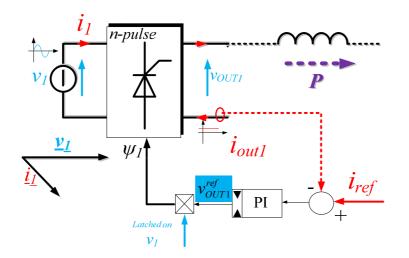

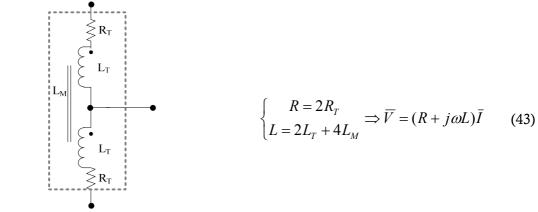

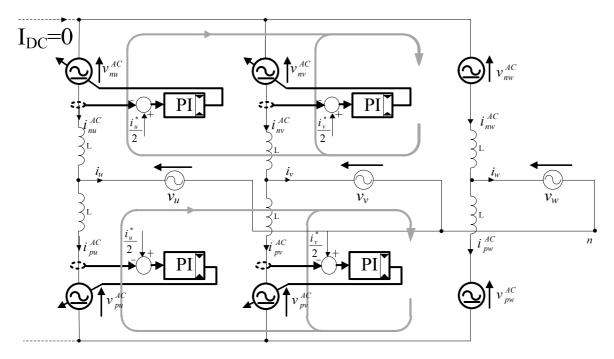

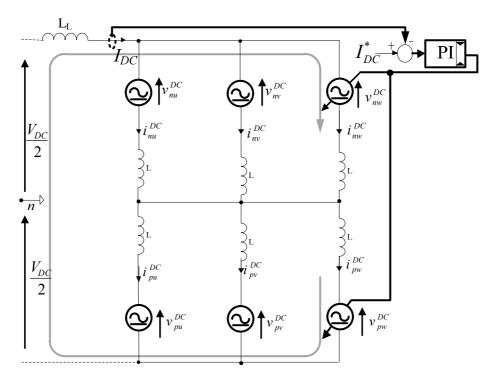

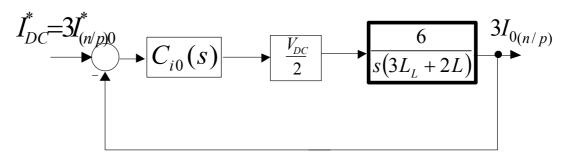

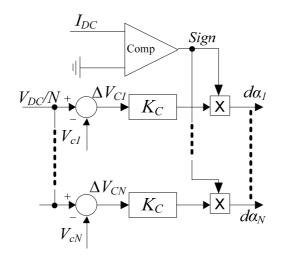

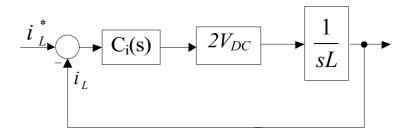

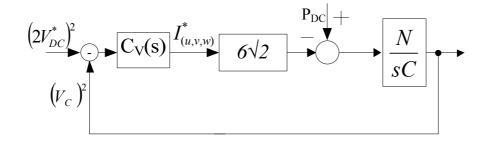

La commande pour convertisseurs modulaires multiniveaux proposée dans ce chapitre comporte trois boucles de contrôle (Figure IV-3) :

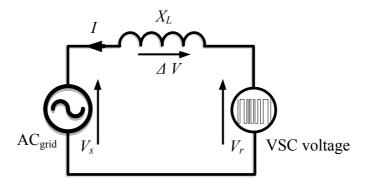

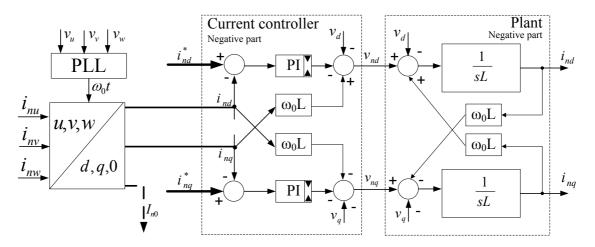

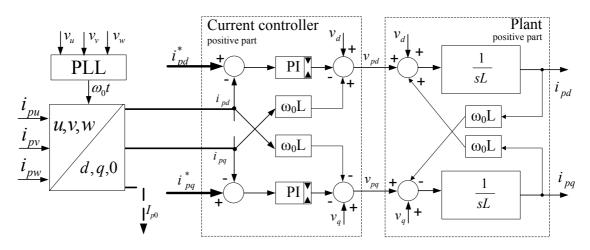

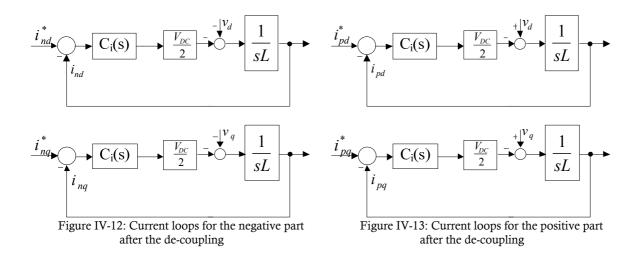

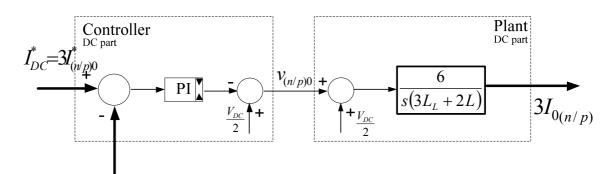

- Le contrôle du courant assure que chaque courant de branche ait les bonnes valeurs des composantes AC et DC nécessaires pour obtenir la puissance requise. Après avoir établi les équations électriques du MMC triphasé, nous exprimons les grandeurs électriques dans un repère tournant dq synchronisé sur le réseau alternatif. Une fois les équations établies dans ce nouveau repère, nous effectuons la synthèse des régulateurs PI de manière à ce que le système soit stable, capable de suivre la consigne de courant à la fréquence fondamentale et de supprimer la composante harmonique de courant de rang 2.

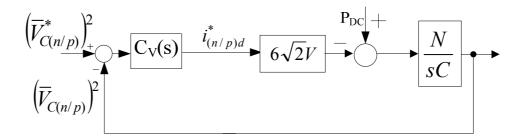

- En amont du contrôle de courant il faut assurer l'équilibre des énergies stockées dans les condensateurs. Compte tenu de la puissance mise en jeu côté continu, cette partie du contrôle adapte la puissance active afin de maintenir constantes les tensions sur les condensateurs des blocs. A cet effet un correcteur PI, dont nous donnons la synthèse, assure pour les branches positive et négative le contrôle de la valeur moyenne des tensions condensateurs.

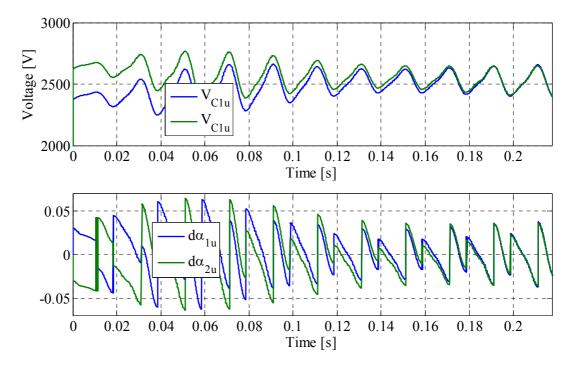

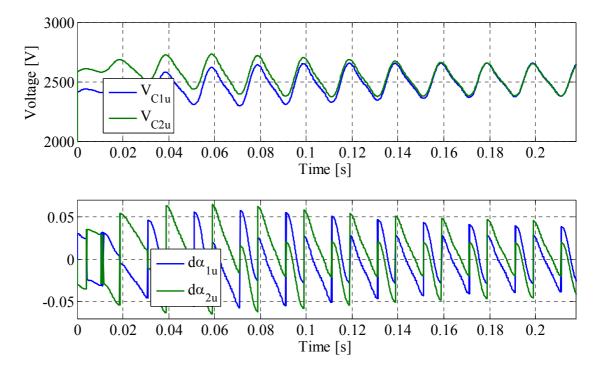

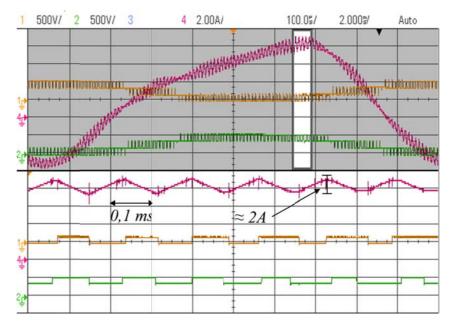

- Dans une branche du convertisseur, les tensions sur chaque bloc peuvent être déséquilibrées à cause des dispersions sur les valeurs des composants passifs et des pertes différentes dans les semi-conducteurs. Pour cela, dans le but de réguler chaque tension condensateur à la valeur désirée, nous prévoyons un contrôle local basé sur un correcteur proportionnel qui agit sur le signal modulant au niveau de chaque bloc élémentaire. Des simulations, basées sur un convertisseur ayant des branches avec des pertes par blocs différentes, valident l'efficacité de ce réglage.

#### Chapitre V : Prototype de convertisseur modulaire multiniveaux de 10 kW.

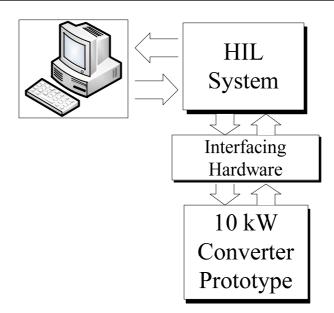

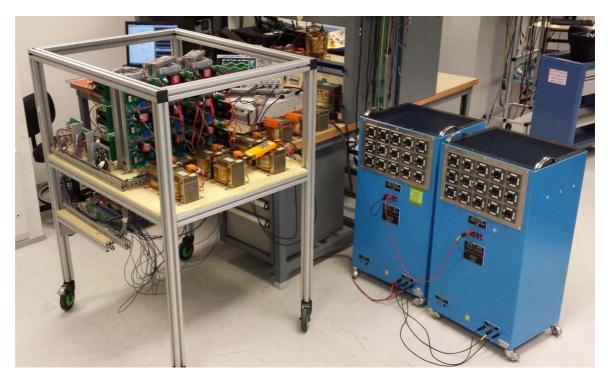

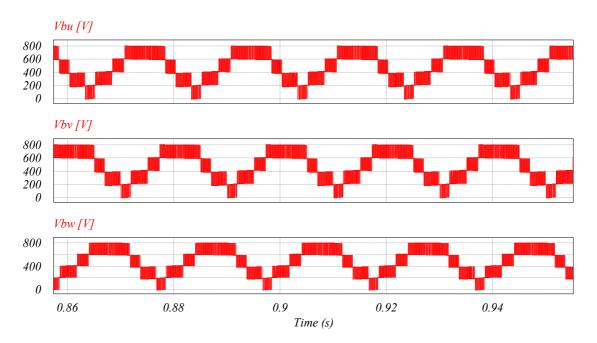

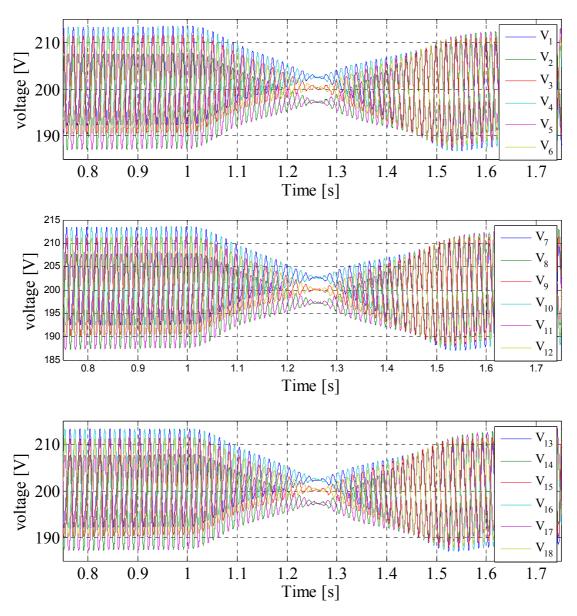

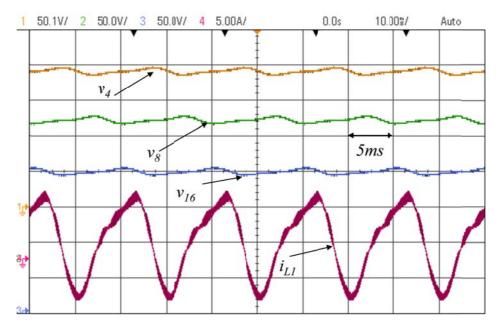

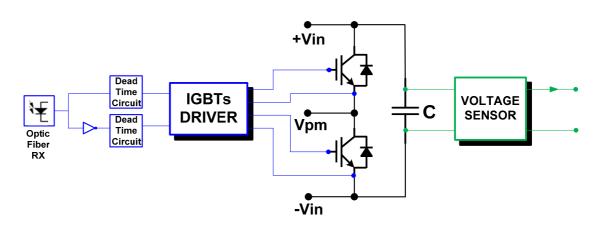

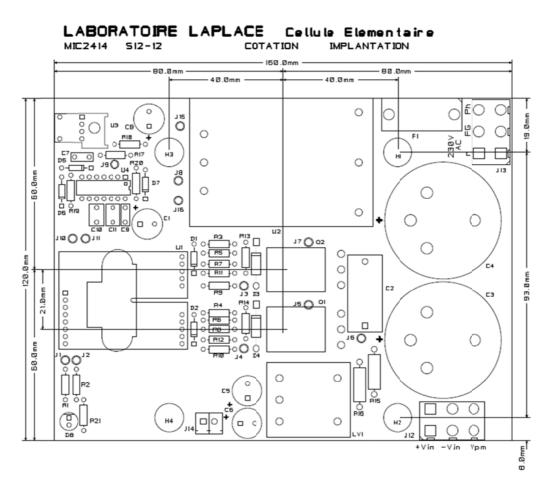

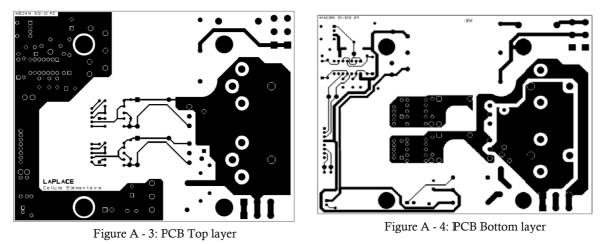

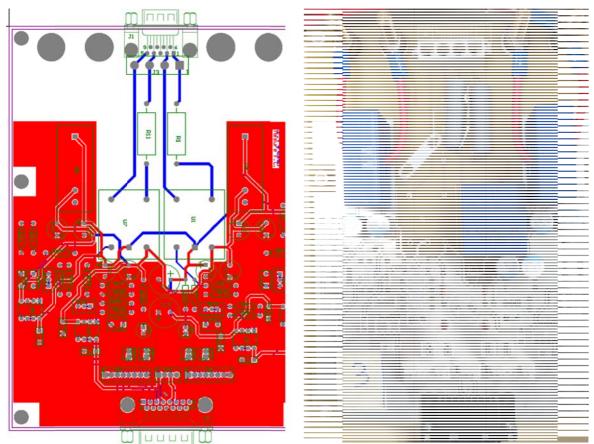

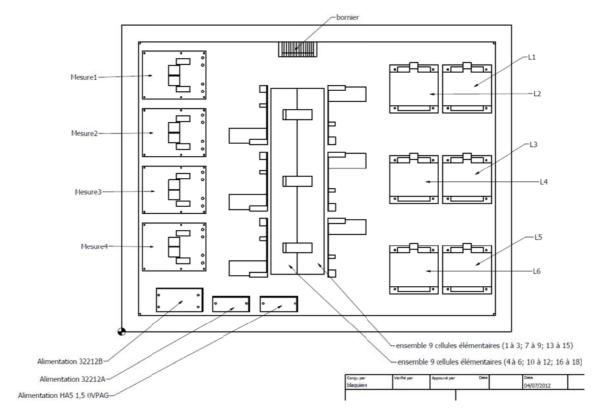

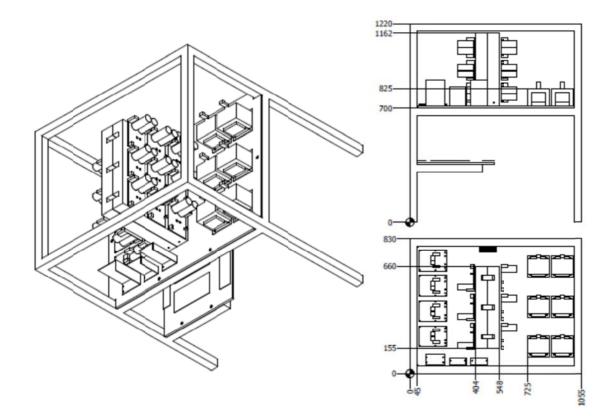

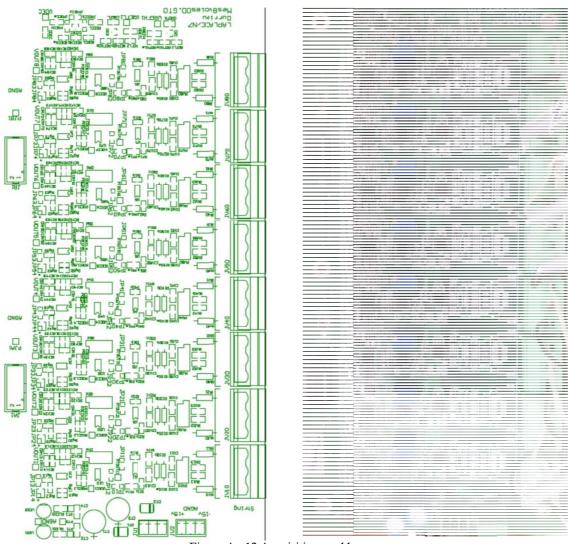

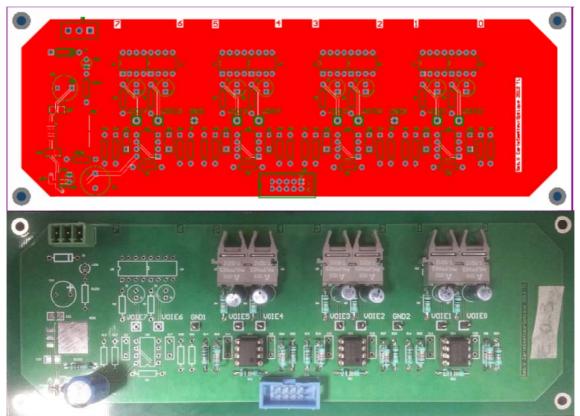

Afin de valider les résultats de calcul et de simulation, nous avons réalisé un prototype à puissance réduite. La structure inclut 18 cellules de commutation, elle est prévue pour fonctionner avec une tension DC de 600 V pour une puissance nominale de 10 kW (Figure V-

1). Cette maquette a été conçue et réalisée au LAPLACE. Le contrôle est implanté sur une plateforme DSP-FPGA.

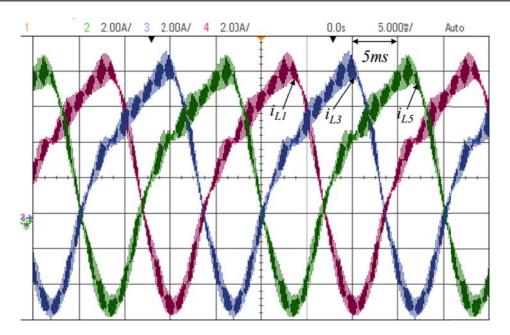

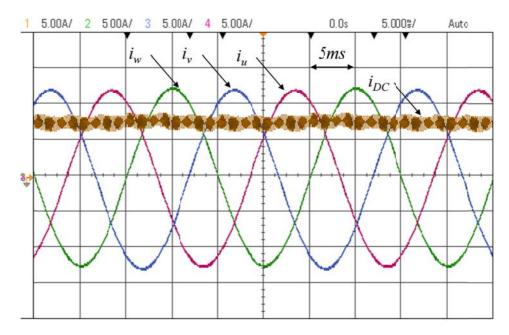

Nous testons une première configuration conformément à la Figure V-5. Nous considérons une branche unique par phase avec une charge RL triphasé de 4 kW en série, le tout est alimenté par une source de tension continue de 600 V. Après avoir étudié les boucles de contrôle et réalisé des simulations préliminaires, nous effectuons les tests en boucle fermée. Cette configuration a été initialement choisie car nous savons que la structure MMC classique, à deux branches par phase, peut difficilement limiter le courant en condition de défaut. Ainsi, la présence de la charge RL en série dans chaque branche limite « naturellement » le courant et permet sans danger la mise au point des chaines de mesure des signaux et la validation de la synthèse des régulateurs.

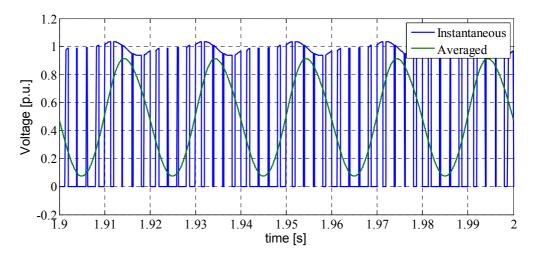

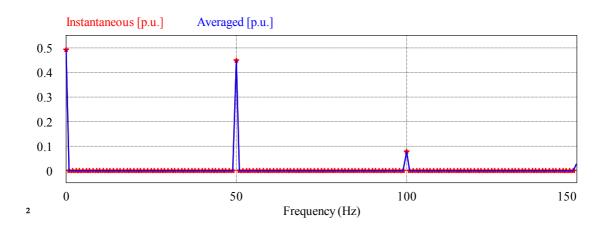

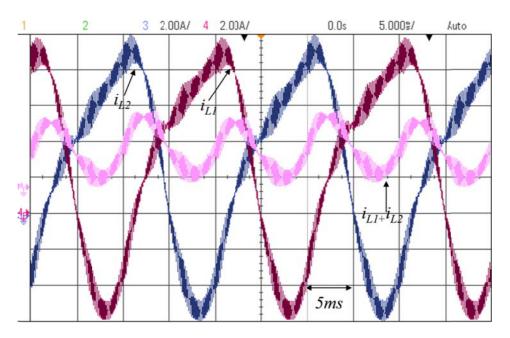

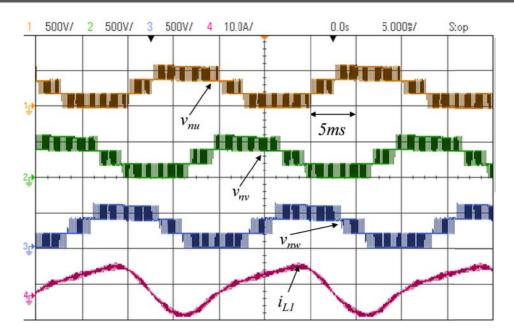

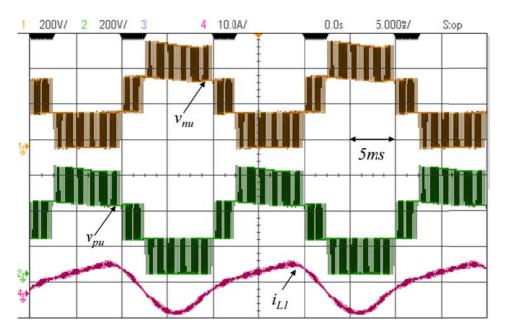

La bonne correspondance entre les résultats expérimentaux et les simulations nous permet alors d'aborder le fonctionnement dans une configuration MMC classique mais dans un premier temps avec un contrôle en boucle ouverte (Figure V-20) sur une charge RL triphasée de 5 kW.

Des simulations en boucle fermée avec un contrôle en boucle fermée dans un repère dq valident ensuite la synthèse des correcteurs pour le système de 10 kW (Figure V-16). Les simulations sont effectuées sur une charge RL triphasée (Figure V-20). Il nous reste à effectuer les tests en boucle fermée sur la maquette.

#### **Conclusions et Perspectives**

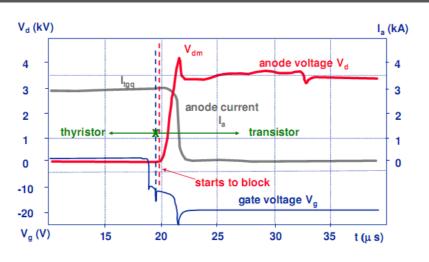

Aujourd'hui, les connexions HVDC constituent un élément de réponse aux besoins énergétiques mondiaux croissants. La technologie multiniveaux, associé au développement de semi-conducteurs haute tension contrôlés au blocage, va permettre aux convertisseurs de type onduleur de tension (VSC) de devenir la topologie la plus employée dans les systèmes HVDC. Toutefois, grâce aux avantages découlant de la facilité de mise en série des thyristors, les structures CSC restent encore mieux adaptées aux tensions élevées. A court terme, l'écart entre les deux topologies pourrait se réduire de manière significative grâce aux performances offertes par les thyristors blocables de type IGCT. Ces composants en boitier pressé présentent par rapport aux modules classiques plusieurs avantages : En cas de court-circuit dans une cellule, il n'y a pas de risque d'explosion du boitier et la structure monolithique de l'IGCT (*single wafer*) est plus adaptée pour l'encapsulation en boitier pressé qu'un ensemble de petites puces IGBT.

Ce travail de thèse a porté sur des topologies convertisseurs modulaires multiniveaux. Pour les études préliminaires, nous avons proposé un « macro modèle », indépendant de la topologie des blocs élémentaires, qui a permis une analyse directe du fonctionnement et des simulations plus rapides.

Le dimensionnement du convertisseur a été effectué pour deux stratégies de contrôle. La première considère seulement un contrôle de la composante fondamentale du courant de sortie mais entraîne la circulation d'un harmonique de rang deux dans les branches du circuit. La mise en œuvre d'inductances couplées dans les branches du convertisseur pourrait

constituer une bonne solution pour limiter ce courant mais dans la gamme de puissance visée (GW), une telle technologie augmenterait les coûts de manière considérable. En revanche, la seconde approche, consiste à contrôler le courant dans chacune des branches mais requiert un système de contrôle plus performant basé sur une commande en dq. A cette condition, la composante harmonique de courant de rang deux est supprimée, ce qui permet de minimiser le volume et donc le coût des éléments réactifs.

L'emploi des différentes topologies de bloc élémentaire rend le MMC plus flexible en termes de réversibilité en tension et en courant. En termes de pertes, à niveaux de puissance et de tension continue identiques, la simple cellule est la plus intéressante. Cependant, les autres topologies qui fournissent une tension de sortie bipolaire (pont asymétrique et pont complet) rendent la structure apte à limiter le courant en cas de court-circuit côté continu.

La commande MLI classique avec entrelacement des porteuses permet une réduction de la fréquence de commutation ce qui minimise les pertes dans les semi-conducteurs. Toutefois cette technique de modulation présente une limite inférieure en fréquence de commutation de l'ordre de 200 Hz. Quand le nombre de niveaux est très élevé, la modulation de la tension en « marches d'escalier » peut être très intéressante. Une étude de cette technique de modulation (marge d'escalier) sera développée prochainement. En effet, il nous reste à analyser l'impact de cette stratégie de modulation sur le dimensionnement des éléments réactifs et les pertes dans les semi-conducteurs pour la comparer à la commande MLI classique avec entrelacement des porteuses.

Différents aspects pourraient rendre le pont asymétrique intéressant dans les applications HVDC. En effet, par rapport à la structure classique, pour une même amplitude relative d'ondulation de tension, la capacité du condensateur de chaque bloc peut être réduite. De plus, comme le système effectue l'inversion du flux de puissance par le changement de polarité de la tension DC, cette topologie peut être employée pour remplacer les structures CSC dans des sous-stations HVDC avec l'avantage de travailler à facteur de puissance unitaire.

La nouvelle structure à une seule branche par phase (single loop) proposée dans le chapitre III permet un contrôle plus simple. Elle ne requiert pas d'inductances en série dans les branches puisqu'elle utilise directement l'inductance de fuite du transformateur dont le secondaire doit être couplé en zigzag pour annuler la composante continue du flux dans les colonnes. De plus l'isolement du transformateur est dimensionné uniquement pour la tension du réseau alternatif. Ceci n'est pas le cas de la configuration classique du MMC où, en plus de la composante alternative de tension, le transformateur doit supporter une tension d'isolement continue égale à la moitié de la tension sur le lien *DC* (composante homopolaire). Au-delà de ces considérations, et de manière plus générale, l'utilisation de cette nouvelle structure pourrait être intéressante pour remplacer d'anciens redresseurs à diodes ou à thyristors, en apportant les avantages découlant de la structure VSC.

Un prototype de 10 kW a été développé au laboratoire LAPLACE. Afin d'interfacer le circuit de puissance avec le système de contrôle, un ensemble de cartes « Interface Hardware » a été réalisée. Cet ensemble de cartes adapte les niveaux des signaux provenant des capteurs du prototype aux niveaux des tensions d'entrée du dispositif de commande. Il permet aussi le

filtrage du bruit pour les signaux analogiques. En ce qui concerne les signaux numériques de commande en provenance du dispositif de contrôle, ceux-ci sont transmis aux cellules de commutation via des fibres optiques.

Avant de démarrer les essais en puissance, une procédure préliminaire de test a été effectuée. Tous les capteurs ont été calibrés et toutes les connexions de la chaine de mesure ont été vérifiées. Enfin, l'interconnexion des masses de tout le système a été effectuée petit à petit afin d'éviter tout problème de compatibilité électromagnétique (CEM).

Les résultats expérimentaux avec une commande MLI classique avec entrelacement des porteuses ont été obtenus pour la structure à boucle simple et la structure classique. Le bon fonctionnement des boucles de contrôle a permis de valider le modèle du système et la synthèse des régulateurs.

Prochainement, ce prototype permettra d'une part de tester la structure à une branche par phase avec le transformateur à secondaire couplé en zigzag et d'autre part le fonctionnement en boucle fermée avec la commande en dq puis la modulation en « marche d'escalier ».

#### RIASSUNTO DETTAGLIATO DELLA TESI IN LINGUA ITALIANA

#### Capitolo I: A proposito di HVDC

Questo capitolo tratta i sistemi HVDC (le transport d'énergie électrique en courant continu Haute Tension) andandone ad evidenziare il ruolo chiave che hanno nel campo della trasmissione dell'energia elettrica attraverso la consultazione di circa 40 riferimenti bibliografici.

L'adozione di sistemi HVDC negli ultimi 40 anni ha avuto un ruolo fondamentale per i sistemi di trasmissione per una serie di considerazioni tecniche ed economiche.

• Rispetto ai sistemi di trasmissione AC, trasmettere in corrente continua, nonostante il costo addizionale dovuto alle sottostazioni di conversione, inizia a diventare conveniente per distanze maggiori di 800 km per linee aeree e 50 km per linee sottomarine (Figure I-1).

• Il continuo miglioramento delle tecnologie dei dispositivi semiconduttori essendo al cuore delle tecnologie HVDC

• Sistemi in corrente continua consentono interconnessioni tra reti eterogenee che possono essere asincrone tra loro e/o a frequenza diversa.

Una descrizione sui principi di connessione HVDC è stata illustrata facendo riferimento alle principali installazioni attualmente esistenti ciascuna delle quali in grado di gestire potenze dell'ordine dei GWs.

Due tipi di connessione HVDC sono utilizzate. Quelle basate su convertitori AC/DC di corrente (CSC) e quelle basate su convertitori AC/DC di tensione (VSC). I lavori presenti nella letteratura corrente fino ad oggi si sono sempre focalizzati sulla topologia dei convertitori, in questo lavoro una delucidazione esaustiva sul concetto di trasferimento di potenza di tipo HVDC sia per strutture CSC che VSC è stata data.

Prima di scendere nel dettaglio i principali dispositivi semiconduttori disponibili sul mercato ed impiegati per le alte tensioni sono stati descritti attraverso la consultazione di circa venti riferimenti bibliografici. Lo studio ha messo in luce le varie evoluzioni dei dispositivi dandone un'ordine di grandezza sulle tensioni e correnti nominali sostenibili per ciascuno di essi. Inoltre una descrizione dettagliata della tecnica presspack è stata data giacché tale tecnologia può essere considerata la meglio candidata per l'utilizzo e l'impiego di dispositivi semiconduttori nelle alte potenze.

Una descrizione dei convertitori CSC basati su tiristori è stata fornita al fine di rendere meglio comprensibile l'approccio adottato per lo scambio di potenza per queste strutture. Grazie al fatto che i tiristori non presentano problemi di connessione diretta in serie, i sistemi CSC-HVDC riescono a raggiungere tensioni dell'ordine dei 500 kV. Ovviamente la topolgia non consente il controllo indipendente della potenza attiva e reattiva ed inoltre esibisce un contenuto armonico in corrente tale da richiedere dispositivi di filtraggio che occupano il 20-30 % della superficie totale di una sottostazione (Figure I-42).

Una descrizione dei convertitori VSC modulati PWM (MLI) basati su dispositivi di commutazione controllabili sia in apertura che in chiusura (IGBT) è stata fornita. Dopodiché la trasmissione di energia HVDC basata su convertitori VSC è stata illustrata. Le topologie VSC riescono ad effettuare il trasferimento di potenza attiva e reattiva in maniera indipendente. D'altro canto per topologie classiche a due livelli si riesce al massimo ad operare a 320 kV a causa dei problemi dovuti alla messa in serie di dispositivi IGBT.

Le topologie VSC sono state prese in considerazione nel lavoro. In particolare una descrizione delle strutture multilivello è stata data grazie alla loro capacità di lavorare ad alte tensioni. Tali topologie rispetto a quelle tradizionali riescono a garantire una forma d'onda quasi sinusoidale riducendo il contenuto armonico e permettendo una riduzione degli elementi di filtraggio. All'interno delle topologie multilivello la struttura modulare multilivello (MMC) è stata presentata nel capitolo e studiata nel lavoro di tesi. Tale struttura consiste nella messa in serie di convertitori elementari (Figure I-62) normalmente identici (per questo modulare). Tale struttura è stata preferita a quelle tradizionali giacché garantisce una modularità in termini di produzione industriale e non ha limitazioni superiori sul valore della tensione DC poiché è possibile sempre aggiungere convertitori elementari in serie.

#### Capitolo II: Strutture modulari multilivello

La struttura modulare multilivello è stata studiata in questo capitolo. La configurazione trifase per questa struttura è formata dalla connessione di due rami per fase (Figure II-1). Ogni ramo impone metà della tensione DC e la tensione al lato AC. Ciascun ramo inoltre conduce un terzo della corrente DC e la metà della corrente AC. La combinazione tra i due rami fa si che si ottengano le correnti e tensioni AC e DC necessarie al trasferimento di potenza richiesto. Per l'analisi un modello medio della struttura è stato estratto (macro modello) al fine di semplificare le considerazioni preliminari. Tale modello non considera gli effetti delle armoniche dovuti ai dispositivi di commutazione ma garantisce una maggiore velocità nelle simulazioni poiché semplifica i calcoli. Lo studio inoltre è stato ottenuto indipententemente dalla scelta della topologia per il convertitore elementare e considerando una phase shifted sinusoidal PWM (commande MLI classique avec entrelacement des porteuses). La potenzialità dello studio, oltre alla semplificazione della comprensione, sta nel fatto che tale struttura è stata resa altamente flessibile e versatile in termini di tensioni e correnti gestite.

In una analisi preliminare correnti e tensioni del sistema sono state analizzate. Dal punto di vista armonico di corrente, ciascun ramo, oltre alle componenti DC ed AC conduce una componente AC al doppio della frequenza fondamentale che rimane all'interno della struttura (corrente circolante in Figure II-9). Questa componente deriva dal bilanciamento energetico tra i due bracci che compongono ogni fase. La soppressione di tale componente gioca un ruolo fondamentale nel dimensionamento dei componenti reattivi che è stata effettuata considerando due casi.

Il primo caso considera un sistema controllato in maniera tale per cui non si è in grado di sopprimere l'armonica di II ordine della corrente di ramo. Per tale motivo la compensazione è

effettuata in maniera hardware. Al crescere del condensatore posto in parallelo a ciascun convertitore elementare e dell'induttore di ramo tale armonica si riduce. Per problemi di controllabilità del sistema dovuti ad elevati valori dell'induttore di ramo una nuova configurazione di tipo tripolare per l'induttore è stata proposta nel lavoro. Tale induttore è configurato in maniera tale da imporre una elevata induttanza di ramo al fine di sopprimere la II arminica nella corrente ed una ridotta induttanza di uscita garantendo la controllabilità del sistema. Tale approccio ovviamente richiede un hardware più costoso ma un controllo più semplice.

Il secondo caso considera un controllo leggermente più complesso capace di controllare ciascuna corrente di ramo in maniera tale da ottenere il riferimento desiderato alla armonica fondamentale di corrente e di sopprimere anche la corrente circolante nel ramo alla seconda armonica della fondamentale. In tali condizioni il dimensionamento dei componenti passivi si riduce giacché solo l'armonica di corrente a frequenza fondamentale è considerata. La complicatezza del controllo non è un problema al giorno d'oggi grazie alla vasta scelta di dispositivi di controllo disponibili sul mercato. Per questo motivo è stato preferito in questo lavoro di tesi. Per tutti i casi, simulazioni su un sistema da 100 MW composto da 64 convertitori elementari per ramo hanno validato lo studio.

#### Capitolo III: Nuove topologie multilivello per sottostazioni HVDC

In questa parte del lavoro nuove configurazioni per la struttura modulare multilivello sono state studiate e proposte. Ciò è avvenuto andando a cambiare di volta in volta la topologia del convertitore elementare. Disporre di differenti topologie ha reso la struttura MMC più versatile e flessibile nei confronti dei livelli di tensione e corrente.

La prima topologia considerata come convertitore elementare è la cella semplice che rappresenta la versione base dell'MMC. Questa topologia è bidirezionale in corrente ma unipolare in tensione. Per tale motivo in condizioni di fault DC il sistema multilivello non è in grado di limitare la correne di corto circuito rischiando di danneggiare i dispositivi semiconduttori. Solo celle bipolari sono in grado di meglio limitare la corrente in condizioni di fault DC. A tale scopo il ponte asimmetrico ad H ed il ponte intero ad H sono stati considerati. La prima struttura (Figure III-8) è bipolare in tensione ma unidirezionale in corrente. Per tale motivo l'impiego di questa topologia rende la struttura MMC poco adatta a scambi di potenza reattiva. In condizioni di fattore di potenza unitario, essendo tale topologia unidirezionale in corrente, il sistema effettua l'inversione della potenza tramite l'inversione della tensione che è tipico dei sistemi CSC. Per questo motivo tale struttura può essere anche utilizzata per il rimpiazzo immediato di convertitori basati su tiristori. Infine tra le celle bipolari anche il ponte ad H è stato considerato (Figure III-11). Ovviamente tale struttura è la più flessibile delle prime due essendo anche bidirezionale in corrente ma esige il doppio dei componenti.

In questa parte un approccio analitico per il calcolo delle perdite nei dispositivi è stato dato. Tale approccio ha reso la valutazione della efficienza del sistema diretta veloce. Tale approccio era stato evitato in letteratura giacché la componente continua della forma di corrente nei dispositivi, dovuta alla struttura MMC, rendeva il calcolo delle perdite molto complesso. Nel presente lavoro invece la formalizzazione analitica delle perdite è stata formalizzata e validata.

A valle della validazione delle forme analitiche tramite il software PSIM un confronto sul rendimento del sistema è stato effettuato considerando l'uso delle tre topologie evidenziate sopra. Il confronto è stato effettuato a parità di potenza (100 MW) e di tensione DC (160 kV). In termini di rendimento la singola cella è la meno dissipativa. Le altre due celle bi-polari hanno un incremento delle perdite giacché richiedono un incremento dei componenti, tali perdite non sono accettabili per i livelli di potenza gestita. Ovviamente tali topologie permettono al sistema di gestire meglio le condizioni di faults.

Successivamente nel capitolo una nuova struttura modulare multilivello è presentata (Figure III-28) chiamata Raddrizzatore a singola semionda. Per ogni fase questa topologia adotta un solo ramo rispetto alla versione tradizionale. D'altro canto si interfaccia con la rete attraverso un trasformatore zig-zag. Il dimensionamento dei componenti reattivi e dei dispositivi semiconduttori è lo stesso della versione base. Al fine di validare lo studio del macromodello questa nuova struttura è stata proposta per rimpiazzare i vecchi raddrizzatori basati su diodi o tiristori (Figure III-30). Il rimpiazzo è stato sviluppato conservando lo stesso trasformatore di linea e dunque gli stessi livelli di corrente e tensione. Simulazioni sono state effettuate considerando un sistema da 10 MVA.

#### Capitolo IV: Un nuovo controllo PWM per le strutture modulari multilivello

Un nuovo controllo per le strutture MMC è stato sviluppato in questo capitolo considerando una modulazione (commande MLI classique avec entrelacement des porteuses). Volta per volta simulazioni hanno validato lo studio considerando un sistema da 100 MW con una tensione DC di 160 kV. Le simulazioni sono state inoltre fornite per condizioni di funzionamento a fattore di potenza unitario in modalità inverter e raddrizzatore.

Il controllo dei sistemi MMC in letteratura hanno sempre cercato di sopprimere la seconda armonica di ramo della corrente in maniera parallela al controllo tradizionale. Ci sono numerosi lavori che adottano tale sistema rendendo il controllo alquanto complesso sia alla comprensione che all'implementazione [49]-[51].

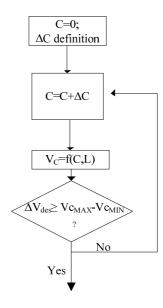

Il controllo tipico per i sistemi multilivello è costituito da tre cicli di controllo fondamentali (Figure IV-3).

• Il controllo di corrente, assicura che ciascuna corrente di ramo abbia i giusti valori per le componenti AC e DC necessare ad ottenere la potenza richiesta. L'approccio per tale controllo è stato effettuato tramite una sovrapposizione degli effetti. Dopo aver impostato le equazioni caratterizzanti il sistema è stata effettuata una trasformazione delle grandezze nel sistema di riferimento ad assi rotanti DQ. Una volta definite le equazioni, la sintesi dei regolatori PI è stata effettuata in maniera tale rendere il sistema in grado di inseguire la corrente desiderata e sopprimere la seconda armonica di corrente (corrente di ricircolo) nei margini di stabilità. Il sistema di controllo proposto nel lavoro di tesi è lineare ed, attraverso la taratura dei regolatori, agisce in maniera tale da sopprimere anche la seconda armonica a frequenza fondamentale di corrente. L'innovazione sta nel fatto che il tutto è effettuato attraverso un singolo ciclo senza l'aggiunta di loops addizionali adottati in [50]-[51].

• A monte del controllo di corrente è posto il bilancio di energia di ramo. Tale parte di controllo regola la potenza attiva necessaria a mantenere tutte le tensioni sui condensatori di ramo costanti al valore desiderato. La sintesi dei regolatori PI è stata fornita.

• Ciascuna cella di ramo può essere sbilanciata a causa delle differenti tolleranze dei componenti passivi, conduzioni diseguali e/o perdite differenti nei dispositivi semiconduttori ed infine differenti risoluzioni dei sensori. Per questo motivo al fine di bilanciare ogni cella al valore di tensione desiderato, un controllo locale è stato previsto definito come il bilancio della tensione di cella. Un correttore proporzionale per ogni convertitore elementare è stato adottato e sintetizzato. Tale controllo in maniera indipendente dai due precedenti agisce direttamente sull'indice di modulazione. Simulazioni in condizioni di celle sbilanciate hanno validato lo studio.

#### Capitolo V: Il prototipo MMC da 10 kW

Al fine di validare i risultati analitici e simulativi un prototipo a potenza ridotta è stato realizzato. Tale struttura include 18 celle di commutazione di tipo semplice (simple cell), una tensione DC di 600 V ed una potenza nominale di 10 kW (Figure V-1). Il prototipo è stato progettato e realizzato presso il LAPLACE. Inoltre al fine di effettuare i test sperimentali il controllo è stato implementata tramite piattaforma DSP-FPGA. I livelli di potenza e di tensione scelti per il prototipo sono abbastanza alti per una rispetto a quelli adottati in letteratura per la sperimentazione da laboratorio di sistemi MMC.

Una prima configurazione in modalità single loop è stata testata (Figure V-5). In particolare solo un ramo per fase si è considerato con in serie un carico RL da 4 kW. Il tutto in parallelo alla sorgente DC. Dopo la sintesi del controllo e simulazioni preliminari, sono stati effettuati tests a ciclo chiuso. Questa è una configurazione intermedia che ha un duplice scopo. È noto che la classica struttura MMC è poco capace di limitare la corrente di ramo in condizioni di faults, per questo motivo non è stata preferita come prima prova. La presenza del carico RL in serie al ramo infatti limita la corrente nel ramo garantendo lo stesso un set-up delle catene di segnale e la validazione della sintesi dei regolatori in condizioni di sicurezza. È definita configurazione intermedia giacché a causa delle proprietà unipolari della cella semplice al carico viene imposta anche una componente DC all'interno del ramo. In ogni caso la buona corrispondenza tra simulazioni e prove sperimentali hanno reso il passaggio alla configurazione con trasformatore zig-zag immediato.

In un secondo step la struttura MMC a ciclo aperto è stata considerata (Figure V-20). Simulazioni preliminari a ciclo chiuso con un controllo nel sistema di riferimento rotante DQ hanno validato la sintesi dei controllori per il sistema da 10 kW (Figure V-16). Le simulazioni sono state effettuate imponendo la rete al lato AC. Il sistema è stato dunque testato in

modalità raddrizzatore e inverter a fattore di potenza unitario. Successivamente prove sperimentali a ciclo aperto sono state effettuate imponendo al sistema un carico RL di circa 5 kW (Figure V-20) al fine di validare la giusta modulazione e il corretto dimensionamento dei componenti reattivi (condensatori ed induttori). Resta da effettuare ovviamente il passaggio dei test a ciclo chiuso per la struttura MMC.

#### Conclusioni e Prospettive

Al giorno d'oggi le connessioni HVDC sono una buona risposta alla fabbisogno energetico mondiale che è sempre più crescente. Le topologie multilivello stanno rendendo i Voltage source converters (VSC) tra i più impiegati nei sistemi HVDC. Lo sviluppo dei dispositivi semiconduttori controllati in fase di spegnimento ed impiegati per alte tensione hanno reso queste strutture molto interessanti. D'altro canto grazie ai vantaggi derivanti dalla facilità della messa in serie di tiristori, le strutture CSC gestiscono meglio le alte tensioni. Nel prossimo futuro, il divario tra le due topologie verrà decisamente ridotto grazie alle prestazioni offerte dai dispositivi IGCT sia nella fase di accensione che di spegnimento. L'inscatolamento a pressione (press pack) porta inoltre una serie di vantaggi rispetto ai moduli classici specialmente in condizioni di emergenza dove c'è il rischio di esplosione. La struttura a singolo tassello (single wafer) rende l'IGCT più adatto per l'inscatolamento a pressione rispetto all'IGBT. Per queste ragioni l'IGCT sembra essere il dispositivo più attrattivo in applicazioni VSC-HVDC.

Il lavoro di tesi è stato focalizzato sui convertitori modulari multilivello. Per studi preliminari il "macromodello" ha consentito valutazioni dirette e simulazioni più veloci. Inoltre ha reso il modello indipendente dalla particolare topologia.

Il dimensionamento del sistema è stato effettuato attraverso due approcci di controllo. Il primo considera solo un controllo sulla corrente di uscita AC che determina una considerevole seconda armonica nel ramo. L'induttore tripolare accoppiato potrebbe essere una buona soluzione al fine di limitare questa corrente ma nel campo delle applicazioni di alta potenza, la particolarità dell'hardware accresce i costi in maniera considerevole. Il secondo approccio invece consiste nel controllo della corrente di ciascun ramo, inoltre esso richiede un sistema di controllo più efficiente basato sul sistema di riferimento rotante DQ. Sotto questa condizione la seconda componente armonica della corrente è cancellata andando a ridurre i costi degli elementi reattivi.

L'impiego di differenti topologie come convertitore elementare rende l'MMC più flessibile in termini di reversibilità di tensione e corrente. In termini di perdite a parità di potenza e tensione DC, la cella semplice è più conveniente. Le altre topologie però che forniscono una tensione bipolare (HB asimmetrico e ponte ad H) rendono la struttura capace di limitare la corrente di corto circuito in caso di fault DC.

La commande MLI classique avec entrelacement des porteuses porta ad una riduzione della frequenza di switching e dunque riduce le perdite nei dispositivi. Certamente questa tecnica di modulazione presenta un limite inferiore sulla frequenza di switching. Quando il numero dei livelli è molto elevato la modulazione stai case (marge d'escalier) può essere molto interessante per strutture multilivello. Uno studio della modulazione (marge d'escalier) sarà presto sviluppato. Infatti rimane da fare una investigazione sugli effetti della modulazione nei confronti del dimensionamento di elementi reattivi e nei confronti delle perdite nei dispositivi rispetto alla (commande MLI classique avec entrelacement des porteuses).

Differenti aspetti potrebbero rendere il ponte asimmetrico ad H interessante nelle applicazioni HVDC. Se questa topologia è scelta, il condensatore di cella potrebbe essere ridotto a parità di ampiezza di oscillazione della tensione. Siccome il sistema effettua l'inversione del flusso di potenza tramite il cambiamento della polarità della tensione DC, questa topologia può essere impiegata per rimpiazzare strutture CSC per sottostazioni HVDC con il vantaggio di lavorare a fattore di potenza unitario.

La struttura nuova a controllo unico (single loop) proposta nel capitolo III permette un controllo più semplice. La topologie non richiede il doppio induttore poiché utilizza l'induttore parassita posto in serie al trasformatore accoppiato zig-zag. l'accoppiamento del trasformatore richiede più rame di un classico avvolgimento. L'isolamento del trasformatore deve essere effettuato solo per la tensione AC. Questo non è il caso della classica configurazione per l'MMC dove il trasformatore deve sostenere un isolamento DC pari alla metà della tensione sullo DC link (sequenza omopolare). Oltre a queste considerazioni, l'uso di questa nuova struttura potrebbe essere interessante per rimpiazzare i vecchi raddrizzatori garantendo i vantaggi derivanti dalle strutture VSC.

Un prototipo da 10 kW è stato sviluppato nel laboratorio LAPLACE. Al fine di interfacciare il circuito di potenza con il sistema di ptototipazione rapida, una piattaforma di schede piazzate sulla struttura chiamata "Hardware di Interfaccia" è stata realizzata. Questo hardware adatta i livelli dei segnali provenienti dai sensori del prototipo verso il livello delle tensioni di ingresso del dispositivo di pototipazione rapida. Inoltre tale hardware fornisce il filtraggio del rumore per i segnali analogici. Anche per i segnali digitali provenienti dal dispositivo di prototipazione, una conversione elettro-ottica è stata fornita dall'hardware di interfaccia al fine di controllare le celle.

Prima di avviare le prove in potenza, una procedura preliminare è state eseguita. Tutti i sensori sono stati calibrati e la giusta connessione della catena di segnale è stata verificata. Infine l'ottimizzazione della configurazione delle masse di tutto il sistema è stata effettuata passo dopo passo al fine evitare tutti i probleme dovuti alla compatibilità elettromagnetica (EMI)

Risultati sperimentali in (commande MLI classique avec entrelacement des porteuses) sono stati ottenuti per la struttura a singolo ciclo e quella classica. Il buon funzionamento dei cicli di controllo ha validato il modello del sistema e la sintesi dei regolatori.

Prossimamente, questo prototipo permetterà di testare la struttura a singolo ciclo con il trasformatore zig-zag, il funzionamento a ciclo chiuso nel sistema di riferimento dq e la modulazione a (marge d'escalier).

# Content

| Chapter                                                         | I                                                                | HVDC SYSTEMS                                                                                                                                                                                              | 1                                                                                                                                              |

|-----------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| I.1                                                             | Aboı                                                             | ıt HVDC                                                                                                                                                                                                   | 1                                                                                                                                              |

| I.2                                                             | HVD                                                              | OC Connection Systems                                                                                                                                                                                     | 3                                                                                                                                              |

| I.2.                                                            | 1 '                                                              | The concept of a HVDC connection                                                                                                                                                                          | 3                                                                                                                                              |

| I.2.                                                            | 2                                                                | HVDC Configurations                                                                                                                                                                                       | 7                                                                                                                                              |

| I.2.                                                            | 3                                                                | Semiconductor devices for HVDC systems                                                                                                                                                                    | 8                                                                                                                                              |

| I.2.                                                            | 4                                                                | CSC-Phase controlled converters                                                                                                                                                                           | 16                                                                                                                                             |

| I.2.                                                            | 5                                                                | CSC-HVDC SYSTEMS                                                                                                                                                                                          | 20                                                                                                                                             |

| I.2.                                                            | 6                                                                | VSC-PWM based AC/DC converters                                                                                                                                                                            | 21                                                                                                                                             |

| I.2.                                                            | 7                                                                | VSC-HVDC systems                                                                                                                                                                                          | 26                                                                                                                                             |

| I.3                                                             | VSC-                                                             | -HVDC multilevel topologies                                                                                                                                                                               | 27                                                                                                                                             |

| I.3.                                                            | 1                                                                | Neutral Point Clamped (NPC)                                                                                                                                                                               | 29                                                                                                                                             |

| I.3.                                                            | 2                                                                | Flying capacitor                                                                                                                                                                                          | 29                                                                                                                                             |

| I.3.                                                            | .3                                                               | Cascaded Multilevel Inverters                                                                                                                                                                             | 31                                                                                                                                             |

| т 4                                                             |                                                                  |                                                                                                                                                                                                           |                                                                                                                                                |

| I.4                                                             | Conc                                                             | clusions                                                                                                                                                                                                  | 32                                                                                                                                             |

| 1.4<br>Chapter                                                  |                                                                  | Clusions                                                                                                                                                                                                  |                                                                                                                                                |

|                                                                 | II.                                                              |                                                                                                                                                                                                           | 33                                                                                                                                             |

| Chapter                                                         | II. The                                                          | MMC systems                                                                                                                                                                                               | 33<br>34                                                                                                                                       |

| Chapter<br>II.1                                                 | II                                                               | MMC systems<br>Macro Model                                                                                                                                                                                | 33<br>34<br>36                                                                                                                                 |

| Chapter<br>II.1<br>II.1                                         | II. 7<br>The 1<br>.1 7                                           | MMC systems<br>Macro Model<br>Macro model validation                                                                                                                                                      | 33<br>34<br>36<br>38                                                                                                                           |

| Chapter<br>II.1<br>II.1<br>II.1                                 | II. 7<br>The 1<br>.1 7<br>.2 7<br>Outp                           | MMC systems<br>Macro Model<br>Macro model validation<br>Study of the MMC basic structure                                                                                                                  | 33<br>34<br>36<br>38<br>40                                                                                                                     |

| Chapter<br>II.1<br>II.1<br>II.1<br>II.2                         | II. The I<br>1                                                   | MMC systems<br>Macro Model<br>Macro model validation<br>Study of the MMC basic structure<br>put current imposition                                                                                        | 33<br>34<br>36<br>38<br>40<br>42                                                                                                               |

| Chapter<br>II.1<br>II.1<br>II.1<br>II.2<br>II.2                 | II. The I                                                        | MMC systems<br>Macro Model<br>Macro model validation<br>Study of the MMC basic structure<br>put current imposition<br>Cell capacitor                                                                      | <ol> <li>33</li> <li>34</li> <li>36</li> <li>38</li> <li>40</li> <li>42</li> <li>43</li> </ol>                                                 |

| Chapter<br>II.1<br>II.1<br>II.2<br>II.2<br>II.2                 | II. The J<br>1                                                   | MMC systems<br>Macro Model<br>Macro model validation<br>Study of the MMC basic structure<br>put current imposition<br>Cell capacitor<br>Branch inductor                                                   | <ol> <li>33</li> <li>34</li> <li>36</li> <li>38</li> <li>40</li> <li>42</li> <li>43</li> <li>48</li> </ol>                                     |

| Chapter<br>II.1<br>II.1<br>II.2<br>II.2<br>II.2<br>II.2         | II. The I<br>1                                                   | MMC systems<br>Macro Model<br>Macro model validation<br>Study of the MMC basic structure<br>out current imposition<br>Cell capacitor<br>Branch inductor<br>Simulations                                    | <ol> <li>33</li> <li>34</li> <li>36</li> <li>38</li> <li>40</li> <li>42</li> <li>43</li> <li>48</li> <li>53</li> </ol>                         |

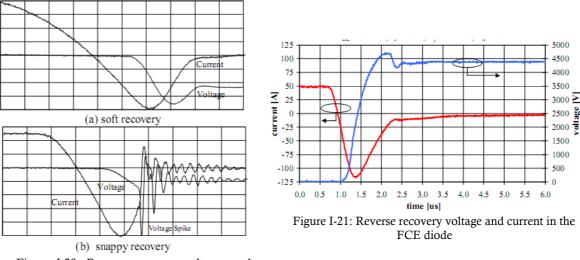

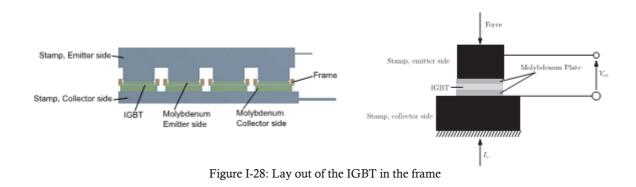

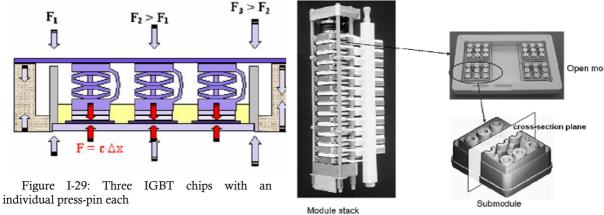

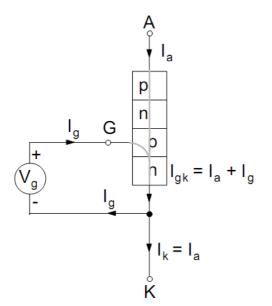

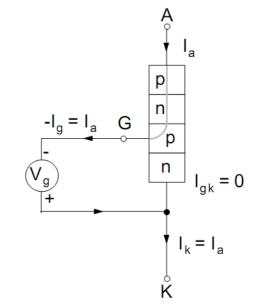

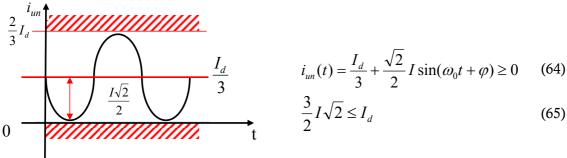

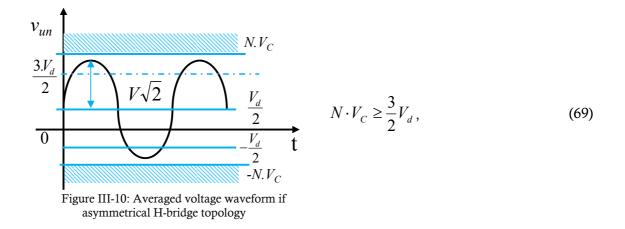

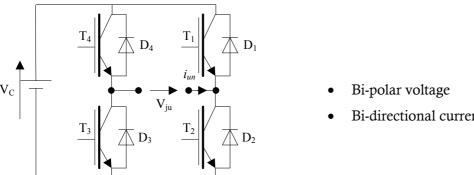

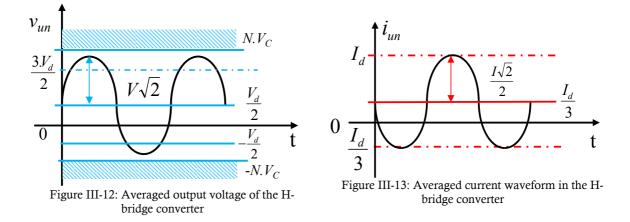

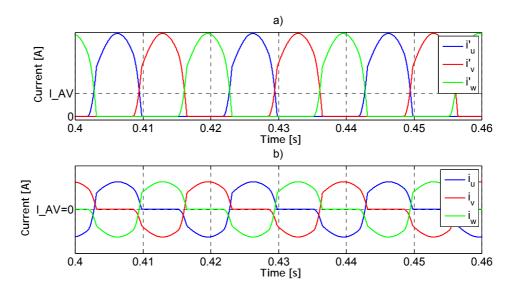

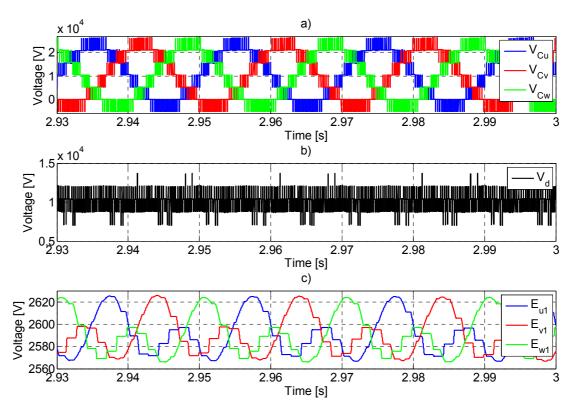

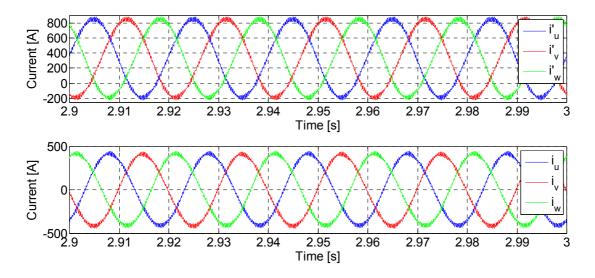

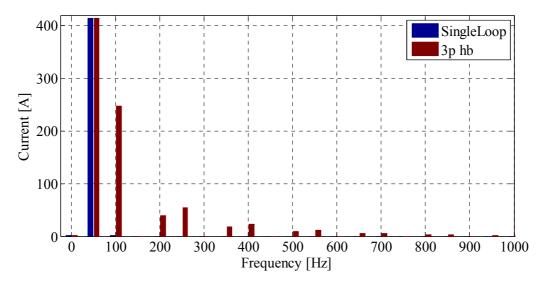

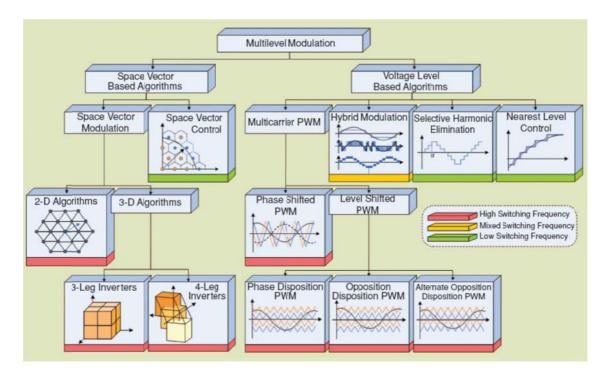

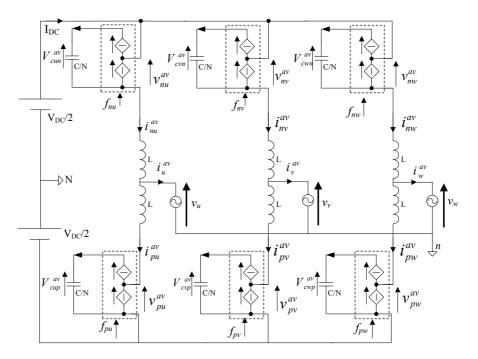

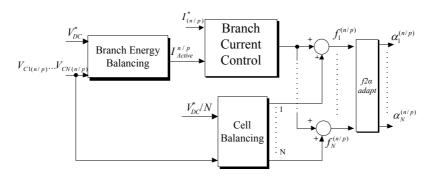

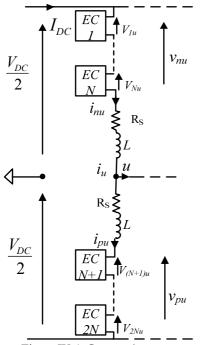

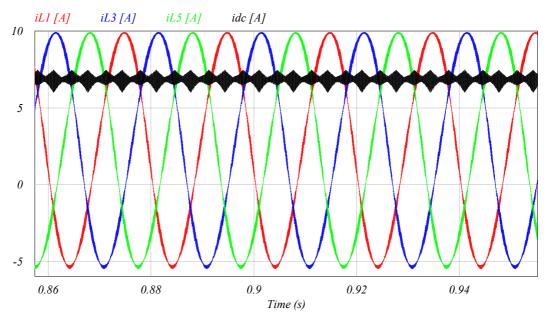

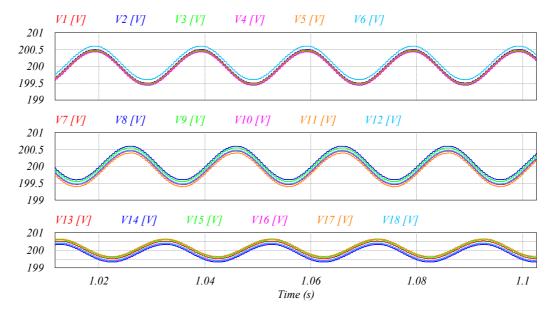

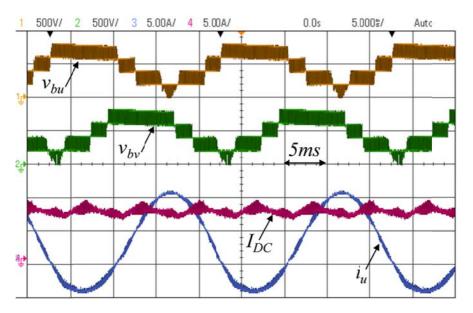

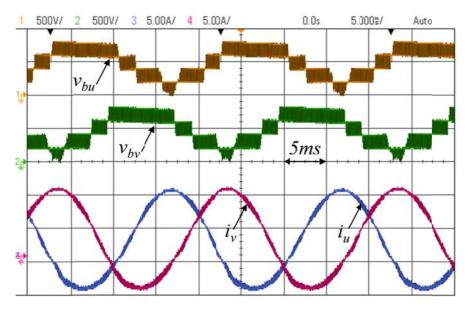

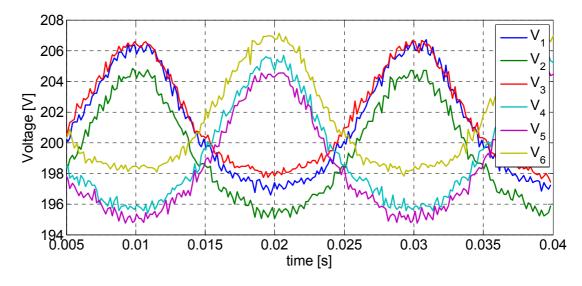

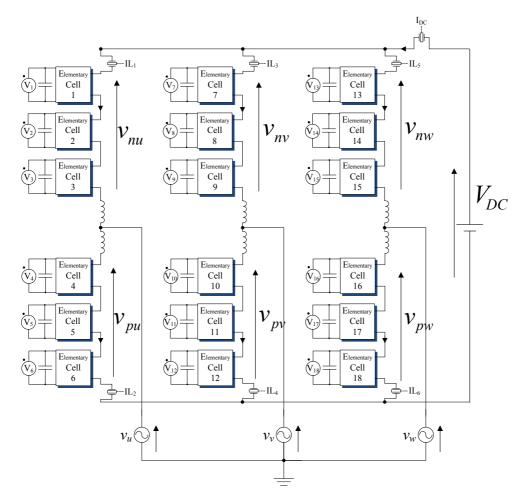

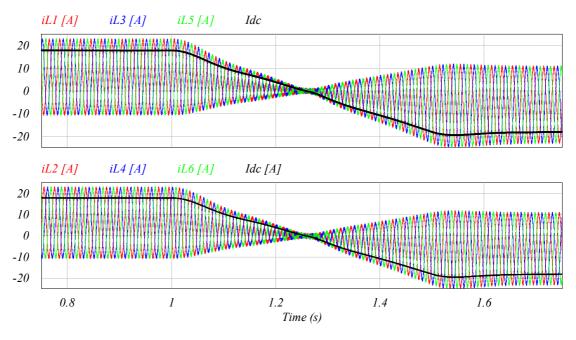

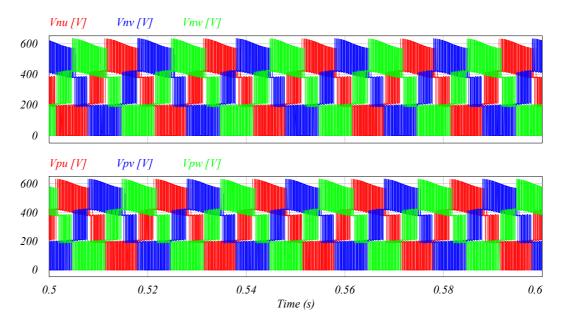

| Chapter<br>II.1<br>II.1<br>II.2<br>II.2<br>II.2<br>II.2<br>II.3 | II. The I<br>1                                                   | MMC systems<br>Macro Model<br>Macro model validation<br>Study of the MMC basic structure<br>put current imposition<br>Cell capacitor<br>Branch inductor<br>Simulations<br>ch current imposition           | <ol> <li>33</li> <li>34</li> <li>36</li> <li>38</li> <li>40</li> <li>42</li> <li>43</li> <li>48</li> <li>53</li> <li>54</li> </ol>             |