# Guidelines for MOSFET Device Optimization accounting for L-dependent Mobility Degradation

Grégory Bidal, Dominique Fleury, Gérard Ghibaudo, Frédéric Boeuf, Thomas

Skotnicki

## ▶ To cite this version:

Grégory Bidal, Dominique Fleury, Gérard Ghibaudo, Frédéric Boeuf, Thomas Skotnicki. Guidelines for MOSFET Device Optimization accounting for L-dependent Mobility Degradation. Silicon Nanoelectronics Workshop (SNW), Jun 2009, Kyoto, Japan. pp.25-26. hal-00465794v2

## HAL Id: hal-00465794 https://hal.science/hal-00465794v2

Submitted on 24 Mar 2010  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Guidelines for MOSFET Device Optimization accounting for L-dependent Mobility Degradation

G. Bidal<sup>1,2</sup>, D. Fleury<sup>1,2</sup>, G. Ghibaudo<sup>2</sup>, F. Boeuf<sup>1</sup> and T. Skotnicki<sup>1</sup>

<sup>1</sup> STMicroelectronics, 850 rue Jean Monnet, 38926 Crolles, France ; <sup>2</sup> IMEP-LAHC, 3 Parvis Louis Néel, 38016 Grenoble, France

Tel: +33 438-92-3688, Fax: +33 438-92-3790, Email: frederic.boeuf@st.com

#### Abstract

This paper reports a new methodology to monitor L-dependent mobility degradation based on empirical modeling of experimental results. This method allows benchmarking the impact on mobility degradation of different technological modules, thus giving some guidelines for device optimization.

#### Introduction

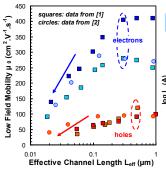

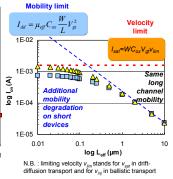

As channel length L of MOSFETs is scaling down, carriers' mobility µ is degraded by additional scattering mechanisms with a dramatic impact below 100nm. As reported by Andrieu et al. [1] and by Cros et al. [2] (Fig.1), this mobility crisis affects both electrons and holes. Moreover, this degradation has been measured for both poly-Si gate and metal gate [3], for both high-K and SiO<sub>2</sub> [4], for strained and unstrained devices [1,3], for doped and undoped channel [2,4] and also whatever the device architecture: Bulk [1], SOI, [4,5], Gate-All-Around [2] or FinFET [6]. This  $\mu(L)$  degradation was confirmed whatever the extraction method, i.e. Y-function, Split-CV or magneto-resistance [7], and cannot be solely explained by ballistic effects [8,9]. Unfortunately, mobility falls is a sign of a poor quality of the transport in the channel keeping us away from the ballistic regime. Whatever the conduction regime (ballistic or drift-diffusion), the on-state current will be limited by a maximum velocity that can be expressed as  $v_{lim} = min(v_{sat}, v_{inj})$  [10]. As shown in Fig.2, strong mobility degradation on short devices prevents from reaching the velocity limit, i.e. maximum on-current. Some authors [7,11] have identified those additional scattering mechanisms as impurity Coulomb scattering while neutral defects have been suggested by others [2,4]. This statement gives ground for a systematic examination of  $\mu(L)$  degradation in order to establish guidelines for device optimization even if the precise origin of those additional scattering mechanisms is still not fully understood.

#### Extraction Methodology & µ-Degradation Modeling

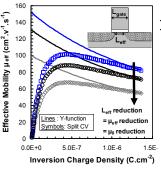

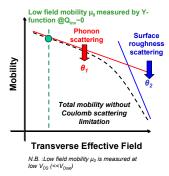

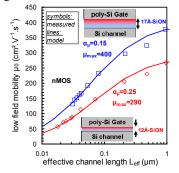

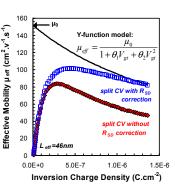

A handy tool for extracting the mobility and monitoring its length dependence is the low field mobility  $\mu_0 = \mu_{eff}(Q_{inv} \approx 0) = \beta_0 C_{os}^{-1} L_{eff} W_{eff}^{-1}$  $\beta_0$  at low  $V_{DS}$  (<< $V_{Dsat}$ ) is extracted from the Y-function [12]  $Y(V_{GS})=I_D/g_m^{-1/2}$  while effective channel length and width (resp. L<sub>eff</sub>) and Weff) and gate oxide capacitance Cox are obtained independently from gate-to-channel  $C_{GC}(V_{GS})$  measurements [13]. The notion of  $\mu_0$ is illustrated by Fig.3. It is also worth noticing that classical Coulomb scattering and surface roughness terms do not significantly alter  $\mu_0$  at 300K. Using first order  $\theta_1$  and second order  $\theta_2$  mobility attenuation parameters,  $\mu_{eff}$  in strong inversion can be reconstructed, showing good agreement in Fig.4 with R<sub>SD</sub>-corrected split C-V extraction [14]. The use of  $\mu_0$  as a mobility indicator has been validated in Fig.5 by comparing it to split C-V extraction for different Leff, clearly showing that  $\mu_0$  and  $\mu_{eff}$  are degraded in similar way as  $L_{eff}$  is reduced. All our  $\mu_0$  extraction have been performed vs. L<sub>eff</sub> to fairly compare the different technological splits. In order to construct our guidelines, we have introduced a new length dependent mobility degradation fitting model:  $1/\mu_0(L_{eff})=1/\mu_{max}+\alpha_{\mu}/L_{eff}$ . The two fitting parameters are the maximum mobility  $\mu_{max}$  [cm<sup>2</sup>.V<sup>-1</sup>.s<sup>-1</sup>], which is generally equal to the "long" channel mobility, and a mobility degradation factor  $\alpha_{\mu}$ [nm.V.s.cm<sup>-2</sup>]. Fig.6 illustrates the different kinds of  $\mu_0(L_{eff})$  curves that can be obtained,  $\alpha_u=0$  meaning zero degradation and thus a constant  $\mu_0$ . However, it should be noted that  $\alpha_{\mu}$  cannot be lower than its minimum value given by the ballistic mobility [15]  $\alpha_{ubal}$ =  $(2kT/q)/v_{inj}$ ,  $v_{inj}$  being the injection velocity at source ( $\alpha_{\mu bal} = 0.04$  or 0.08 nm.V.s.cm<sup>-2</sup> for electron and hole respectively).

#### **Experimental Results**

<u>Gate stack</u>: Gate stack impact on  $\mu_0$  was examined in Fig.7 & Fig.8. In Fig.7, two plasma nitrided SiON gate oxide thicknesses (12Å vs. 17Å) were compared for the same poly-Si gate, showing more degraded electron mobility for the thinner 12Å oxide. In Fig.8, we have found that nitrided metal gates (TiN, TaN) lead to more degraded electron mobility than the non-nitrided TaC metal gate. Those results are suggesting that N-species in the gate oxide and/or in the gate electrode lead to a lower long channel mobility in agreement with [16], but also to a higher  $\alpha_{\mu}$  i.e. to stronger scattering mechanisms.

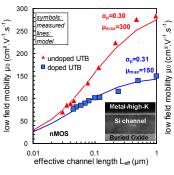

<u>Channel doping</u>: Effect of channel doping was examined in Fig.9 using ultra thin body (UTB) structures in both cases (doped vs. undoped) for avoiding short channel effects disturbances. Devices fabricated using Silicon-On-Nothing (SON) technology have bulk S/D [17]. We found that increasing the channel doping is lowering the long channel electron mobility but has no significant effect on additional scattering mechanisms since close  $\alpha_u$  values were found.

<u>Junction architecture</u>: Since neutral defects introduction is likely related to the junction (S/D+LDD) ion implantation (I/I), S/D architecture appears as a key module for improving mobility degradation. Cros *et al.* have already shown in [2] that an increase of the temperature during the RTP activation anneal could cure partially the mobility degradation. Taking the problem differently, we have examined if it was possible to improve mobility degradation by changing I/I conditions (species, energy, dose). Results in Fig. 10 are demonstrating that S/D architecture optimization is possible even when reducing the RTP temperature.

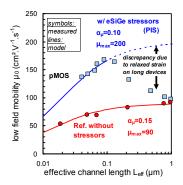

<u>Mobility boosters:</u> After having examined some possible causes of degradation, we have now investigating the effects of mobility boosters on mobility degradation. Local process induced stress (PIS) engineering by using eSiGe stressors is studied in Fig.11, while surface orientation is considered in Fig.12. Even if both strategies have an impact on holes'  $\mu_{max}$ , only local PIS which is also L-dependent [18] significantly improves  $\alpha_{\mu}$ .

#### **Discussion & Guidelines**

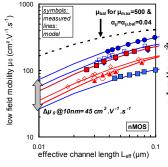

Seeing the strong degradation of the mobility, one could think that any mobility improvement is not relevant since all strategies will finally have the same mobility at very short gate length. Using our model, we have extrapolated from the measurements the resulting mobility at L<sub>eff</sub>=10nm in Fig.13. We can see that mobility improvement is still possible even at 10nm if well optimized. We have also investigated a possible link between  $\mu_{max}$  and  $\alpha_{\mu}$  in Fig.14: no clear correlation was found between the two parameters meaning that they are needed to monitor the mobility degradation. Thus we have introduced a new figure of merit  $\eta = \mu_{max}/\alpha_{\mu}$ . Higher  $\eta$  is, higher the short channel mobility will be and closer to its limiting velocity the device will operate. Finally, we give some guidelines, based on this work in Fig.15 in order to limit  $\mu(L)$  degradation.

#### Conclusion

Using a new monitoring method based on empirical modeling of  $\mu(L)$  degradation, we have systematically examined the impact on  $\mu(L)$  of the gate stack, channel doping, junction architecture and mobility boosters. It has been found that this degradation is not ineluctable and that working on key technological modules would help us to get closer to the ballistic regime.

#### Acknowledgments

The authors thank Process Integration teams and ST-LETI Advanced R&D for devices fabrication. This work was partially supported by IST-PULLNANO project.

Fig.1: Literature data from [1] & [2] clearly showing length dependent mobility degradation for both electrons and holes.

Fig.5:  $\mu_{eff}$  measurements for different  $L_{eff}$ .  $\theta_1$  and  $\theta_2$  are kept constant for all channel lengths. Inset:  $L_{eff}$  definition

Fig.9: Comparison of electron mobility between undoped & doped ultra thin body (UTB) with high-K/metal gate stack.

Fig.13: Sub-100nm electron mobility with extrapolation at  $L_{eff}$ =10nm using our model.

Fig.2: Strong mobility degradation on short devices prevents from reaching the velocity limit, i.e. maximum on-current.

Fig.6: Length dependent mobility degradation model introducing mobility degradation factor  $\alpha_{\mu}$ . For  $\alpha_{\mu}$ =0,  $\mu_0(L_{eff})$ =Cte.

Fig.10: Comparison of electron mobility between two S/D architectures while keeping the same Poly/SiON gate stack.

Fig.14:  $\alpha_{\mu}$  as a function of  $\mu_{max}$ clearly showing no universal correlation between  $\alpha_{\mu} \& \mu_{max}$ .

Fig.3: Illustration of low field mobility  $\mu_0=\mu(Q_{inv}\approx 0)$ . Coulomb scattering & surface roughness limitations are negligible.

Fig.7: Comparison of electron mobility between two SiON gate oxide thicknesses. Thinner 12Å oxide is more degraded than 17Å.

Fig.11: Comparison of hole mobility between unstrained reference and locally strained device with eSiGe S/D stressors.

|    | echno.<br>Iodule    | impact<br>on<br>µ <sub>max</sub> | impact<br>on α <sub>µ</sub> | η           |

|----|---------------------|----------------------------------|-----------------------------|-------------|

| Ga | te stack            | +                                | ++                          | x2 to<br>x4 |

| Ju | nctions             | +                                | +                           | x2          |

| -  | hannel<br>oping     | ++                               | =                           | x2          |

| Lo | cal PIS             | ++                               | +                           | x3          |

|    | Crystal<br>entation | ++                               | =                           | X2          |

Fig.15: Guidelines for short channel mobility optimization based on the figure of merit  $\eta = \mu_{max} / \alpha_{\mu}$ .

Fig.4: Series resistance  $R_{SD}$  correction which is critical on short devices is intrinsically taken into account when using Y-function.

Fig.8: Comparison of electron mobility between different metal gate materials. Nitrided metals are more degraded than not nitrided.

Fig.12: Comparison of hole mobility between (100)/<110> device and (110)/<110> device with same poly/SiON gate stack.

#### References

F.Andrieu et al., VLSI 2005. [2] A.Cros et al., IEDM 2006. [3] G.Bidal et al., SSDM 2008. [4]

L.Pham-Nguyen et al., SOI conf. 2008. [5]

C.Gallon et al., SOI conf. 2005. [6] J.Ramos et al., ESSDERC 2006. [7] M.Cassé et al., VLSI 2008. [8] M.Zilli et al., EDL, v.28, Issue 11, 2007. [9] I.Pappas et al., SSE, v.53, 2009. [10]

D.Fleury et al., submitted to VLSI 2009. [11]

V.Barral et al., SNW 2008. [12] G. Ghibaudo et al., Elsc. Let., v.24, 1988. [13] D.Fleury et al., TSM, v. 21, Issue 4, 2008. [14] K. Romanjek et al., EDL, v.25, 2004. [15] M.Shur et al., EDL,

v23, 2002. **[16]** X.Garros *et al.*, VLSI 2008. **[17]** G.Bidal *et al.*, VLSI 2008. **[18]** F.Payet *et al.*, TED v. 55, Issue 4, 2008.